MIMO-OFDMA無線基站的DSP-FPGA系統(tǒng)劃分

引言

無線運(yùn)營(yíng)商通過提供增強(qiáng)數(shù)據(jù)服務(wù)來提高單位用戶平均收益(ARPU),這同時(shí)推動(dòng)了對(duì)寬帶的需求,導(dǎo)致對(duì)數(shù)據(jù)速率的要求越來越高。而且,為用戶提供各種應(yīng)用體驗(yàn)的要求也促使底層網(wǎng)絡(luò)體系結(jié)構(gòu)進(jìn)行變革。

窄帶2G GSM、IS-95系統(tǒng)等以語音為中心的技術(shù)已經(jīng)發(fā)展到了基于WCDMA的HSDPA和HSUPA系統(tǒng),峰值數(shù)據(jù)速率達(dá)到了10Mbps。今后的3GPP長(zhǎng)期發(fā)展規(guī)范采用了多輸入多輸出(MIMO)等復(fù)雜的信號(hào)處理技術(shù),以及正交頻分復(fù)用接入(OFDMA)和多載波碼分復(fù)用接入(MC-CDMA)等新的射頻技術(shù),這些技術(shù)是實(shí)現(xiàn)100 Mbps以上吞吐量的關(guān)鍵。WiMAX等其他OFDM寬帶無線系統(tǒng)也在不斷發(fā)展,傳輸速率已經(jīng)超過了70 Mbps。

數(shù)據(jù)速率之所以能夠提高,主要是使用了高階調(diào)制技術(shù)以及可變速率通道編碼,也就是常說的自適應(yīng)調(diào)制和編碼(AMC)等技術(shù)。復(fù)雜的空間信號(hào)處理方法,例如聚束和MIMO天線技術(shù),也是提高數(shù)據(jù)速率成熟可靠的技術(shù),但其代價(jià)是需要進(jìn)行復(fù)雜的計(jì)算。對(duì)于設(shè)計(jì)基站的OEM而言,這些支撐技術(shù)帶來了很大的挑戰(zhàn),設(shè)計(jì)的基站不但要有很高的性價(jià)比,能夠更新,而且要非常靈活,隨著標(biāo)準(zhǔn)的發(fā)展能夠繼續(xù)使用。

基站設(shè)計(jì)要求

無線系統(tǒng)設(shè)計(jì)人員需要滿足的關(guān)鍵需求包括處理速度、靈活性以及產(chǎn)品及時(shí)面市等,所有需求最終決定了對(duì)硬件平臺(tái)的選用。

處理帶寬

WiMAX和LTE寬帶無線系統(tǒng)對(duì)吞吐量和數(shù)據(jù)速率的要求遠(yuǎn)遠(yuǎn)高于WCDMA和cdma2000等蜂窩系統(tǒng)。為了能夠支持如此高的數(shù)據(jù)速率,底層硬件平臺(tái)必須有足夠的處理帶寬。而且,Turbo編解碼等高級(jí)信號(hào)處理技術(shù)以及快速傅立葉變換/反變換(FFT/IFFT)、聚束、MIMO、峰值因子抑制(CFR)和數(shù)字預(yù)失真(DPD)等前端功能都需要進(jìn)行大量的計(jì)算,每秒乘累加(MAC)操作高達(dá)數(shù)十億次。

靈活性

WiMAX是相對(duì)較新的市場(chǎng),目前還處于最初的發(fā)展和實(shí)施階段。同樣,3GPP LTE也還在制定過程中,在最終完成之前,還需要經(jīng)過多個(gè)版本的修訂。雖然有很多種移動(dòng)寬帶技術(shù),例如WiMAX、LTE和UMB等,但它們的共同點(diǎn)是OFDMA-MIMO。在目前的背景下,需要有靈活的可編程產(chǎn)品來實(shí)現(xiàn)標(biāo)準(zhǔn)未確定的或多協(xié)議的基站。系統(tǒng)如果具有這種靈活性,無線基礎(chǔ)設(shè)施OEM和運(yùn)營(yíng)商則可以大大降低資金投入和運(yùn)營(yíng)開支,同時(shí)減小了標(biāo)準(zhǔn)不斷變化帶來的風(fēng)險(xiǎn)。

降低成本的途徑

設(shè)計(jì)和開發(fā)3G系統(tǒng)時(shí)得出的一個(gè)重要經(jīng)驗(yàn)是從一開始就要制定長(zhǎng)期降低成本的策略。不斷發(fā)展的WiMAX和LTE標(biāo)準(zhǔn)最終會(huì)穩(wěn)定下來。OEM和服務(wù)供應(yīng)商要保持在市場(chǎng)上的競(jìng)爭(zhēng)地位,必須重視最終產(chǎn)品的成本,這要比靈活性重要得多。合適的硬件平臺(tái)也是降低批量生產(chǎn)成本的無縫措施,能夠節(jié)省數(shù)百萬美元由系統(tǒng)重新設(shè)計(jì)導(dǎo)致的工程成本投入。

系統(tǒng)體系結(jié)構(gòu)設(shè)計(jì)和邏輯任務(wù)劃分

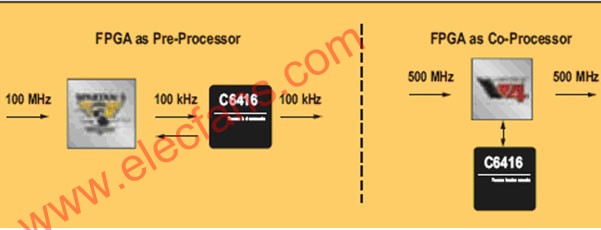

信號(hào)處理數(shù)據(jù)通路和控制運(yùn)算是無線基站中最主要的處理負(fù)荷。大部分體系結(jié)構(gòu)結(jié)合使用微控制器(MCU)、FPGA和可編程數(shù)字信號(hào)處理器來實(shí)現(xiàn)系統(tǒng)控制、配置和信號(hào)處理數(shù)據(jù)通路。MCU控制系統(tǒng),而FPGA和數(shù)字信號(hào)處理器進(jìn)行數(shù)據(jù)流處理。處理任務(wù)較輕,主要面向控制的任務(wù)在數(shù)字信號(hào)處理器中通過軟件來實(shí)現(xiàn);負(fù)載較重的任務(wù)最好在FPGA中進(jìn)行,它具有明顯的并行處理優(yōu)勢(shì)。數(shù)字信號(hào)處理器和FPGA相結(jié)合可實(shí)現(xiàn)非常靈活的系統(tǒng),其可編程能力有助于改正缺陷,甚至能夠支持完全不同的標(biāo)準(zhǔn)。

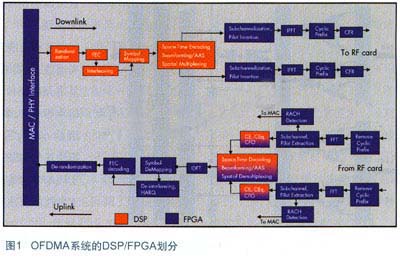

FPGA和數(shù)字信號(hào)處理器之間的劃分取決于處理需求,系統(tǒng)帶寬以及系統(tǒng)配置,發(fā)送和接收天線的數(shù)量等。圖1所示為WiMAX和LTE等OFDMA系統(tǒng)中實(shí)現(xiàn)基帶物理層(PHY)功能時(shí)典型的數(shù)字信號(hào)處理器/FPGA劃分。

通過采用高級(jí)多路天線技術(shù),這類系統(tǒng)的吞吐量將有可能超過100 Mbps。基帶PHY功能可以大致分為比特級(jí)處理和符號(hào)級(jí)處理兩類。下面幾節(jié)介紹了這些功能,以及怎樣使用FPGA來完善DSP模塊,同時(shí)實(shí)現(xiàn)比特級(jí)和符號(hào)級(jí)功能。

比特級(jí)處理

比特級(jí)模塊包括發(fā)送側(cè)的隨機(jī)處理、前向糾錯(cuò)(FEC)、頻譜交錯(cuò)、正交相移鍵控(QPSK)和正交振幅調(diào)制(QAM)功能映射等。相應(yīng)的接收處理比特級(jí)模塊是符號(hào)去映射、頻譜去交錯(cuò)、FEC解碼和去隨機(jī)。發(fā)送比特級(jí)功能相對(duì)簡(jiǎn)單,計(jì)算量不大。例如,隨機(jī)處理涉及到數(shù)據(jù)比特和簡(jiǎn)單偽隨機(jī)二進(jìn)制序列發(fā)生器輸出的模2加運(yùn)算。在比特級(jí)處理上,雖然FPGA要比固定總線寬度的數(shù)字信號(hào)處理器靈活一些,但是更容易在數(shù)字信號(hào)處理器上實(shí)現(xiàn)這些計(jì)算量不大的函數(shù)。相反,隨著吞吐量需求的增加,可以把Turbo編碼功能卸載到FPGA中,以提高系統(tǒng)的性能。在接收側(cè),F(xiàn)EC解碼,包括Viterbi解碼、Turbo卷積解碼、Turbo乘解碼和LDPC解碼等,在數(shù)字信號(hào)處理器中實(shí)現(xiàn)時(shí),其計(jì)算量比較大,占用較大的帶寬。

FPGA被廣泛用于卸載這些功能,釋放數(shù)字信號(hào)處理器帶寬以處理其他功能。在同一FPGA中實(shí)現(xiàn)去隨機(jī)、去速率匹配和混合ARQ等其他比特級(jí)功能減少了FPGA和數(shù)字信號(hào)處理器之間的數(shù)據(jù)傳送,降低了延時(shí)和系統(tǒng)總功耗。同一FPGA還可以用于和MAC層接口,實(shí)現(xiàn)加密/解密和認(rèn)證等某些底層MAC功能。

符號(hào)級(jí)處理

OFDMA系統(tǒng)中的符號(hào)級(jí)功能包括副通道和去副通道、FFT/IFFT、信道估算/均衡、測(cè)距/隨機(jī)訪問通道(RACH)探測(cè)等功能。其他功能包括DFT/IDFT(LTE確定的),以及通道卡可能采用的CFR等。通道估值和均衡可以離線執(zhí)行,涉及到更適合在數(shù)字信號(hào)處理器中實(shí)現(xiàn)的控制算法。相反,F(xiàn)FT和IFFT函數(shù)是普通的數(shù)據(jù)通路函數(shù),需要以非常快的速度進(jìn)行復(fù)數(shù)乘法,更適合在FPGA上實(shí)現(xiàn)。RACH探測(cè)和CFR等功能也需要高性能的低延時(shí)FFT/IFFT運(yùn)算。

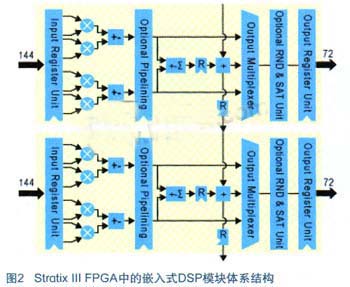

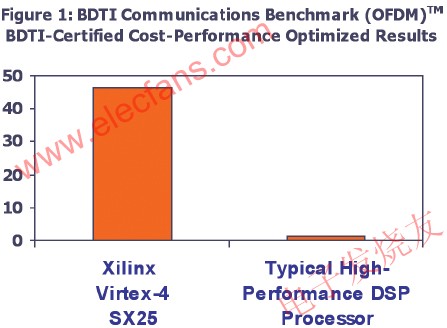

圖2所示為高端FPGA(Altera Stratix III器件)中含有的嵌入式DSP模塊。DSP模塊一般包括8個(gè)專用乘法器;而Stratix III EP3SE110等高級(jí)FPGA的112個(gè)DSP模塊能夠提供896個(gè)18x18乘法器,吞吐量高達(dá)500 GMAC。這要比目前市場(chǎng)上的商用數(shù)字信號(hào)處理器高出一個(gè)數(shù)量級(jí)。

在基站中采用高級(jí)多路天線技術(shù)時(shí),例如空時(shí)編碼(STC)、聚束和MIMO方案等,F(xiàn)PGA和數(shù)字信號(hào)處理器的這種信號(hào)處理能力差異便顯得更加突出。在目前以及今后的WiMAX和LTE無線系統(tǒng)中,普遍認(rèn)為OFDM-MIMO相結(jié)合是實(shí)現(xiàn)更高數(shù)據(jù)速率的關(guān)鍵。

圖1所示的是基站中采用的多路發(fā)送和接收天線。在這種配置中,進(jìn)行MIMO解碼前,對(duì)每一天線流單獨(dú)進(jìn)行符號(hào)處理,產(chǎn)生單路比特級(jí)數(shù)據(jù)流。當(dāng)在數(shù)字信號(hào)處理器上實(shí)現(xiàn)的天線以串行方式執(zhí)行操作時(shí),符號(hào)級(jí)處理的復(fù)雜度會(huì)隨之線性增加。例如,使用兩路發(fā)送和接收天線時(shí),假設(shè)FFT和IFFT變換長(zhǎng)度為2048點(diǎn),其運(yùn)算將占用1GHz數(shù)字信號(hào)處理器60%的處理能力。相比之下,采用FPGA時(shí),可以有效地?cái)U(kuò)展實(shí)現(xiàn)多路天線。FPGA對(duì)多路天線數(shù)據(jù)進(jìn)行時(shí)分復(fù)用和并行處理。同一2x2天線FFT/IFFT配置可以利用不到5%的Stratix III EP3SE110 FPGA資源來實(shí)現(xiàn)。

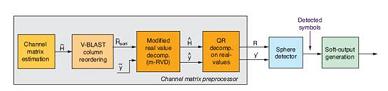

多路天線方案的優(yōu)勢(shì)更明顯,包括更高的數(shù)據(jù)速率、陣列增益、分集增益和鄰近信道干擾抑制能力等。聚束和空分復(fù)用MIMO技術(shù)對(duì)計(jì)算量的要求較大,涉及到矩陣分解和相乘等運(yùn)算。特別是在這些系統(tǒng)中解線性方程組時(shí),需要采用Cholesky分解、QR分解和奇異值分解函數(shù)。這些函數(shù)會(huì)很快耗盡DSP資源,但在采用了脈動(dòng)陣列結(jié)構(gòu)的FPGA中實(shí)現(xiàn)卻非常適合,這種結(jié)構(gòu)通過并行FPGA來提供最具成本效益的解決方案。

數(shù)字IF處理和RRH

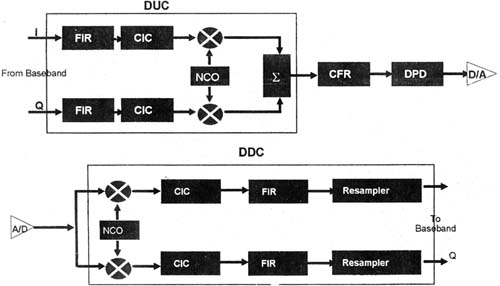

圖3顯示了基帶通道卡向RF卡發(fā)送數(shù)據(jù),進(jìn)行后續(xù)的數(shù)字中頻(IF)處理,包括數(shù)字上變頻(DUC)、CFR和DPD。數(shù)字IF將數(shù)字信號(hào)處理的范圍從基帶擴(kuò)展到了天線--RF域,在降低生產(chǎn)成本的同時(shí)提高了系統(tǒng)靈活性。而且,數(shù)字變頻要比傳統(tǒng)的模擬技術(shù)更靈活,性能更好(在衰減和選擇性方面)。需要采用CFR和DPD功能來提高基站功率放大器的效率,從而大大節(jié)省了OPEX。CFR和DPD都需要進(jìn)行采樣率高達(dá)100+Msps的復(fù)數(shù)乘法運(yùn)算。與DUC相似,在接收側(cè)需要采用數(shù)字下變頻(DDC)將IF頻率變回到基帶。

引入MIMO和多載波體系結(jié)構(gòu)需要采用時(shí)分復(fù)用和多通道技術(shù)。利用Altera的IP內(nèi)核,以及創(chuàng)新的DSP Builder工具,在Altera FPGA中可以很容易實(shí)現(xiàn)這些任務(wù)。DUC和DDC都使用復(fù)數(shù)濾波器體系結(jié)構(gòu),包括有限沖擊響應(yīng)(FIR)和級(jí)聯(lián)積分梳狀(CIC)濾波器。高級(jí)FPGA能夠提供數(shù)百個(gè)18x18乘法器,運(yùn)行速率高達(dá)350MHz。這不但為多信道并行處理提供了平臺(tái),而且還是最具成本效益的集成單芯片解決方案。另一發(fā)展趨勢(shì)是分布式BTS,射頻單元相對(duì)于BTS的其他部分位于遠(yuǎn)端,而不是在一個(gè)地方。這些射頻單元也稱為遠(yuǎn)端射頻前端(RRH),通過光鏈路和主要的BTS單元進(jìn)行通信。CPRI和OBSAI是實(shí)現(xiàn)RRH的兩個(gè)標(biāo)準(zhǔn)。CPRI和OBSAI接口一般在FPGA上實(shí)現(xiàn),利用BTS體系結(jié)構(gòu)的多通道特性可以實(shí)現(xiàn)成本效益非常好的解決方案。

結(jié)論

隨著標(biāo)準(zhǔn)的穩(wěn)定,應(yīng)該逐漸降低最初對(duì)基站靈活性的要求,在這一階段,高性能和長(zhǎng)期降低成本的途徑是獲得市場(chǎng)成功的關(guān)鍵因素。一般采用ASIC來降低成本。FPGA可以無風(fēng)險(xiǎn)移植到低成本結(jié)構(gòu)化ASIC,通過這一途徑能夠大大降低產(chǎn)品生命周期的后期成本。例如,Altera HardCopy II技術(shù)提供了無縫、無風(fēng)險(xiǎn)移植途徑,從Stratix II FPGA轉(zhuǎn)換到成本很低的ASIC,同時(shí)也提高了系統(tǒng)性能。HardCopy能夠把成本和功耗降低近70%,進(jìn)一步減小了封裝尺寸,同時(shí)降低了CAPEX和OPEX的構(gòu)成成本。

在目前的無線基站設(shè)計(jì)中采用數(shù)字信號(hào)處理器和PLD一直是有效的設(shè)計(jì)方法。從系統(tǒng)吞吐量需求以及對(duì)成本的長(zhǎng)期考慮出發(fā),產(chǎn)品要獲得成功的關(guān)鍵是基站體系結(jié)構(gòu)的智能劃分。這樣可以確保最終的產(chǎn)品能夠更新,性價(jià)比高,而且非常靈活,隨著多種標(biāo)準(zhǔn)的發(fā)展而重新進(jìn)行配置。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論