AD8150數(shù)字交叉式轉換開關

AD8150是ANALOG DEVICES公司生產(chǎn)的數(shù)字交叉式轉換開關,它具有1Gbps的高數(shù)據(jù)通過率、低功耗、完全差動、PECL和ECL兼容等優(yōu)良性能。文中介紹了AD8150的主要特點、引腳功能、內(nèi)部電路和工作原理。最后介紹了它的接口設計方法。

??? 關鍵詞:轉換開關 完全差動 轉換矩陣 AD8150

1 概述

AD8150是一個巨大的開關矩陣(33×17),它功耗小于1.5W,并可在超過每端口1.5Gb/s的速率下運行,而且,AD8150的價格低廉,因而適用于高清晰度電視、SD數(shù)字視頻以及OC-24光學網(wǎng)絡轉換等方面的應用。

AD8150的供電電壓靈活,可以實現(xiàn)PECL和ECL的數(shù)據(jù)電平操作,它可在+3.3V的電壓下運行,因而可進一步降低功率。其控制接口與CMOS/TTL兼容(+3V~+5V)。當允許使用較小的單端電壓振幅時,它的全差動信號路徑可減小抖動和交調(diào)失真。AD8150采用184腳LQFP封裝,工作溫度為0~85℃。

此外,AD8150還有如下主要特性;

●價格低廉;

●具有33×17開關陣列,可完全差動式工作;

●具有大于1.5Gb/s的每端口反向不歸零制數(shù)據(jù)速度;

●供電范圍可在+5V,+3.3V,-5V,-3.3V中選擇;

●低功耗電流使能輸出時為400mA;

非使能輸出時為300mA;

●與PECL和ECL兼容;

●CMOS或TTL控制輸入:+3V~+5V;

●抖動小于50ps p-p;

●無散熱要求;

●輸出電流可編程,可以優(yōu)化負載阻抗,并可由用戶控制負載電壓,以使電源消耗最小;

●總線和建立可單獨使能輸出;

●具有雙排鎖定功能;

●具有緩沖輸入功能;

●采用184管腳LQFP封裝;

●可應用于高清晰度電視和SD數(shù)字視頻(電視)以及光纖通信轉換等方面。

2 工作原理及引腳說明

2.1 工作原理

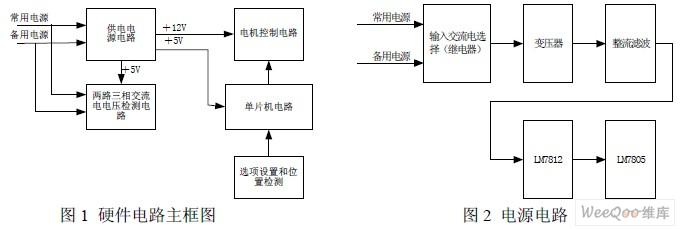

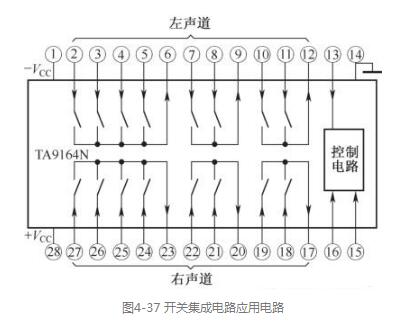

AD8150的內(nèi)部框圖如圖1所示,它的控制接口可接收和存儲33個輸入信號及17個輸出信號,該接口包括17行雙精度的7位鎖存器,每行輸出一路信號。存儲在這些鎖存器中的7位數(shù)據(jù)用來控制連接33個輸出中的某一個。

通過設置輸出地址可將所需連接的數(shù)據(jù)寫入到第一級鎖存器中,這樣可以預先編程使開關一次只輸出一路信號。此過程可以反復進行,直至每一個輸出的變化均被編程后,再通過從第一級鎖存器把數(shù)據(jù)傳輸?shù)降诙夋i存器即可編程所有輸出連接。需是說明是的:只有第一級鎖存器的數(shù)據(jù)完全置入第二級之后,連接才有效。

為滿足系統(tǒng)分辨率的需要,第二級鎖存器的數(shù)據(jù)可以從控制接口讀回。

任何時候都可以將一個復位脈沖加到控制接口上,這樣可以使第二級中適當?shù)奶卣鲾?shù)據(jù)復位,但這時17個信號均不可輸出。這一性能可以避免在系統(tǒng)啟動時發(fā)生輸出總線競爭現(xiàn)象。進行此操作地,第一級數(shù)據(jù)保持不變。

接口控制引腳可借助于邏輯電平轉換器進行連接,并且允許控制接口的編程和讀操作使用不同于信號矩陣的邏輯電平。

為了方便多個器件的地址譯碼,設器件配置了一個片選引腳。只有在片選引腳有效時,所有邏輯信號(除復位脈沖)才有效。片選引腳只能使控制接口停止工作,并不影響信號矩陣的信號傳輸。片選引腳不會使任何鎖存器掉電,存入鎖存器的所有數(shù)據(jù)均被保存。

所有控制引腳均為電平觸發(fā),而非邊沿觸發(fā)。

2.2 管腳說明

A4~A0輸入:輸出地址引腳。通過這5個輸入引腳的狀態(tài)可決定17個輸出中的某一個是補編程還是補讀回。其最高有效位為A4。

D6~D0輸入/輸出:設置數(shù)據(jù)輸入引腳。在進行寫操作時,通過引腳D6~D0的二進制編碼數(shù)據(jù)來決定33個輸入中的哪一個連接到A4~A0指定的輸出腳上。最高有效位是D5,最低有效位是D0。D6為使能位,它若為高電平,則可使指定輸出信號為使能狀態(tài);若為低電平,則使之為高阻態(tài)。

在讀回模式下,引腳是低阻抗輸出,表明數(shù)據(jù)字節(jié)已存入第二級鎖存器中,可以在A4~A0所指定的引腳上輸出。讀回驅動器只用于驅動高阻態(tài),所以在讀回模式下連至D6~D0的外部驅動器應置于禁止態(tài)。

WE輸入:第一級寫使能引腳。置此引腳為低電平可將D6~D0引腳的數(shù)據(jù)存入到A4~A0指定的輸出腳的第一級鎖存器中。該引腳在一個寫循環(huán)之后必須回復至高電平,以免第一級數(shù)據(jù)被覆蓋。

UPDATE輸入:第二級寫使能引腳。置此引腳為低電平,可使17個第一級鎖存器中的數(shù)據(jù)傳輸?shù)降诙夋i存器中。當?shù)诙夋i存器的數(shù)據(jù)改變時,信號連接矩陣將重新被編程。這是一個共用腳,一次可傳輸17行全部數(shù)據(jù),且不需對地址引腳進行編程。但應注意:上電時的第一級數(shù)據(jù)未定義。因此,在進行第一個UPDATE循環(huán)前必須提前設設17個輸出。

RE輸入:第二級讀使能引腳。置此腳為低電平可以激發(fā)雙向D[6:0]引腳上的驅動器進入讀回操作模式。如果通過A4~A0腳選擇一個輸出地址并使RE置低電平,那么存儲在第二級鎖存器中的輸出地址的7位數(shù)據(jù)將被寫入到D6~D0引腳中。在讀回模式下,數(shù)據(jù)應從外部寫入D6~D0引腳。RE引腳和WE引腳要吧同時工作而不互斥,但此時在讀回模式下,數(shù)據(jù)不能從外部寫入到D6~D0引腳。

CS輸入:片選引腳。從邏輯接口上(除了RESET引腳)讀取或接收數(shù)據(jù)時,CS引腳應置低電平。此引腳對信號無影響,也不改變已存儲的任何數(shù)據(jù)。

RESET輸入:共用輸出禁止引腳。若RESET為邏輯低電平,則不論其他引腳的狀態(tài)如何,17個第二級鎖存器的D6均復位。這樣可立即禁止在變換電路中的17個輸出信號。當AD8150用在一個有關聯(lián)輸出信號對的系統(tǒng)中時,上電時應保持RESET腳為低電平。否則,上電后會產(chǎn)生多個輸出信號的競爭。RESET引腳不受片選引腳的控制,也不對包含未定義數(shù)據(jù)的第一級鎖存器編程。

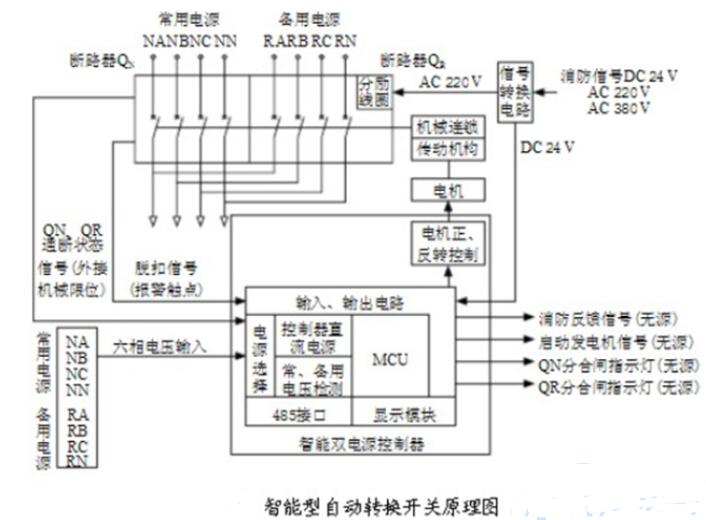

3 控制接口

圖2為AD8150的控制接口電路,該電路有兩個供電引腳,即VDD和VSS。當正電位和負是之間的電壓位于3V到5V之間時。閾值電平高于VDD約1.6V,因此,接口可用于大多數(shù)CMOS和TTL邏輯驅動器。信號轉換電路的供電引腳VCC和VEE可以獨立于VDD和VSS來進行設置,但它服從VCC和VDD的約束且(VDD-VEE)應小于10V。表1給出了控制口的真及其基本功能。

表1 基本控制功能

| 控? 制? 引? 腳 |

功?????? 能 | ||||

| RESET | CS | WE | FE | UPDATE | |

| 0 | X | X | X | X | 共用復位:使第二級鎖存器的所有使能位復位為0(禁止所有輸出) |

| 1 | 1 | X | X | X | 控制禁止:忽略所有邏輯(信號矩陣仍按設定功能工作)。D[6:0]為高阻態(tài) |

| 1 | 0 | 0 | X | X | 信號輸出預先設定:從輸入數(shù)據(jù)總線D[6:0]將輸入狀態(tài)數(shù)據(jù)寫入輸出地二總線A[4:0]所指定的第一級鎖存器中 |

| 1 | 0 | X | 0 | X | 信號通道讀回:從第二級鎖存器將輸入狀態(tài)的數(shù)據(jù)讀到數(shù)據(jù)總線D[6:0]以供輸出地址總線選定的信號輸出使用 |

| 1 | 0 | X | X | 0 | 完全更新:新17個第一極鎖存器中的輸入狀態(tài)數(shù)據(jù)復制到第二極鎖存器中,并更新連接所有輸出的信號矩陣 |

| 1 | 0 | 0 | 0 | 1 | 第二級到第一級的復制實例:可以實現(xiàn)從第二級連續(xù)讀回數(shù)據(jù)并寫入第一級。此操作在完全復位之前有效,但17個輸出必須一次復位為1 |

| 1 | 0 | 0 | 1 | 0 | 典型寫和更新實例:可以實現(xiàn)直接寫入數(shù)據(jù)到第二級。當不需要進行同步信號矩陣更新時,此操作將簡化邏輯 |

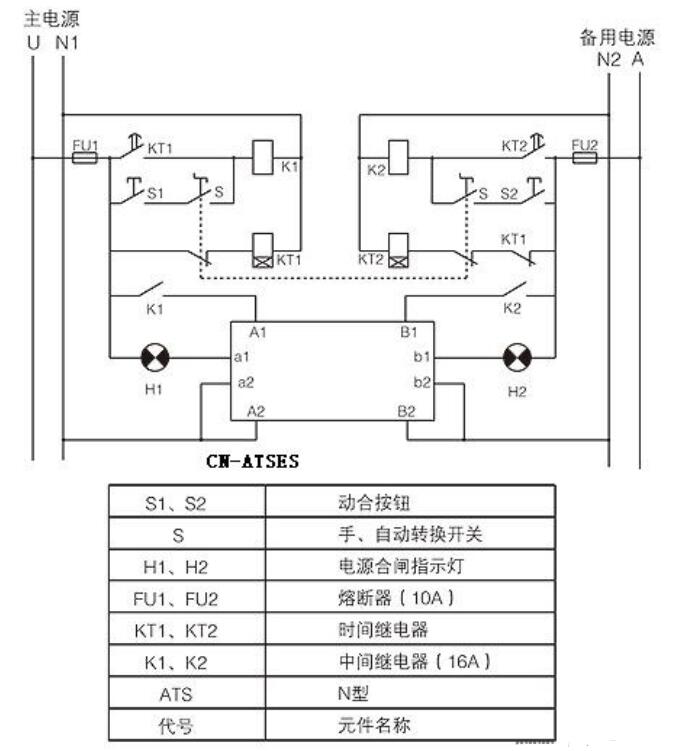

4 接口設計

AD8150是一個數(shù)據(jù)速度高達每端口1.5Gbs的33×17的差動式轉換開關。采用5V(Vcc)供電時,它支持與PECL兼容的輸入和輸出電平,當采用-5V供電(Vcc=GND,VEE=-5V)時,支持與ECL兼容的電平。為降低功耗,AD8150也支持 PECL低電壓電路,這時可工作在3.3V至最高極限的電壓下;而支持ECL低電平電路時則可工作在-3.3V至最低極限的電壓下。AD8150采用有獨立禁止控制能力的差動電流模式輸出,因而可以將并聯(lián)的多個AD8150連接在一起以實現(xiàn)更大的轉換矩陣。這樣也可以減小系統(tǒng)的交調(diào)失真,且可大大降低在一個巨大轉換矩陣中產(chǎn)生的功耗。采用單個外部電阻器可為全部使能輸出級設定電流,因此用戶可以通過改變不同的輸出級和傳輸線特性阻抗來控制輸出電平。

4.1 高速數(shù)據(jù)輸入(InxxP,INxxN)

AD8150有33對差動電壓模式的輸入。公共模式的輸入范圍從正供電電壓Vcc到包含標準ECL或PECL輸入電平(Vcc-2V)的電壓。最小的差動輸入電壓小于300mV,未工作的輸入引腳可連接至允許輸入范圍的任意電壓。圖3為AD8150的簡化輸入等效電路。

為保證信號在高速時的保真度,輸入傳輸線應盡量連接在靠近輸入引腳的地方。選擇輸入端結構的類型應視其具體的用途以及來自于某個輸出電路的數(shù)據(jù)而定。如果是由標準ECL組成的開放發(fā)射極輸出形式,則要求減小電阻器的電阻。圖4為三個適于這種源類型的網(wǎng)絡。其中圖4(a)為使用VTT供電的并行端點;圖4(b)采用THEBVENIN等效端點;圖4(c)采用差動端點。

若AD8150受其它電流輸出模式和輸出狀態(tài)(如另一個AD8150)的驅動,則輸入端點應選作與源類型一致。

4.2 高速數(shù)據(jù)輸出(OUTYYP,OUTYYN)

AD8150有17對差動電流模式的輸出。其輸出電路如圖5所示,該輸出實際上是一種開集NPN電流開關,可由電阻來控制尾電流,輸出范圍可從正電壓VCC到標準ECL或PECL輸出電平(Vcc-2V)。輸出可各自獨立地停止,從而允許AD8150上的輸出直接并聯(lián)連接。此種連接的并聯(lián)方式可使能輸出狀態(tài)的電流集總,因此應注意保證任何時候的輸出阻抗均不可超出極限,為此,應在使能任何一個尚未工作的輸出驅動器之前禁止已經(jīng)工作的驅動器。

為保證器件的正常運行,所有輸出(包括未工作的輸出)端必須被拉至高電平,這可以通過將使用外部上拉網(wǎng)絡調(diào)至輸出阻抗變化范圍內(nèi)的一個電平來實現(xiàn)。若多個AD8150的輸出連在一起,則每條輸出總線使用一個上拉網(wǎng)絡,該上拉網(wǎng)絡必須保證輸出電壓一直處于允許范圍內(nèi)。建議使用上拉網(wǎng)絡來產(chǎn)生PECL/ECL的100k和10k兼容輸出,具體電路如圖6所示。必要時可用不同的供電壓來提供VCOM、RCOM和DCOM的電壓。

輸出電壓可由下列公式計算:

VOH=VCOM

VOL=VCOM-IOUTRL

VSWING=VOH-VOL=IOUTRL

VCOM=VCC-IOUT RCOM(100k模式)

VCOM=VCC-V(DCOM)(10k模式)

若接收器的輸入范圍中包括正電壓,則公共模式調(diào)整因子(RCOM馬克VCOM)可忽略。旁路電容用來提供一個從公共結點VCOM到地的交流能路,以減小在公共模式下存在的干擾。

在AD罰150輸出集總進行聞聯(lián)或系統(tǒng)在高速工作時,建議使用輸出雙端點,以調(diào)節(jié)開放傳輸線及輸出腳集總電容帶來的反射沖擊。一種可行的連接電路如圖7所示,圖中的旁路電容用于提供從端點電阻結點到地的交流短路。為保證高速下的保真度,連接輸出腳至輸出傳輸線或負載電阻部分的連線應越短越好。

采用該電路時的輸出電平為:

VOH=VCOM-IOUTRL/4

VOL=VCOM-3IOUTRL/4

VSWING=VOH-VOL=IOUTRL/2

4.3 輸入電流設置引腳(REF)

圖8是一個簡化的等效參考電路。在所有輸出狀態(tài)下,連接在REF和VEE之間的一個外部電阻RSET可以決定輸出電流的大小。利用這一特點可以實現(xiàn)對拉動網(wǎng)絡和傳輸線特性阻抗的選擇,同時可得到約800mV的輸出小擺動。在低速下,利用輸出小擺動和大裝載電阻可以得到極有價值的節(jié)能。其輸出電流可由下式給出:

IOUT=20×1.25V/RSET

在調(diào)整電阻RSET取1kΩ的最小值時,可產(chǎn)生25mA最大的IOUT電流,而將RSET調(diào)至5kΩ的最大值時,可產(chǎn)生5mA的最小輸出電流。在負載為50Ω、RSET為1.56kΩ(IOUT=16mA)或在雙端點負載為75Ω、RSET為1.17kΩ(IOUT=21.3mA)時可以獲得800mV的微小輸出擺動。

為將分布電容減至最小以避免引入干擾信號,可將外部調(diào)整電阻安裝在靠近REF腳的地方。并且不要對其旁路。

電子發(fā)燒友App

電子發(fā)燒友App

評論