模數(shù)轉(zhuǎn)換技術(shù)原理及發(fā)展

隨著電子技術(shù)的迅速發(fā)展以及計(jì)算機(jī)在自動(dòng)檢測和自動(dòng)控制系統(tǒng)中的廣泛應(yīng)用,利用數(shù)字系統(tǒng)處理模擬信號的情況變得更加普遍。數(shù)字電子計(jì)算機(jī)所處理和傳送的都是不連續(xù)的數(shù)字信號,而實(shí)際中遇到的大都是連續(xù)變化的模擬量,模擬量經(jīng)傳感器轉(zhuǎn)換成電信號的模擬量后,需經(jīng)模/數(shù)轉(zhuǎn)換變成數(shù)字信號才可輸入到數(shù)字系統(tǒng)中進(jìn)行處理和控制,因而作為把模擬電量轉(zhuǎn)換成數(shù)字量輸出的接口電路-A/D轉(zhuǎn)換器是現(xiàn)實(shí)世界中模擬信號向數(shù)字信號的橋梁,是電子技術(shù)發(fā)展的關(guān)鍵和瓶所在。

當(dāng)前,為了適應(yīng)計(jì)算機(jī)、通訊和多媒體技術(shù)的飛速發(fā)展以及高新技術(shù)領(lǐng)域的數(shù)字化進(jìn)程不斷加快,ADC在工藝、結(jié)構(gòu)、性能上都有了很大的變化,正在朝著低功耗、高速、高分辨率的方向發(fā)展。

1 ADC的主要類型

目前,世界上有多種類型的ADC,有傳統(tǒng)的并行、逐次逼近型、積分型ADC,也有近年來新發(fā)展起來的∑-Δ型和流水線型ADC,多種類型的ADC各有其優(yōu)缺點(diǎn)并能滿足不同的具體應(yīng)用要求。低功耗、高速、高分辨率是新型的ADC的發(fā)展方向,同時(shí)ADC的這一發(fā)展方向?qū)⑦m應(yīng)現(xiàn)代數(shù)字電子技術(shù)的發(fā)展。

任何ADC都包括三個(gè)基本功能:抽樣、量化和編碼。抽樣過程將模擬信號在時(shí)間上離散化,使之成為抽樣信號;量化將抽樣信號的幅度離散化使之成為數(shù)字信號;編碼則將數(shù)字信號最彈簧表示成數(shù)字系統(tǒng)所能接受的形式。如何實(shí)現(xiàn)這三個(gè)功能就決定了ADC的形式和性能。同時(shí),ADC的分辨率越高,需要的轉(zhuǎn)換時(shí)間就越長,轉(zhuǎn)換速度就越低,故ADC的分辨率和轉(zhuǎn)換速率兩者總是相互制約的。因而在發(fā)展高分辨率ADC的同時(shí)要兼顧高速,在發(fā)展高速ADC的同時(shí)要兼顧高分辨率,在此基礎(chǔ)上還要考慮功耗、體積、便捷性、多功能、與計(jì)算機(jī)及通訊網(wǎng)絡(luò)的兼容性以及應(yīng)用領(lǐng)域的特殊要求等問題,這樣也使得ADC的結(jié)構(gòu)和分類錯(cuò)綜復(fù)雜。目前, ADC集成電路主要有以下幾種類型。???

1.1 并行比較ADC

并行比較ADC是現(xiàn)今速度最快的模/數(shù)轉(zhuǎn)換器,采樣速率在1GSPS以上,通常稱為“閃爍式”ADC。它由電阻分壓器、比較器、緩沖器及編碼器四種分組成。這種結(jié)構(gòu)的ADC所有位的轉(zhuǎn)換同時(shí)完成,其轉(zhuǎn)換時(shí)間主取決于比較器的開關(guān)速度、編碼器的傳輸時(shí)間延遲等。增加輸出代碼對轉(zhuǎn)換時(shí)

間的影響較小,但隨著分辨率的提高,需要高密度的模擬設(shè)計(jì)以實(shí)現(xiàn)轉(zhuǎn)換所必需的數(shù)量很大的精密分壓電阻和比較器電路。輸出數(shù)字增加一位,精密電阻數(shù)量就要增加一倍,比較器也近似增加一倍。例如,n位的ADC需要2n個(gè)精密電阻和2(n-1)個(gè)并聯(lián)比較器。分壓電阻網(wǎng)絡(luò)彼此相差1個(gè)最低有效位VR/2n,如圖1所示。?

?  ?

?

閃爍式ADC的分辨率受管芯尺寸、過大的輸入電容、大量比較器所產(chǎn)生的功率消耗等限制。結(jié)果重復(fù)的并聯(lián)比較器如果精度不匹配,還會(huì)造成靜態(tài)誤差,如會(huì)使輸入失調(diào)電壓增大。同,這一類型的ADC由于比較器的亞穩(wěn)壓、編碼氣泡,還會(huì)產(chǎn)生離散的、不精確的輸出,即所謂的“火花碼”。這類ADC的優(yōu)點(diǎn)是模/數(shù)轉(zhuǎn)換速度最高,缺點(diǎn)是分辨率不高,功耗大,成本高。

現(xiàn)代發(fā)展的高速 ADC電路結(jié)構(gòu)主要采用這種全并行的ADC,但由于功率和體積的限制,要制造高分辨率閃爍式ADC是不現(xiàn)實(shí)的。由兩個(gè)較低分辨率的閃爍式ADC構(gòu)成較高分辨率的半閃爍式ADC或分級型ADC是當(dāng)今世界制造高速ADC的主要方式。圖2所示是一個(gè)8位的兩級并行半閃爍式ADC的原理框圖。其轉(zhuǎn)換過程分為兩步:第一步是粗化量化。先用并行方式進(jìn)行高4位的轉(zhuǎn)換,作為轉(zhuǎn)換后的高4位輸出,同時(shí)再把數(shù)字輸出進(jìn)行D/A轉(zhuǎn)換,恢復(fù)成模擬電壓。第二步是進(jìn)一步細(xì)化量化。把原輸入電壓與D/A 轉(zhuǎn)換器輸出的模擬電壓相減,其差值再進(jìn)行低4全的A/D轉(zhuǎn)換。然后將上述兩級A/D轉(zhuǎn)換器的數(shù)字輸出并聯(lián)后作為總的輸出。這樣,在轉(zhuǎn)換速度上作出了一點(diǎn)犧牲,但解決了分辨率提高和元件數(shù)目刷增的矛盾。現(xiàn)代高速ADC與普通ADC相比的主要特點(diǎn)是:單電源性能;將基準(zhǔn)電源、采樣保持器和增益放大器集成在一塊芯片上,集成度高;采用標(biāo)準(zhǔn)的0.6μm的CMOS工藝開發(fā)各種價(jià)格的低功耗ADC。??

?  ?

?

1.2 逐次逼近型

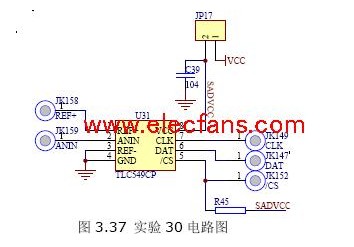

逐次逼近型ADC是應(yīng)用非常廣泛的模/數(shù)轉(zhuǎn)換方法,它由比較器、D/A轉(zhuǎn)換器、比較寄存器SAR、時(shí)鐘發(fā)生器以及控制邏輯電路組成,將采樣輸入信號與已知電壓不斷進(jìn)行比較,然后轉(zhuǎn)換成二進(jìn)制數(shù)。其原理圖如圖3所示,首先將DAC的最高有效位MSB保存到SAR,接著將該值對應(yīng)的電壓與輸入電壓進(jìn)行比較。比較器輸出被反饋到DAC,并在一次比較前對其進(jìn)行修正。在邏輯控制電路和時(shí)鐘驅(qū)動(dòng)下,SAR不斷進(jìn)行比較和移位操作,直到完成LSB的轉(zhuǎn)換,此時(shí)所產(chǎn)生的 DAC輸出逼近輸入電壓的±1/2LSB。當(dāng)每一位都確定后,轉(zhuǎn)換結(jié)果被鎖存到SAR并作為ADC輸出。這一類型ADC的優(yōu)點(diǎn):高速,采樣速率可達(dá) 1MSPS;與其它ADC相比,功耗相當(dāng)?shù)停辉诜直媛实陀?2位時(shí),價(jià)格較低。缺點(diǎn):在高于14位分辨率情況下,價(jià)格較高;傳感器產(chǎn)生的信號在進(jìn)行模/數(shù)轉(zhuǎn)換之前需要進(jìn)行調(diào)理,包括增益級和濾波,這樣會(huì)明顯增加成本。

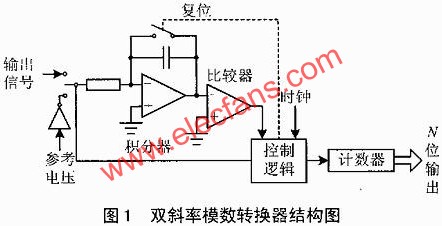

1.3 積分型ADC

積分型ADC又稱為雙斜率或多斜率ADC,是應(yīng)用比較廣泛的一類轉(zhuǎn)換器。它的基本原理是通過兩次積分將輸入的模擬電壓轉(zhuǎn)換成與其平均值成正比的時(shí)間間隔。與此同時(shí),在此時(shí)間間隔內(nèi)利用計(jì)數(shù)器對時(shí)鐘脈沖進(jìn)行計(jì)數(shù),從而實(shí)現(xiàn)A/D轉(zhuǎn)換。其原理圖如圖4所示。其工作分為兩個(gè)階段,第一階段為采樣期;第二階段為比較期。通過兩次積分和計(jì)數(shù)器的計(jì)數(shù)可以得到模擬信號的數(shù)字值D=2nV1/VR,其中n為計(jì)數(shù)器的位數(shù),V1為輸入電壓在固定時(shí)間間隔內(nèi)的平均值。

積分型ADC兩次積分的時(shí)間都是利用同一個(gè)時(shí)鐘發(fā)生器和計(jì)數(shù)器來確定,因此所得到的D表達(dá)式與時(shí)鐘頻率無關(guān),其轉(zhuǎn)換精度只取決于參考電壓VR。此外,由于輸入端采用了積分器,所以對交流噪聲的干擾有很強(qiáng)的抑制能力。若把積分器定時(shí)積分的時(shí)間取為工頻信號的整數(shù)倍,可把由工頻噪聲引起的誤差減小到最小,從而有效地抑制電網(wǎng)的工頻干擾。這類ADC主要應(yīng)用于低速、精密測量等領(lǐng)域,如數(shù)字電壓表。其優(yōu)點(diǎn)是:分辨率高,可達(dá)22位;功耗低、成本低。缺點(diǎn)是:轉(zhuǎn)換速率低,轉(zhuǎn)換速率在12位時(shí)為100~300SPS。???

1.4 壓頻變換型ADC

前面所講到的并行比較ADC和逐次逼近型ADC均屬于直接轉(zhuǎn)換ADC,而積分型和下面所講到的壓頻變換型ADC則屬于間接ADC。壓頻變換型ADC是先將輸入模擬信號的電壓轉(zhuǎn)換成頻率與其成正比的脈沖信號,然后在固定的時(shí)間間隔內(nèi)對此脈沖信號進(jìn)行計(jì)數(shù),計(jì)數(shù)結(jié)果即為正比于輸入模擬電壓信號的數(shù)字量。從理論上講,這種ADC的分辨率可以無限增加,只要采用時(shí)間長到滿足輸出頻率分辨率要求的累積脈沖個(gè)數(shù)的寬度即可。其優(yōu)點(diǎn)是:精度高、價(jià)格較低、功耗較低。缺點(diǎn)是:類似于積分型ADC,其轉(zhuǎn)換速率受到限制,12位時(shí)為100~300SPS。

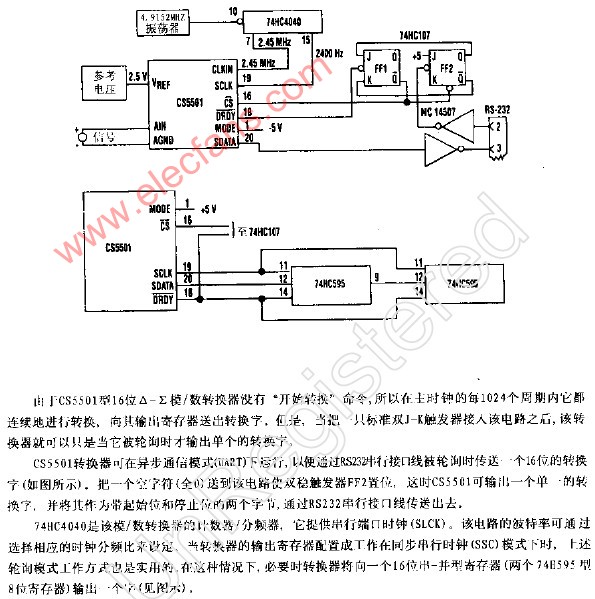

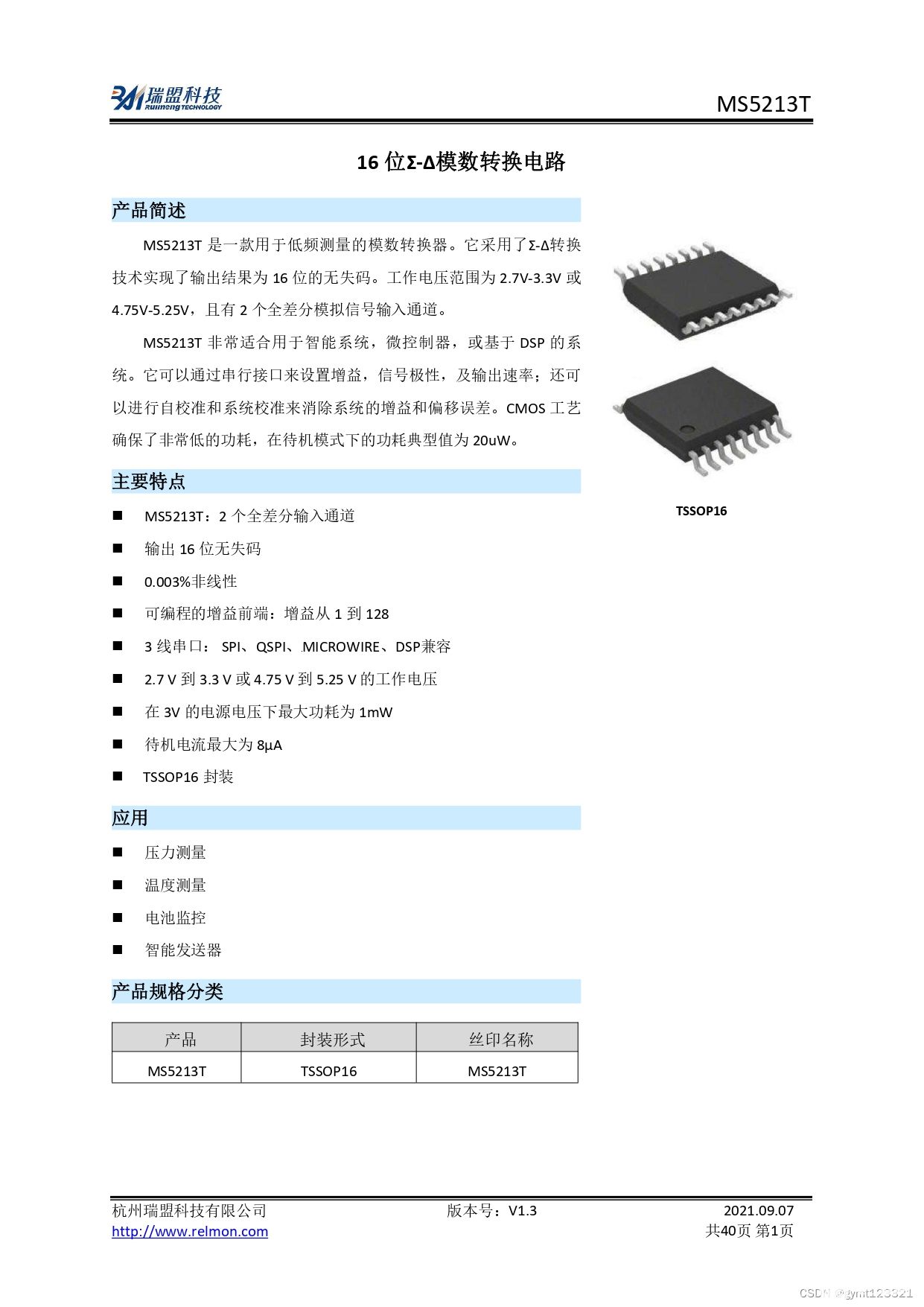

1.5 ∑-Δ型ADC

與一般的ADC不同,∑-Δ型ADC不是直接根據(jù)抽樣第一個(gè)樣值的大小進(jìn)行量化編碼,而根據(jù)前一量值與后一量值的差值即所謂的增量的大小來進(jìn)行量化編碼。從某種意義講,它是根據(jù)信號波形的包絡(luò)線進(jìn)行量化編碼的。∑-Δ型ADC由兩部分組成,第一部分為模擬∑-Δ調(diào)制器,第二部分為數(shù)字抽取濾波器,如圖5所示。∑-Δ調(diào)制器以極高的抽樣頻率對輸入模擬信號進(jìn)行抽樣,并對兩個(gè)抽樣之間的差值進(jìn)行低位量化,從而得到用低位數(shù)碼表示的數(shù)字信號即∑-Δ碼;然后將這種∑-Δ碼送給第二部分的數(shù)字抽取濾波器進(jìn)行抽取濾波,從而得到高分辨率的線性脈沖編碼調(diào)制的數(shù)字信號。因此抽取濾波器實(shí)際上相當(dāng)于一個(gè)碼型變換器。由于∑--△具有極高的抽樣速率,通常比奈奎斯特抽樣頻率高出許多倍,因此∑--△轉(zhuǎn)換器又稱為過抽樣A/D轉(zhuǎn)換器。這種類型的ADC采用了極低位的量化器,從而避免了制造高位轉(zhuǎn)換器和高精度電阻網(wǎng)絡(luò)的困難;另一方面,因?yàn)樗捎昧恕?-△調(diào)制技術(shù)和數(shù)字抽取濾波,可以獲得極高的分辨率;同時(shí)由于采用了低位量化輸出的采用高分辨率的碼,不會(huì)對抽樣值幅度變化敏感,而且由于碼位低,抽樣與量化編碼可以同時(shí)完成,幾乎不花時(shí)間,因此不需要采樣保持電路,這就使得采樣系統(tǒng)的構(gòu)成大為簡化。這種增量調(diào)制型ADC實(shí)際上是以高速抽樣率來換取高位量化,即以速度來換精度。近年來,采用高分辨率的∑--△型ADC頗為流行,它的一個(gè)突出優(yōu)點(diǎn)是在一片混合信號CMOS大規(guī)模集成電路上實(shí)現(xiàn)了ADC與數(shù)字信號處理技術(shù)的結(jié)合。這一技術(shù)的其它優(yōu)點(diǎn):分辨率高達(dá)24位;比積分型及壓頻變換型ADC的轉(zhuǎn)換速率高;采用混合信號CMOS工藝,可實(shí)現(xiàn)低價(jià)格、高分辨率的數(shù)據(jù)采集和數(shù)字信號處理;由于采用高倍頻過采樣技術(shù),降低了對傳感器信號進(jìn)行濾波的要求,實(shí)際上取消了信號調(diào)理。缺點(diǎn):當(dāng)高速轉(zhuǎn)換時(shí),需要高階調(diào)制器;在轉(zhuǎn)換速率相同的條件下,比積分型和逐次逼近型ADC的功耗高。

目前,∑--△型ADC分為四類:

(1)高速類ADC;

(2)調(diào)制解調(diào)器類ADC;

(3)編碼器類ADC;

(4)傳感器低頻測量ADC。

其中每一類∑--△型ADC又分為許多型號,給用戶帶來極大方便。流水線型(Pipeline)ADC又稱為子區(qū)式ADC,它由若干級級聯(lián)電路組成,每一級包括一個(gè)采樣/保持放大器、一個(gè)低分辨率的ADC和DAC以及一個(gè)求和電路,其中求和電路還包括可提供增益的級間放大器。快速精確的n位轉(zhuǎn)換器分成兩段以上的子區(qū)(流水線)來完成。首級電路的采樣/保持器對輸入信號取樣后先由一個(gè)m位分辨率粗A/D轉(zhuǎn)換器對輸入進(jìn)行量化,接著用一個(gè)至少n位精度的乘積型數(shù)模轉(zhuǎn)換器(MDAC)產(chǎn)生一個(gè)對應(yīng)于量化結(jié)果的模/擬電平并送至求和電路,求和電路從輸入信號中扣除此模擬電平。并將差值精確放大某一固定增益后關(guān)交下一級電路處理。經(jīng)過各級這樣的處理后,最后由一個(gè)較高精度的K位細(xì) A/D轉(zhuǎn)換器對殘余信號進(jìn)行轉(zhuǎn)換。將上述各級粗、細(xì)A/D的輸出組合起來即構(gòu)成高精度的n位輸出。圖3所示為一個(gè)14位5級流水線型ADC的原理圖,圖7 所示為每級內(nèi)部結(jié)構(gòu)圖。

流水線型ADC必須滿足以下不等式以便糾正重疊錯(cuò)誤:式中,1為級數(shù),m為各級中ADC的粗分辨率,k為精細(xì)ADC的細(xì)分辨率,而 n是流水線ADC的總分辨率。流水線ADC不但簡化了電路設(shè)計(jì),還具有如下優(yōu)點(diǎn):每一級的冗余位優(yōu)化了重疊誤差的糾正,具有良好的線性和低失調(diào);每一級具有獨(dú)立的采樣/保持放大器,前一級電路的采樣/保持可以釋放出來用于處理下一次采樣,因此允許流水線各級同時(shí)對多個(gè)采樣進(jìn)行處理,從而提高了信號的處理速度,典型的為 Tconv<100ns;功率消耗低;很水有比較器進(jìn)入亞穩(wěn)態(tài),從根本上消除了火花碼和氣泡,從而大大減少了ADC的誤差;多級轉(zhuǎn)換提高了ADC的分辨率。同時(shí)流水線型ADC也有一些缺點(diǎn):復(fù)雜的基準(zhǔn)電路和偏置結(jié)構(gòu);輸入信號必須穿過數(shù)級電路造成流水延遲;、同步所有輸出需要嚴(yán)格的鎖存定時(shí);對工藝缺陷敏感,對印刷線路板更為敏感,它們會(huì)影響增益的線性、失調(diào)及其它參數(shù)。

目前,這種新型的ADC結(jié)構(gòu)主要應(yīng)用于對THD和SFDR及其它頻域特性要求較高的通訊系統(tǒng),對噪聲、帶寬和瞬態(tài)相應(yīng)速度等時(shí)域特性要求較高的CCD成像系統(tǒng),對時(shí)域和頻域參數(shù)都要求較高的數(shù)據(jù)采集系統(tǒng)。隨著數(shù)字技術(shù)的發(fā)展,AD也有了長足的進(jìn)步和發(fā)ADC正朝著低功耗高速、高分辨率的方向發(fā)展,在此基礎(chǔ)上,還要考慮功耗、體積、便捷多功能、與計(jì)算機(jī)及通信網(wǎng)絡(luò)的兼容性。ADC主要的應(yīng)用領(lǐng)域不斷拓寬,廣泛應(yīng)用于多媒體、通訊、自動(dòng)化、儀器儀表等領(lǐng)域。對不同領(lǐng)域的不同要求,例如接口、電源、通道、內(nèi)部配置的要求,每一類ADC都有相應(yīng)的優(yōu)化設(shè)計(jì)方法。同時(shí),用戶不僅要考慮到ADC本身的工藝和電路結(jié)構(gòu),而且還應(yīng)考慮到ADC的外圍電路,如相應(yīng)的信號調(diào)理電路等模擬電路的設(shè)計(jì)。如在單電源、低功耗條件下設(shè)計(jì)新型的ADC時(shí),為了解決單電源的輸入和輸出的動(dòng)態(tài)范圍問題,可以采用超高速補(bǔ)償雙極性(XFCB)工藝制造的電流反饋運(yùn)算放大器;為了解決推薦電壓、低電流條件下的低噪聲低溫漂基準(zhǔn)電壓問題,可以采用外加離子注入場效應(yīng)管(XFET)基準(zhǔn)源的方法;為了滿足低功耗的要求,可以采用節(jié)能工作方式(Power Down);為設(shè)計(jì)出微型ADC,可采用減小體積的2線或2線制兼容的串行接口;為了減小信號源到整個(gè)AD轉(zhuǎn)換器的模擬信號通路的誤差,可以采用自校準(zhǔn)技術(shù)糾正誤差等等。針對實(shí)際應(yīng)用中具體要求,各種新型的設(shè)計(jì)方案應(yīng)運(yùn)而生。這些技術(shù)不斷完善和改進(jìn)現(xiàn)有ADC的速度和精度,同時(shí)也成為現(xiàn)代ADC新補(bǔ)充的特點(diǎn)和發(fā)展方向。????

? ?

?

傳統(tǒng)方式的ADC,例如逐次逼近型、積分型、壓頻變換型等,主要應(yīng)用于中速或較低速、中等精度的數(shù)據(jù)采集和智能儀器中。在全并行基礎(chǔ)上發(fā)展起來的分級型和流水線型ADC主要應(yīng)用于高速情況下的瞬態(tài)信號處理、快速波形存儲(chǔ)與記錄、高速數(shù)據(jù)采集、視頻信號量化及高速數(shù)字通訊技術(shù)等領(lǐng)域。此外,采用脈動(dòng)型和折疊型等結(jié)構(gòu)的高速ADC,可應(yīng)用于廣播衛(wèi)星中的基帶解等方面。這些高速ADC,今后的展方向是在現(xiàn)有高速基礎(chǔ)上盡可能提高其分辨率,以滿足兼顧高速、高精度的發(fā)展方向。20世紀(jì)90年代以來獲得很大發(fā)展的∑-Δ型ADC利用高抽樣率和數(shù)字信號處理技術(shù),將抽樣、量化、數(shù)字信號處理融為了一體,從而獲得了高精度的ADC,目前可達(dá)24位,主應(yīng)用于高精度數(shù)據(jù)采集特別是數(shù)字音響系統(tǒng)、多媒體、地震勘探儀器、聲納等電子測量領(lǐng)域。???

自電子管A/D轉(zhuǎn)換器面世以來,經(jīng)歷了分立半導(dǎo)體、集成電路數(shù)據(jù)轉(zhuǎn)換器的發(fā)展歷程。在集成技術(shù)中,又發(fā)展了模塊、混合和單片機(jī)集成數(shù)據(jù)轉(zhuǎn)換器技術(shù)。在這一歷程中,工藝制作技術(shù)都得到了很大改進(jìn)。單片集成電路的工藝技術(shù)主要有雙極工藝、CMOS工藝以及雙極和CMOS相結(jié)合的BiCMOS工藝。模塊、混合和單片集成轉(zhuǎn)換器齊頭發(fā)展,互相發(fā)揮優(yōu)勢,互相彌補(bǔ)不足,開發(fā)了適用不同應(yīng)用要求的A/D和D/A轉(zhuǎn)換器。近年來轉(zhuǎn)換器產(chǎn)品已達(dá)數(shù)千種。

A/D和D/A轉(zhuǎn)換器的主要發(fā)展趨勢是,單片集成以硅為主導(dǎo)發(fā)展技術(shù),并加速以硅為基礎(chǔ)的異質(zhì)結(jié)技術(shù)的發(fā)展;混合和模塊集成A/D和D/A轉(zhuǎn)換器是軍事/航天系統(tǒng)的主導(dǎo)產(chǎn)品,將與硅芯片技術(shù)并行發(fā)展,而且需建立在先進(jìn)的芯片技術(shù)基礎(chǔ)之上;低電源、低功耗、高速、高精度A/D和D/A轉(zhuǎn)換器是主導(dǎo)發(fā)展產(chǎn)品,其中16位100~200MHz及8~10位10GHz的高性能 A/D轉(zhuǎn)換器是新一代先進(jìn)雷達(dá)、電子占和通訊電子系統(tǒng)的關(guān)鍵器件之一,它們是重點(diǎn)發(fā)展目標(biāo);目前已有工藝技術(shù)能滿足目標(biāo)產(chǎn)品的制作,如III/V化合物半導(dǎo)體異質(zhì)結(jié)技術(shù)℃,其日體管的ft已大于50GHz;工藝技術(shù)中,雙極(特別是異質(zhì)結(jié)雙極)、CMOS、BiCMOS將并行發(fā)展,加工尺寸已發(fā)展到半亞微米亞料微米,將繼續(xù)向深度發(fā)展。近年來,A/D和D/A轉(zhuǎn)換器的市場呈穩(wěn)步增長的發(fā)展趨勢,它們在現(xiàn)代軍用和民用電子系統(tǒng)中均顯示出其重要地。2000年的市場銷售額已達(dá)20.3億美元。??

不論是傳統(tǒng)型ADC還是表發(fā)展起來的ADC都有各自的優(yōu)缺點(diǎn)和適應(yīng)場合。在選用ADC時(shí),不僅要考慮應(yīng)用的精度、速度等主要指標(biāo),還要考慮輸入信號的形式(單端或差動(dòng)輸入)、輸入信號范圍、輸入通道類型和數(shù)量、工作電源、內(nèi)部基準(zhǔn)、激勵(lì)源等多種具體功能上的差異,這些在選型上都是認(rèn)真考慮的。現(xiàn)代ADC制造商為用戶應(yīng)用考慮的越來越多,用戶在方案設(shè)計(jì)時(shí)一定要在器件選型上下一些功夫,針對實(shí)際應(yīng)用的具體要求盡量做到選型合理,這樣往往可以簡化設(shè)計(jì)、降低成本、提高性價(jià)比。

電子發(fā)燒友App

電子發(fā)燒友App

評論