多媒體處理,特別是視頻和音頻編解碼以及數碼照相機已經成為手機的常見功能。然而,正當手機對功能需求日益增長的時候,手機生產廠商和OEM設備制造商卻面臨著不斷減少器件數量和降低物料(BOM)成本同時滿足嚴格低功耗要求的壓力。他們必須解決這些問題,同時支持在多種網絡上運行的各種通信標準。

傳統手機芯片組是以DBB(數字基帶)芯片為中心,通常包含微控制器(MCU)和數字信號處理器(DSP)。在多媒體功能應用在手機之前,MCU的基本作用是完成以下兩個主要功能:一個是運行通信協議物理層的控制碼(也稱為第1層);另一個是控制通信協議棧的上層軟件(第2或第3層),包括表示層或人機界面(MMI)。DSP的基本作用是完成物理層大量的數學計算功能,包括信道均衡、信道編解碼以及電話語音編解碼。

隨著多媒體功能的日益增加,增加手機功能的方法之一是提高DBB中的集成度。新一代基帶處理器是一種高度復雜的系統芯片(SoC),它不僅支持幾種通信標準,而且提供多媒體功能以及用于多媒體顯示器、圖像傳感器和音頻設備相關的接口。 完全可編程的軟件定義無線電(SDR)對手機設計工程師來說非常有吸引力。SDR的最終目標是使無線手機能夠支持多種手持設備功能(例如,電話、個人數字助理、智能手機和許多其他設備),并且實時改變個性化無線電通信,同時確保服務質量(QoS)。有人認為大范圍推廣軟件無線電所面臨的所有因素對于手機都很關鍵:多功能(相同設備上增加其他服務)、全球移動性、小封裝和低功耗、容易生產以及容易升級。

新一代手機對SDR的需求更加明顯,要求支持三套不同的標準:無線標準、多媒體標準和連接標準。例如,GSM和GPRS通信模塊必須與FDD WCDMA調制解調模塊共存在一部多模手機上,手機還也必須能夠實現MPEG4視頻編解碼和MP3編解碼,還要支持IEEE 802.11無線局域網和藍牙標準。AD6900 DBB是一種支持未來SDR多標準和多媒體手機終端的平臺,可滿足新一代手機對各種功能的要求。

AD6900系統結構

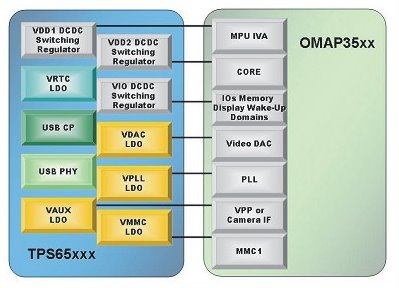

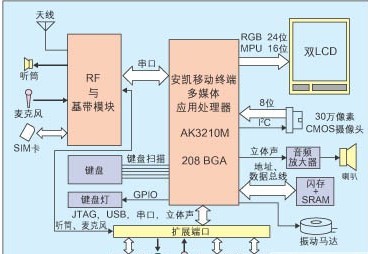

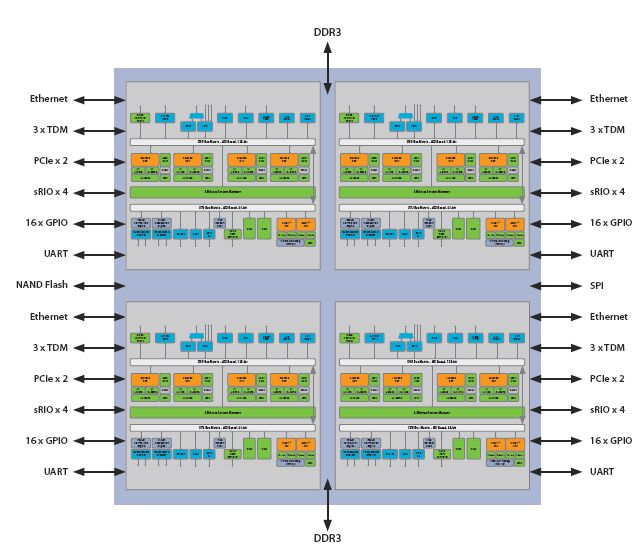

AD6900是低功耗無線數字基帶芯片,高級電源管理系統滿足了GSM、GPRS和EDGE終端的嚴格要求,還支持對計算量要求很大的多媒體功能。AD6900集成了Blackfin DSP處理器、ARM926EJ-S處理器、片內大容量RAM,以及外設擴展接口。AD6900包含支持專用數碼相機、USB OTG、多媒體卡(MMC)、SD卡、IrDA紅外端口、拇指輪、彩色顯示器以及串行接口設備(例如藍牙、WiLAN和A-GPS模塊)的集成接口,結構框圖如圖1所示。

圖1 AD6900結構框圖

圖1中的右上方是Blackfin處理器子系統,它由Blackfin處理器內核、L1代碼存儲器和數據存儲器(可配置為高速緩存或SRAM)、統一的L2存儲器、DSPDMA作為Blackfin DMA控制器,以及用于采集和處理GSM數據的DSP外設。Blackfin處理器子系統與系統總線接口單元(SBIU)交叉開關相連接。 圖1右下方是ARM926-S微控制器子系統,它由ARM微控制器內核、高速緩存和緊密耦合內存(TCM)組成。系統中第三片片內內存稱為系統RAM(L3存儲器),Blackfin處理器和ARM微控制器都可訪問它。連接外部設備的通用外設部分稱為外設總線(PBUS),它主要用于控制大多數外部設備,模擬基帶(ABB)處理器和RF收發系統。

多媒體連接功能,即用于顯示器和捕獲設備的接口,由專用APBUS子系統支持。它由并行外圍接口(PPI)控制器(支持10bit數碼相機傳感器或視頻輸入接口(包括ITU-656和ITU-601數字視頻))和專用外部總線接口(支持并行液晶顯示器,稱為EBUS2)組成,消除了主要外部存儲器接口中的噪聲和負載。多媒體接口設備的數據搬移由稱作APPDMA的多通道DMA控制器支持,它支持包括YUV4:2:2、YUV4:2:0和RGB565等其他格式的視頻格式。

AD6900是基于分級存儲器系統。從Blackfin處理器角度來看,L1緩存器提供有限容量的快速零等待存儲能力。由于Blackfin處理器的時鐘頻率很高,所以L1存儲器也十分昂貴,采用小容量的快速存儲器才是經濟上切實可行的方案。較低級別的存儲器可提供較大的儲存容量,但需要更長的訪問時間。對ARM處理器來說也是一樣,在處理器中具有容量相當小的快速L1高速緩存存儲器。

存儲器系統由以下幾部分組成。

L1 DSP存儲器:DSP內核工作在260MHz頻率時的高速緩存和SRAM,包括80KB指令存儲器和32KB數據存儲器。

L1 ARM存儲器:ARM內核工作在260MHz頻率時的高速緩存和SRAM,包括20KB指令存儲器和16KB數據存儲器。

L2 存儲器:以一半的DSP內核頻率(130MHz)工作的64KB流水線SRAM,主要用來存儲DSP數據和指令。

L3存儲器:以幾分之一DSP內核頻率工作的256KB存儲器,也稱作系統RAM。

L4存儲器:大容量片外存儲器,包括SRAM、PSRAM(蜂窩RAM)、SDRAM、NOR以及NAND閃存。

AD6900的視頻編解碼 AD6900系統的對稱性允許DSP和ARM內核都能夠訪問外圍設備和存儲器,在實現視頻、音頻和語音編解碼時具有很大的靈活性。手機制造商可能只選擇其中一個內核來實現編解碼,這取決于系統的不同要求,例如指令執行性能、代碼可用性和負載平衡。通常,由于DSP優化了數據路徑并且具有數字計算能力,所以用DSP實現視頻和音頻編解碼比用ARM內核實現具有更好的性能。在某些情況下,系統設計工程師可能希望使用ARM內核完成這項工作,這時代碼在ARM內核中運行,或是在要求平衡DSP和ARM工作負載的計算中使用ARM內核。為了將多媒體系統和通信模塊集成在同一DBB中,多媒體系統必須具有另一個功能,即從L1指令和數據高速緩存中執行程序。視頻和音頻編解碼占用盡可能少的DMA和系統資源是非常重要的,這樣可以避免引起對通信模塊的意外影響。與以前基于DMA的舊方法相比,現代DBB中的軟件對高速緩存使用進行了擴展。

衡量視頻編解碼的復雜性 在無線DBB上支持視頻編解碼,會大大增加處理模塊的計算量。調制解調、語音和視頻模塊都是基于數據流的算法,也就是說它們處理輸入數據流并且產生輸出數據流。然而,通常視頻編解碼所處理的數據量(相對數據的計算量)要比語音編解碼或典型調制解調模塊的數據量大許多倍。以典型的電話語音編碼器為例,其處理160個16bit的采樣幀,產生80~130個輸出bit。通常,優化的AMR編碼器處理一幀的時間是250 000個處理器時鐘周期(用Blackfin處理器來度量)。因此,每個輸入語音采樣大約需要1500個DSP處理器時鐘周期,或者每個輸入數據字節需要750個時鐘周期。用類似的方法,EDGE均衡器的主要組件可輸入122個16bit的采樣幀,通常用大約100 000個DSP時鐘周期完成數據處理,或者每個輸入字節400個時鐘周期。相反,以QCIF分辨率尺寸的視頻解碼器為例,其每幀具有25 344個像素,通常每幀執行1 000 000個DSP時鐘周期。這相當于每個輸出字節需要26個時鐘周期(假設采用YUV4:2:0視頻格式,每像素1.5字節編碼),這種視頻解碼器要求輸入的數據是EDGE數據均衡器的15倍多,并且幾乎是比語音編解碼器多6倍的數據。這意味著實現視頻編解碼器的主要難題與系統中需要輸入的大量數據的數量有關。每個數據的計算量比手機中任何其他算法低很多。為了支持這種大量數據移動的要求,AD6900具有專用子系統APBUS,以及用于PSRAM和SDRAM的快速外部存儲器接口。視頻編解碼器不僅需要非常寬的數據帶寬,而且還需要大容量的存儲器來存儲大量的圖像數據結構,這稱為幀緩存。在AD6900中,幀緩存可配置在外部的PSRAM或SDRAM存儲器中。

系統劃分 AD6900具有處理完成QVGA圖像格式視頻解碼和編碼能力。由于視頻編解碼需要相當大容量的存儲空間,所以將所有的存儲對象放在最佳的物理存儲器中對于編解碼器的性能是非常重要的,因為必須使數據流量要求與系統接口和總線之間的可用帶寬保持平衡。在很大程度上,視頻編解碼器的時鐘性能是由傳輸像素數據接口的速度決定的。如圖1所示,可用的物理存儲器是L1(DSP和ARM)、L2(DSP)、L3(系統RAM)和L4(片外存儲器,包括SRAM、PSRAM、SFDRAM和只讀存儲器)存儲器。AD6900最重要的系統接口是外部總線接口,也稱為EBUS。這是一個支持所有外部存儲器設備的接口。液晶顯示器是由稱為EBUS2的單獨外部接口支持,攝像頭是由專用的PPI接口支持,這兩個接口都屬于APPBUS。

視頻編解碼器需要的存儲器可以劃分為以下幾個分區:幀緩存器區、堆區、程序區、常量區和堆棧區。到目前為之,幀緩存器是最大的內存對象區,它能存儲編碼器和解碼器所需要的幀。視頻編解碼器基于以下兩個原則:幀內冗余和幀間冗余。幀間冗余僅使用幀N的不同部分像素來壓縮幀N。幀間冗余使用每幀內的像素而不是幀N中的部分像素來壓縮幀N,由于這個原因,視頻編解碼器需要過去(在某些情況下需要未來)幀的拷貝。MPEG4-SP簡單類解碼器在1/4VGA(QVGA)分辨率時需要兩個幀緩存器,每個幀緩存器容量為110KB,總共為220KB。堆區包含多種類型的臨時存儲器,容量為80KB,程序區大約是150KB,常量區是另外30KB,堆棧區大小是2KB。

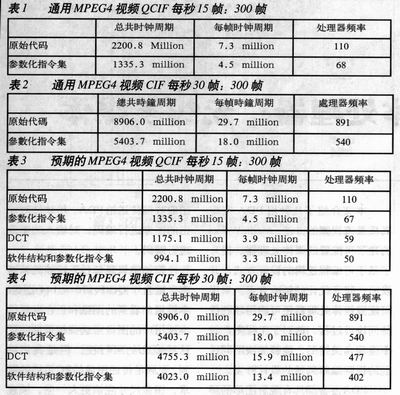

為了對視頻編解碼器內存儲對象的布置作出最佳選擇,也必須量化每個對象所需的數據帶寬。表1給出了每個對象所需要的數據流量。例如,在解碼器中幀緩存要求圖像數據的每個像素具有4.36字節,這轉換到QVGA分辨率的30 fps情況下大約是10MB/s,這大約是完整解碼器所要求的總帶寬的一半。堆區要求大約是6.7MB/s,或者是總帶寬的32%。

表1 MPEG4的內存對象和相對帶寬

幀緩存器所需要的給定帶寬及其大小都放在在AD6900的外部存儲器中(第四級),即PSRAM或SDRAM。SDRAM接口(圖1中的SDC)能夠達到130MB/s的最大吞吐量。在這種情況下幀緩存所需要的帶寬10MB/s正好在可接受的限制范圍內。可能的存儲器映射如表1所示,包括幀緩存器、所有片外存儲器的程序區和常量區以及系統RAM(第三級)中的堆區。

AD6900的視頻編解碼器支持MPEG4 simple profile Levels 0-3包括I-VOP和P-VOP幀格式、AC/DC系數預測、4-Motion向量、無限制向量移動以及短標頭模式。(MPEG4用語,VOP或稱為視頻對象平面是表示某一時刻采樣一幀圖像數據的單位。)為了最大程度提供集成靈活性和與其他DBB相連的代碼接口,AD6900的大多數代碼基(大約90%的代碼基)仍然使用C高級語言編寫,僅有很小部分(大約10%)的接口采用Blackfin專用匯編語言編寫。

另外也對MPEG4視頻編解碼器進行了優化,以便匹配現有總線和外部接口資源,并且也為了它們能產生盡可能少的數據流量。通過精心的管理數據移動,可使外部存儲器所需的帶寬減少30%。

多媒系統統除了支持編解碼所需要的存儲對象外,還需具有額外的幀緩存來支持輸出和輸入顯示設備(例如液晶顯示器和圖像傳感器模塊)。然而,在APPBUS系統中也支持輸入和輸出設備本身,每種設備都有一個專用的外部接口。在最終的分析中,還必須考慮EBUS中這些存儲器的大小和帶寬分配。

可變的處理時間以及輸出和輸入緩存 與視頻編解碼相關的一個特殊問題是編碼或解碼一幀所要求的處理時間并不是常量。也就是說,它是與場景內容(特別是場景的運動量)、比特率和特定編碼流結構或圖像組(GOP)大小有關的一種復雜函數。 圖2所示為例,示出了使用Blackfin DSP解碼MPEG4流時,解碼每幀所需要的時鐘周期數。本測試的輸入流采用CIF格式編碼,比特率為350b/s,幀率為10fps,GOP大小為10。參數GOP表示兩個I-VOP之間的P-VOP數量,因此在本例中每隔9個P-VOP就有一個I-VOP。圖2中的每個點表示解碼某幀所需的時鐘周期數。實線表示20個采樣值的移動平均數。從這幅圖中可以很清楚地看出,I-VOP比P-VOP需要大很多的處理能力,每十個幀點的趨勢明顯地表明大約有700萬~900萬個時鐘周期。P-VOP的處理時間最少為100萬個時鐘周期,最多高達1000萬個處理時鐘周期。

圖2 MPEG4解碼對時間的波動

每幀的時鐘周期平均數與場景中的運動量成比例。場景的初始部分(1~420幀)有相當低的運動,而中間部分(421~630幀)有高的運動量。在場景的最后一部分(1260到最終的幀)中,場景中有非常大的運動量。這也表明P-VOP所需要的處理時間與場景的運動量有關,而I-VOP所要求的處理時間與此關聯較小。 從這幅圖中可以看出,當設計播放器時,必須考慮可變的解碼時間。如果僅假設解碼器要求最差情況下的執行時間,這時大約是每幀1000萬個時鐘周期,則由于大多數幀不需要那么多的時鐘周期,過于保守的設計浪費了大量的DSP資源。 相反,現在是在解碼器的輸出端使用緩存來存儲幾個幀以為顯示做準備。這種輸出緩存系統能夠平滑解碼器執行時間的波動,所以允許設計師工程師按照平均執行時間來設計解碼器。

MPEG4的品質因數 用來加速視頻編解碼器的許多優化方案可能會對編碼器的數字性能引起負面影響。也就是說,使用太過分的措施減少編碼器時鐘周期數可能會引起由于峰值信噪比(PSNR)的減小而導致的編碼性能變差。下降的PSNR將減小編碼器壓縮視頻內容的能力,從而造成規定質量條件下輸出的比特率比預期的高。例如,使用運動估計的方法可以非常簡單或非常復雜,取決于所搜索的相鄰宏塊的數量。如果試圖減少計算量而搜索太少的宏塊數,則對于給定的壓縮比,PSNA值會變低。

圖3示出四種不同MPEG4編碼器相應的速率失真曲線,它們都工作在Simple Profile @ Level 2簡單類二級條件下。速率失真曲線是用來描述在給定某壓縮比(或比特率)條件下產生的噪聲(失真)進入視頻流的程度。隨著比特率下降,噪聲增加(PSNR降低)。被測編碼器是Blackfin AD6900編碼器、ISO/IEC的anci C參考編碼器、微軟的參考編碼器和xvid編碼器。所使用的采樣是稱作“Akiyo”的測試順序。性能較好的編碼器可能對任何給定的比特速率都有較高的PSNR值。這幅圖表明了Blackfin編碼器和其他的編碼器具有相同或者更好的性能。

圖3 Blackfin DSP MPEG4-SP編碼器的PSNR性能

AD6900的音頻編解碼 早期的多媒體手機幾乎完全依靠于多種電話語音編解碼來支持音頻。例如AMR的標準編解碼器用來輔助記錄和播放QCIF格式甚至更低的低分辨率運動剪輯。而且,AMR也是MMS標準的主要部分,它可提供多媒體信息通信功能。然而,目前全功能多媒體手機需要支持多種音頻編解碼標準,例如MP3、AAC、AAC-LC、HE-AAC(也稱為aac Plus)、RealAudio、WMA以及WB-AMR。 在AD6900中,MCU和DSP都能夠運行音頻編解碼,并且和視頻編解碼一樣,用哪一個處理器完成音頻編解碼取決于負載平衡、編解碼可用性以及其他考慮因素。一般地,用DSP實現音頻編解碼要比MCU執行速度快并且功耗低。 以HE-AAC為例。Blackfin處理器實現高質量(HQ)類需要40MIPS的速率,實現低功耗(LP)類需要25MIPS,兩種情況都采用立體聲。ARM9E實現LP類需要33MIPS的速率,或者大約30%以上的處理器資源。AAC-LC是一個以13.8MIPS速率運行并且需要非常低DSP負荷的音頻編解碼的例子。

Blackfin處理器為實現語音編解碼已做了高度優化。特別是NB-AMR語音編解碼器,代碼區大小為50KB,數據區大小為30KB,編碼速率要求8~16MIPS的,解碼速率為2MIPS。WB-AMR編解碼器,代碼區大小為50KB,數據區大小為25KB,編碼速率要求20~30MIPS的速率,解碼速率為6~8MIPS。 將音頻編解碼器集成到數字基帶中所面臨的難題遠不如上面所述的視頻編解碼器復雜。一般地,音頻編解碼器可能具有非常高的數據計算速率,因此不需要配置大量的外部總線接口和存儲器。音頻編解碼器所使用的數據對象也比較小。例如,HE-AAC的數據存儲器(音頻編碼標準中存儲器要求最大的一種)要求是70KB,而QVGA視頻編解碼器要求超過250KB。在AD6900中,通常將大多數音頻編解碼器的數據對象放置在外部存儲器上(例如,SDRAM或PSRAM),這樣就不會產生寬帶寬問題。

結束語 本文討論了系統設計工程師在使用無線數字基帶處理器AD6900實現軟件多媒體標準時所遇到的幾個難題及其解決方案。在給定的大動態無線環境中,無線手機不僅必須支持多種空中接口,而且也必須支持多種復雜的視頻和音頻標準,這種情況下,移動終端利用軟件可編程能力以保持高度靈活性是很關鍵的。

電子發燒友App

電子發燒友App

評論