引 言

目前,市場上有相當多的超外差式掃頻接收機采用模擬的掃描控制方式,利用掃描斜波電壓同步各掃描硬件單元,這種控制方式精度差,并且要求主控CPU實時干預掃描過程,使得接收機的掃描速度很慢。針對這些問題,本文提供了一種數字掃描控制器設計新方法。采用該方法,我單位在2005年成功開發了一種新型微波毫米波接收機,其掃描控制精度、掃描速度等指標較以前的接收機產品有了很大的提高。

1 掃描控制變量

超外差式掃頻接收機在掃描過程中一般需要控制的變量有:YIG振蕩器頻率(或VCO頻率)、YIG濾波器中心頻率(或帶通濾波器頻率)、與測試頻率相關的功率補償數據(如平坦度補償數據)等。

理想的YIG器件調諧曲線是一條直線(調諧曲線是根據諧振頻率變化與線包電流變化繪制的曲線),但是,由于受磁性材料磁特性的影響,實際的調諧曲線是非線性的。與此類似,由于接收機內各部件(如混頻器、濾波器等)幅度一頻率響應曲線是非線性的,造成整機幅頻曲線也是非線性的。

在工程上,通常采用多段直線逼近的方法對上述曲線進行線性化處理,就是將各控制量曲線進行分段,在段內認為控制量曲線是一條直線。只要各線段分段點位置選取合適,可以保證整機指標滿足設計要求。

通過計算各段控制量的起始值、步進值與步進個數(終止值減去起始值再除以步進量)就可以表征本段的控制量曲線。超外差式掃頻接收機包含多種控制變量,因此對每種控制變量都需要計算其控制量的起始值、步進值與步進個數。又由于各控制量曲線不盡相同,所用逼近曲線的直線段數目也就不盡相同。劃分的線段越多,逼近效果越好,控制精度也就越高。因此,在進行掃描控制之前,計算機主控的程序應該首先確定各控制量的分段數目和各段內的起始值、步進值、步進個數,這也就是送給掃描控制器的輸入參數。另外,為了提高控制速度,避免在掃描過程中CPU干預掃描進程,在各控制量換段時要求設計的掃描控制器能夠根據控制進度主動地讀取下一段的換段信息。下面,我們詳細介紹一下數字掃描控制器內各單元的組成及實現。

2 組成框圖及控制時序

如圖1所示,掃描控制器包括:地址譯碼/數據緩存單元、RAM存儲單元、運算單元、觸發單元、中斷處理單元、步進脈沖發生單元和D/A輸出單元。

?

掃描控制基本流程如下:

1)程序首先計算各控制量的分段數目及段內各控制量的起始值、步進值、步進個數。

2)通過系統總線,程序將上述計算好的數據依次送入掃描控制器內的RAM中保存。

3)程序控制觸發單元產生全局中斷信號,由中斷處理單元通知運算單元讀取各控制量首段的初始值。

4)程序控制觸發單元產生使能信號,控制步進脈沖發生單元產生計數脈沖。這時運算單元開始進行累加/減計算并且計數器記錄已產生的脈沖個數。累加/減運算器的輸出值通過D/A變換器轉換為電壓值控制相關硬件電路。

5)當運算單元內計數器的計數值達到本段設定的步進個數時,運算單元產生中斷信號通過中斷處理單元進行中斷識別并通知運算單元內已產生中斷的模塊自動從RAM內讀取下一段的初始值。運算單元內四個模塊產生中斷的中斷級別各不相同,如果多個中斷同時產生,那么中斷處理單元會對各中斷進行緩存、排序并且首先處理中斷級別高的中斷。

6)當下一個計數脈沖到來時,運算單元內產生中斷的模塊又會重新開始累加/減運算并計數,重復4、5步。

7)觸發單元記錄掃描時間。當掃描時間達到預設值時,觸發單元控制使能信號為低電平,各寄存器復位,掃描過程結束。

3 模塊內部實現

1)地址譯碼/數據緩存單元地址譯碼/數據緩存單元連接外部總線,通過譯碼接收屬于本掃描控制器的數據和控制字,包括:復位控制字、掃描使能控制字、觸發單元內計數器的計數值(用于計算掃描時間)、步進脈沖發生單元內計數器的計數值(用于產生步進脈沖)以及RAM內需存儲的控制量DAC值。

2)RAM存儲單元

存儲控制量DAC值。如果接收機內地址資源足夠豐富,軟件可以通過地址譯碼/數據緩存單元直接訪問RAM。如果接收機內地址資源有限,可以將整個RAM劃分為若干個區域(段地址),每個區域對應于一種控制量。每種控制量的各分段數據依次排列,可通過段內偏移地址訪問。

3)運算單元

運算單元包括RAM數據回讀模塊、計數器及累加/減運算器模塊。RAM數據回讀模塊的回讀方式取決與RAM內數據的存儲格式;計數器通過將讀取的步進個數值與當前的計數值進行比較決定是否產生中斷。在實際應用中,累加/減運算器位數有限,而計算的步進DAC值位數有可能大大超過運算器位數,這就要求設計人員必須認真選取步進DAC的有效長度,對DAC值進行適當截取,使控制誤差能夠在可接受的范圍內。累加/減運算器模塊在步進脈沖的觸發下,對初始值進行累加/減運算,其DAC值輸出位數等于選甩的DAC器件位數。

4)D/A輸出單元

D/A輸出單元負責將已累加/減數據轉換為模擬信號輸出。D/A輸出單元時序同步于控制脈沖。如果掃描控制器硬件資源不多,可以給每一個控制量單獨配置一個D/A轉換器;否則,可以將這些控制量先緩存起來再通過一個D/A轉換器輸出以減少硬件成本。

5)觸發單元

觸發單元接收到掃描使能控制字后控制步進脈沖發生單元使能端有效,步進脈沖發生單元開始工作,進而使得整個掃描控制器運轉起來。當觸發單元內計數器的計數值與接收到的用于計算掃描時間的計數量相同時表明掃描過程已經完成,這時觸發單元控制步進脈沖發生單元使能端失效,步進脈沖發生單元停止工作,掃描過程結束。另外,在掃描開始前觸發單元接收控制字產生全局中斷信號,通過中斷處理單元通知運算單元調用各硬件控制量的初始DAC值。

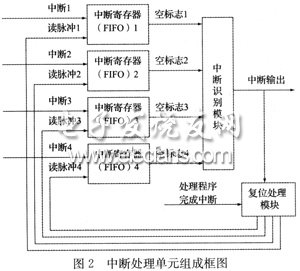

6)中斷處理單元

中斷處理單元根據預先設定的中斷優先級別決定控制運算單元內各模塊的先后順序。中斷處理單元由中斷寄存器、中斷識別模塊、復位處理模塊三部分組成。組成框圖見圖2所示。

?

掃描控制基本流程如下:

1)程序首先計算各控制量的分段數目及段內各控制量的起始值、步進值、步進個數。

2)通過系統總線,程序將上述計算好的數據依次送入掃描控制器內的RAM中保存。

3)程序控制觸發單元產生全局中斷信號,由中斷處理單元通知運算單元讀取各控制量首段的初始值。

4)程序控制觸發單元產生使能信號,控制步進脈沖發生單元產生計數脈沖。這時運算單元開始進行累加/減計算并且計數器記錄已產生的脈沖個數。累加/減運算器的輸出值通過D/A變換器轉換為電壓值控制相關硬件電路。

5)當運算單元內計數器的計數值達到本段設定的步進個數時,運算單元產生中斷信號通過中斷處理單元進行中斷識別并通知運算單元內已產生中斷的模塊自動從RAM內讀取下一段的初始值。運算單元內四個模塊產生中斷的中斷級別各不相同,如果多個中斷同時產生,那么中斷處理單元會對各中斷進行緩存、排序并且首先處理中斷級別高的中斷。

6)當下一個計數脈沖到來時,運算單元內產生中斷的模塊又會重新開始累加/減運算并計數,重復4、5步。

7)觸發單元記錄掃描時間。當掃描時間達到預設值時,觸發單元控制使能信號為低電平,各寄存器復位,掃描過程結束。

中斷處理過程如下:首先,四種中斷分別緩存入四個中斷寄存器。中斷寄存器使用FIFO存儲單元可以儲存多個中斷,利用FIFO存儲單元內部自身的標志位作為邏輯判斷依據可以簡化我們的設計。其次,中斷識別模塊檢測各FIFO存儲單元的空標志位。如果有任意一個FIFO存儲單元的空標志位為O,則說明有中斷產生,那么中斷識別模塊將按中斷優先級別排序,并產生一個脈沖通知與最高中斷級別相對應的運算單元內的數據調用模塊從RAM中讀取下一段控制量的初始值。再次,數據調用模塊完成讀取任務后返回給復位處理模塊一個處理程序完成標志。復位處理模塊在收到處理程序完成標志后根據輸出中斷類別產生讀脈沖至空標志位為O且中斷優先級別最高的中斷寄存器中。此時,中斷寄存器的空標志位有可能發生變化。最后,中斷識別模塊再次檢測所有的空標志是否都為1,如果不是,中斷處理單元繼續上述過程直到所有的空標志都為1。中斷處理過程結束。

7)步進脈沖發生單元

步進脈沖發生單元內包含多個計數器,計數使能由觸發單元控制,計數器的模從地址譯碼/數據緩存單元讀取。每隔一定時間,步進脈沖發生單元產生計數脈沖作為累加/減器的時鐘并由運算單元內計數器計數。

4 設計實例

以某型號微波毫米波接收機為例。在此接收機中,系統總線設計為串行總線,需要控制的變量有YIG振蕩器頻率、YIG濾波器中心頻率、平坦度補償數據和預選器帶寬控制電壓。選用Altera公司的EplkSOQC208—3芯片作為數字掃描控制器芯片,IDT71V016SA20Y作為RAM存儲芯片,AD7538KR、DAC8412作為DAC轉換芯片。

經測量,YIG振蕩器頻率開環控制精度達到5MHz(接收機鎖相環的鎖頻范圍可達80MHz),YIG濾波器中心頻率控制精度達到3MHz(YIG濾波器3dB帶寬最小處40MHz),平坦度補償值誤差小于O.2dB,預選器帶寬誤差小于帶寬2%。數字掃描控制器選用60MHz時鐘作為外部時鐘,在最忙碌情況下(四種中斷同時到來),完成四種中斷處理總時間小于5μs。

通過仿真和測試數字掃描控制器僅使用了FPGA內約70%的資源,可以為今后的模塊擴展留有余地。

5 結束語

實際使用過程中,我們須綜合考慮硬件自身的性能(如YIG器件磁滯效應、機械開關切換時間、中頻濾波器響應時間等)、軟件設計復雜度、要求的性能指標等多組因素對掃描控制精度、速度的影響,合理選擇劃分段數及工作時鐘,最大限度挖掘出接收機潛能.

電子發燒友App

電子發燒友App

評論