引言

數字BIST的工作原理:用一個LFSR(線性反饋移位寄存器)生成偽隨機的位模式,并通過臨時配置成串行移位寄存器的觸發器,將這個位模式加到待測電路上。數字BIST亦用相同的觸發器捕獲響應,將移出的結果壓縮成一個數字標志,再將其與一個正確的標志作逐位對比。

1 “模擬”的定義

“模擬”電路對不同的人有不同的含義。一個PLL或SERDES(串行器/解串器)可以看作是數字的,模擬的,或混合信號的。對這些單元的BIST測試可以是純數字的,因為這些功能只有數字輸入和輸出。例如,有些IC會用片上的頻率計數器

來測量PLL的輸出頻率,它是用一個基準頻率的已知周期數,統計振蕩的周期數,如果計數中的任何位不同于期望值,則測試就失敗。很多用于測試IC SERDES收發器性能的方法是采用環回的偽隨機數據,如檢測到一個誤碼就認為失敗。然而,測試ADC或DAC這類模擬電路時,顯然要求BIST電路可以生成或捕獲模擬信號,即瞬時電壓總是相關的信號。傳統的模擬電路(如濾波器和線性穩壓器)都有模擬輸入與輸出,不過很多都有數字控制的信號或時鐘。最純粹的模擬電路(如RF電路)可能根本沒有數字信號。

在測試時,模擬電路至少要有一個非確定性瞬態電壓的信號。測試包括對信號的檢查,是在兩個電壓之間,是數字值,還是時間閾值;還要檢查信號統計值是否在極限內;或檢查一個有關信號的算術運算值是否在極限之間。對所有具備任何模擬信號的電路,都應采用模擬測試原理。

純數字電路的響應是確定性的,因此,一個可接受的輸出信號只需要采樣一次。不過,如果能看到數字電路信號足夠多的細節,如毫伏或皮秒量級,則所有電路都是模擬的。在納米級CMOS工藝時,這種考慮尤其不能忽視,因為對于1V電源軌以及亞納秒級時鐘周期,電源軌噪聲、抖動、溫度以及參量變動都有顯著的影響。測試模擬電路的BIST電路容易受這些效應影響,哪怕BIST幾乎是全數字的,因此,很多模擬設計者都想了解模擬BIST如何比相同芯片上的模擬電路更精確。

2 設計模擬BIST的挑戰

設計用于模擬電路的BIST要比精確提供和捕捉模擬信號更加復雜。信號變動與需要測量的參數都要比數字BIST處理的邏輯0和邏輯1要多得多。模擬激勵與響應可以從直流電壓、線性斜坡以及脈沖,直到正弦波與頻率調制。激勵與響應可能還屬于不同的域,從而使挑戰更加復雜化。例如,一個DC電壓輸入可能產生一個頻率輸出。挑戰中還增加了需要分析的各種參數,它們可能包括幅度、相位延遲,以及SNR(信噪比),還有DC電壓、峰峰抖動,以及占空比。

測試設備一般必須比待測電路精度高一個數量級。于是,最令人生畏的模擬BIST挑戰就是:如何經濟地實現比待測電路更高的精度,而后者很可能已經實現了在其硅片面積與技術下的最佳精度。信號幅度的范圍可能非常巨大。ADC與DAC可以處理動態范圍高達224的片上模擬信號,相當于8個數量級。

數字BIST可以比作一個正在給自己的多項選擇測試打分的學生。他將一個模板放在答題紙上,統計正確答案數。另一方面,模擬BIST則可以比做一個正在做作文考試的學生。這不是一個簡單而客觀的過程。現在,考慮到實用模擬BIST所必須應用的基礎電路原理,應可以了解挑戰的量級了。

3 基礎電路原則

3.1 原則一

通過施加時序不敏感的數字測試模式、時鐘以及DC電壓,測試機制本身必須是可測的,而無需片外的線性AC信號或測量。ATE(自動測試設備)在離開工廠前,要做大量的校準與測試。要讓BIST成為混合信號ATE的替代方案,就必須在使用前作校準與測試。采用基于掃描的測試,模擬BIST電路的純數字部分應是可測的,包括邏輯BIST。如果數字電路包含了延遲線或延遲匹配線路,則應測試這些延遲和延遲增量。測量一個延遲的方法是:將延遲線包含或配置到一個回路振蕩器中,并用片上頻率計數器測量其振蕩頻率。

對模擬BIST中純 模擬部分的測試則更復雜。有些研究人員建議在自己的模擬BIST中使用一個ADC或DAC,暗含著ATE可以測試它的假設;然而,混合信號ATE仍將是必要的,因此削弱了BIST的很多優勢。

也許最陳舊的BIST技術就是將一個DAC輸出連回到一個ADC輸入,或將一個調制器輸出連到一個解調器輸入,以此完成整個數字測試。這種方法仿佛是用一個未經測試的電路,去測試另外的電路,對補償失誤不敏感。例如,對于ADC中補償的相似非線性,DAC的非線性則可能過高,因為兩者一起要好于任何單獨一個。

3.2 原則二

模擬BIST的第二個原則是欠采樣,即慢于Nyquist速率的采樣,這意味著采樣速率要低于最高頻率的兩倍——這對于較慢地分析一個信號是必需的。較慢的采樣還有利于使BIST電路小于待測電路。

在有些自校準方法中,會用一個低速ADC去欠采樣一只高速ADC或DAC的模擬信號。一級sigma-delta調制器是小而簡單的模擬電路,如果帶寬降低就可以將模擬信號轉換為任意分辨率的數字碼流。調制器可以采樣一個1600萬次/秒的信號,產生1600個1 bit的采樣;調制器可以對這些采樣作數字濾波,產生100萬個4位分辨率采樣/秒,或16000個16 位采樣/秒,每種情況都將可用帶寬減少至1/16。欠采樣可以讓一個較窄的興趣帶寬定位于原始信號頻率的中心,使其轉換為一個低的頻率,從而更便于做分析。不過,欠采樣也要付出混疊效應的代價,這是必須考慮的。

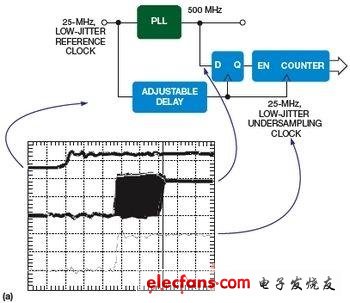

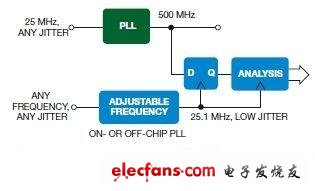

另一個采樣的例子是一個PLL BIST,它使用PLL的輸入基準時鐘沿,去采樣PLL的輸出(圖1a)。此時,一個基準通過一個可調延遲線,為一只鎖存器提供時鐘,鎖存器完成采樣工作。假設鎖存器的輸出計數1000個時鐘周期,然后延遲遞增。這個動作不斷重復,直到鎖存器獲得了累加的分布函數(圖1b)。PLL的輸出頻率可以比其基準頻率高出很多倍。這種BIST不能檢測到基準時鐘沿之間的抖動,但另外一種采用略微偏移的采樣頻率的技術,可以在輸出相位的所有點上作采樣(圖2)。

圖1,PLL BIST使用PLL的輸入基準時鐘沿,采樣PLL的輸出 (a)。一個基準通過一根可調延遲線,為一個鎖存器提供時鐘,鎖存器完成采樣工作。鎖存器的輸出計數1000個時鐘周期,然后延遲遞增。這個動作不斷重復,直到鎖存器獲得了累積分布函數 (b)。

這兩種技術表示了時間測量的一個重要原則:控制一個信號被采樣的時間時,要么是一個來自可調延遲的恒定時間偏移,要么是來自一個可調振蕩器的恒定頻率偏移,如PLL。在實現納米CMOS時,低抖動延遲越來越困難,但低抖動頻率偏移卻越來越容易實現。

3.3 原則三

模擬BIST的另一個原則通過減去系統誤差來提高精度。例如,當測量電壓時,必須消除任何比較器或運算放大器的偏移電壓。如果這些電路有可忽略的偏移,則必須測量該偏移,以驗證它確實是可忽略的;否則,就必須減去它的值。比較簡單的方法是假設該偏移較大,將其減掉。當測量延遲時,必須從輸出的延遲中,減去待測電路輸入端的測試接入路徑延遲,以確保消除了接入路徑的延遲。ATE通常采用乘法和減法,做模擬自校準,但這種運算需要太多電路,對BIST并不經濟。當系統誤差上下起伏時,可能會出現低頻效應,如由于電力線噪聲而使偏移以50 Hz或60 Hz變化。

通過增加采樣來計算均值,可以提高精度。一個信號或測量電路中的隨機噪聲限制了對任何信號特性測量的可重復性。當在一次測量中包含了更多的采樣時,就改善了測量的變動與可重復性。模擬測量電路實現均化的方法一般是用低通濾波,或用一個電容做電荷積分。

可以在模擬BIST的數字電路中使用全加法器,但很多情況下,用二進制計數器可以更高效地實現均化。用簡單的均化或減法都無法抑制掉非隨機的噪聲,例如來自鄰近同步邏輯或60 Hz電力線的干擾。不過,可以通過與干擾的同步采樣,或對干擾頻率作整數周期的積分,從而降低其影響。

為獲得成本效益,BIST電路必須有高于待測電路的成品率。對于數字BIST的情況,這種要求只是意味著其面積必須小于待測電路面積。然而對于模擬BIST,這一原則還意味著BIST必須在不影響成品率情況下,實現所需要的線性度、噪聲以及帶寬。在一項研究中,一個測試芯片上只有70%的小型模擬BIST電路可以實現所需要的測量精度。該BIST的成品率對SoC(系統單芯片)的影響等同于電路占整個SoC的30%情況。

使BIST的成品率高于待測模擬電路的最佳方式是盡可能減少BIST中的模擬電路數量,即使其數字化。通過在多個功能之間共享一個BIST電路,可以減少與BIST電路有關的面積。數字BIST可以很容易實現這一任務,但模擬BIST則相反,因為需要測試的功能之間存在差異性。這就是MadBIST建立的原因,這種方法由MF Ton er和Gordon W Roberts共同開發。采用MadBIST時,一只DSP首先測試一只ADC然后才是DAC。MadBIST、ADC和DAC,然后再測試其它模擬電路。

采用共享分析塊有一個問題,即將感興趣的模擬信號傳送給分析塊。完成這個工作一般采用模擬總線,但它們會帶來負載、噪聲和非線性,并且會減小帶寬。一種替代方法是在本地將信號轉換為某種數字表述,然后采用一個數字總線。

模擬BIST必須能夠采用基于規范的結構化測試。換句話說,所做激勵與響應分析的結果,必須能與模擬電路的功能規范作校對,但它們也必須面向制造缺陷,幫助做診斷,并盡可能減少測試時間。面向缺陷的測試有助于完成這個任務,但一般不會嘗試使用仿功能測試。飛利浦(現在的恩智浦公司)在1995年首先在基于規范的傳統模擬測試與面向缺陷的測試之間做了一個公開的行業對比。結論是:當設計規范有更大的裕度,并且過程得到良好的控制時,面向缺陷的測試能對相近的缺陷覆蓋實現更快的測試。另一方面,基于規范的測試對保持測試覆蓋和成品率都是必要的。

數字BIST天然地就采用一種仿功能的激勵,因為幾乎任何1和0的模式都能表示功能模式下的輸入信號,包括偽隨機數據。而為模擬電路提供一種仿功能激勵則可能復雜得多。偽隨機噪聲是一個誘人的模擬激勵,它能處理很多潛在的缺陷,并且易于生成。一只電阻和一只電容就可以對數字BIST中的LFSR輸出做濾波,產生一個模擬波形。乘法器和加法器可以將待測模擬電路的響應與其偽隨機輸入做交叉關聯。

另外一種更容易實現的方案是,將電路輸出端連接到輸入端,必要時增加增益或反相,從而將電路重新配置為一個振蕩器,并測量其振蕩頻率。這種技術具有面積效率。不幸的是,這兩種方案都被證明難以使用,因為測量對于噪聲和非線性都太不敏感,而診斷也不實用。

ATE廣泛采用一種線性斜坡與單音正弦波作為測試激勵,從而有效地測試ADC和DAC的線性度,并作診斷輔助。在片上產生一個純斜坡或正弦波的最強大方式是在一個循環移位寄存器中存儲一個周期性的sigma-delta碼流,不過這種方案可能需要數千個邏輯門,外加模擬濾波。所幸的是,一個激勵塊可能就足以應付一片SoC中的所有模擬功能,并且可以有效地將串行數字碼流送給芯片的各個區域。

激勵生成的最簡單而有用的信號是一個數字方波,可以用它去測量一個步長,或一個脈沖響應。令人驚訝的是,對于一個用于生成波形的采樣比較器來說,精確DC電壓是一種困難的激勵或基準,除非求助于需要更多自測的模擬技術。對一個占空比可編程的數字波形做低通濾波,可以產生一個基本上是DC的波形,其平均電壓取決于占空比,并且在高開關降低開關頻率,就降低了DC電壓對這種不匹配的敏感度,但增加了DC電壓的峰峰變動。在模擬功能中(如穩壓器),增加有源低通濾波就可以減少這種噪聲。但采用這種方案的模擬BIST必須對濾波做測試。更適合于BIST的是在“高速模擬電路測試與驗證研討會”上剛剛演示的一種技術。

3.4 原則四

模擬BIST的最后原則是,必須通過與上下測試極限值的比較,將其結果輸出為一個數字測量值以及合格/不合格的比特。如果要將一個模擬的電壓結果送至片外做特性描述,它就可能遭到損壞,并且可能需要混合信號ATE。一個未在片上與極限值比較過的數字結果可能需要用ATE去捕捉和分析數字字,而不是單個比特,這就不能使用最常見的測試模式語言WGL(波形生成語言)和STIL(標準測試界面語言),以及很多低成本的測試儀。單有合格/不合格的結果將無法確定參數特性,也缺乏測量的可重復性,而這是設定測試極限的一個基本步驟。

了解了這些基礎原則,就明白,實用PLL BIST既沒有采用模擬電路,也沒有使用延遲線,因此它對噪聲的敏感度弱于待測PLL。例如,PLL必須每納秒生成一個低抖動邊沿,并盡量減小抖動的累積。但是,PLL BIST可以用一個預測試的低抖動時鐘對邊沿作欠采樣,時鐘通過幾個數字反相器傳送,這些反相器有快速的轉換性能,盡量減少附加的抖動。

如果沒有預測試的時鐘,則PLL可以對相同芯片上工作在一個略為異步頻率的其它PLL邊沿作采樣。獲得的抖動測量結果是兩個抖動水平之和;隨機抖動不可能相互抵消。在一個直方圖中增加很多這類采樣,可以降低寄生噪聲的影響,并且以與任何干擾相同速率采樣,可以進一步降低這種影響。

4 模擬BIST的需求

過去15年來,很少有什么人提出的模擬BIST技術包含了上述所有原則。但所有這些原則都是BIST實用性與性價比的關鍵。開發一種實用的模擬BIST已被證明有太高的挑戰性,但工程師們無疑將開發出一些包含這 些原則的技術,因為對它們的需求在不斷增加。

SoC中正在加入更多的系統模擬功能,有更多的管腳數和門數,所有這些都推升了測試時間與測試成本。增加嵌入閃存會大大增加測試時間(遠不止一分鐘),從而絕對需要多址的測試,這種要求又推動了對低管腳接入以及更多模擬測試資源的需求。

電子發燒友App

電子發燒友App

評論