整流電路啟發設計了如下電路,通過proteus仿真可以實現3倍壓全波整流:仿真結果如下:相對傳統半波倍壓電路,此電路除了具有全波倍壓輸出穩定的特點,另外還有一個特點當負載增大到使4個儲能電容放電到

2015-08-15 11:36:02

為什么要創造新的電池放電技術?當前電池放電技術有哪幾種?全在線放電技術是什么?全在線放電是如何工作的?在線放電技術與當前放電技術對比,有什么不同?

2021-04-15 06:34:57

差分電路三角波轉正弦波原理很簡單可是我multisim仿真老是不對啊波形好夸張啊求大神幫忙{:1:}

2014-07-04 12:17:15

差分放大電路,里面使用的運放是否有什么要求,必須雙電源供電的?還是必須單電源也可以我用TLC2254做差分放大電路,在輸入端輸入0.287V直流電壓,不變,而放大倍率是1+210K/1K=21倍

2023-03-17 10:31:28

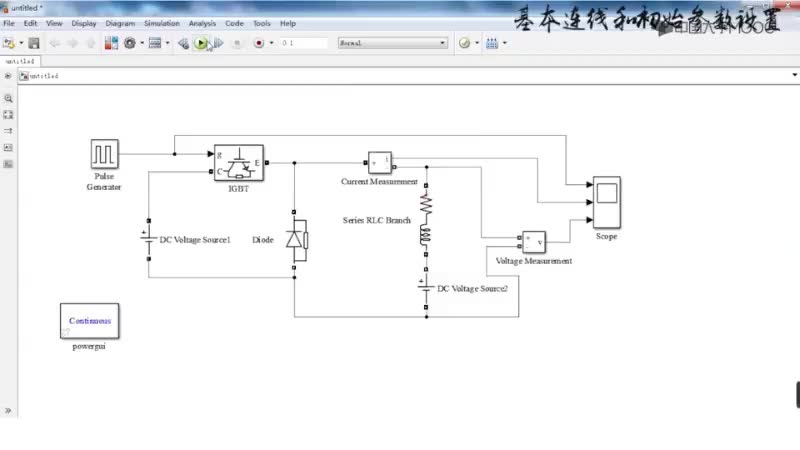

圖2-3α=80%時電源電壓,負載兩端電壓,脈沖信號和流過負載電流波形當占空比α=80%時,電源電壓100V,負載兩端電壓為500V。3.升降壓斬波電路的仿真研究3.1電路原理圖升降壓斬波電路

2021-07-09 07:30:12

本帖最后由 gk320830 于 2015-3-7 09:22 編輯

斬波電路原理

2012-08-20 10:03:03

斬波電路原來是指在電力運用中,出于某種需要,將正弦波的一部分"斬掉".(例如在電壓為50V的時候,用電子元件使后面的50~0V部分截止,輸出電壓為0.)后來借用到DC-DC

2011-11-02 18:25:10

斬波電路電流能夠連續的主要原因是什么?

2023-05-11 17:08:28

斬波型運放提供較低的失調電壓,同時也極大地減少了1/ f(閃爍)噪聲。它是怎么做到的?

2021-04-06 09:43:57

作者: TI 專家 Bruce Trump翻譯: TI信號鏈工程師 Tom Wang (王中南) 斬波型運放提供較低的失調電壓,同時也極大地減少了1 / f(閃爍)噪聲。它是怎么做到的?這篇短文就來

2018-09-21 09:43:34

斬波型運放是如何減少噪聲的?

2021-03-11 06:13:21

差分輸入電壓VIN(t)和頻率 2 × fCHOPP的情況,如圖2所示。可以看出,當斬波時鐘CHOP和CHOP_INV切換時,VIN(t)達到其峰值VIN_AC。因此,就像直流差分輸入電壓一樣,該交流

2021-01-25 09:12:24

。采樣交流輸入電壓引起的動態輸入電流直流輸入電壓下的動態輸入電流由方程式3給出。現在考慮一種具有交流正弦差分輸入電壓VIN(t)和頻率 2 × fCHOPP的情況,如圖2所示。可以看出,當斬波時鐘

2022-07-14 11:51:16

釋: 大概是這個意思,步進電機的頻沖頻率決定步進電機的轉速,但由于繞組是一個電感線圈,電源電壓一定時,轉速低時流過步進電機繞組的平均電流會很大,為了限制電流,采取斬波電路,就是當電流上升到某一值時,將繞組

2017-08-28 17:40:29

輸入端視為等電位,這一特性稱為虛假短路,簡稱虛短。顯然不能將兩輸入端真正短路。那么在電路設計中,如何分析虛斷與虛短運放電路呢?

2019-03-27 09:39:16

運放的電壓追隨電路,如圖 1 所示,利用虛短、虛斷,一眼看上去簡單明了,沒有什么太多內容需要注意,那你可能就大錯特錯了。理解好運放的電壓追隨電路,對于理解運放同相、反相、差分、以及各種各樣的運放

2020-02-28 08:00:00

運放電路,好像還有一些用,需要的來下載吧

2015-04-04 22:44:03

運放電路PCB設計技巧

2020-12-29 07:50:05

運放電路中的相位補償

2021-03-17 07:04:41

本帖最后由 gk320830 于 2015-3-4 20:20 編輯

運放電路是模擬電路中最基本的電路,也是每個工程師必須要掌握的電路!!

2012-07-27 20:13:54

在公司的產品看到兩個運放的應用電路,有兩點不明,還請賜教:1. 差分轉單端電路 在差分正負輸入跨接R5的作用是什么?2. 單端轉差分電路 在網上看到的資料都是兩個運放,一個接輸入正,另一個接輸入負,圖上的兩個運放都接正端輸入,有什么區別?差分轉單端電路

2019-02-19 15:59:59

常見外部噪聲源運放電路如何降噪

2021-02-26 06:03:22

運放電路的七大應用場景

2021-03-11 07:49:46

此運放電路怎么計算啊,求解答

2014-08-26 18:39:05

運放電路輸出怎么計算

2021-08-23 11:57:19

最近做了一個全波整流,用的就是經典型運放電路,但是頻率升高的時候到了100k的時候波形就失真了,我用的是5532,想問一下到底是怎么回事?希望大神指點一下。

2016-05-28 13:14:33

如何,你接受能力如何,更決定了你將來走的深度。附件為運放精密全波整流電路原理圖,包含多個經典電路圖,歡迎大家下載學習。如果積分不夠,或者是網速不行,可以留下郵箱,我給大家發到郵箱。^_^ …………我很好吧?^_^

2015-04-13 11:37:22

請問一下高側全斬波驅動正常,只是將獨立輸出的PWM改為互補輸出,想實現半斬波驅動BLDC需要怎么開半橋

2019-09-21 11:39:44

Cuk斬波電路是開關電源六種基本DC/DC變換拓撲之一。Cuk斬波電路也稱Cuk變換器。美國加州理工學院SlobodanCuk提出的對Buck/Boost改進的單管不隔離直流變換器,在輸入輸出段均有

2019-02-27 07:00:00

0引言近日,在學習電力電子技術課程時,需要小組完成對有關DC-DC斬波電路的理論分析與仿真,恰好有關大創項目需要用到Buck斬波電路的滑模控制方法,需要對其建立狀態空間模型做控制器,因此我就以

2021-12-28 07:53:14

和可靠性,因此。如何選擇斬波電路和斬波器件十分重要。IGBT是近代新發展起來的全控型功率半導體器件,它是由MOSFET(場效應晶體管)與GTR(大功率達林頓晶體管)結合,并由前者擔任驅動,因此具有

2018-10-17 10:05:39

14腳,...使用LM324的升壓器怎么做?LM324D運放電路故障分析LM324簡易電子琴電路仿真proteus5V單電源供電LM324組成的差分放大電路,輸出波形被截波>>

2018-08-29 17:26:16

采用一片LM324集成運放,設計制作精密全波整流電路,具體要求如下:要求可以輸入任意波形,如正弦波,三角波或方波,輸入頻率范圍為0~100kHz,信號幅度幅度0~5V,利用運算放大器消除二極管的非線性影響,輸出精確的全波整流波形,且放大倍數可調。

2021-06-07 18:57:15

boost斬波電路

2012-10-22 12:26:28

會增加到3A,這樣形成恒流斬波,不過仿真過程中卻是由3A直接變成0A,3、一樣的電路,為什么昨天仿真和今天仿真結果不同?剛剛接觸proteus,不是很懂,希望有會的人指點一下,萬分感謝。

2017-04-20 17:31:28

這兩天有幸參與眾籌,并開始學習《5大運放電路設計教程 帶你吃透模電技術》這一課程的“運放電路基礎:開環、閉環、反饋和零極點”部分,下面就第一講的學習,做個小總結。 1.基本運放基本電路介紹 下圖是一

2019-06-30 22:55:59

1、什么是斬波電路?斬波電路原來是指在電力運用中,出于某種需要,將正弦波的一部分"斬掉".(例如在電壓為50V的時候,用電子元件使后面的50~0V部分截止,輸出電壓為0.)后來

2018-07-22 21:12:05

一個控制周期中負載電流脈波數稱為斬波電路的相數對嗎?

如果電源側直流電壓相同,負載側濾波電感電流連續,采用半橋電路時輸出電壓為100V,假如采用全橋電路時輸出電壓為50V對嗎?

電力電子器件一般由

2023-05-11 16:39:09

的增益以及匹配組件的要求存在限制。新型交叉連接技術通過交叉連接兩個儀表放大器,如圖4所示,這種新電路使用單個增益電阻提供具有精密增益或衰減的全差分輸出。通過將兩個參考引腳連接在一起,用戶可以根據需要調整

2021-10-15 06:30:00

` 誰能闡述一下什么是斬波頻率?`

2019-08-23 16:42:18

仿真從零學運放—16 運放開發板反相放大電路仿真從零學運放—17 運放開發板差分放大電路仿真《從0學運放,史上最全運放電路設計入門資料》下載地址:https://pan.baidu.com/s/1slrrDLz

2017-04-08 16:44:35

全差分儀表放大器具有其他單端輸出放大器所沒有的優勢,它具有很強的共模噪聲源抗干擾性,可減少二次諧波失真并提高信噪比,還可提供一種與現代差分輸入ADC連接的簡單方式。低功耗全差分儀表放大器電路怎么設計?

2021-04-06 08:11:07

最近在設計全差分折疊型共源共柵運放的時候,有一個問題想不明白,加入偏置電壓后,調節管子讓每個管子都處于飽和狀態,并且輸出處在了VDD/2。但是我發現只要偏置電壓改變一點點哪怕1mv,靜態工作點就會有很大的改變,這是為什么呢,好奇怪,有沒有老哥為我解惑

2022-09-27 00:29:12

這里寫自定義目錄標題問題分析傳輸線全波放大浮地方案問題采用逐飛的運放電路,先同相放大后倍壓檢波,得到的直流電平直接給RT1064核心板ADC,發現從車身兩側的電感采集到的數據有非常大的尖峰(如圖

2021-09-17 08:15:04

升壓斬波電路影響電流連續和斷續的電路參數是什么呢?

2023-05-11 16:41:00

求高手教我升壓斬波電路怎么做

2013-03-21 23:56:22

升降壓與Cuk斬波電路模塊比較分析

2019-10-31 09:10:44

升降壓直流斬波電路及matlab仿真.doc 電力電子課程設計1目錄緒論………………………………………………………………….3一.降壓斬波電路…………………………………………………6二.直流斬波電路

2021-09-15 08:41:52

各種運放電路

2015-03-14 19:22:25

我用同相輸入運放電路放大一下轉速正弦信號時,LM324使用單電源5V供電, 為什么到正弦波的負半周輸出變成了高電平?見附圖,負半周輸出不是應該是0電位嗎?

補充內容 (2017-9-24 18:19):

用Multisim仿真也是這樣的結果,說明電路是對的,但是不理解為什么這樣。

2017-09-18 18:45:02

兩路輸入,太陽能供電是恒壓20V,用壓降斬波實現;風力供電是8-15V,用升壓斬波電路,通過電壓的變化改變占空比!電路輸出是15V!電路調式達不到效果!

2012-05-05 09:48:19

。首先,串聯超級電容器的部分能量被多重SEPC斬波電路吸收,然后再被優先分配給電壓較低的超級電容,而電壓最高的超級電容則不會被分配到能量,這樣隨著能量的分配,圖4中的電壓差△V就會逐漸減小并消失。 3

2018-10-22 15:48:39

如何利用單電源運放實現精密全波整流

2021-03-11 06:30:28

可以使用儀表放大器生成差分輸出信號嗎?隨著對精度要求的不同提高,全差分信號鏈組件因出色的性能脫穎而出,這類組件的一個主要優點是可通過信號路由拾取噪聲抑制。由于輸出會拾取這種噪聲,輸出經常會出現誤差

2019-09-11 11:51:20

為了解決傳統S/H電路失真大和靜態工作點不穩定的問題,采用0.25 μm BiCMOS工藝,設計了一款高速率、高精度的10位全差分BiCMOS S/H電路。文中改進型自舉開關電路和雙通道開關電容共模反饋電路(CMFB)設計具有創新性。

2021-04-21 06:24:21

`運放電路設計參考圖圖中精密全波整流電路的名稱,純屬本人命的名,只是為了區分;除非特殊說明,增益均按1設計.圖1是最經典的電路,優點是可以在電阻R5上并聯濾波電容.電阻匹配關系為R1=R2,R4

2011-07-23 09:43:36

LF355N JFET輸入運放 ULN LF357N JFET寬帶非全襝運放 ULN2003 周邊七段驅動陳列 LF398N 采樣/保持電路 ULN2004 周邊七段驅動陳列

2011-05-08 09:58:45

Miguel Usach典型DPD應用模數轉換器(ADC)中集成的緩沖器和放大器通常是斬波型。有關這種斬波實現的例子,可參見AD7124-8和AD7779數據手冊。需要這種斬波技術來最大程度地降低

2018-10-16 10:09:58

晶閘管實現的降壓斬波電路

最近學電力電子有題不會,是晶閘管實現的降壓斬波電路。有沒有人給分析一下,是如何實現降壓斬波的。

2012-11-16 09:40:01

橋式可逆斬波電路設計方法與心得(1)原理分析驅動電路(基本配置)包括PWM信號處理、封鎖信號處理、死區生成、MOSFET 驅動、H橋主電路、直流電源變換(電池7.2V→5V、12V)等6個功能單元

2021-11-12 08:36:00

本帖最后由 奇牙虎威 于 2021-3-5 17:11 編輯

求一個音頻差分輸入轉單端輸出運放電路這個對不對

2021-03-05 16:27:53

`這是鄙人用multisim13仿真實現的一個“經典運放全波精密整流電路”(含仿真電路和仿真結果),仿真實現該電路的作用主要有以下兩點:1、熟習Multisim13這款電路仿真設計軟件各個功能模塊

2015-12-14 16:24:51

1、整流電路2、直流斬波電路降壓斬波電路(Buck Chopper)。該電路使用一個全控型器件IGET,也可使用其他器件,若采用晶閘管,需設置使晶閘管關斷的輔助電路。斬波電路的典型用途之一是拖動

2021-09-17 07:58:54

電路、升降壓斬波電路、復合斬波電路等多種方式的變換電路,直流斬波技術已被廣泛用于開關電源及直流電動機驅動中,使其控制獲得加速平穩、快速響應、節約電能的效果。

2019-09-12 09:00:03

【不懂就問】直流斬波就是DC/DC的電源變換電路嗎?不明白這個“斬”怎么理解,要是DC/DC變換,這個被斬的“波”是什么?是不是DC首先轉換成AC后的交流波形?

2018-07-04 11:42:01

大家好,遇到一個疑惑,要對原來做的系統改進,原系統用的是偽差分ADC,單端信號輸入,現在想改為真差分ADC,但是傳感器輸出的是單端信號,所以在ADC之前要用一個單端轉差分的模塊,就想問一下,這么做的效果在理論上是不是會好點,還有全差分ADC與偽差分ADC相比優勢在哪里,謝謝。

2023-12-15 08:22:16

在做課程設計時,老師讓使用MATLAB軟件做“電力MOSFET升壓斬波電路電源對三相變壓器進行仿真”,可實在不知升壓斬波電路電源怎么具體使用。所以1、怎么能讓升壓斬波電源在仿真中起作用。2、三相變壓器仿真的一些步驟。望各位能予以解答或提供相關資料。謝謝。

2018-12-07 13:59:43

斬波運放的工作原理是什么?怎樣去設計斬波運放電路?如何降低D類音頻系統的低頻噪聲和電壓失調?

2021-04-23 07:28:32

D 類音頻功放的1/f噪聲和電壓失調對信號的失真和噪聲性能產生直接的影響,特別是在輸入信號為零時的背景噪聲最為明顯,通過采用全差分斬波運放電路和T /H解調技術,有效地降

2010-07-22 17:07:21 33

33

電子發燒友App

電子發燒友App

評論