的評(píng)估方法,不代表可以在應(yīng)用電路對(duì)共模信號(hào)實(shí)現(xiàn)有效抑制。本篇解析放大器共模抑制比參數(shù)定義與其影響的評(píng)估方法,以及結(jié)合一個(gè)實(shí)際案例討論影響電路共模抑制的因素。

2020-10-14 16:41:45 10135

10135

放大倍數(shù)F比較大,因此輸入共模電壓就被衰減了,Vo_cm會(huì)非常小,共模抑制比是差模增益與共模增益的比值,因此共模抑制比就可以提高。

2022-11-02 18:04:50 2956

2956

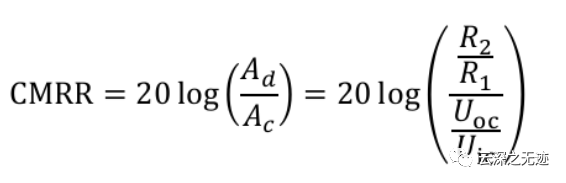

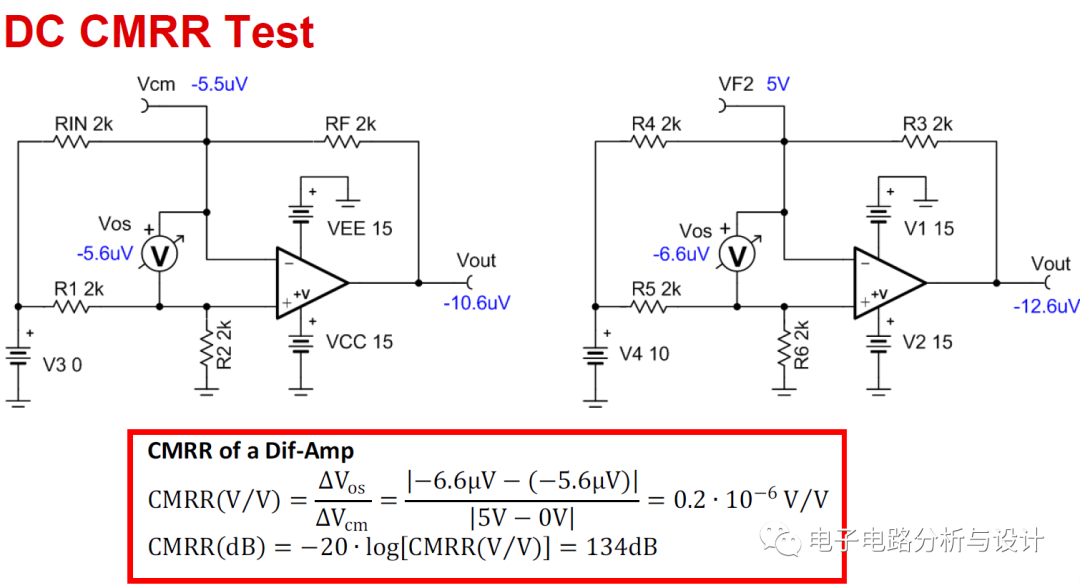

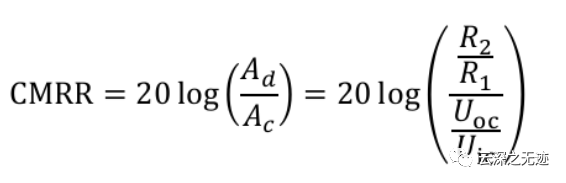

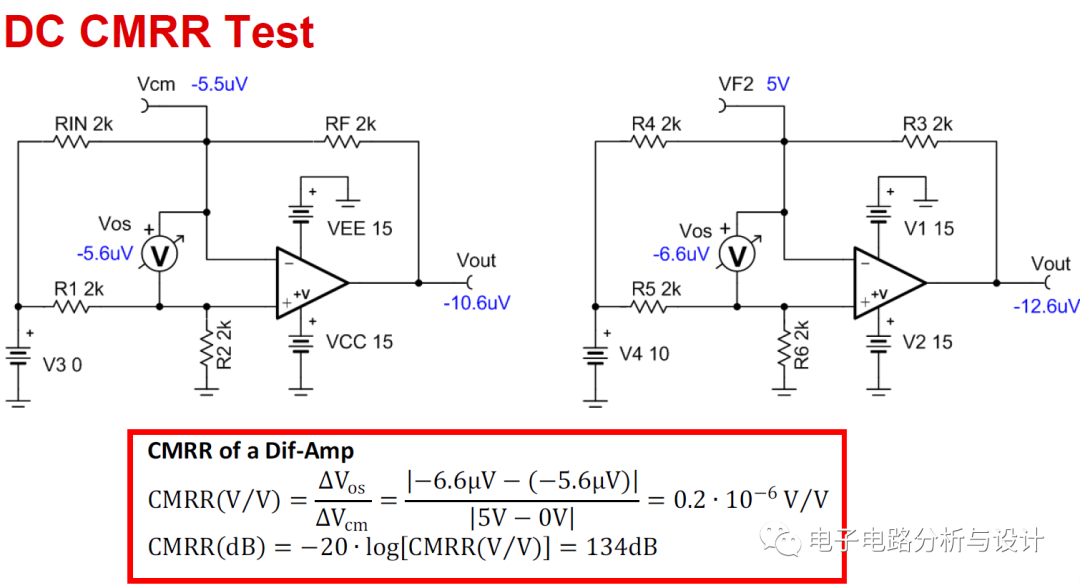

實(shí)際上,共模電壓的變化會(huì)引起輸出變化。 運(yùn)算放大器共模抑制比(CMRR)是 指共模增益與差模增益的比值。

2023-02-12 17:08:42 2184

2184

在高壓差分探頭的設(shè)計(jì)和應(yīng)用中共模抑制比(Common Mode Rejection Ratio,簡(jiǎn)稱(chēng)CMRR)是一個(gè)重要的性能指標(biāo)。CMRR代表了差分信號(hào)和共模信號(hào)之間的差異,量化了探頭能夠抵抗

2023-08-09 09:41:30 453

453

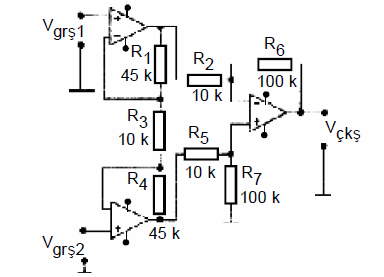

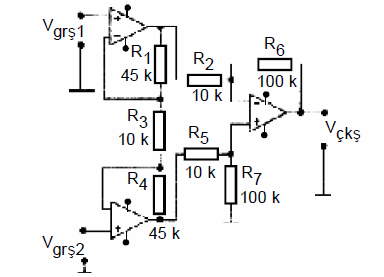

在儀表放大器中,高共模抑制比 (CMRR) 是一個(gè)理想的屬性,因?yàn)樗试S精確的差分信號(hào)放大,同時(shí)抑制共模噪聲。我們將在這篇文章中討論高 CMRR 儀表放大器的電路原理圖。

2023-08-09 15:39:10 1234

1234

今天繼續(xù)給大家分享運(yùn)放另一項(xiàng)指標(biāo)——共模抑制比(CMRR)。

2023-10-01 13:10:00 1514

1514

在開(kāi)始討論運(yùn)放的共模抑制比CMRR之前,我們先了解一下運(yùn)放的共模輸入電壓和軌對(duì)軌運(yùn)放。

2023-11-02 10:20:11 1132

1132

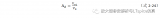

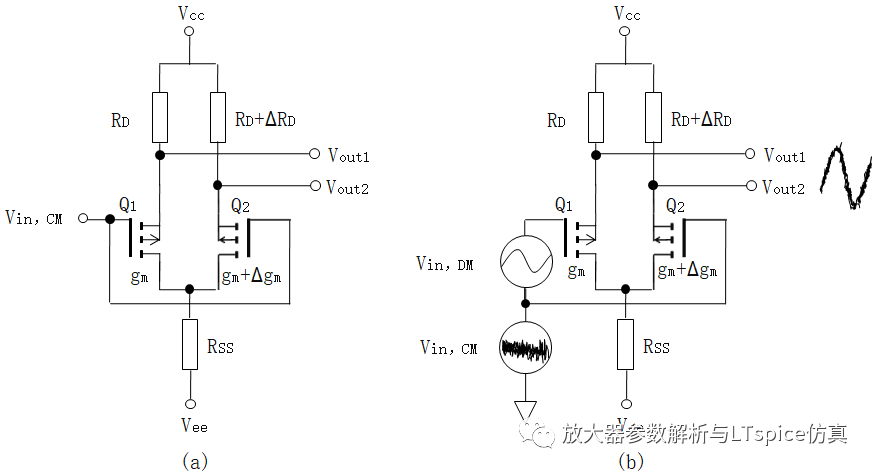

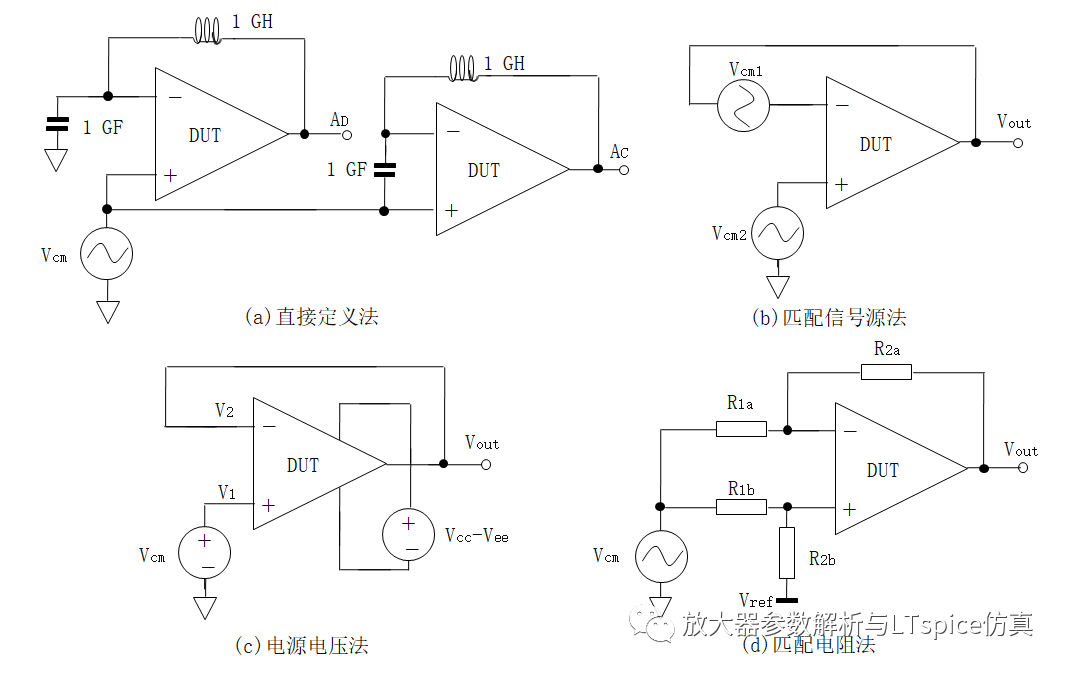

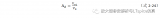

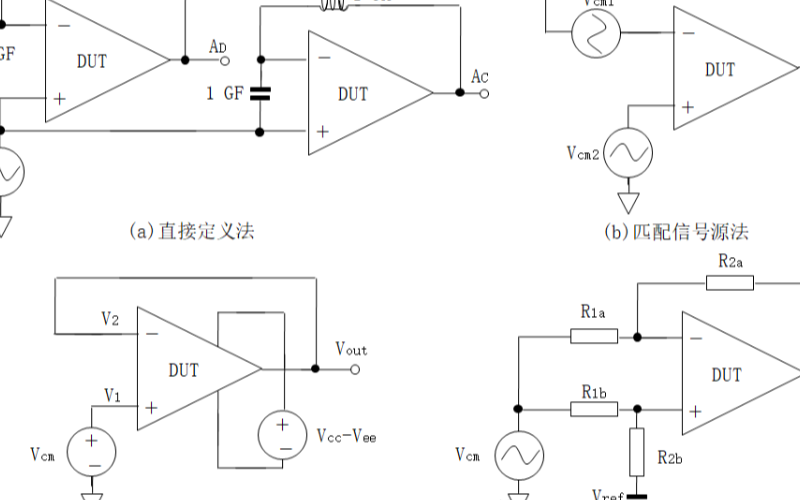

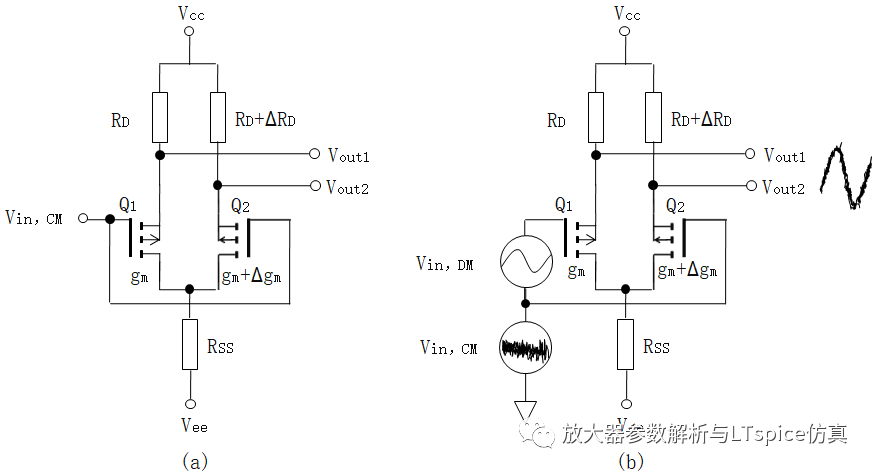

方法,在Allen書(shū)中都有相關(guān)的介紹。最近發(fā)覺(jué)對(duì)這些仿真電路的原理有點(diǎn)模糊(主要還是對(duì)于CMRR的仿真電路),在這里拿出來(lái)重新溫習(xí)一下下圖是共模抑制比仿真電路,通過(guò)ac小信號(hào)分析(兩個(gè)Vcm相同,都取 ac=1),分析Vout輸出的信號(hào)共模抑制比由電路分析看到: Vout=Adm?(V1?V2)+Ac

2021-12-27 07:24:51

我在找信號(hào)放大器的時(shí)候,有的給出了增益,類(lèi)似于功率可以增加多少倍,有的給出了共模抑制比,這兩個(gè)我怎么分別?我最后的結(jié)果是看我的信號(hào)功率能否從-15dBm增加到10dBm,共模抑制比我怎么換算?

2018-08-09 09:48:40

讀論文analysis of switched-capacitor commom-mode feedback circuit1.與單端輸出相比,全差分電路有更好的共模抑制比和電源抑制比。2.共模環(huán)路

2021-10-29 07:10:25

AD-運(yùn)算放大器共模抑制比CMRR

2012-04-01 10:47:33

。實(shí)測(cè)出來(lái)的這個(gè)值相比其他差分運(yùn)放相差很大,在AD8260的手冊(cè)上并沒(méi)有找到CMRR值說(shuō)明。High current driver的共模抑制比測(cè)量出來(lái)的結(jié)果對(duì)嗎??

2024-03-06 06:58:28

儀表放大器AD620的共模輸入范圍超過(guò)電源電壓,會(huì)影響共模抑制比嗎?比如AD620采用正負(fù)5V電源供電,放大倍數(shù)為10倍,測(cè)試時(shí)共模輸入范圍為7.07V / 100Hz,會(huì)影響共模抑制比嗎?

2023-11-15 06:49:17

全工作頻率范圍內(nèi)的運(yùn)放共模抑制比如何測(cè)試?

2023-11-17 09:17:54

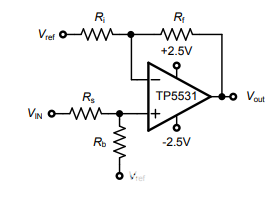

如圖所示,下面是一個(gè)交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(hào)(10V,10Hz),進(jìn)行電路的共模抑制比(CMRR)測(cè)試,測(cè)試發(fā)現(xiàn):

1、差分信號(hào)從INS+

2018-08-03 06:26:16

,Kcmrmin_計(jì)算結(jié)果:依次是(r1,r2,r3,r4在電路中的實(shí)際值,共模放大率,差模放大率,共模抑制比)CMmax_ = 995010050100509950

2016-09-23 15:34:29

對(duì)消驅(qū)動(dòng)電路提高共模抑制比的原理分析

2021-04-06 06:57:03

[td][/td] 如圖所示,如何設(shè)計(jì)AD8221交流耦合電路能:

1、降低噪聲,提高信噪比(SNR);

2、提高儀表運(yùn)放輸入阻抗;

3、提高共模抑制比(CMRR)。

2023-11-17 09:47:43

通過(guò)精確匹配的電阻網(wǎng)絡(luò)提高差分放大器的共模抑制比

2021-01-28 06:19:27

提高差分放大器的共模抑制比,電阻的選擇很關(guān)鍵

2021-03-11 07:17:03

如何利用高增益運(yùn)放,設(shè)計(jì)了一種具有高共模抑制比,高增益數(shù)控可顯的測(cè)量放大器。提高了測(cè)量放大器的性能指標(biāo),并實(shí)現(xiàn)放大器增益較大范圍的步進(jìn)調(diào)節(jié)。

2021-04-22 06:59:18

該款芯片為一高性能的差分信號(hào)接收器,但輸入為含共模干擾的一對(duì)差模信號(hào),但輸出亦含有不少共模干擾信號(hào)。用示波器觀(guān)察差分輸入信號(hào)時(shí),信號(hào)質(zhì)量很好,也即差模信號(hào)都應(yīng)該濾除。一直不明白此芯片應(yīng)該具有良好的共模抑制比啊,有沒(méi)有哪位曾經(jīng)用過(guò)該芯片的,介紹下注意事項(xiàng)。

2013-07-22 16:42:46

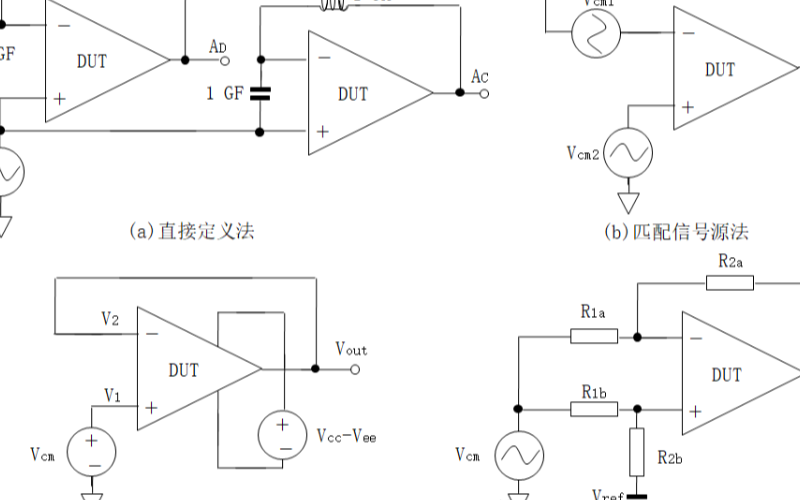

下圖是電子學(xué)第二版的一個(gè)差分放大電路,書(shū)中說(shuō)這電路共模抑制比是10萬(wàn),這能從圖中算出來(lái)嗎?

2020-04-08 23:09:06

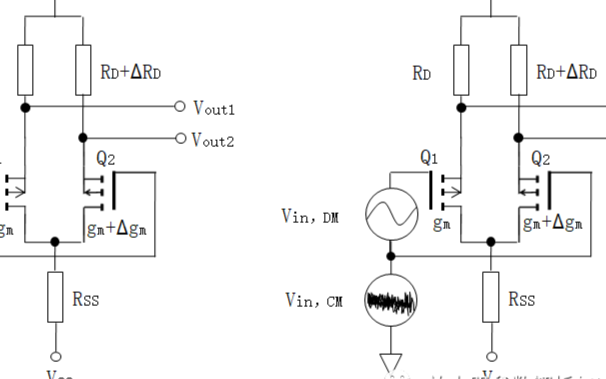

差動(dòng)放大電路加深理解差動(dòng)放大器的工作原理;學(xué)習(xí)差動(dòng)放大器共模抑制比的測(cè)量方法;掌握提高差動(dòng)放大器共模抑制比的方法;差動(dòng)放大器是一種零點(diǎn)漂移非常小的直接耦合放大器。由于電路結(jié)構(gòu)的盡可能對(duì)稱(chēng)性,使其具有

2009-09-08 08:52:26

多個(gè)型號(hào),THS4521是比較出色的一個(gè)型號(hào),性能優(yōu)異。但即使再好的差分驅(qū)動(dòng)器,也必須配合合適的匹配電阻網(wǎng)絡(luò)才能發(fā)揮其優(yōu)越性能。而實(shí)際上,電阻器的非理想性會(huì)對(duì)各種電路產(chǎn)生影響,例如:共模抑制比(CMRR

2019-05-22 08:53:17

用到AD8227這款芯片,感覺(jué)共模抑制比有點(diǎn)低,請(qǐng)問(wèn)怎么測(cè)定這個(gè)參數(shù),我試過(guò):將所有電極連在一起,相對(duì)于大地驅(qū)動(dòng)這些電極。同樣,共模抑制的定義是20×log(VOUT/VIN),其中,VIN為共模

2023-11-21 06:24:20

什么是紋波抑制比PSRR?如何確定應(yīng)用的紋波抑制比PSRR呢?怎樣去測(cè)量LDO芯片的紋波抑制比PSRR呢?

2021-11-03 06:48:15

常被誤用的放大器共模抑制比測(cè)量方法會(huì)存在哪些不足?有沒(méi)有一種有效測(cè)量共模抑制比電路方案介紹?

2021-03-11 06:00:18

為 400KHz 的噪聲,折算到輸出端是幅值為 4mV 頻率為 400KHz 噪聲。圖 2.62 ADA4077 電源抑制比評(píng)估電路所以在開(kāi)關(guān)電源供電精密電路中,依靠放大器自身提高電源抑制比的方式十分

2020-11-24 09:20:54

容易讓人想到,在高增益下產(chǎn)生任何輸出偏移,都需要電源的明顯變化!但一定要記住:共模抑制比 (CMRR) 和 PSRR 都是輸入?yún)⒖紖?shù):(1) PSRR 和 CMRR 定義為輸入失調(diào)電壓變化 ΔVOS

2018-09-19 11:00:26

如圖所示,下面是一個(gè)交流耦合放大電路,在電路的差分輸入端輸入差模(100uV,10Hz)和共模信號(hào)(10V,10Hz),進(jìn)行電路的共模抑制比(CMRR)測(cè)試,測(cè)試發(fā)現(xiàn):

1、差分信號(hào)從INS+

2023-11-17 09:09:39

尋找一款超高共模抑制比的儀表運(yùn)放,起碼高于120dB,越高越好

2018-08-03 07:12:09

想通過(guò)國(guó)標(biāo)的方式測(cè)試ADA4077、LF357、TL081的開(kāi)環(huán)增益和共模抑制比,想問(wèn)下大家有沒(méi)有好的建議?目前已經(jīng)在測(cè)試TL081的開(kāi)環(huán)增益,但是出現(xiàn)振蕩現(xiàn)象,大家?guī)蛶兔ΓF(xiàn)象為:J1處供給6V

2023-11-20 06:18:06

現(xiàn)在正做一個(gè)折疊式共源共柵放大器的設(shè)計(jì),性能指標(biāo)增益和電源抑制比不能同時(shí)達(dá)到要求,各位大神幫忙告訴我怎么提高電源抑制比?另外,抑制電路到底是什么啊?最好有圖呈現(xiàn),謝謝了!

2016-05-27 13:52:28

請(qǐng)問(wèn)下有沒(méi)有共模抑制比測(cè)量的芯片,我只百度到了下面的測(cè)量電路。

2021-12-29 11:39:15

如圖所示,如何設(shè)計(jì)AD8221交流耦合電路能:1、降低噪聲,提高信噪比(SNR);2、提高儀表運(yùn)放輸入阻抗;3、提高共模抑制比(CMRR)。

2018-08-06 06:55:10

能在輸入端再跟隨一級(jí)運(yùn)放嗎?

2023-11-20 07:31:59

用到AD8227這款芯片,感覺(jué)共模抑制比有點(diǎn)低,請(qǐng)問(wèn)怎么測(cè)定這個(gè)參數(shù),我試過(guò):將所有電極連在一起,相對(duì)于大地驅(qū)動(dòng)這些電極。同樣,共模抑制的定義是20×log(VOUT/VIN),其中,VIN為共模

2018-09-13 11:52:30

想通過(guò)國(guó)標(biāo)的方式測(cè)試ADA4077、LF357、TL081的開(kāi)環(huán)增益和共模抑制比,想問(wèn)下大家有沒(méi)有好的建議?目前已經(jīng)在測(cè)試TL081的開(kāi)環(huán)增益,但是出現(xiàn)振蕩現(xiàn)象,大家?guī)蛶兔ΓF(xiàn)象為:J1處供給6V

2018-08-16 07:01:59

能在輸入端再跟隨一級(jí)運(yùn)放嗎?

2019-01-11 06:57:47

輸入電壓范圍的定義是什么?什么是共模抑制比?影響共模抑制比的因素有哪些?

2021-09-27 07:49:52

高共模抑制比儀用放大電路方案

2012-10-29 06:44:52

通過(guò)硬件和軟件的仿真實(shí)驗(yàn),總結(jié)出差分放大電路共模抑制比測(cè)定的正確方法關(guān)鍵詞:差分放大電路;共模抑制比;差模電壓放大倍數(shù);共模電壓放大倍數(shù);仿真

2010-04-13 11:07:33 90

90 共模抑制比(CMRR) 是指差分放大器對(duì)同時(shí)加到兩個(gè)輸入端上的共模信號(hào)的抑制能力。更確切地說(shuō),CMRR是產(chǎn)生特定輸出所需輸入的共模電壓與產(chǎn)生同樣輸出所需輸入的差分電壓的比值。

2010-07-05 16:00:55 75

75 什么是共模抑制比

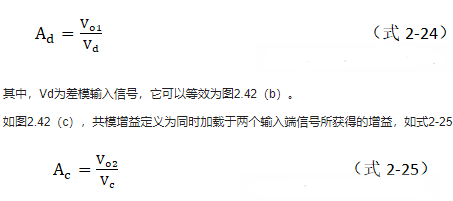

為了說(shuō)明差動(dòng)放大電路抑制共模信號(hào)的能力,常用共模抑制比作為一項(xiàng)技術(shù)指標(biāo)來(lái)衡量,其定義為放大器對(duì)差模信號(hào)的電壓放大倍數(shù)Aud 與對(duì)共模信號(hào)的電

2007-10-15 17:37:51 7499

7499

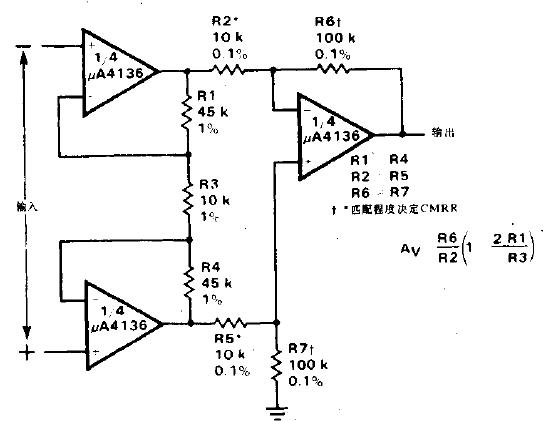

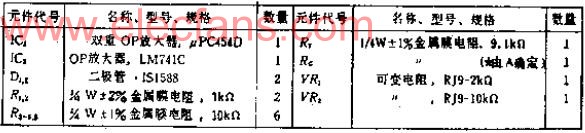

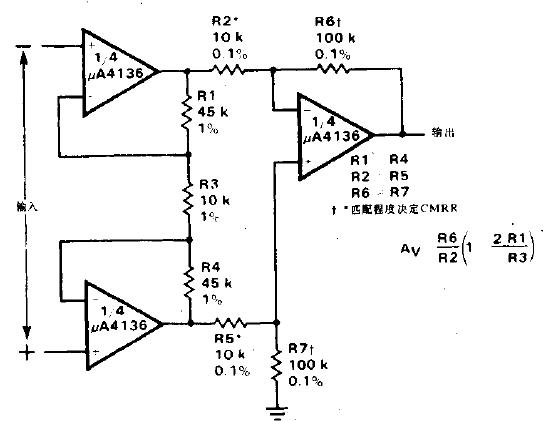

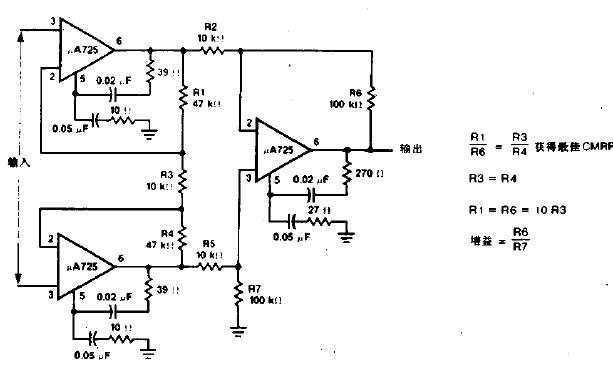

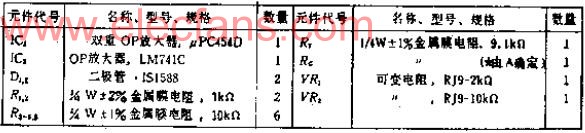

具有高共模抑制比的差分輸入儀器用放大器電路圖

2009-04-01 09:14:11 1047

1047

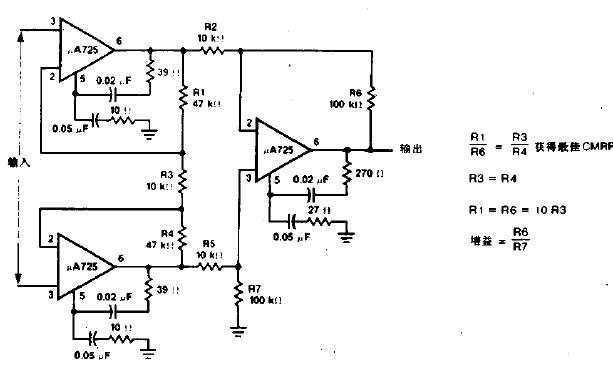

具有高共模抑制比的儀器用放大器電路圖

2009-04-01 09:14:35 1006

1006

放大器的共模抑制比的定義

共模抑制比(CMRR)是指差分放大器對(duì)同時(shí)加到兩個(gè)輸入端上的共模信號(hào)的抑制能力。更確切地說(shuō),CMRR是產(chǎn)生特

2009-04-22 20:40:37 2179

2179 共模抑制比,共模抑制比是什么意思

共模抑制比的定義

為了綜合評(píng)價(jià)差動(dòng)放大電路對(duì)共模信號(hào)的抑制能力和對(duì)差模信號(hào)的放大能力,特

2010-03-09 16:36:11 12738

12738 用平衡輸入電路抑制共模噪聲的話(huà)筒放大器

電路的功能

OP放大器的共模抑制比很大,可

2010-04-26 17:23:34 3421

3421

共模抑制比和輸入阻抗高的儀表用差動(dòng)放大電路

電路的功能

一個(gè)OP放大器構(gòu)成的高增益差

2010-04-27 16:16:13 3229

3229

本文鐘睜傳統(tǒng)儀用放大電路的特點(diǎn),介紹了一種高共模抑制儀用放大電路,引入若模負(fù)反饋,大大提高了通用儀表放大器的共模抑制能力。 現(xiàn)場(chǎng)測(cè)試結(jié)果表明,在不加入共模對(duì)消電路時(shí)

2011-08-29 17:13:41 100

100 本文針對(duì)傳統(tǒng)儀用放大電路的特點(diǎn),介紹了一種高共模抑制比儀用放大電路,引入共模負(fù)反饋,大大提高了通用儀表放大器的共模抑制能力。

2012-02-02 14:32:34 118

118 你或許知道“共模抑制比是差模增益與共模增益之比”,但你知道共模抑制比120dB與60dB區(qū)別多大嗎?你知道為什么要抑制共模信號(hào)嗎?

2015-10-01 15:00:00 21297

21297 2598277

2018-08-28 20:21:30 1245

1245 呢? 網(wǎng)絡(luò)變壓器

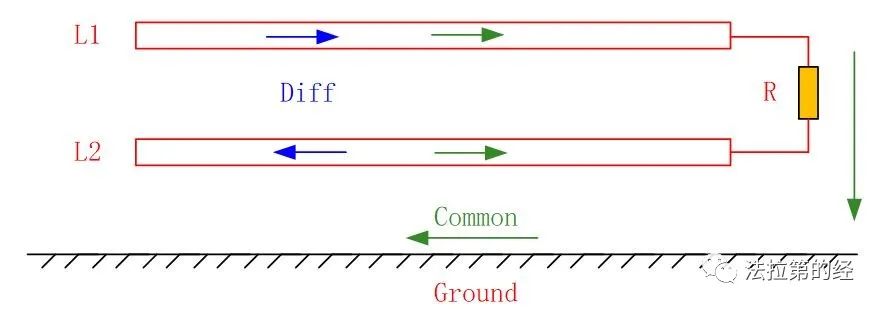

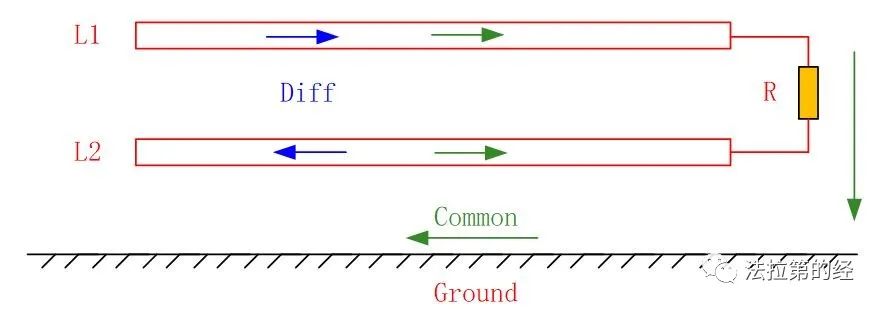

CMRR:在一個(gè)網(wǎng)絡(luò)系統(tǒng)中,為了說(shuō)明差分放大電路抑制共模信號(hào)及放大差模信號(hào)的能力,常用共模抑制比作為一項(xiàng)技術(shù)指標(biāo)來(lái)衡量,其定義為放大器對(duì)差模信號(hào)的電壓放大倍數(shù)Aud與對(duì)共模信號(hào)的電壓

2019-02-25 17:55:54 1185

1185 來(lái)源:羅姆半導(dǎo)體社區(qū) 共模抑制比(CMRR) 是指差分放大器對(duì)同時(shí)加到兩個(gè)輸入端上的共模信號(hào)的抑制能力。更確切地說(shuō),CMRR是產(chǎn)生特定輸出所需輸入的共模電壓與產(chǎn)生同樣輸出所需輸入的差分電壓的比值

2023-02-01 13:42:32 1822

1822 放大器的差模增益是電路所需要的增益,而共模增益將放大直流噪聲。共模抑制比(Common Mode Rejection Ratio,CMRR),定義為差模增益與共模增益的比值,如式2-26。

2020-10-22 17:51:53 3398

3398

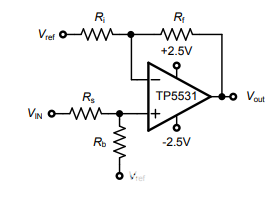

如《放大器共模抑制比(CMRR)參數(shù)評(píng)估與電路共模抑制能力實(shí)例分析》中案例,由于電阻誤差導(dǎo)致電路共模抑制能力下降,是使用通用放大器組建差動(dòng)放大電路的常見(jiàn)問(wèn)題之一。工程師常常疑惑1%誤差的電阻

2020-10-31 09:42:35 3484

3484

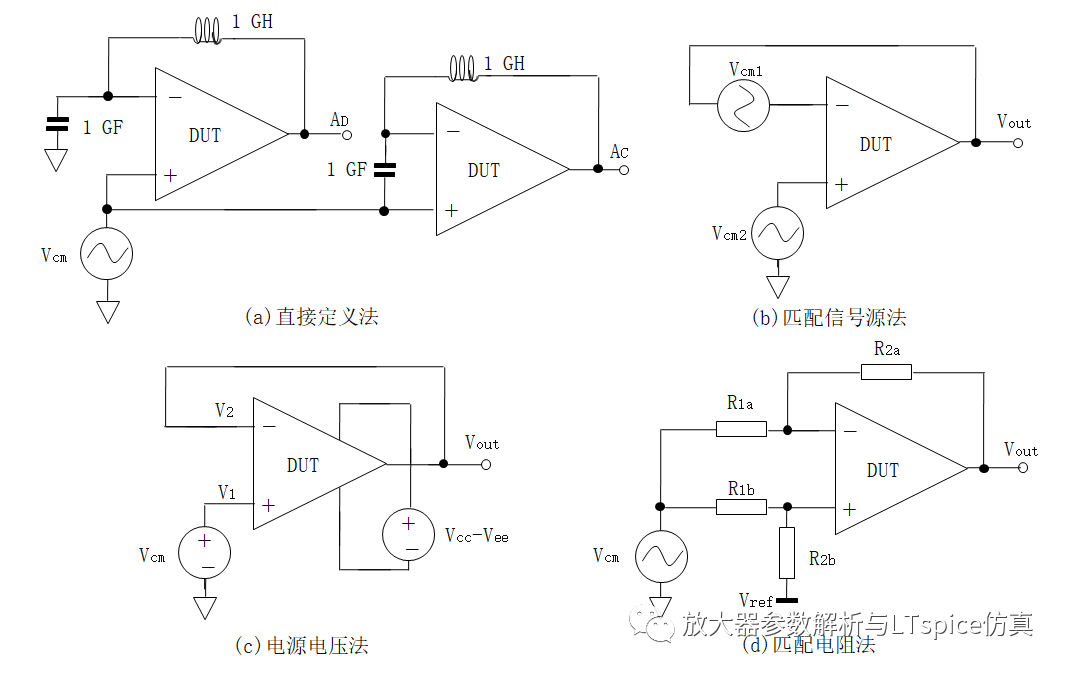

測(cè)量放大器的失調(diào)電壓、偏置電流參數(shù),可根據(jù)所設(shè)計(jì)的電路簡(jiǎn)易調(diào)整就能完成測(cè)試。而共模抑制比參數(shù)的測(cè)試方法卻相對(duì)復(fù)雜,本篇分析幾種常被誤用的放大器共模抑制比測(cè)量方法的不足之處,以及提供一種有效測(cè)量

2020-11-04 18:00:47 4458

4458

在《放大器共模抑制比(CMRR)參數(shù)評(píng)估與電路共模抑制能力實(shí)例分析》文中,介紹使用共模抑制比的倒數(shù),將共模信號(hào)折算到輸入端評(píng)估所引起的誤差,有工程師認(rèn)為這種方式在輸入共模信號(hào)為交流信號(hào)時(shí)的結(jié)果不準(zhǔn)

2020-11-14 11:09:05 3733

3733

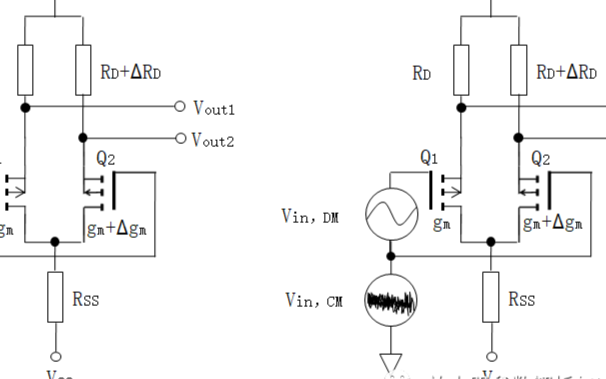

共模抑制比的提高方法和模擬噪聲分析的注意事項(xiàng) 一、共模抑制比的提高方法 ? ?? 我們重點(diǎn)介紹通過(guò)精確匹配的電阻網(wǎng)絡(luò)提高差分放大器的共模抑制比。在各種應(yīng)用領(lǐng)域,采用模擬技術(shù)時(shí)都需要使用差分放大器電路

2021-05-04 10:15:00 7762

7762

DN1023-精密匹配電阻器自動(dòng)提高差分放大器共模抑制比-方法如下

2021-05-11 19:58:22 4

4 方法,在Allen書(shū)中都有相關(guān)的介紹。最近發(fā)覺(jué)對(duì)這些仿真電路的原理有點(diǎn)模糊(主要還是對(duì)于CMRR的仿真電路),在這里拿出來(lái)重新溫習(xí)一下下圖是共模抑制比仿真電路,通過(guò)ac小信號(hào)分析(兩個(gè)Vcm相同,都取 ac=1),分析Vout輸出的信號(hào)共模抑制比由電路分析看到: Vout=Adm?(V1?V2)+Ac

2022-01-05 14:22:58 5

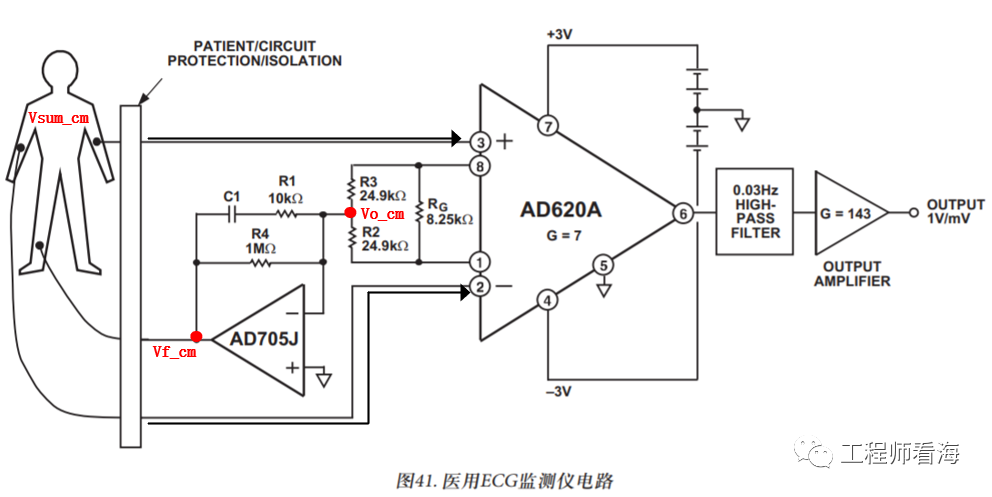

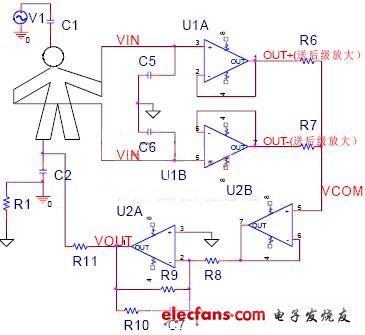

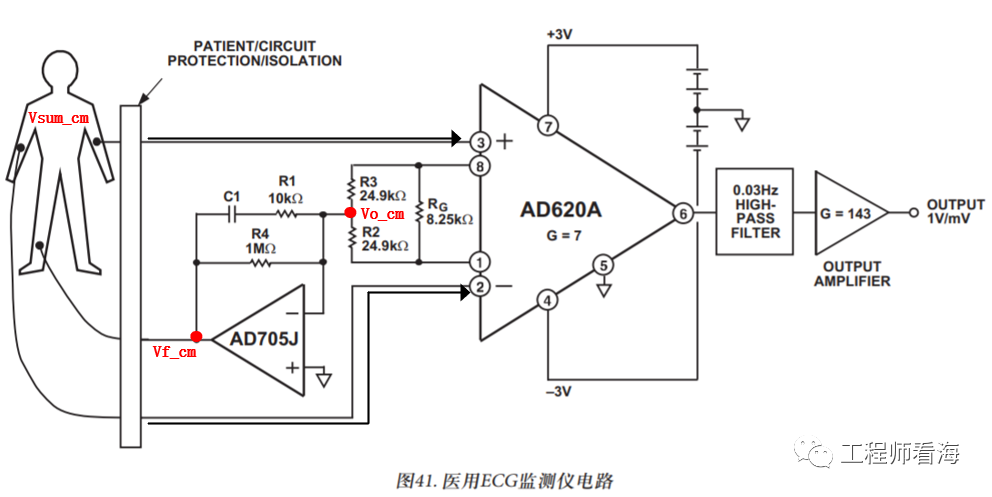

5 下圖是典型的心電放大電路,AD620是3運(yùn)放儀表放大器,AD705J構(gòu)成右腿驅(qū)動(dòng)電路,右腿驅(qū)動(dòng)電路的主要作用是提高共模抑制比,減少50Hz或60Hz的工頻干擾。

2022-04-15 16:08:42 2962

2962 理想情況下,差分放大器電路中的電阻應(yīng)仔細(xì)選擇,其比值應(yīng)相同 (R2/R1 = R4/R3)。這些比值有任何偏差都將導(dǎo)致不良的共模誤差。差分放大器抑制這種共模誤差的能力以共模抑制比(CMRR) 來(lái)表示。

2022-06-01 09:41:09 2487

2487 其實(shí)在共模信號(hào)為交流信號(hào)時(shí),這種評(píng)估方法仍然實(shí)用,問(wèn)題在于放大器的共模抑制比參數(shù)并非恒定不變,它隨共模信號(hào)頻率變化變化。本篇介紹共模抑制比隨共模交流信號(hào)變化的原因,評(píng)估示例,并通過(guò)仿真增強(qiáng)理解。

2023-02-22 14:30:55 614

614

測(cè)量放大器的失調(diào)電壓、偏置電流參數(shù),可根據(jù)所設(shè)計(jì)的電路簡(jiǎn)易調(diào)整就能完成測(cè)試。而共模抑制比參數(shù)的測(cè)試方法卻相對(duì)復(fù)雜,本篇分析幾種常被誤用的放大器共模抑制比測(cè)量方法的不足之處,以及提供一種有效測(cè)量共模抑制比電路以及提供仿真。

2023-02-22 14:33:45 1305

1305

電源抑制比是什么意思?電源抑制比怎么提高? 一、電源抑制比的概念 電源抑制比(PSRR)又稱(chēng)電源噪聲抑制比,是指在電路中,當(dāng)電源發(fā)生噪聲時(shí),電路輸出端對(duì)電源噪聲的抑制程度,一般使用分貝(dB)單位

2023-09-02 17:50:32 3367

3367 儀表放大器共模抑制比怎么計(jì)算? 儀表放大器是一種性能較高的放大器,其主要功能是對(duì)信號(hào)進(jìn)行高精度的放大和測(cè)量,具有通用性,不僅可用于電子器件中,還可用于傳感器和儀表等領(lǐng)域。儀表放大器的共模抑制比是衡量

2023-09-05 17:39:18 1449

1449 失調(diào)電壓和共模抑制比的區(qū)別和聯(lián)系? 失調(diào)電壓和共模抑制比是兩個(gè)重要的電路參數(shù),它們的測(cè)量和分析對(duì)于電路的設(shè)計(jì)和穩(wěn)定性評(píng)估非常重要。本文將詳細(xì)介紹失調(diào)電壓和共模抑制比的定義、測(cè)量方法以及它們之間的區(qū)別

2023-09-21 17:40:32 576

576 。為了解決這個(gè)問(wèn)題,大多數(shù)差分放大器電路都會(huì)使用恒流源,以提高其共模抑制比。 恒流源的原理是將電路中的電阻轉(zhuǎn)化為一個(gè)固定的電流源,通過(guò)固定的電流來(lái)驅(qū)動(dòng)電路的工作。這種電流源可以提供穩(wěn)定的電流,并對(duì)電路的共模抑制

2023-10-23 10:29:16 892

892 什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和電源抑制比(power supply rejection

2023-10-29 11:45:48 2999

2999 能夠有效抑制共模干擾,提高信號(hào)傳輸質(zhì)量。影響共模抑制比的主要因素有系統(tǒng)設(shè)計(jì)、電路拓?fù)洹V波器設(shè)計(jì)、地線(xiàn)布局等。 首先,系統(tǒng)設(shè)計(jì)是影響共模抑制比的關(guān)鍵因素之一。在系統(tǒng)設(shè)計(jì)過(guò)程中,合理地選擇合適的工作電壓范圍、工作

2023-11-08 17:46:26 1146

1146 能夠有效抑制共模干擾,提高信號(hào)傳輸質(zhì)量。影響共模抑制比的主要因素有系統(tǒng)設(shè)計(jì)、電路拓?fù)洹V波器設(shè)計(jì)、地線(xiàn)布局等。 首先,系統(tǒng)設(shè)計(jì)是影響共模抑制比的關(guān)鍵因素之一。在系統(tǒng)設(shè)計(jì)過(guò)程中,合理地選擇合適的工作電壓范圍、工作

2023-11-09 09:10:09 443

443 運(yùn)放的共模抑制比高有什么作用?共模抑制比比較高的運(yùn)放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一個(gè)衡量運(yùn)放的性能的重要指標(biāo),表示運(yùn)放在輸入信號(hào)

2023-11-20 16:35:53 916

916 高壓差分探頭的共模抑制比如何排除? 高壓差分探頭是用于測(cè)量高壓電壓的一種儀器,在實(shí)際應(yīng)用中,可能會(huì)遇到共模干擾的問(wèn)題,影響測(cè)量的準(zhǔn)確性。為了排除共模抑制比,我們需要從以下幾個(gè)方面著手:探頭設(shè)計(jì)、信號(hào)

2024-01-08 14:55:37 193

193 同相比例放大器為什么對(duì)共模抑制比要求高?運(yùn)放的共模抑制比如何仿真? 同相比例放大器是一種常見(jiàn)的放大電路,用于放大微弱信號(hào)。在應(yīng)用中,通常需要對(duì)放大的信號(hào)進(jìn)行差分測(cè)量,即對(duì)信號(hào)的差值進(jìn)行放大,而抑制

2024-01-26 14:42:55 237

237 共模抑制比和邊模抑制比分別是什么意思?有什么區(qū)別? 共模抑制比和邊模抑制比是電子電路設(shè)計(jì)中兩個(gè)重要的性能指標(biāo)。它們描述了一個(gè)電路在輸入信號(hào)中存在的共模干擾和邊模干擾下能夠提供的抑制程度。共模抑制比

2024-02-05 14:55:20 186

186

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論