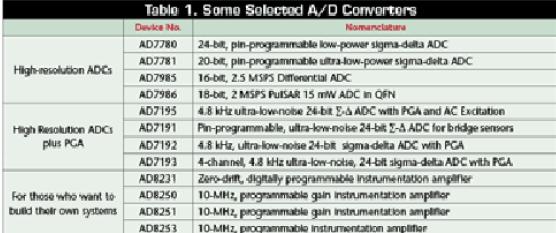

ADC的主要趨勢之一是分辨率越來越高。這一趨勢影響各種應用,包括工廠自動化、溫度檢測和數據采集。對更高分辨率的需求正促使設計者從傳統的12位逐次逼近寄存器(SAR)ADC轉至分辨率高達24位的Δ-ΣADC。

所有的ADC都會具有一定的噪聲,這包括輸入參考噪聲(ADC固有噪聲)和量化噪聲(ADC轉換時產生的噪聲)。諸如噪聲、ENOB(有效位數)、有效分辨率和無噪聲分辨率等指標在很大程度上定義了ADC的實際精度。所以,理解與噪聲相關的性能指標是從SAR過渡至Δ-ΣADC最困難的方面之一。由于當前對更高分辨率的迫切需求,設計者必須更好地理解ADC噪聲、ENOB、有效分辨率,以及信噪比(SNR)。本文的目的正基于此。

Δ-ΣADC的更高分辨率和價值

在過去,12位SAR ADC通常足以滿足各種信號和電壓輸入的測量。如果應用中需要更為精細的測量,可在ADC之前增加增益級或可編程增益放大器(PGA)。

分辨率為16位時,設計者的選擇仍然主要是SAR ADC,但也包括部分Δ-ΣADC。然而,對于需要16位以上分辨率的設計,Δ-ΣADC則更為普遍。SAR ADC目前受限于18位,而Δ-ΣADC則延伸至18、20和24位。Δ-ΣADC還有其它優勢。其價格在過去10年中已大幅下降,使用越來越簡單,已被廣泛接受。

有效分辨率

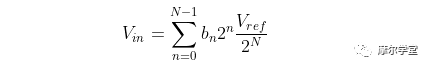

有效分辨率由下式定義(以位為單位):

有效分辨率= log2 [滿幅輸入電壓范圍/ADC RMS噪聲]

或更為簡單:

有效分辨率= log2 [VIN/VRMS NOISE]

切勿將有效分辨率與ENOB相混淆,盡管兩者聽起來非常類似。測量ENOB的最常見方法是對ADC的正弦波輸入進行FFT分析。IEEE(r)標準1057將ENOB定義為:

ENOB = log2 [滿幅輸入電壓范圍/(ADC RMS噪聲× √12)]

SINAD定義為信噪比加失真比。SINAD和ENOB用于衡量ADC的動態性能。

所以:

SINAD = [RMS輸入電壓/RMS噪聲電壓]

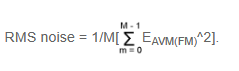

式中,RMS噪聲= 1/M[eq1。

式中,EAVM =剩余XAVM,XAVM(FM)為DFT之后規定離散頻率下的平均幅度譜分量。

有效分辨率和無噪聲分辨率本質上衡量ADC在直流下的噪聲性能,此時頻譜失真(THD、SFDR)無關緊要。

知道ADC的噪聲和輸入范圍后,計算有效分辨率和無噪聲分辨率就很簡單。

ADC的輸入電壓范圍基于參考電壓。如果ADC集成PGA,也會影響電壓范圍。有些Δ-ΣADC包括PGA,以放大小信號。最新帶PGA的ADC往往規定噪聲小于100nVRMS。盡管這些噪聲系數與舊式ADC相比看起來很吸引人,但往往基于非常小的輸入范圍。這是因為小的輸入范圍最終會放大至適合更寬、基于參考電壓的ADC有效范圍。所以,盡管這些帶PGA的ADC的噪聲看起來很小,但有效分辨率和無噪聲分辨率可能并不像無PGA的ADC那么好。

簡單舉例說明。PGA設置為128的24位ADC,參考電壓為2.5V,輸入范圍為(VREF/PGA ((2.5V/128 = 39.1mV)時,噪聲為70nVRMS。因此,有效分辨率為:

log2 [VIN/VRMS NOISE] = log2 [39.1mV/70nV] = 19.1位

使用相同的ADC,PGA設置為1時,噪聲上升至1.53(VRMS。輸入范圍為5V ((2.5V/1)時,有效分辨率變為21.6位。

最佳方法是參閱ADC的數據資料,檢查您所需的輸入范圍。

無噪聲分辨率

無噪聲分辨率采用峰-峰電壓噪聲,而非RMS噪聲。無噪聲分辨率由下式定義,單位也為位:

無噪聲分辨率= log2 [滿幅輸入電壓范圍/ADC峰-峰噪聲]

無噪聲分辨率= log2 [VIN/VP-P NOISE]。

無噪聲分辨率有時候也稱為無閃爍分辨率。以實驗室中的51/2或61/2數字多用表為例考慮這一指標。如果顯示屏上的最后一位穩定且無閃爍,數據輸出字則優于系統的噪聲水平。

以波峰因子6.6為例,峰-峰噪聲為RMS噪聲的6.6倍。因此,有效分辨率比無噪聲分辨率高2.7位。采用以上相同的噪聲和參考值,無噪聲分辨率為18.9位。

無噪聲計數

無噪聲計數是高精度系統的另一指標,用于評估ADC性能。對于那些可能需要50,000個無噪聲計數的應用,例如電子秤,尤其如此。可將無噪聲分辨率乘以系數2N,通過轉換計算得到該值。

以10位ADC為例。采用210,理想10位ADC的無噪聲計數為1,024。理想12位ADC的無噪聲字數為4,096。同理,采用以上相同的無噪聲分辨率,得到的無噪聲計數為218.9或489,178。

Δ-ΣADC過采樣

Δ-ΣADC的優勢之一是其過采樣架構。這意味著內部振蕩器/時鐘的工作頻率遠高于輸出數據速率(也稱為吞吐率)。有些Δ-ΣADC可改變輸出數據速率。這樣設計者可將采樣優化為速度較高、噪聲性能較差;或者優化為速度較低并帶更多濾波、噪聲整形(將噪聲移至感興趣測量區域之外的頻帶)及噪聲性能更好。許多最新的Δ-ΣADC以表格形式提供有效分辨率和無噪聲分辨率結果,很容易比較優缺點。

表1所示為示例ADC在雙極性輸入模式和單極性模式下的數據率、噪聲、無噪聲分辨率(NFR)和有效分辨率。ADC為MAX11200,24位器件,能夠測量雙極性((VREF)或單極性(0V至VREF)輸入。MAX11200工作于2.7V至3.6V單電源,基準可最大偏置至電源。雙極性值基于最大輸入范圍±3.6V;單極性測量基于0V至3.6V輸入范圍。

MAX11200的內部振蕩器可由軟件設置為2.4576MHz,在較低數據率下可提供60Hz抑制;或者設置為2.048MHz,在較低數據率下可提供50Hz抑制。無論哪種數據率,ADC噪聲相同。因此,無噪聲分辨率和有效分辨率值相一致。可施加外部振蕩器,實現55Hz限波,很好地抑制50Hz和60Hz。

表1中詳細列出的一項關鍵因素是雙極性有效分辨率。由于輸出數據字長度為24位,所以該指標限制為最大24位。在3組最低數據率設置下,如果ADC在串行接口上可輸出超過24位的話,那么ADC的噪聲水平可低至使有效分辨率優于24位。

有效分辨率總比無噪聲分辨率好2.7位,除非受限于數據輸出字。

表1. MAX11200采樣率與噪聲關系表。

噪聲整形和濾波,實現更低噪聲和更優分辨率

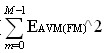

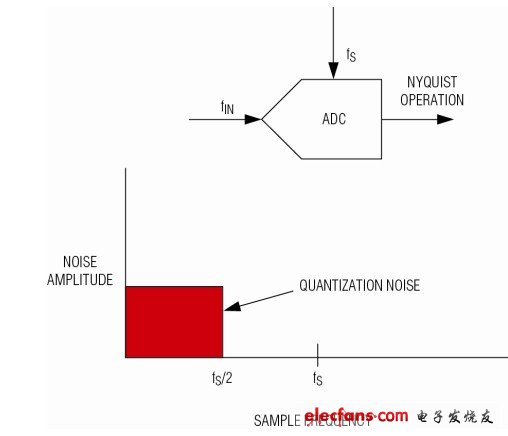

除過采樣外,噪聲整形可使Δ-ΣADC實現表1所示的低噪聲和高精度。如圖1至3所示。圖1所示為標準ADC的量化噪聲。圖2給出的ADC包括過采樣、數字濾波和抽樣。采用過采樣的大部分ADC核心為Δ-Σ。過采樣N倍將噪聲延展至更寬的頻帶,而數字(sinc)濾波器濾除了相當部分的噪聲。

圖1. 標準ADC噪聲性能

圖2. ADC采用N倍過采樣、數字濾波器和抽樣。

圖3給出的Δ-Σ調制器與圖2具有相同的框圖,再加上噪聲整形。通過將噪聲不均勻地移至較高頻率,感興趣頻帶內的噪聲變得極低。這樣的技術使得Δ-Σ ADC制造商可以獲得小于1(VRMS的噪聲系數。

圖3. ADC采用N倍過采樣、噪聲整形、數字濾波器和抽樣。感興趣的ADC輸入頻帶內的噪聲(綠色區域)變得非常小。

結論

Δ-ΣADC具有過采樣能力和固有的低噪聲,是需要較高分辨率系統設計中的極佳選擇。由于設計者必須處理更小的信號,所以充分理解ADC噪聲、有效分辨率、ENOB和無噪聲分辨率就成為選擇正確ADC方案中不可缺少的一部分。

電子發燒友App

電子發燒友App

評論