數(shù)據(jù)采集和通用測(cè)試測(cè)量設(shè)備中使用的精密信號(hào)鏈必須適應(yīng)寬廣的輸入電平范圍。信號(hào)鏈可能需要提供高輸入阻抗,同時(shí)支持增益和衰減,并調(diào)整共模電平以確保信號(hào)落在ADC的適當(dāng)輸入范圍內(nèi)。

2023-07-07 12:35:48 371

371

匹配傳感器輸出和 ADC 輸入范圍可能很難,尤其是要面對(duì)當(dāng)今傳感器所產(chǎn)生的多種輸出電壓擺幅時(shí)。本文為不同變化范圍的差分、單端、單極性和雙極性信號(hào)提供簡(jiǎn)便但高性能的 ADC 輸入驅(qū)動(dòng)器解決方案,本文

2013-07-23 09:26:46 3545

3545 在本文中,“傳感器”和“輸入信號(hào)”可以互換使用,代表ADC信號(hào)鏈的任何類型的電壓輸入。ADC信號(hào)鏈的輸入信號(hào)可以是傳感器、來(lái)自某些源的信號(hào)或控制回路的反饋。

2021-08-18 10:26:41 4810

4810

16位數(shù)據(jù)寄存器中。模擬看門狗特性允許應(yīng)用程序檢測(cè)輸入電壓是否超出用戶定義的高/低閥值。ADC 的輸入時(shí)鐘不...

2021-08-05 06:53:44

示波器使用8位ADC來(lái)數(shù)字化所輸入的信號(hào),這主要由示波器的應(yīng)用需求及ADC的技術(shù)發(fā)展所決定。隨著一些新興應(yīng)用的不斷推進(jìn),8位ADC往往會(huì)因?yàn)樵肼暤脑蚨鴣G失細(xì)節(jié),無(wú)法很好地滿足市場(chǎng)需求。力科

2019-06-10 08:13:51

我用的是AD9220采集信號(hào),這款ADC數(shù)據(jù)是并行輸出,測(cè)試的時(shí)候我給的0V輸入(VINA-VINB=0),其中有一位數(shù)據(jù)輸出的電平應(yīng)該一直是低,但是在時(shí)鐘周期內(nèi)會(huì)出現(xiàn)一段高的情況。如圖,藍(lán)色是時(shí)鐘信號(hào),黃色為我測(cè)試的其中一位數(shù)據(jù)輸出信號(hào):此款芯片的時(shí)序圖如圖:

2019-01-22 12:37:12

問一個(gè)ADC AD9628-125的問題,使用中發(fā)現(xiàn),采樣輸出信號(hào)的底噪與輸入信號(hào)功率關(guān)系密切,沒有輸入信號(hào),噪底很干凈,噪聲水平與預(yù)期相當(dāng),使用19MHz -16dBm的單音輸入測(cè)試,顯示spur

2023-12-06 06:51:41

STM32家族中的所有芯片都內(nèi)置了逐次逼近寄存器型ADC模塊.內(nèi)部大致框架如下:每次ADC轉(zhuǎn)換先進(jìn)行采樣保持,然后分多步執(zhí)行比較輸出,步數(shù)等于ADC的位數(shù),每個(gè)ADC時(shí)鐘產(chǎn)生一個(gè)數(shù)據(jù)位。說(shuō)到這里

2021-07-09 07:30:00

在使用STM32F030C8 adc進(jìn)行采集時(shí),啟動(dòng)采樣時(shí)在輸入信號(hào)會(huì)出現(xiàn)一個(gè)很大的過沖信號(hào),嘗試過單通道單次采樣,單通道重復(fù)采樣,均出現(xiàn)以上問題,下面是具體的采集波形,硬件電路信號(hào)由運(yùn)放輸出直接

2018-09-04 15:35:57

我有一個(gè)項(xiàng)目,用到AD7610BSTZ。一個(gè)現(xiàn)象是這樣的:我輸入的模擬量增加2MV,34401數(shù)字萬(wàn)用表可以測(cè)得。但是ADC轉(zhuǎn)換的數(shù)字量并沒有變化。不知道為什么? 另外一個(gè)問題是:ADC數(shù)據(jù)轉(zhuǎn)換必須要用到采集保持IC嗎?如果不用會(huì)對(duì)采集精度有影響嗎?

2018-12-03 09:09:25

輸出電阻rds和互導(dǎo)gm都會(huì)受到輸出電壓vgs的影響,那么在mos場(chǎng)效應(yīng)管的小信號(hào)模型中,輸出電阻和互導(dǎo)是否會(huì)受到交流信號(hào)的影響不斷變化?

2023-04-28 14:32:13

用verilog 語(yǔ)言來(lái)寫一個(gè)。。。當(dāng)輸入端4位數(shù)據(jù)發(fā)生變化時(shí),輸出端會(huì)輸出一個(gè)脈沖信號(hào),就僅輸出一個(gè)就行,我想用數(shù)據(jù)變化產(chǎn)生的上升沿謝謝親們了 {:1:}

2014-03-18 20:05:03

AD5326在使用中嚴(yán)格按照資料時(shí)序施加串行數(shù)據(jù),并且在寫入后經(jīng)過readback驗(yàn)證,要轉(zhuǎn)換的數(shù)確定已經(jīng)寫入輸入寄存器,但是在寫完數(shù)據(jù) stop位后給出 LDAC信號(hào),發(fā)現(xiàn)并沒有轉(zhuǎn)換后的數(shù)據(jù)輸出。想知道AD5326具體使用方法,和注意事項(xiàng)。

2019-01-04 10:17:47

AD5684的命令位+地址位+數(shù)據(jù)位一共24位,但是SPI通信只能傳送16位數(shù)據(jù)怎么辦?請(qǐng)問有沒有推薦的方案或者案例

2023-12-08 08:13:53

你好!我在數(shù)據(jù)手冊(cè)上看AD8421可以單電源供電,但是我單電源供電后,輸入正信號(hào)(0~50mV)3KHz正弦波,輸出為1.26V直流信號(hào)。輸入信號(hào)幅值和頻率變化,輸出均沒有變化。附件是原理圖:附件123.png52.7 KB

2018-09-03 14:05:31

我用的是AD9220采集信號(hào),這款ADC數(shù)據(jù)是并行輸出,測(cè)試的時(shí)候我給的0V輸入(VINA-VINB=0),其中有一位數(shù)據(jù)輸出的電平應(yīng)該一直是低,但是在時(shí)鐘周期內(nèi)會(huì)出現(xiàn)一段高的情況。

如圖,藍(lán)色是時(shí)鐘信號(hào),黃色為我測(cè)試的其中一位數(shù)據(jù)輸出信號(hào):

此款芯片的時(shí)序圖如圖:

2023-12-12 07:29:21

設(shè)計(jì)了一個(gè)ADC電路,使用ADA4930-1放大器和AD9642-210BCPZ,芯片采樣率在210M,在放大器輸入端加3MHZ正弦波輸入信號(hào),測(cè)量放大器輸出基本正常且為正弦波。FPGA控制

2018-11-12 09:54:32

Link傳輸?shù)脑O(shè)置,但沒有關(guān)于如何連接數(shù)據(jù)位的規(guī)范。塊是否處理位到差分線的攝像機(jī)鏈接映射?以上來(lái)自于谷歌翻譯以下為原文Can anyone describe how a 24-bit RGB data

2019-03-18 14:59:18

H750 UART 7數(shù)據(jù)位 + 校驗(yàn)接收數(shù)據(jù)異常的原因?如何解決?

2021-12-06 07:46:07

MODBUS rtu發(fā)送報(bào)文時(shí),是將報(bào)文轉(zhuǎn)換成二進(jìn)制再?gòu)氖椎侥┪惨来伟?b class="flag-6" style="color: red">位發(fā)送的嗎?數(shù)據(jù)位中間有沒有間隔?

2024-01-18 17:50:32

首先我們先了解下“位”與“字”的區(qū)別,位一共有兩種狀態(tài)0和1,0代表關(guān)、1代表開,對(duì)用于PLC中的X、Y、M、S,處理關(guān)/開信號(hào)的軟元件稱之為位軟元件。我們?cè)僬f(shuō)下字,字有單字和雙字,單字由16

2020-12-09 16:51:35

STM32串口如何實(shí)現(xiàn)7位數(shù)據(jù)位?

2021-12-06 07:21:02

STM32實(shí)現(xiàn)7位數(shù)據(jù)位支持需要滿足什么要求?

2021-12-03 07:40:17

各位TI的大神們:請(qǐng)教下,鄙人最近在開發(fā)一款數(shù)據(jù)采集系統(tǒng),底端的傳感器是0~10V模擬輸出的,想在TI的網(wǎng)站找一款24位的直接能采集0~10V電壓信號(hào)的芯片,竟然沒找到,絕大部分都是最大支持到

2019-06-21 08:16:49

。 aduc7061內(nèi)部應(yīng)該有兩個(gè)24位的ADC,但從讀出來(lái)的數(shù)據(jù)看,[size=13.3333330154419px]ADC0DAT好像是16位的,不像是24位的ADC輸出。[size

2018-09-27 11:43:42

如下圖所示是RF開關(guān)hmc221的電路,工作頻率2.1GHz,只使用其中一條通路RF1,RF2通過電容后經(jīng)50歐電阻到地。但是實(shí)際調(diào)試中用頻譜儀測(cè)輸出頻率和功率,在控制信號(hào)電平變化時(shí),輸出信號(hào)功率

2018-12-27 09:28:52

短路而損壞芯片!

**iEnable是數(shù)據(jù)有效標(biāo)志,可以通過屏蔽IO區(qū)域來(lái)操作少量的IO變化,從而不影響其它端口的正常工作。比如8個(gè)IO口輸入輸出各4個(gè),配置輸出時(shí)需要屏蔽掉4個(gè)輸入,否則輸入將受

2023-06-10 12:56:48

labview出串口通訊能9個(gè)數(shù)據(jù)位嗎?我單片機(jī)配置是9個(gè)數(shù)據(jù)位

2018-04-04 09:15:22

stm32中的串口通信中的USART_WordLength,數(shù)據(jù)位的長(zhǎng)度包不包括開始位哪些?

2018-10-11 17:57:54

和精度都應(yīng)當(dāng)優(yōu)于所選擇的ADC。模擬放大器不僅能放大模擬輸入信號(hào),而且還具有阻抗變化的作用。對(duì)于輸入電阻比較小的ADC,而信號(hào)源的內(nèi)阻又比較大時(shí),需要選用高輸入阻抗、低輸出阻抗的放大器,有時(shí)也可以加接電

2021-03-26 07:00:00

串口多機(jī)通訊,上位機(jī)如何設(shè)置串口9位數(shù)據(jù)位/TB8**常用的串口數(shù)據(jù)位設(shè)置只有5~8位,但對(duì)于多機(jī)通訊要求9位數(shù)據(jù)位,即要求通過設(shè)置TB8區(qū)分地址與數(shù)據(jù)的發(fā)送。**先貼一下多機(jī)通訊的過程:主機(jī)要發(fā)送

2022-02-23 07:28:55

原子哥在串口初始化中 void uart_init(u32 pclk2,u32 bound){。。。。USART1->CR1|=0X200C;//1位停止,無(wú)校驗(yàn)位.。。。。}沒有對(duì)bit12進(jìn)行或操作啊? 那豈不是到底是9位還是8位數(shù)據(jù)不確定了?謝謝指點(diǎn)!!

2019-06-13 04:35:10

我用vs2010,c++編寫了一個(gè)串口助手程序,然后為什么端口號(hào)和校驗(yàn)位下拉菜單有顯示,而波特率,數(shù)據(jù)位,停止位就沒有呢,我的方法都是一樣的啊。。。求大神指點(diǎn)

2020-03-12 03:45:07

您好:我使用ADA4930驅(qū)動(dòng)器芯片直流耦合信號(hào)驅(qū)動(dòng)ADC。當(dāng)沒有模擬信號(hào)輸入的時(shí)候,adc會(huì)采集到毛刺信號(hào)。只要有信號(hào)輸入之后,從此之后ADC就不會(huì)采到毛刺信號(hào)。請(qǐng)問是什么原因?qū)е碌摹Vx謝

2018-08-08 09:32:16

;每組輸入信號(hào)(D3~D0)的數(shù)據(jù)位寬是可自定義的,因按鍵開關(guān)個(gè)數(shù)限制,在驗(yàn)證實(shí)驗(yàn)時(shí)將其位寬定為1位。表4.1給出了對(duì)應(yīng)的真值表。原作者:語(yǔ)雀

2022-07-04 16:09:34

故障現(xiàn)象:

a、項(xiàng)目中使用AD9258-105芯片,上電默認(rèn)不進(jìn)行任何配置時(shí),通道A或通道B的某些位沒有輸出(特別是低幾bit,比如D0~D5。具體是哪些位,無(wú)規(guī)律),電壓固定在0.2V

2023-12-13 08:05:07

512bit的數(shù)據(jù)同時(shí)輸入),以達(dá)到更好的效果,但是當(dāng)前的NICE接口的讀寫數(shù)據(jù)位寬都是32bit,

我的問題:

1. 是否可以在協(xié)處理器上添加另外的數(shù)據(jù)通道,比如AIcore的專用通路?

2. 是否可以

2023-08-12 07:40:33

1、 解決方案(必要的公式、文字等)在課外實(shí)驗(yàn)中,我們選擇利用ADC對(duì)輸入的信號(hào)進(jìn)行采集,然后利用串口控制DAC的輸出,實(shí)現(xiàn)通過串口控制DAC輸出采集到的波形的功能。在本實(shí)驗(yàn)中,是通過判斷串口發(fā)送

2019-07-05 06:42:13

aci_gap_get_oob_data 得到了數(shù)據(jù)配對(duì)數(shù)據(jù)包顯示未設(shè)置 OOB 數(shù)據(jù)位。aci_gap_set_authentication_requirement(0x01 - 啟用綁定0x01 啟用 MITM0x02 僅限

2022-12-08 09:02:44

的一部分。數(shù)據(jù)采集系統(tǒng)的其他部分也可增加其靈活性,包括信號(hào)輸入接口、參考電壓接口、用于ADC的時(shí)鐘和采樣系統(tǒng)以及用于轉(zhuǎn)換后ADC輸出數(shù)據(jù)的數(shù)據(jù)管理。 通常情況下,模擬信號(hào)輸入接口共享一個(gè)通用輸入輸出(I/O

2017-12-19 17:10:08

在驅(qū)動(dòng)芯片信號(hào)端輸入信號(hào)為什么沒有輸出

2019-06-20 10:07:05

任何人都可以幫助代碼或功能,將在4位模式下接口4X20液晶和PIC18F46K22與端口1,2,3,4,而不是上或下Nybble,因?yàn)槲野l(fā)現(xiàn)的所有代碼。我已經(jīng)嘗試改變4X數(shù)據(jù)位和掩碼的移位,但是沒有成功。我希望有人有一個(gè)功能,你可以改變數(shù)據(jù)位以外的只是nbyle。謝謝!

2019-11-07 09:41:34

如何收發(fā)數(shù)據(jù)位寬度為9位的數(shù)據(jù)?

2022-01-27 06:33:31

本帖最后由 liuyongwangzi 于 2018-6-21 09:44 編輯

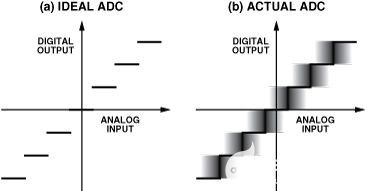

ADC采樣模擬信號(hào)提供表示輸入信號(hào)的量化數(shù)字碼。數(shù)字輸出代碼得到后處理,并且結(jié)果可以報(bào)告給使用該信息做出決定

2018-06-21 09:42:04

轉(zhuǎn)換器的數(shù)字接口狀態(tài)良好,然后檢查轉(zhuǎn)換器的輸出是否普遍代表輸入信號(hào)。之后,我再查看零輸入(轉(zhuǎn)換器噪聲)。在您測(cè)得ADC噪聲后,便可將輸入短路接地。利用DAC,您可以將數(shù)字輸入編程為模擬零輸出。 此類

2016-01-29 14:47:40

如何測(cè)量不斷變化的信號(hào)

2019-09-16 09:08:45

隨著ADC的供電電壓的不斷降低,輸入信號(hào)擺幅的不斷降低,輸入信號(hào)的共模電壓的精確控制顯得越來(lái)越重要。交流耦合輸入相對(duì)比較簡(jiǎn)單,而直流耦合輸入就比較復(fù)雜。 典型的例子是正交下變頻(混頻器)輸出

2019-06-19 06:50:39

在做一個(gè)設(shè)計(jì),需要至少14位的ADC(1.8mV的分辨率),輸入的是一個(gè)差分信號(hào)(±1.5V)和一個(gè)temp信號(hào)。有沒有單電源供電的雙通道的ADC滿足我這個(gè)設(shè)計(jì)條件啊?我在選型里面篩選了好久都沒有

2019-05-08 14:58:16

ADC 利用高抽樣率和數(shù)字信號(hào)處理技術(shù),將抽樣,量化、數(shù)字信號(hào)處理融為了一體,從而獲得了高精度的 ADC,目前可達(dá) 24 位,主要應(yīng)用于高精度數(shù)據(jù)采集特別是數(shù)字音響系統(tǒng)、多媒體、地簇勘探儀器、聲納等

2020-12-25 09:20:51

AD603級(jí)聯(lián)構(gòu)成的AGC電路的檢波電路中,小信號(hào)輸入檢波電路,Vagc輸出信號(hào)變化不明顯,如何讓輸入的小信號(hào),在Vagc的輸出也能有明顯變化。電路按照數(shù)據(jù)手冊(cè)AD603級(jí)聯(lián)構(gòu)成的AGC參考電路

2018-07-31 08:40:25

故障現(xiàn)象:a、項(xiàng)目中使用AD9258-105芯片,上電默認(rèn)不進(jìn)行任何配置時(shí),通道A或通道B的某些位沒有輸出(特別是低幾bit,比如D0~D5。具體是哪些位,無(wú)規(guī)律),電壓固定在0.2V左右;b

2018-08-14 07:38:50

的方法,信號(hào)輸入端加隔值電容。用萬(wàn)用表實(shí)測(cè)當(dāng)隔直電容前端(隔直電容前端連接AD)電壓為零時(shí),獲得ADS805E的輸出數(shù)字量不斷變化,變化范圍為20mv,可能是什么原因?qū)е碌模?b class="flag-6" style="color: red">輸入時(shí)鐘1MHz)??4.

2019-03-01 13:46:19

PCB板制版后,進(jìn)行硬件測(cè)試發(fā)現(xiàn),VCO輸出不隨輸入信號(hào)變化而變化,只保持輸出最低頻率,VCO單獨(dú)測(cè)試可用,VCO控制電壓為0V時(shí)輸出27KHZ,5V時(shí)輸出46KHZ,請(qǐng)問VCO輸出不隨輸入信號(hào)變化而變化,保持輸出27KHZ是怎么回事?

2016-10-26 10:18:14

如題,中文手冊(cè)中有一句“ADC濾波器進(jìn)行真24位信號(hào)處理,以正確的采樣頻率轉(zhuǎn)換來(lái)自ADC過采樣的多位原始數(shù)據(jù),然后從數(shù)字音頻接口輸出。”,這里的ADC濾波器的位數(shù),和ADC的位數(shù)一樣嗎?是不是WM8978的ADC輸出也是24位呢?

2019-02-14 00:19:40

圖一是“接收內(nèi)容”創(chuàng)建字符串類的屬性-顯示樣式(因?yàn)槭M(jìn)制顯示才能正常接收,否則亂碼),圖二是modbus rtu 協(xié)議的數(shù)據(jù)傳輸,圖三是我接收的傳感器傳輸?shù)钠渲幸唤M數(shù)據(jù),請(qǐng)問如何實(shí)現(xiàn)數(shù)據(jù)位的提取?謝謝

2019-03-30 15:07:31

做一個(gè)頻率電壓轉(zhuǎn)換器的仿真,lm358的輸出端有信號(hào),但是741的輸出端并沒有變化,甚至還是反向了

2018-12-22 13:01:36

圖一是“接收內(nèi)容”-創(chuàng)建-字符串類的屬性-顯示樣式(因?yàn)槭M(jìn)制顯示才能正常接收,否則亂碼),圖二是modbus rtu 協(xié)議的數(shù)據(jù)傳輸,圖三是傳感器傳輸?shù)摹敖邮諆?nèi)容”中的一組數(shù)據(jù),請(qǐng)問如何實(shí)現(xiàn)數(shù)據(jù)位的提取?謝謝

2019-03-30 15:16:17

最近正在調(diào)試AD5754,芯片電壓正常,±12,3.3v,和2.5v都正常供入。但是用FPGA寫驅(qū)動(dòng)程序是發(fā)現(xiàn),只能讀,SDO信號(hào)數(shù)據(jù)位全為0。不能夠?qū)懭爰拇嫫鳌O旅娓缴衔业牟ㄐ胃郊o(wú)標(biāo)題.JPG8.1 KB

2018-08-24 11:18:35

要檢查運(yùn)放輸入端的阻抗匹配,因?yàn)?b class="flag-6" style="color: red">輸入端的阻抗失配會(huì)改變輸出失調(diào)電壓,由于輸出幅度受到限制,因此會(huì)減小ADC的動(dòng)態(tài)范圍。 捕獲數(shù)字輸出數(shù)據(jù)以很高的頻率(1GSps甚至更高)對(duì)信號(hào)進(jìn)行采樣意味著由轉(zhuǎn)換器

2019-05-30 05:00:04

隨著ADC的供電電壓的不斷降低,輸入信號(hào)擺幅的不斷降低,輸入信號(hào)的共模電壓的精確控制顯得越來(lái)越重要。交流耦合輸入相

2010-11-26 10:27:59 4769

4769

任何通過時(shí)鐘電路進(jìn)入ADC的噪聲都能直接到達(dá)輸出端。ADC中此電路的噪聲機(jī)制可認(rèn)為是一個(gè)混頻器。當(dāng)看到噪聲時(shí),以這種方式考慮輸入就真正能洞察一切了。通過時(shí)鐘輸入進(jìn)入ADC的噪聲頻率將混入模擬輸入信號(hào),并出現(xiàn)在轉(zhuǎn)換器輸出端的FFT中。

2017-09-14 17:17:12 8

8 隨著ADC的供電電壓的不斷降低,輸入信號(hào)擺幅的不斷降低,輸入信號(hào)的共模電壓的精確控制顯得越來(lái)越重要。交流耦合輸入相對(duì)比較簡(jiǎn)單,而直流耦合輸入就比較復(fù)雜。 典型的例子是正交下變頻(混頻器)輸出到ADC

2017-12-10 12:09:24 11432

11432

將以上草圖上傳到Uno32板上,然后從MPIDE打開串行終端窗口。 ADC樣本(整數(shù)ADC輸出)以1秒的間隔打印在窗口上。您可以觀察這些數(shù)字如何隨著LDR上光線的變化而變化。如果您將手指放在LDR上并阻擋掉落在LDR上的光,則ADC輸出將突然下降。

2019-12-05 16:59:48 7889

7889

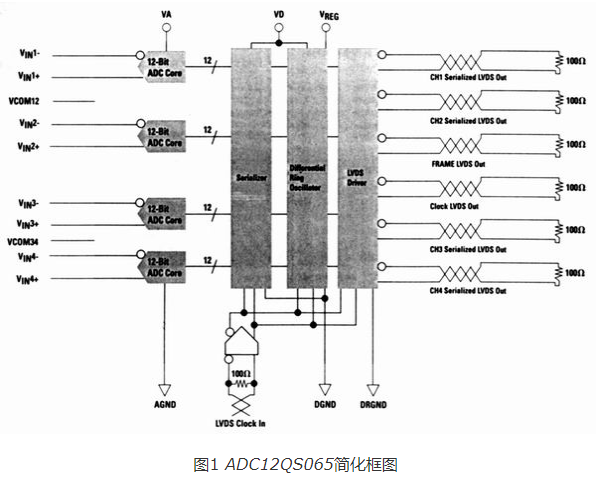

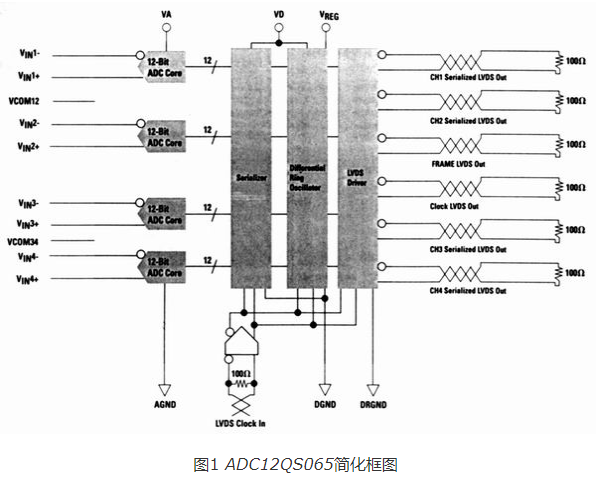

在輸入信號(hào)轉(zhuǎn)換數(shù)字數(shù)據(jù)之后,必須傳輸它們到DSP或ASIC/FPGA進(jìn)行處理。流行的全差分輸出信號(hào)傳輸是方便的。全差分的輸出信號(hào)通過兩條對(duì)稱線給出和吸收電流。這種信號(hào)傳輸?shù)囊粋€(gè)例子是LVDS(低壓差分信號(hào))格式。ADC12QS065用LVDS來(lái)解決所有這些系統(tǒng)問題(圖1)。

2020-04-04 17:43:00 2324

2324

這是一種純粹的ADC驅(qū)動(dòng)功能,無(wú)信號(hào)調(diào)理。 當(dāng)前一級(jí)的驅(qū)動(dòng)能力不夠時(shí),它為ADC提供高輸入阻抗。 這種配置的噪聲和功耗最低,因?yàn)?b class="flag-6" style="color: red">沒有附加電阻。 在單電源應(yīng)用中,信號(hào)擺幅可能會(huì)受輸入或輸出放大器裕量要求的限制。 對(duì)于差分輸入,可利用兩個(gè)單位增益驅(qū)動(dòng)器來(lái)實(shí)現(xiàn)高阻抗輸入,參見CN0307。

2020-07-13 18:02:26 5247

5247

問題:有沒有一個(gè)模塊,能讓我直接將微小的傳感器輸出訊號(hào)轉(zhuǎn)換為ADC輸入電壓?

2021-04-03 09:11:00 1820

1820

STM32系列單片機(jī)控制寄存器只支持8、9位數(shù)據(jù)位。

2021-07-23 11:15:56 5603

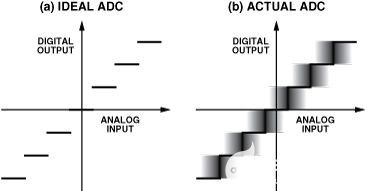

5603 這個(gè)情景真的令人很沮喪:你終于將模數(shù)轉(zhuǎn)換器 (ADC) 搭建起來(lái)并開始運(yùn)行,不過事情看起來(lái)有點(diǎn)兒不太正常。你輸入了一個(gè)電壓,不過ADC的輸出有所不同。

出了什么問題?

看起來(lái)所有的設(shè)置都沒有

2021-11-24 09:31:47 2421

2421 問題:STM32移植freemodbus 后測(cè)試時(shí),只能使用無(wú)校驗(yàn) ,設(shè)置奇偶校驗(yàn)時(shí)無(wú)法與上位機(jī)通訊解決方法如果串口助手使用串口配置為:數(shù)據(jù)位8 停止位1 有奇偶校驗(yàn)STM32需設(shè)置為:數(shù)據(jù)位

2021-12-24 18:44:23 19

19 基本輸入輸出Proteus圖沒有代碼

2022-12-30 16:48:39 0

0 所有模數(shù)轉(zhuǎn)換器(ADC)都有一定量的輸入參考噪聲,建模為與無(wú)噪聲ADC輸入串聯(lián)的噪聲源。不要將折合到輸入端的噪聲與量化噪聲混淆,量化噪聲僅在ADC處理時(shí)變信號(hào)時(shí)才有意義。在大多數(shù)情況下,輸入噪聲越少越好;然而,在某些情況下,輸入噪聲實(shí)際上有助于實(shí)現(xiàn)更高的分辨率。

2023-02-03 16:08:37 1267

1267

無(wú)源探頭(探極)置于×10檔時(shí),輸入示波器的信號(hào)如何變化?

2023-02-07 12:33:58 666

666

本應(yīng)用筆記說(shuō)明,ADC根據(jù)信號(hào)輸入電平產(chǎn)生不同水平的噪聲功率,并且ADC噪聲會(huì)影響小信號(hào)和大信號(hào)電平極端情況下的整體接收器響應(yīng)。如果在接收器設(shè)計(jì)中未正確考慮ADC噪聲(和失真)功率的級(jí)聯(lián)貢獻(xiàn),則轉(zhuǎn)換器可能超出或低于任何特定應(yīng)用的規(guī)定。

2023-02-25 11:40:40 1050

1050

在采樣或子采樣接收器設(shè)計(jì)中使用高性能奈奎斯特模數(shù)轉(zhuǎn)換器(ADC)時(shí),RF設(shè)計(jì)人員需要了解ADC在小信號(hào)和大信號(hào)輸入下的噪聲性能。接收器必須滿足這兩個(gè)信號(hào)電平極端下的靈敏度和阻塞(高電平干擾)要求

2023-03-02 15:15:10 930

930

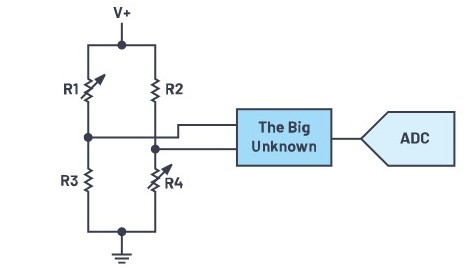

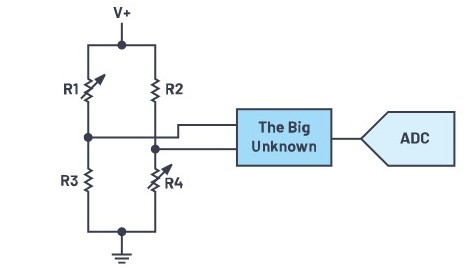

數(shù)據(jù)采集和通用測(cè)試測(cè)量設(shè)備中使用的精密信號(hào)鏈必須適應(yīng)寬廣的輸入電平范圍。信號(hào)鏈可能需要提供高輸入阻抗,同時(shí)支持增益和衰減,并調(diào)整共模電平以確保信號(hào)落在ADC的適當(dāng)輸入范圍內(nèi) 。 圖1中的原理圖顯示

2023-07-07 18:40:03 531

531

FPGA相比MCU而言,在數(shù)據(jù)位操作上有很明顯的優(yōu)勢(shì)。FPGA支持任意位拼接以及數(shù)據(jù)截取操作。本篇主要是總結(jié)和分享一些對(duì)數(shù)據(jù)位操作的實(shí)用語(yǔ)法技巧。內(nèi)容不多,其中最最最重要的內(nèi)容是數(shù)據(jù)的動(dòng)態(tài)位截取操作。

2023-10-01 17:12:00 660

660

怎么辦?晶振沒有信號(hào)輸出? 晶振作為電子設(shè)備中常見的元器件之一,在電子系統(tǒng)中起到時(shí)鐘信號(hào)供應(yīng)的重要作用。然而,有時(shí)我們可能會(huì)遇到晶振沒有信號(hào)輸出的問題,這會(huì)嚴(yán)重影響設(shè)備的正常運(yùn)行。本文將針對(duì)這一

2024-01-25 13:51:17 125

125

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論