現代高速運算放大器 (op amps) 的建立時間都為幾納秒左右。這個時間是如此的短暫。因此,要想在某個合理誤差范圍內對其進行測定,不僅僅對自動測試設備(ATE)是一個難題,即使在工作臺上也難以完成。今天的運算放大器產品說明書中,常常以模擬值的形式給出產品的建立時間數據,原因是在工作臺上對其進行測試需要安裝更多硬件設備,而這會增加測定的成本和難度。傳統的高速示波器僅有一個10比特模數轉換器,限制了測量分辨率(最大0.1%)。

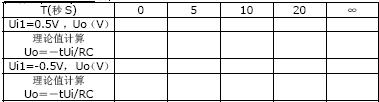

?

本文將介紹一種新方法,其經過證明可以有效地完成這些測量工作。它是一種相對低成本、簡單的建立時間測量方法。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相對速度上。

?

受測器件的步進輸入

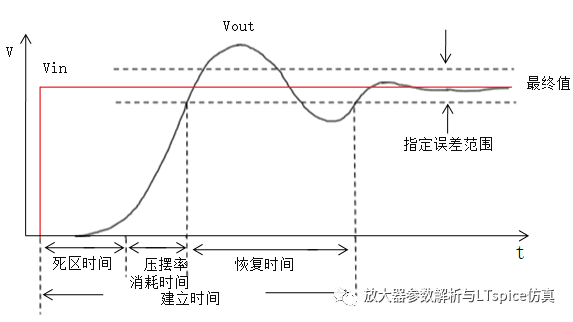

本文中,建立時間是指使用某個理想步進輸入,到受測器件(DUT)進入并維持在某個規定誤差范圍(終值對稱)內的時間。理想步進輸入很容易在模擬中產生得到,但在實驗室中卻沒有能夠產生理想步進波形的儀器設備。即使在理想條件下,過阻尼和高阻尼儀器的輸出可能需要一些RC時間常量,以單調地穩定在0.1%終值范圍以內。

?

對于一些欠阻尼系統而言,步進波形會超出終值,并且可能會出現振鈴。實際上,即使是高阻尼系統也會有欠阻尼現象。一般而言,步進波形下降越快,過沖和振鈴也就越多。之后,這種非理想狀況傳播至受測器件的測量輸出波形。幸運的是,利用計算機日志記錄輸入和輸出數據,通過排列這兩種數據并用輸出減去輸入便可實現輸出標準化(受測器件使用同相單位增益配置)。

?

平底脈沖生成器

波形生成器降沿用作受測器件的輸入時,可以使用一個平底脈沖生成器(FBPG)來平整生成信號的低壓電平。平底脈沖生成器將降電壓鉗制接地,代價是出現更大的過沖。這樣便讓測試工程師能夠通過測試裝置調節平衡實現一定程序的控制。同樣,我們可以使用平頂脈沖生成器來平整高壓電平。

?

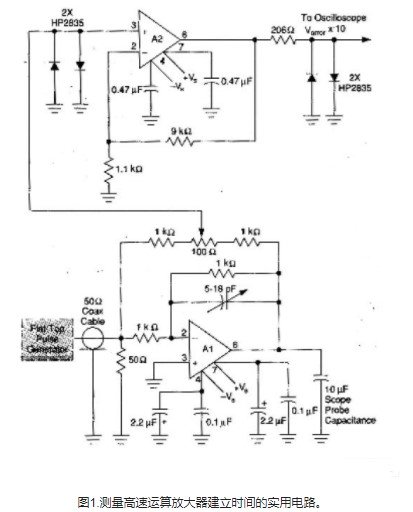

圖 1 顯示了兩個背靠背放置的高速齊納二極管,每個二極管都有一個單獨、可調節電源。一般原則是,按照如下順序啟動裝置:調節Rsupply,獲得D1/D2連接5V電壓,然后調節Vgenerator輸出電壓,讓其在2V高壓和-5V低壓之間擺動。這樣便可在2Vpp高壓電平和0V低壓電平下對輸出進行偏置。當Vgenerator為高時,D2關閉,D1開啟。在此期間,輸出電壓成為D1正向電壓(Vsupply)的函數,同時也是流經Rsupply和D1電流量的函數。當輸入為低時,D1關閉,D2開啟。在此期間,輸出電壓擺至接地電壓,同時其轉換速率與流入相應電阻器R3的電流大小成正比例關系。瞬態響應與二極管電容、反向恢復時間和正向恢復電壓有關。

?

圖 1 平底脈沖生成器 (FBPG)

?

由于二極管的非線性特性,需使用嚴密的方程式來計算DC電平和平底脈沖生成器瞬態響應。作為一種替代方法,也可以在軟件(例如:德州儀器公司的TINA-TI?)中模擬這些方程式。假設脈沖生成器的速度非常快,則輸出波形的降時間和過沖與二極管的速度和恢復時間有關,同時也與寄生電容和安裝平底脈沖生成器的印刷電路板(PCB)的電感有關。換句話說,設計人員應該選擇最快速、最健壯的二極管,并在將平底脈沖生成器用于高速波形生成時遵循優秀PCB布局原則。

?

建立時間測量的采樣保持方法

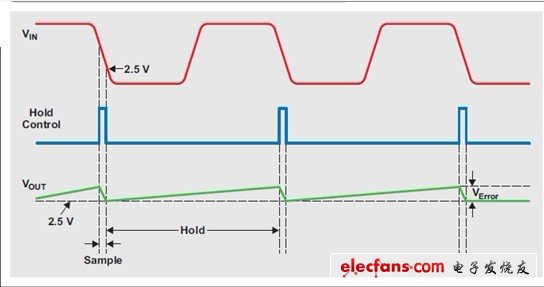

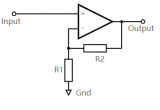

就這里介紹的例子而言,我們選擇使用TI的OPA615(見圖2)來實現建立時間測量的采樣保持(S/H)功能,這是因為:它擁有寬帶運算跨導放大器(OTA),針對低輸入偏置電流進行了優化;另外,它還擁有快速、精確的采樣OTA(SOTA),其同時起到一個比較器和緩沖器的作用。當保持控制引腳為高時,通過SOTA在電容器(CHOLD)上對模擬輸入(VIN)采樣。當保持控制引腳變低時,CHOLD電壓在輸出(VOUT)端得到保持和反射。采樣期間,CHOLD電壓被調節至輸入實時電壓電平。如果輸入和CHOLD之間的差異較大,并且采樣時間僅為幾納秒,則要求高轉換速率。保持期間,CHOLD電壓始終充電/放電,原因是其漏電流和OTA所需的偏置電流。電流反饋環路可確保SOTA轉換速率足以捕獲VIN的正確電壓電平。

?

圖 2 采樣保持(S/H)電路

?

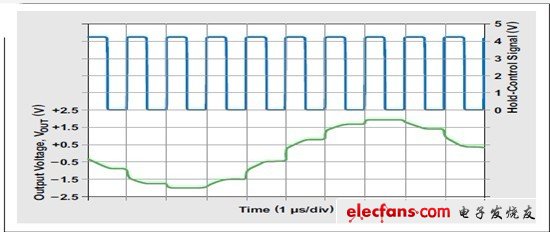

圖3顯示了一個100kHz正弦波輸入S/H輸出的例子。我們可以使用一個波形生成器來產生受測器件的輸入階梯函數,并將S/H信號與該階梯函數同步。S/H電路可用于捕獲受測器件輸出波形上的各個點。如果有一個與輸出同步的標記輸出,則任何任意波形生成器都有效,從而產生非常合適的保持控制信號。舉例測試使用一個Tektronix AWG610,其擁有2.6 Gbps的采樣時間和100 ps的最小標記步進,讓它適用于大多數高速運算放大器建立時間的測量工作。

?

圖 3 100kHz正弦波的舉例1MHz S/H輸出

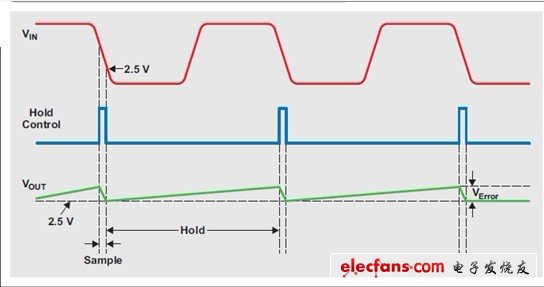

圖4描述了如何使用一個S/H電路捕獲曲線上的各個點,而該S/H電路將標記用作保持控制信號。設計人員可以通過移動標記位置來捕獲曲線上的連續各點。在記錄完所有點以后,可將S/H曲線繪制出來進行分析。使用MATLAB?或者LabVIEW?等軟件對波形生成器編程,以此來改變標記和記錄結果,是一種非常簡單的方法。將標記設定在位置1后,S/H電路追蹤標記為高時的VIN電壓電平,并在標記為低時保持該值。在位置1處,輸出保持在1V。在位置2處,輸出保持在0.2V。

?

圖 4 AWG610輸出的標記同步例子

?

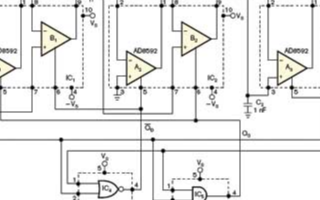

圖5顯示了建立時間測量的測試裝置,其使用AWG610和OPA615實現S/H功能。所有信號線路均為50Ω。波形生成器輸出用作測試信號,并使用兩個S/H電路:一個測量受測器件(OPA656)的輸入,另一個測量受測器件的輸出。數字萬用表(DMM)用于記錄各個保持值。

?

圖 5 建立時間測量測試裝置

例如,我們對100 ns的建立時間進行測量。假設波形生成器經過了編程,目的是不斷輸出50%占空比的方波,持續時間為200ns。標記最初被設定在波形生成器輸出的降沿開端處。生成器持續工作(執行許多個采樣和保持周期),而S/H電路對其輸出電壓求積分,以獲得一個穩定的DC值。之后,由DMM記錄該值,然后測試工程師將標記移至下一個位置,重復前面的周期,直到記錄完100 ns的數據為止。

?

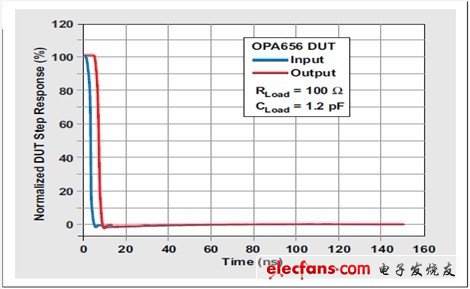

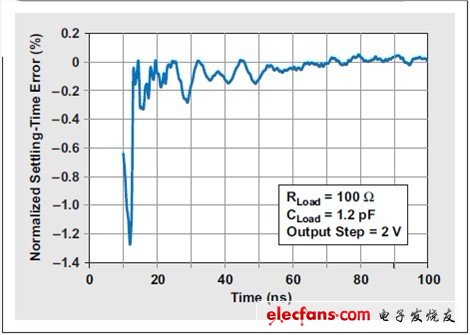

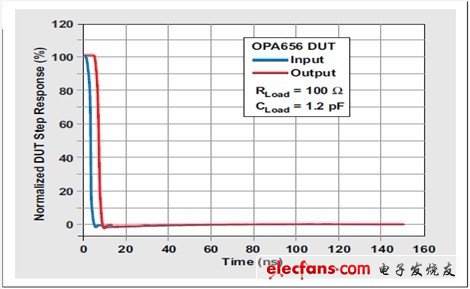

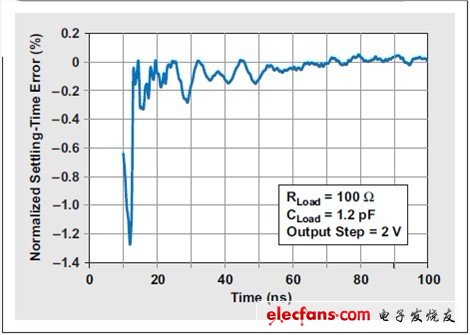

圖6顯示了使用圖5所示測試裝置所得結果的波形圖。為了獲得建立時間誤差波形,對DC誤差進行補償,并對輸出進行輸入標準化。圖7顯示了所得結果。

?

圖 6 運算放大器輸入和輸出階躍波形

?

局限性與挑戰

需要時刻謹記的是,這里介紹的測試裝置存在一些局限性。如果有疑問,設計人員應始終使用下列方程式:

I = CHOLD × dv/dt

使用該方程式時,應根據下列3個因素選擇初始CHOLD的大小:

1、保持期間,OTA偏置電流會流入或者流出電容器,從而影響保持電壓的準確性。

2、由于電容器會因偏置電流而出現壓降,應根據測量應達到的誤差百分比選擇三角接線電壓。

3、增量時間為采樣電壓保持的時間,不能長于要測量的計劃建立時間。

?

例如,下列條件下CHOLD不能小于50 pF:OTA偏置電流為0.5 μA;欲達到1-VPP信號0.1%以下的誤差;要測量的時長為100 ns。

?

其他考慮因素

采樣時間的長短會極大影響測量結果。保持期間,采樣電容器電壓始終會偏離于預計DC值,因為OTA要求偏置電流。之后,電壓被再調節回到采樣期間的預計DC值。因此,讀取S/H電路輸出的DMM必需使用這種三角波形的平均值。圖8描述了這種現象。要想減小這種誤差,需最小化保持時間,并最大化電容器尺寸。記住,采樣電容器越大,充電電荷積分獲得穩定DC值所需的S/H周期(積分時間)也就越多。

?

圖 7 運算放大器標準化穩定誤差

圖 8 采樣電容器的充電漏泄

?

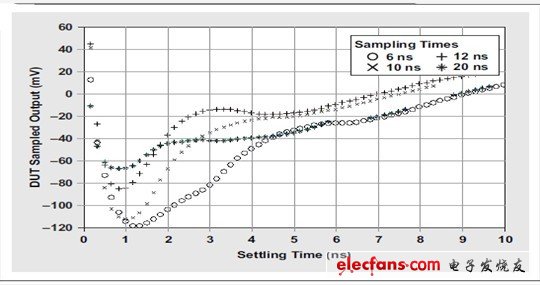

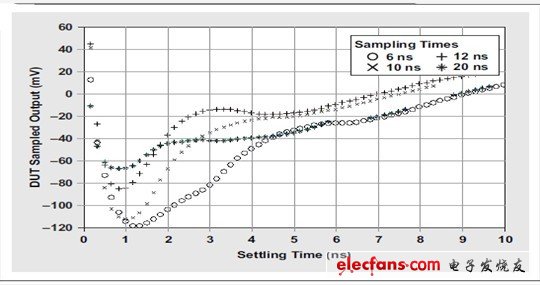

當然,增加采樣時間并不能緩解漏電問題。應使用最小采樣時間,以保證SOTA保持時間延遲,并確保追蹤S/H電路輸入的同時有足夠的時間采樣電容器的充電/放電。圖9顯示了相同保持和積分時間使用不同采樣時間時,所記錄的運算放大器建立時間。這些結果均根據一個6GHz、10比特示波器的相同波形測量得到,其顯示最大過沖為-60mV。使用20ns采樣時間的測量結果與該示波器顯示情況相匹配,但需對結果使用大濾波。相反,使用6ns的測量僅使用了小濾波,但產生了更大的過沖,其為測量中產生的人為現象。

?

圖 9 不同采樣時間測量得建立時間

?

結論

測量建立時間的方法有很多。本文為您介紹了一種簡單但卻準確的測量方法,它使用一個相對快速的波形生成器和一個S/H電路。了解這種方法存在的局限性以后,使用者便能夠對所有測量參數進行必要的調整,從而獲得給定時間范圍和預計準確度的最佳結果。

?

本文將介紹一種新方法,其經過證明可以有效地完成這些測量工作。它是一種相對低成本、簡單的建立時間測量方法。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相對速度上。

?

受測器件的步進輸入

本文中,建立時間是指使用某個理想步進輸入,到受測器件(DUT)進入并維持在某個規定誤差范圍(終值對稱)內的時間。理想步進輸入很容易在模擬中產生得到,但在實驗室中卻沒有能夠產生理想步進波形的儀器設備。即使在理想條件下,過阻尼和高阻尼儀器的輸出可能需要一些RC時間常量,以單調地穩定在0.1%終值范圍以內。

?

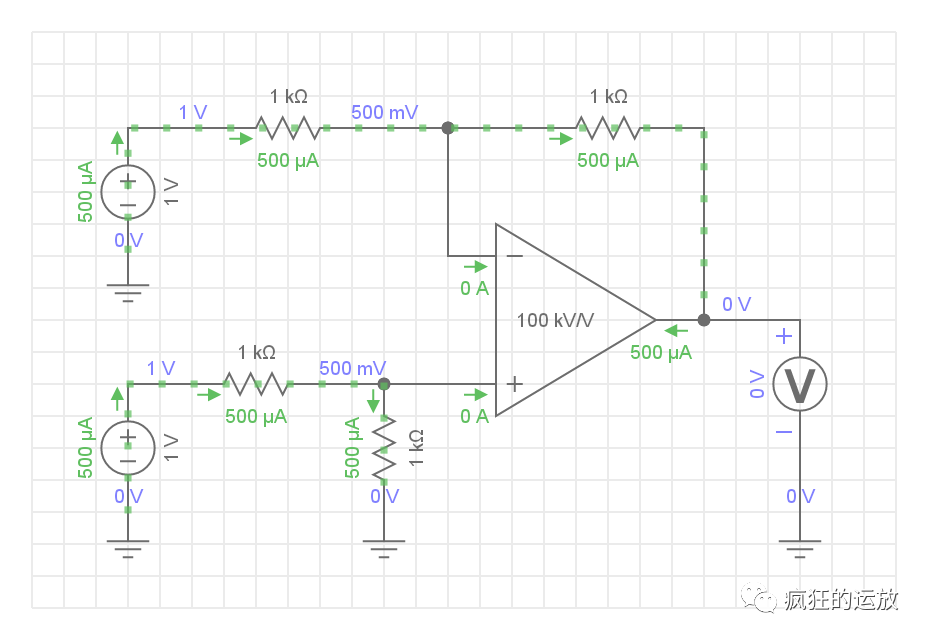

對于一些欠阻尼系統而言,步進波形會超出終值,并且可能會出現振鈴。實際上,即使是高阻尼系統也會有欠阻尼現象。一般而言,步進波形下降越快,過沖和振鈴也就越多。之后,這種非理想狀況傳播至受測器件的測量輸出波形。幸運的是,利用計算機日志記錄輸入和輸出數據,通過排列這兩種數據并用輸出減去輸入便可實現輸出標準化(受測器件使用同相單位增益配置)。

?

平底脈沖生成器

波形生成器降沿用作受測器件的輸入時,可以使用一個平底脈沖生成器(FBPG)來平整生成信號的低壓電平。平底脈沖生成器將降電壓鉗制接地,代價是出現更大的過沖。這樣便讓測試工程師能夠通過測試裝置調節平衡實現一定程序的控制。同樣,我們可以使用平頂脈沖生成器來平整高壓電平。

?

圖 1 顯示了兩個背靠背放置的高速齊納二極管,每個二極管都有一個單獨、可調節電源。一般原則是,按照如下順序啟動裝置:調節Rsupply,獲得D1/D2連接5V電壓,然后調節Vgenerator輸出電壓,讓其在2V高壓和-5V低壓之間擺動。這樣便可在2Vpp高壓電平和0V低壓電平下對輸出進行偏置。當Vgenerator為高時,D2關閉,D1開啟。在此期間,輸出電壓成為D1正向電壓(Vsupply)的函數,同時也是流經Rsupply和D1電流量的函數。當輸入為低時,D1關閉,D2開啟。在此期間,輸出電壓擺至接地電壓,同時其轉換速率與流入相應電阻器R3的電流大小成正比例關系。瞬態響應與二極管電容、反向恢復時間和正向恢復電壓有關。

?

圖 1 平底脈沖生成器 (FBPG)

?

由于二極管的非線性特性,需使用嚴密的方程式來計算DC電平和平底脈沖生成器瞬態響應。作為一種替代方法,也可以在軟件(例如:德州儀器公司的TINA-TI?)中模擬這些方程式。假設脈沖生成器的速度非常快,則輸出波形的降時間和過沖與二極管的速度和恢復時間有關,同時也與寄生電容和安裝平底脈沖生成器的印刷電路板(PCB)的電感有關。換句話說,設計人員應該選擇最快速、最健壯的二極管,并在將平底脈沖生成器用于高速波形生成時遵循優秀PCB布局原則。

?

建立時間測量的采樣保持方法

就這里介紹的例子而言,我們選擇使用TI的OPA615(見圖2)來實現建立時間測量的采樣保持(S/H)功能,這是因為:它擁有寬帶運算跨導放大器(OTA),針對低輸入偏置電流進行了優化;另外,它還擁有快速、精確的采樣OTA(SOTA),其同時起到一個比較器和緩沖器的作用。當保持控制引腳為高時,通過SOTA在電容器(CHOLD)上對模擬輸入(VIN)采樣。當保持控制引腳變低時,CHOLD電壓在輸出(VOUT)端得到保持和反射。采樣期間,CHOLD電壓被調節至輸入實時電壓電平。如果輸入和CHOLD之間的差異較大,并且采樣時間僅為幾納秒,則要求高轉換速率。保持期間,CHOLD電壓始終充電/放電,原因是其漏電流和OTA所需的偏置電流。電流反饋環路可確保SOTA轉換速率足以捕獲VIN的正確電壓電平。

?

圖 2 采樣保持(S/H)電路

?

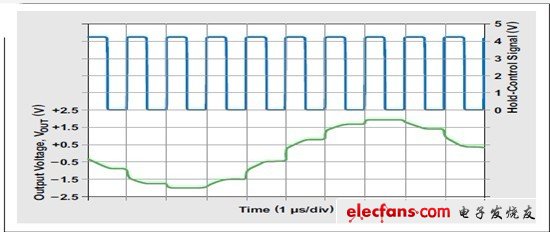

圖3顯示了一個100kHz正弦波輸入S/H輸出的例子。我們可以使用一個波形生成器來產生受測器件的輸入階梯函數,并將S/H信號與該階梯函數同步。S/H電路可用于捕獲受測器件輸出波形上的各個點。如果有一個與輸出同步的標記輸出,則任何任意波形生成器都有效,從而產生非常合適的保持控制信號。舉例測試使用一個Tektronix AWG610,其擁有2.6 Gbps的采樣時間和100 ps的最小標記步進,讓它適用于大多數高速運算放大器建立時間的測量工作。

?

圖 3 100kHz正弦波的舉例1MHz S/H輸出

圖4描述了如何使用一個S/H電路捕獲曲線上的各個點,而該S/H電路將標記用作保持控制信號。設計人員可以通過移動標記位置來捕獲曲線上的連續各點。在記錄完所有點以后,可將S/H曲線繪制出來進行分析。使用MATLAB?或者LabVIEW?等軟件對波形生成器編程,以此來改變標記和記錄結果,是一種非常簡單的方法。將標記設定在位置1后,S/H電路追蹤標記為高時的VIN電壓電平,并在標記為低時保持該值。在位置1處,輸出保持在1V。在位置2處,輸出保持在0.2V。

?

圖 4 AWG610輸出的標記同步例子

?

圖5顯示了建立時間測量的測試裝置,其使用AWG610和OPA615實現S/H功能。所有信號線路均為50Ω。波形生成器輸出用作測試信號,并使用兩個S/H電路:一個測量受測器件(OPA656)的輸入,另一個測量受測器件的輸出。數字萬用表(DMM)用于記錄各個保持值。

?

圖 5 建立時間測量測試裝置

例如,我們對100 ns的建立時間進行測量。假設波形生成器經過了編程,目的是不斷輸出50%占空比的方波,持續時間為200ns。標記最初被設定在波形生成器輸出的降沿開端處。生成器持續工作(執行許多個采樣和保持周期),而S/H電路對其輸出電壓求積分,以獲得一個穩定的DC值。之后,由DMM記錄該值,然后測試工程師將標記移至下一個位置,重復前面的周期,直到記錄完100 ns的數據為止。

?

圖6顯示了使用圖5所示測試裝置所得結果的波形圖。為了獲得建立時間誤差波形,對DC誤差進行補償,并對輸出進行輸入標準化。圖7顯示了所得結果。

?

圖 6 運算放大器輸入和輸出階躍波形

?

局限性與挑戰

需要時刻謹記的是,這里介紹的測試裝置存在一些局限性。如果有疑問,設計人員應始終使用下列方程式:

I = CHOLD × dv/dt

使用該方程式時,應根據下列3個因素選擇初始CHOLD的大小:

1、保持期間,OTA偏置電流會流入或者流出電容器,從而影響保持電壓的準確性。

2、由于電容器會因偏置電流而出現壓降,應根據測量應達到的誤差百分比選擇三角接線電壓。

3、增量時間為采樣電壓保持的時間,不能長于要測量的計劃建立時間。

?

例如,下列條件下CHOLD不能小于50 pF:OTA偏置電流為0.5 μA;欲達到1-VPP信號0.1%以下的誤差;要測量的時長為100 ns。

?

其他考慮因素

采樣時間的長短會極大影響測量結果。保持期間,采樣電容器電壓始終會偏離于預計DC值,因為OTA要求偏置電流。之后,電壓被再調節回到采樣期間的預計DC值。因此,讀取S/H電路輸出的DMM必需使用這種三角波形的平均值。圖8描述了這種現象。要想減小這種誤差,需最小化保持時間,并最大化電容器尺寸。記住,采樣電容器越大,充電電荷積分獲得穩定DC值所需的S/H周期(積分時間)也就越多。

?

圖 7 運算放大器標準化穩定誤差

圖 8 采樣電容器的充電漏泄

?

當然,增加采樣時間并不能緩解漏電問題。應使用最小采樣時間,以保證SOTA保持時間延遲,并確保追蹤S/H電路輸入的同時有足夠的時間采樣電容器的充電/放電。圖9顯示了相同保持和積分時間使用不同采樣時間時,所記錄的運算放大器建立時間。這些結果均根據一個6GHz、10比特示波器的相同波形測量得到,其顯示最大過沖為-60mV。使用20ns采樣時間的測量結果與該示波器顯示情況相匹配,但需對結果使用大濾波。相反,使用6ns的測量僅使用了小濾波,但產生了更大的過沖,其為測量中產生的人為現象。

?

圖 9 不同采樣時間測量得建立時間

?

結論

測量建立時間的方法有很多。本文為您介紹了一種簡單但卻準確的測量方法,它使用一個相對快速的波形生成器和一個S/H電路。了解這種方法存在的局限性以后,使用者便能夠對所有測量參數進行必要的調整,從而獲得給定時間范圍和預計準確度的最佳結果。

電子發燒友App

電子發燒友App

評論