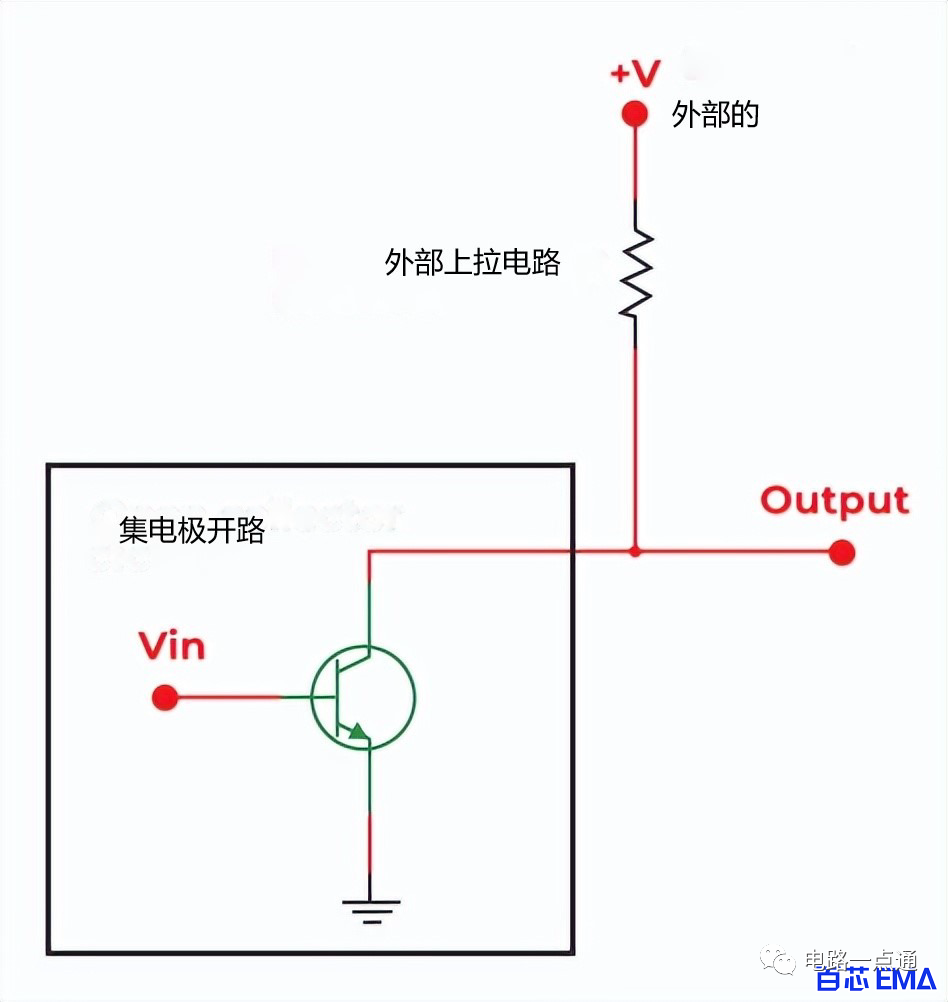

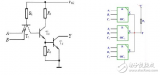

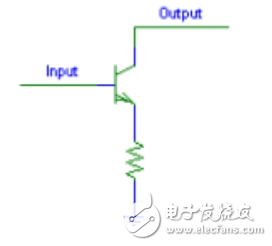

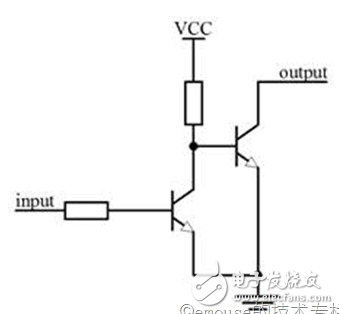

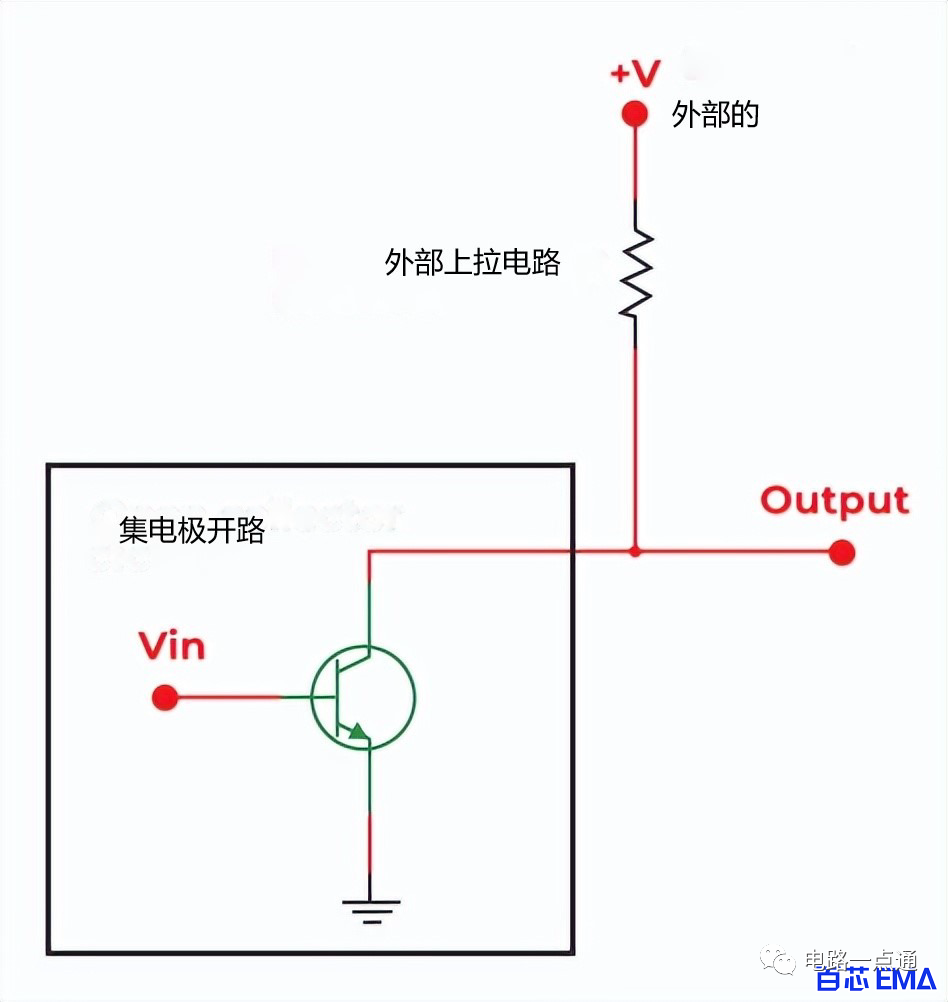

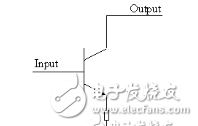

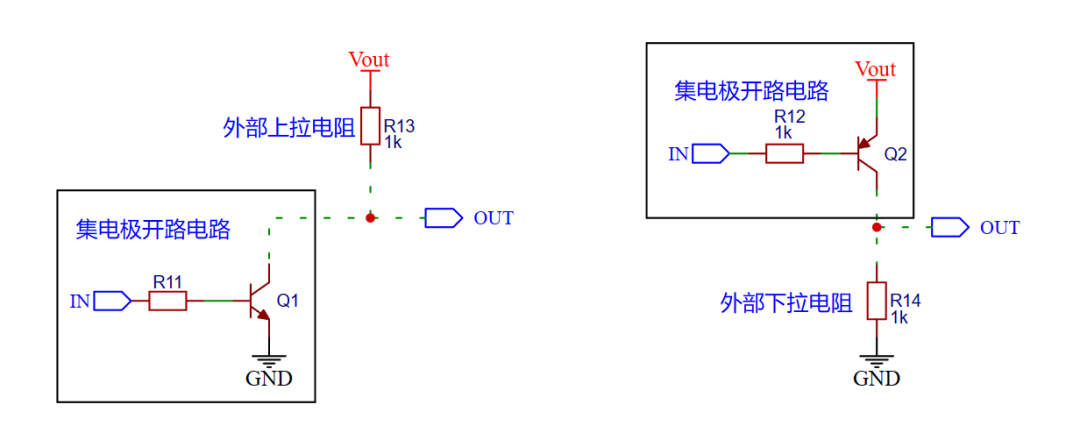

我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做集電極開(kāi)路(左邊的三極管為反相之用,使輸入為“0”時(shí),輸出也為“0”)。對(duì)于圖1,當(dāng)左端

2022-11-21 10:37:35 5971

5971 集電極開(kāi)路電路、集電極開(kāi)路晶體管電路、集電極開(kāi)路工作原理、集電極開(kāi)路TTL、集電極開(kāi)路輸出接線(xiàn)圖、集電極開(kāi)路優(yōu)缺點(diǎn)。

2023-02-01 08:59:17 529

529 今天給大家分享的是:集電極開(kāi)路電路、集電極開(kāi)路晶體管電路、集電極開(kāi)路工作原理、集電極開(kāi)路TTL、集電極開(kāi)路輸出接線(xiàn)圖、集電極開(kāi)路優(yōu)缺點(diǎn)。

2023-02-06 11:54:41 2842

2842

今天給大家分享的是:集電極開(kāi)路電路、集電極開(kāi)路晶體管電路、集電極開(kāi)路工作原理、集電極開(kāi)路TTL、集電極開(kāi)路輸出接線(xiàn)圖、集電極開(kāi)路優(yōu)缺點(diǎn)。

2023-07-17 09:03:55 2322

2322

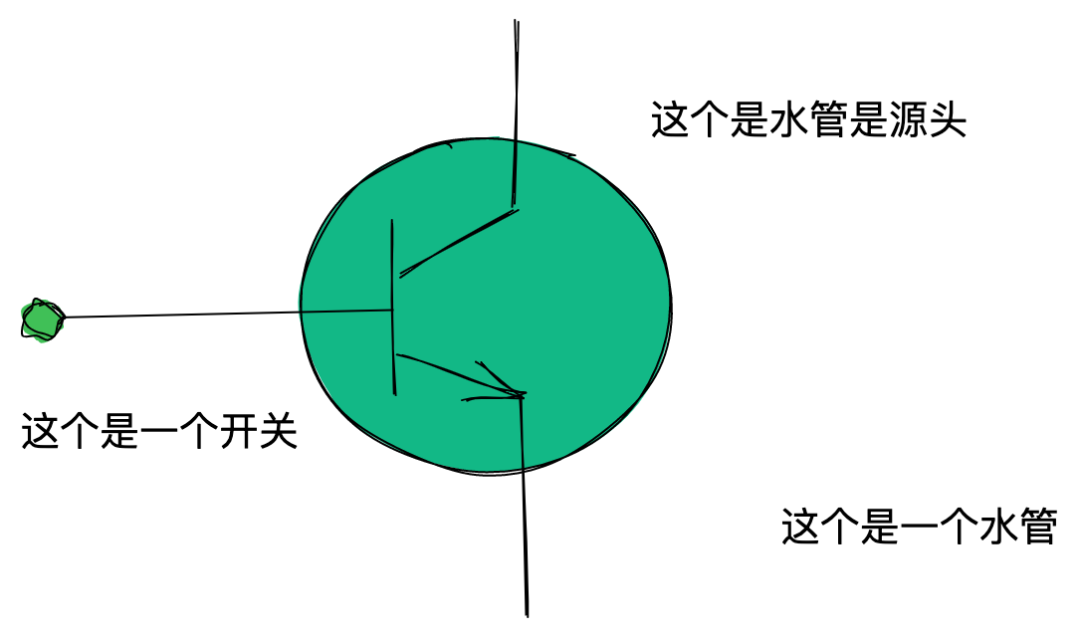

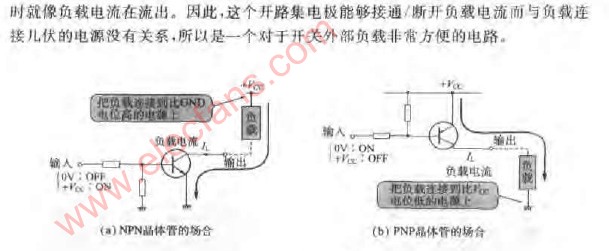

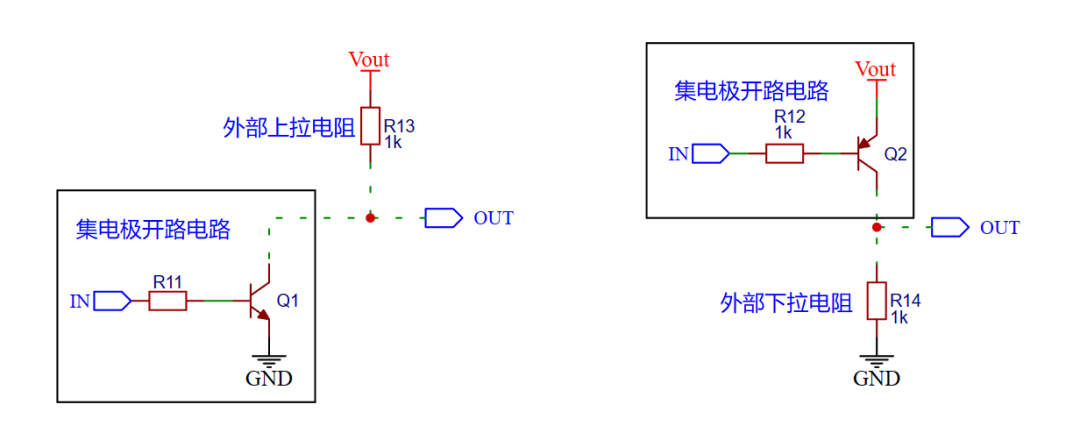

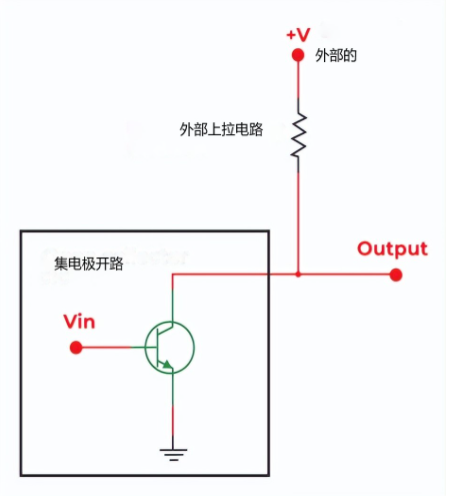

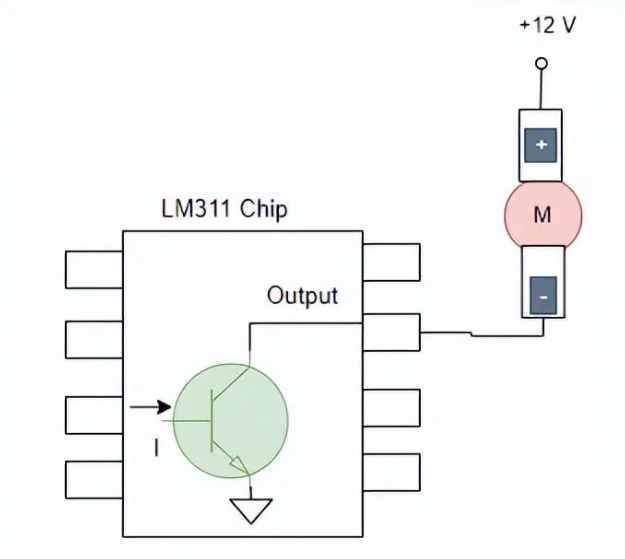

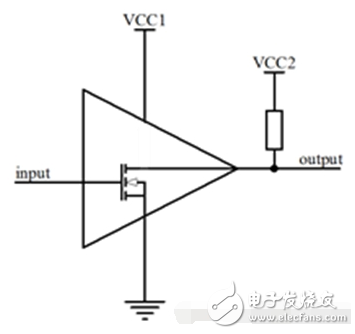

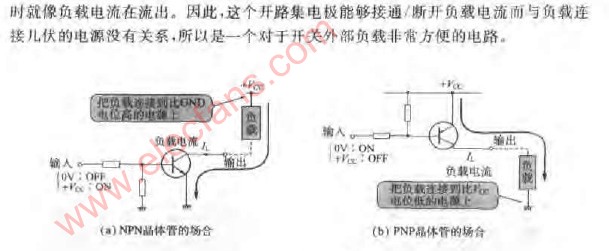

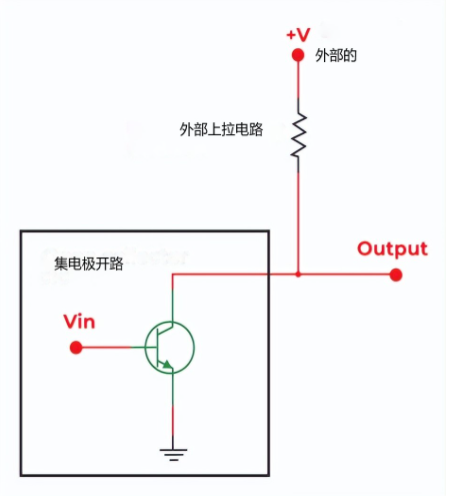

集電極開(kāi)路就像是一個(gè)開(kāi)關(guān),其一端連接電源或接地。集電極開(kāi)路電路常用在集成電路的輸出,其輸出可以根據(jù)使用的晶體管類(lèi)型(NPN型或PNP型)為外圍提供灌電流和拉電流能力。

2023-07-21 10:00:28 793

793

漏極開(kāi)路上拉電阻取值為何不能很大或很小?開(kāi)關(guān)電源布線(xiàn)注意哪些?為何用萬(wàn)用表量電路板的電阻時(shí)需斷電?

2021-11-12 07:59:46

集電極開(kāi)路 漏極開(kāi)路 推挽 上拉電阻 弱上拉 三態(tài)門(mén) 準(zhǔn)雙向口

2016-06-02 16:22:21

時(shí)給引腳或線(xiàn)路節(jié)點(diǎn)一個(gè)固定的默認(rèn)的電平。上拉電阻有時(shí)還用來(lái)增加輸出引腳的驅(qū)動(dòng)能力。當(dāng)所接電阻值比較大時(shí)稱(chēng)為弱上拉或弱下拉,否則就是強(qiáng)上拉或強(qiáng)下拉。上拉電阻應(yīng)用比較普遍,大部分OC或OD輸出都需要接上拉電阻。單片機(jī)的大部分I/O引腳也配備了弱上拉電阻。

2019-05-20 11:15:28

1、集電極開(kāi)路輸出上拉電阻電路為什么會(huì)速度降低和噪聲變大?在此基礎(chǔ)出引出了三態(tài)門(mén)?

2、多集電極開(kāi)路上拉電阻輸出實(shí)現(xiàn)了線(xiàn)或結(jié)構(gòu),有高為低,全低為高。那么什么電路結(jié)構(gòu)可以實(shí)現(xiàn)線(xiàn)與結(jié)構(gòu),射極跟隨,推挽,互補(bǔ)或者其他簡(jiǎn)單輸出電路?

2024-01-28 16:32:00

的復(fù)位閾 值時(shí),輸出有效的復(fù)位信號(hào);當(dāng)電源電壓上升到復(fù)位閾 值以上時(shí),在至少140毫秒的時(shí)間內(nèi)復(fù)位信號(hào)還將維持 有效。CS803提供漏極開(kāi)路復(fù)位輸出,CS809/810提供 CMOS復(fù)位輸出。CS803

2021-07-27 11:31:25

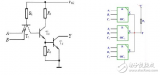

斷開(kāi),而對(duì)于P0口來(lái)說(shuō),就是高阻態(tài)了。對(duì)于漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。另一種輸出結(jié)構(gòu)

2016-06-29 11:11:00

斷開(kāi),而對(duì)于P0口來(lái)說(shuō),就是高阻態(tài)了。對(duì)于漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。另一種輸出結(jié)構(gòu)是推挽

2017-03-21 09:20:02

推挽輸出:可以輸出高,低電平,連接數(shù)字器件;開(kāi)漏輸出:輸出端相當(dāng)于三極管的集電極. 要得到高電平狀態(tài)需要上拉電阻才行. 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi)).推挽結(jié)構(gòu)一般

2022-02-08 06:50:38

內(nèi)部上拉),當(dāng)我們要使用輸入功能時(shí),只要將輸出口設(shè)置為1即可,這樣就相當(dāng)于那個(gè)開(kāi)關(guān)斷開(kāi),而對(duì)于P0口來(lái)說(shuō),就是高阻態(tài)了。對(duì)于漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管

2017-10-12 10:41:10

開(kāi)關(guān)斷開(kāi),而對(duì)于P0口來(lái)說(shuō),就是高阻態(tài)了。 對(duì)于漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。 另一種

2018-03-20 16:19:06

設(shè)置成開(kāi)路輸出模式,并設(shè)置輸出高,應(yīng)該不會(huì)有電流流過(guò)電阻吧? 理論上漏極開(kāi)路應(yīng)該不會(huì)。相當(dāng)于開(kāi)路。我的理解對(duì)嗎?

2023-06-26 07:17:51

我正在嘗試在Verilog中實(shí)現(xiàn)一個(gè)開(kāi)放收集器但是輸出0會(huì)被卡住。模塊......(inout wire sdcka,sdckb)...... always @(posedge aclk)begin

2020-03-26 08:07:16

端口需要配置為漏極開(kāi)路輸出或集電極開(kāi)路輸出,請(qǐng)問(wèn)該怎么用啊沒(méi)有相關(guān)的寄存器可以配置輸出模式

2018-08-13 06:41:32

我使用 xmc7100 芯片,使用 pwm 功能時(shí),我需要將引腳配置為開(kāi)路和漏極輸出。 當(dāng)我沒(méi)有連接上拉電阻器時(shí),示波器會(huì)檢測(cè)到應(yīng)該沒(méi)有波形,但是有波形表明開(kāi)路和漏極輸出配置不成功,為什么不呢? 能否將 pwm 引腳配置為開(kāi)路和漏極輸出?

2024-01-23 06:34:37

本帖最后由 gk320830 于 2015-3-4 23:25 編輯

【經(jīng)典】集電極開(kāi)路,漏極開(kāi)路,推挽,上拉電阻,弱上拉,三態(tài)門(mén),準(zhǔn)雙向口

2012-07-29 21:17:03

什么是集電極開(kāi)路(OC)?什么是漏極開(kāi)路(OD)?

2021-03-10 06:35:21

PLC輸入分為源型和漏型,什么是源型和漏型,是指?jìng)鞲衅鞯木w管類(lèi)型嗎?源型NPN和漏型PNP,還是指信號(hào)流入流出的方向,源極為流出,射極為流入?再或者是指信號(hào)輸出的方式,集電極輸出和射極輸出?電子專(zhuān)業(yè)常說(shuō)的有源指的是什么?什么有源負(fù)載,有源電路的。

2024-01-14 00:29:14

推挽輸出:可以輸出高,低電平,連接數(shù)字器件;推挽結(jié)構(gòu)一般是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止.開(kāi)漏輸出:輸出端相當(dāng)于三極管的集電極. 要得到高電平狀態(tài)需要上拉

2021-11-24 07:22:11

單片機(jī)I/O開(kāi)漏輸出詳解開(kāi)漏輸出:輸出端相當(dāng)于三極管的集電極. 要得到高電平狀態(tài)需要上拉電阻才行. 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi)).我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)

2021-11-24 08:11:44

1.什么是源型 漏型?什么是上拉電阻?下拉電阻?什么是 線(xiàn)驅(qū)動(dòng)輸出 集電極開(kāi)路輸出,推挽式輸出?我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接

2021-07-15 09:15:48

本帖最后由 zhihuizhou 于 2011-11-2 10:20 編輯

集電極開(kāi)路、漏極開(kāi)路、推挽、上拉電阻、弱上拉、三態(tài)門(mén)、準(zhǔn)雙向口集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極

2011-11-02 10:20:11

你好,我使用的是PIC16F18854和開(kāi)放漏極輸出模式,我的問(wèn)題是開(kāi)放漏極泄漏電流似乎沒(méi)有在數(shù)據(jù)表中指定。指定了輸入漏電流(D340,D341),但是沒(méi)有提到開(kāi)路漏極。端口部分中的電路顯示通過(guò)

2020-03-11 06:35:45

如圖電路是我從一個(gè)視頻教程里找到的,是一個(gè)光控的蜂鳴器輸出其中這個(gè)Q1的射極可以輸出去控制Q2導(dǎo)通嗎?我不明白為什么不使用Q1的集電極開(kāi)路輸出呢?這里搞一個(gè)射極輸出控制有什么含義?

2019-07-29 02:02:50

的IIC引腳設(shè)置為漏極開(kāi)路。我讀了ug471:7系列fpga selectedIO資源, ug768:7系列硬盤(pán) ug865:zynq-7000-pkg-pinout但我沒(méi)有找到將iic引腳設(shè)置為漏極開(kāi)路的方法。你可以幫幫我嗎?謝謝。

2020-05-14 06:37:27

我正在連接一個(gè)5V PIC18到2.5V設(shè)備。PIC18上的一些輸出可以是開(kāi)路漏極。我非常熟悉漏極/開(kāi)路集電極輸出,并使用了很多年。然而,說(shuō)明書(shū)上的措辭有點(diǎn)麻煩。從PIC18F66K80系列說(shuō)明書(shū)第

2020-05-12 10:28:10

我正在嘗試清理我們的代碼,現(xiàn)在正在查看我們的代碼,該代碼將兩個(gè) RMT 通道(一個(gè)輸入,一個(gè)輸出)配置為在同一引腳上工作,輸出為漏極開(kāi)路。我想我明白其中的大部分內(nèi)容,但我不明白為什么我們需要設(shè)置

2023-03-02 08:25:00

我正在使用 NUCLEO-L552ZE-Q 并制作了一個(gè)非常簡(jiǎn)單的測(cè)試電路來(lái)測(cè)試漏極開(kāi)路輸出信號(hào)。我將引腳配置為漏極開(kāi)路輸出,沒(méi)有上拉或下拉,信號(hào)通過(guò) 1K 電阻上拉至 3.3V。當(dāng)我設(shè)置引腳時(shí),我

2022-12-27 06:13:19

你好。我用的是STM32G071GBU6,VDD電壓我設(shè)計(jì)成1.8V。我有一些關(guān)于董事會(huì)的問(wèn)題。1. 3.3V GPIO 輸出控制- 我是否應(yīng)該將 MCU 的 GPIO 引腳設(shè)置為漏極開(kāi)路并連接它

2022-12-07 08:43:22

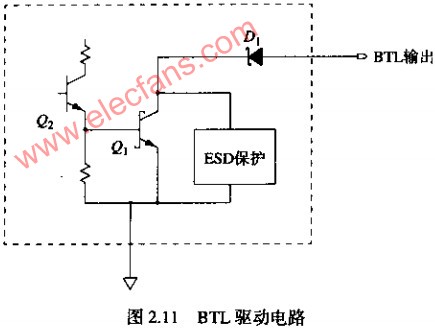

1.1.1 接口相關(guān)電路及概念1. 集電極開(kāi)路輸出在電路中常會(huì)遇到漏極開(kāi)路(Open Drain)和集電極開(kāi)路(Open Collector)兩種情形。漏極開(kāi)路電路概念中提到的“漏”是指

2022-01-14 07:57:32

的,Vcc也要在數(shù)據(jù)手冊(cè)規(guī)定的范圍內(nèi)。集電極或者漏極開(kāi)路輸出引腳是由一個(gè)晶體管控制的,當(dāng)晶體管關(guān)閉時(shí),輸出引腳為懸空狀態(tài)(開(kāi)路或者高阻態(tài))。一個(gè)常見(jiàn)的列子就是當(dāng)N溝道晶體管導(dǎo)通時(shí),輸出信號(hào)接地,但關(guān)斷時(shí),輸出

2019-04-23 08:00:00

集電極開(kāi)路輸出結(jié)構(gòu)與推挽輸出結(jié)構(gòu)有什么不同?開(kāi)漏電路有哪些特點(diǎn)?在使用開(kāi)漏電路時(shí)有哪些注意事項(xiàng)?

2021-04-19 10:41:41

1.什么是源型漏型?什么是上拉電阻?下拉電阻?什么是線(xiàn)驅(qū)動(dòng)輸出集電極開(kāi)路輸出,推挽式輸出?我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做

2021-11-23 07:22:08

推挽輸出:可以輸出高,低電平,連接數(shù)字器件;開(kāi)漏輸出:輸出端相當(dāng)于三極管的集電極. 要得到高電平狀態(tài)需要上拉電阻才行. 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi)).推挽結(jié)構(gòu)一般

2021-11-03 06:28:05

當(dāng)三極管為開(kāi)路輸出時(shí),三極管集電極通過(guò)一個(gè)負(fù)載,再?gòu)呢?fù)載另一端接到電源,-----------------------------通常我們稱(chēng)為集電極開(kāi)路輸出。那么三極管為發(fā)射極這邊來(lái)接負(fù)載時(shí),這個(gè)

2019-08-01 00:03:31

請(qǐng)問(wèn)各位:如何在QUARTUS II里將EPM1270的管腳配置為漏極開(kāi)路?

2021-04-13 15:48:08

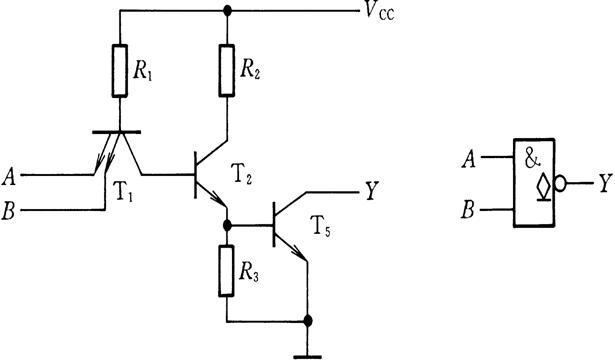

集電極開(kāi)路門(mén)和三態(tài)輸出門(mén)的應(yīng)用

一、 實(shí)訓(xùn)目的1.熟悉集電極開(kāi)路門(mén)(OC門(mén))和三態(tài)輸出門(mén)(TSL門(mén))的邏輯功能;2.熟悉用OC門(mén)構(gòu)成線(xiàn)與功能;3.熟悉用TSL門(mén)

2009-04-07 23:23:53 59

59 我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做集電極開(kāi)路(左邊的三極管為反相之用,使輸入為“0”時(shí),

2010-08-14 17:15:55 136

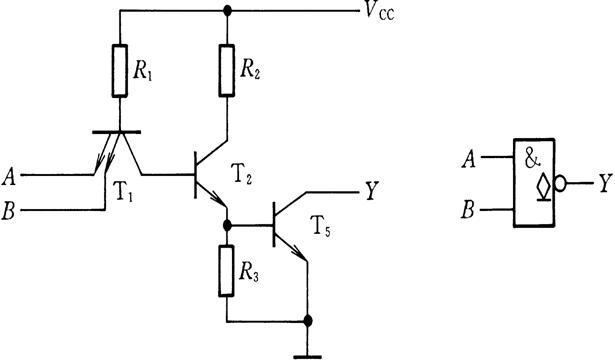

136 TTL或非門(mén)、集電極開(kāi)路門(mén)和三態(tài)門(mén)電路

1.TTL或非門(mén)

下圖為T(mén)TL或非門(mén)的邏輯電路及其代表符號(hào)。

2009-04-07 00:11:59 14317

14317

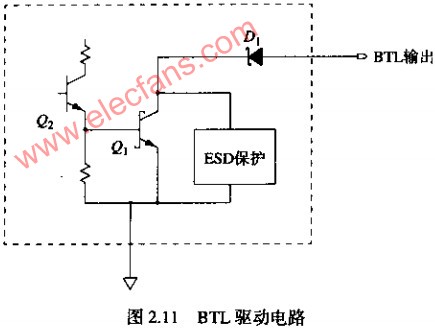

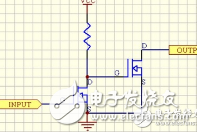

集電極開(kāi)路門(mén)

在工程實(shí)踐中將兩個(gè)門(mén)的輸出端并聯(lián)以實(shí)現(xiàn)與邏輯的功能稱(chēng)為線(xiàn)與。 考察下圖所示的情況。當(dāng)將圖中所示的兩個(gè)邏輯門(mén)的輸出連接在一起,并且

2009-04-07 00:15:19 20553

20553

集電極開(kāi)路與非門(mén)的電路和圖形符號(hào)

2009-07-15 19:02:06 7870

7870

開(kāi)路集電極電路圖

2009-08-15 17:27:30 864

864

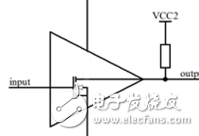

什么是漏極開(kāi)路(OD)? 對(duì)于漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管即可

2010-03-04 15:37:00 51861

51861 漏極開(kāi)路(OD)原理說(shuō)解

漏極開(kāi)路(OD),它與集電極開(kāi)路(OC)是一致的,就是把下圖的三極管改成CMOS管就是了。

2010-03-04 15:38:44 3052

3052 集電極開(kāi)路(OC)/漏極開(kāi)路(OD)輸出的結(jié)構(gòu)

A:我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)

2010-03-04 15:41:39 2810

2810 用來(lái)計(jì)算TTL集電極開(kāi)路輸出電路靜態(tài)功耗的公式如下:

其中:VT=上拉電阻的有效

2010-06-01 16:17:42 2549

2549

集電極開(kāi)路_漏極開(kāi)路_推挽_上拉電阻_弱上拉_三態(tài)門(mén)_準(zhǔn)雙向口,感興趣的小伙伴們可以瞧一瞧。

2016-11-16 18:32:35 0

0 介紹了什么是集電極開(kāi)路,漏極開(kāi)路,推挽上拉,電阻弱上拉,三態(tài)門(mén)。

2017-02-28 22:08:40 1

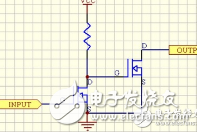

1 三極管導(dǎo)通時(shí),集電極輸出低電平;三極管關(guān)斷時(shí),集電極輸出懸空,因此該電路在工作時(shí)需要外接負(fù)載電阻和電源。只要電阻的阻值和電源電壓的數(shù)值選擇得當(dāng),就能夠做到既保證輸出的高、低電平符合要求,輸出端三極管的負(fù)載電流又不過(guò)大。

2017-11-09 12:17:53 145604

145604

漏極開(kāi)路(OD)輸出,跟集電極開(kāi)路輸出是十分類(lèi)似的。將上面的三極管換成場(chǎng)效應(yīng)管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。對(duì)于漏極開(kāi)路(OD)來(lái)說(shuō),輸出端相當(dāng)于三極管的集電極。 要得到高電平狀態(tài)需要上拉電阻才行。 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi))。

2017-11-09 14:17:01 17820

17820

集電極開(kāi)路輸出的結(jié)構(gòu),右邊的那個(gè)三極管集電極什么都不接,所以叫做集電極開(kāi)路(左邊的三極管為反相之用,使輸入為“0”時(shí),輸出也為“0”)。漏極開(kāi)路是驅(qū)動(dòng)電路的輸出三極管的集電極開(kāi)路,可以通過(guò)外接的上拉電阻提高驅(qū)動(dòng)能力。

2017-11-09 14:28:38 17067

17067

線(xiàn)與”邏輯是因?yàn)槎鄠€(gè)邏輯門(mén)的輸出三極管(場(chǎng)效應(yīng)管、二極管),共用一個(gè)上拉電阻,只要一個(gè)邏輯門(mén)輸出低電平,即集電極(漏極)開(kāi)路輸出的管子導(dǎo)通,就把上拉電阻接地,輸出低電平;只有全部輸出管截止,輸出端被上拉電阻置為高電平,這就是與邏輯的運(yùn)算結(jié)果。

2017-11-09 17:13:35 23227

23227

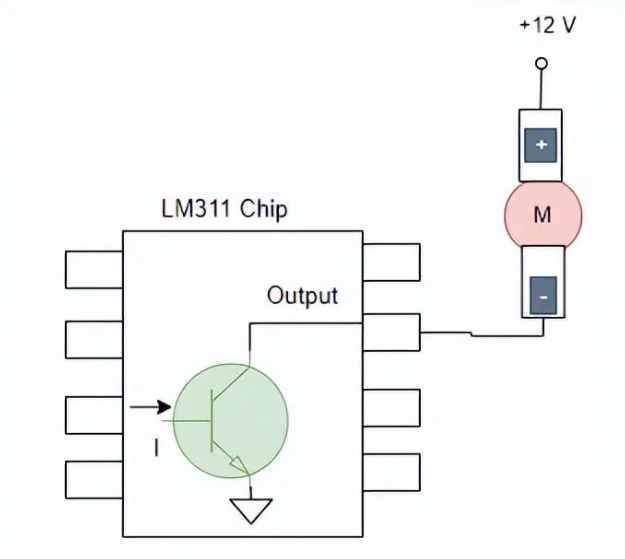

該裝置包含六個(gè)獨(dú)立的門(mén),每個(gè)門(mén)執(zhí)行緩沖功能。開(kāi)路集電極輸出需要外部上拉電阻才能正常邏輯操作。

2019-04-24 08:00:00 1

1 首先講一下集電極開(kāi)路輸出(Open-Collector),單片機(jī)I/O常用的輸出方式的開(kāi)漏輸出(Open-Drain),漏極開(kāi)路電路概念中提到的“漏”是指 MOSFET的漏極。同理,集電極開(kāi)路電路中的“集”就是指三極管的集電極。在數(shù)字電路中,分別簡(jiǎn)稱(chēng)OD門(mén)和OC門(mén)。

2019-08-26 17:30:00 12

12 集電極開(kāi)路輸出端或者M(jìn)OS管漏極輸出端其性質(zhì)都是一樣的,這種電路在數(shù)字電路中都要加上拉電阻。比如在單片機(jī)P0口其內(nèi)部驅(qū)動(dòng)電路是MOS構(gòu)成的,其結(jié)構(gòu)就是一個(gè)漏極開(kāi)路電路,其內(nèi)部沒(méi)有上拉電阻。

2019-09-28 07:00:00 8622

8622 PmodOC1是使用MMBT3904晶體管的集電極開(kāi)路BJT模塊。

2019-11-29 14:38:33 1351

1351

A、開(kāi)路集電極NPN的接線(xiàn)方式,采用內(nèi)部電源(由于采用內(nèi)部電源,所以“+24V”和“PLC”的短接片必須連接可靠,而且電流的流向?yàn)閺摹?24V”到“PLC”到控制板內(nèi)部整理電路,再到“Xi”端子,經(jīng)過(guò)外部接點(diǎn)后回到變頻器的“COM”端子):

2020-11-11 08:00:00 1

1 電子發(fā)燒友網(wǎng)為你提供什么是集電極開(kāi)路(OC)?什么是漏極開(kāi)路(OD)?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶(hù)指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-13 08:42:31 9

9 DM5438/DM7438緩沖器集電極開(kāi)路輸出資料手冊(cè)免費(fèi)下載。

2021-06-01 17:51:18 11

11 是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止.我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫

2021-10-28 17:51:00 9

9 1.什么是源型漏型?什么是上拉電阻?下拉電阻?什么是線(xiàn)驅(qū)動(dòng)輸出集電極開(kāi)路輸出,推挽式輸出?我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做

2021-11-15 13:51:02 0

0 上拉電阻才行. 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi)).我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫做集電極開(kāi)路...

2021-11-15 20:21:06 34

34 單片機(jī)I/O開(kāi)漏輸出詳解開(kāi)漏輸出:輸出端相當(dāng)于三極管的集電極. 要得到高電平狀態(tài)需要上拉電阻才行. 適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對(duì)強(qiáng)(一般20ma以?xún)?nèi)).我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)

2021-11-15 20:36:07 7

7 是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止.我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫

2021-11-16 09:21:01 21

21 是指兩個(gè)三極管分別受兩互補(bǔ)信號(hào)的控制,總是在一個(gè)三極管導(dǎo)通的時(shí)候另一個(gè)截止.我們先來(lái)說(shuō)說(shuō)集電極開(kāi)路輸出的結(jié)構(gòu)。集電極開(kāi)路輸出的結(jié)構(gòu)如圖1所示,右邊的那個(gè)三極管集電極什么都不接,所以叫

2021-12-05 10:36:05 13

13 1.1.1 接口相關(guān)電路及概念1. 集電極開(kāi)路輸出在電路中常會(huì)遇到漏極開(kāi)路(Open Drain)和集電極開(kāi)路(Open Collector)兩種情形。漏極開(kāi)路電路概念中提

2022-01-14 14:32:40 23

23 如果開(kāi)關(guān)斷開(kāi),則由于開(kāi)關(guān)電阻為無(wú)窮大(不考慮實(shí)際中的漏電流),所以流過(guò)的電流為0,因此在1k電阻上的壓降也為0,所以輸出端的電壓就是5v了,這樣就能輸出高電平了。

2022-08-31 14:18:39 1925

1925 因此集電極開(kāi)路的輸出視為NPN晶體管,它允許電流吸收到公共端。對(duì)于這樣集電極開(kāi)路電路,必須有一個(gè)電源才能使輸出正常工作。當(dāng)我們要求未連接任何電源時(shí)計(jì)算輸出電壓時(shí),電壓不會(huì)發(fā)生變化。必須計(jì)算輸出端的電壓以了解集電極開(kāi)路電路的正常運(yùn)行。

2023-01-08 15:03:01 2856

2856 今天給大家分享的是:集電極開(kāi)路電路、集電極開(kāi)路晶體管電路、集電極開(kāi)路工作原理、集電極開(kāi)路TTL、集電極開(kāi)路輸出接線(xiàn)圖、集電極開(kāi)路優(yōu)缺點(diǎn)。

2023-01-13 09:48:30 908

908 集電極開(kāi)路是各種集成電路中常見(jiàn)的輸出。集電極開(kāi)路就像一個(gè)接地或斷開(kāi)的開(kāi)關(guān)。除了將IC或任何其他晶體管的輸出連接到特定設(shè)備外,還連接到NPN晶體管的集電極開(kāi)路的基極端子,NPN晶體管的發(fā)射極端子與接地引腳內(nèi)部連接。

2023-01-16 09:16:28 756

756 具有漏極開(kāi)路輸出的低功率逆變器-74AUP1G06

2023-02-14 19:05:03 0

0 具有漏極開(kāi)路輸出的 2 輸入與門(mén)-74AHC1G09_Q100

2023-02-14 19:11:18 1

1 具有漏極開(kāi)路輸出的 2 輸入與門(mén)-74AHC1G09

2023-02-14 19:11:35 0

0 帶漏極開(kāi)路輸出的六角反相器-74LVC06A

2023-02-17 19:46:23 0

0 帶漏極開(kāi)路輸出的六角反相器-74LVC06A_Q100

2023-02-17 19:46:40 0

0 帶漏極開(kāi)路輸出的六角反相器-74HC05

2023-02-17 19:54:59 0

0 帶漏極開(kāi)路輸出的六角反相器-74LV05A

2023-03-03 19:49:05 0

0 對(duì)于電浪涌發(fā)生器,開(kāi)路輸出電壓的精度非常重要。因此,在校準(zhǔn)電浪涌發(fā)生器開(kāi)路輸出電壓時(shí),必須使用高精度的探頭。在這篇文章中,我們將介紹如何使用P6015A探頭正確校準(zhǔn)電浪涌發(fā)生器的開(kāi)路輸出電壓。

2023-04-07 14:38:19 703

703

何為集電極開(kāi)路電路?集電極開(kāi)路就像是一個(gè)開(kāi)關(guān),其一端連接電源或接地。集電極開(kāi)路電路常用在集成電路的輸出,其輸出可以根據(jù)使用的晶體管類(lèi)型(NPN型或PNP型)為外圍提供灌電流和拉電流能力。由于NPN

2023-07-31 23:07:05 890

890

ttl電路中推拉輸出,集電極開(kāi)路輸出,三態(tài)輸出有何不同?? TTL電路是一種常見(jiàn)的數(shù)字邏輯電路,在電路中經(jīng)常出現(xiàn)推拉輸出、集電極開(kāi)路輸出、三態(tài)輸出這些術(shù)語(yǔ)。這些輸出方式在不同的電路中具有不同的意義

2023-08-31 10:32:19 2131

2131 開(kāi)路電壓是什么意思? 開(kāi)路電壓指的是在電路中沒(méi)有負(fù)載負(fù)荷的情況下,測(cè)量到的電源輸出的電壓大小。在沒(méi)有負(fù)載的情況下,電源輸出電壓的測(cè)量結(jié)果往往會(huì)比有負(fù)載時(shí)高出一定比例。 為了更好地理解開(kāi)路電壓的概念

2023-12-12 14:09:47 3501

3501 集電極開(kāi)路電路是一種常見(jiàn)的邏輯電路,它的特點(diǎn)是輸出端有一個(gè)開(kāi)路的集電極。

2024-02-17 15:11:00 292

292

集電極開(kāi)路是各種集成電路中常見(jiàn)的輸出。集電極開(kāi)路就像一個(gè)接地或斷開(kāi)的開(kāi)關(guān)。除了將IC或任何其他晶體管的輸出連接到特定設(shè)備外,還連接到NPN晶體管的集電極開(kāi)路的基極端子,NPN晶體管的發(fā)射極端子與接地引腳內(nèi)部連接。

2024-02-15 09:24:00 179

179

集電極開(kāi)路門(mén)的內(nèi)部結(jié)構(gòu)設(shè)計(jì)會(huì)直接影響其開(kāi)關(guān)速度。例如,電極間的距離、材料選擇、通道長(zhǎng)度等都會(huì)對(duì)開(kāi)關(guān)速度產(chǎn)生影響。

2024-03-18 17:10:20 125

125

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論