觸發(fā)器是一個具有記憶功能的二進制信息存儲器件,是構(gòu)成多種時序電路的最基本邏輯單元。觸發(fā)器具有兩個穩(wěn)定狀態(tài),即“0”和“1”,在一定的外界信號作用下,可以從一個穩(wěn)定狀態(tài)翻轉(zhuǎn)到另一個穩(wěn)定狀態(tài)。

觸發(fā)器:具有記憶功能的基本邏輯電路,能存儲二進制信息(數(shù)字信息)。

觸發(fā)器有三個基本特性:

(1)有兩個穩(wěn)態(tài),可分別表示二進制數(shù)碼0和1,無外觸發(fā)時可維持穩(wěn)態(tài);

(2)外觸發(fā)下,兩個穩(wěn)態(tài)可相互轉(zhuǎn)換(稱翻轉(zhuǎn)),已轉(zhuǎn)換的穩(wěn)定狀態(tài)可長期保持下來,這就使得觸發(fā)器能夠記憶二進制信息,常用作二進制存儲單元。

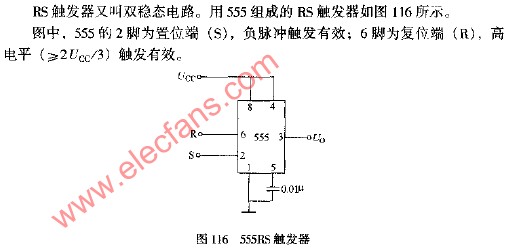

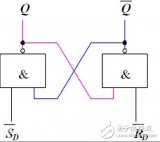

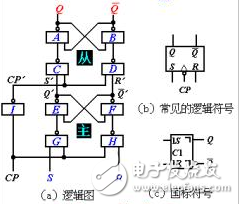

RS觸發(fā)器是構(gòu)成其它各種功能觸發(fā)器的基本組成部分。又稱為基本RS觸發(fā)器。結(jié)構(gòu)是把兩個與非門或者或非門G1、G2的輸入、輸出端交叉連接。

基本RS觸發(fā)器、同步RS觸發(fā)器、D觸發(fā)器

具有記憶功能的門電路,工作特征與上述兩種基本門和可控門數(shù)字電路,有了質(zhì)的差異。現(xiàn)在的輸出結(jié)果并不一定是“現(xiàn)在的”輸入信號所導(dǎo)致的,可能為“過去時”,即“已消失”輸入信號動作后的存儲結(jié)果,電路有了“記憶的”能力。電路的動作方式,也一改輸入信號的“長時生效”而變?yōu)椤八矔r信號”的觸發(fā)機制。

是具有記憶功能,能儲存一位二進制信息的邏輯電路。

該類電路,即數(shù)字電路中的基本RS觸發(fā)器、同步RS觸發(fā)器、同步D觸發(fā)器、主從觸發(fā)器、邊緣觸發(fā)器等和在此基礎(chǔ)之上的時序邏輯電路,而整個數(shù)字電路的大廈,也即由組合邏輯電路和時序邏輯電路所構(gòu)成。

1、基本RS觸發(fā)器

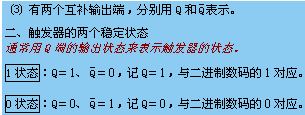

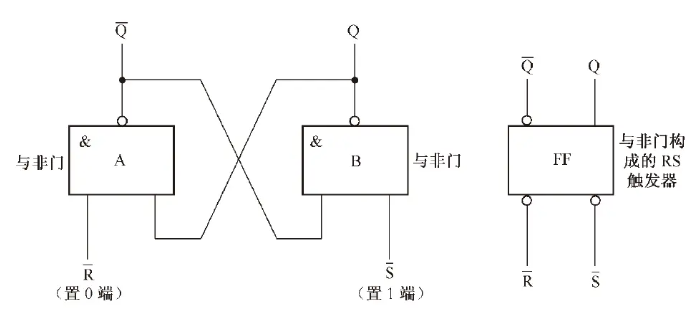

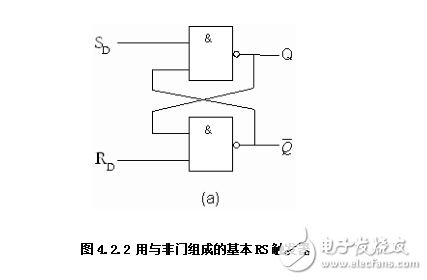

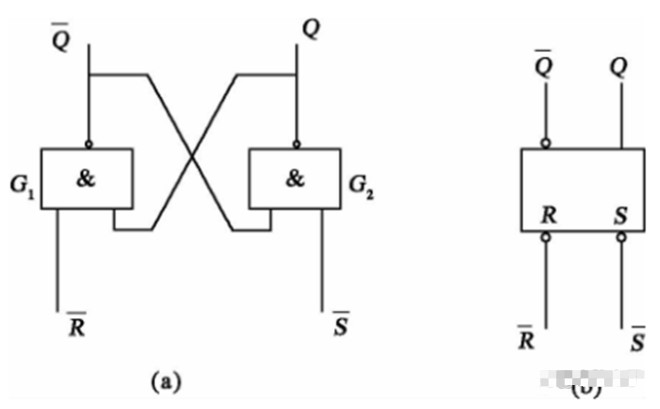

1)由與非門構(gòu)成的基本RS觸發(fā)器

由兩個與非門電路交叉耦合即構(gòu)成基本的RS觸發(fā)器,由于電路中G1、G2作用相同,習(xí)慣上用邏輯符號予以表示。

具有記憶功能門電路之基本RS觸發(fā)器、同

圖1 由與非門構(gòu)成的基本RS觸發(fā)器

/RD、/SD為觸發(fā)器的兩個輸入端,/SD稱為置位(或置1)端;/RD稱復(fù)位(或置0)端。在標注字母上方加短杠,表示低電平信號有效。觸發(fā)器還有兩個輸出端,兩者的邏輯電平相反,以Q端為基準。如Q=1,則/Q=0。

從電路結(jié)構(gòu)來看,因僅有兩個輸入端子,則輸入有四種電平組合,在合適的信號作用下,觸發(fā)器可以從一種穩(wěn)態(tài)翻轉(zhuǎn)至另一穩(wěn)態(tài)。

當/SD=0,/RD=1時,觸發(fā)器置1;

當/SD=1,/RD=0時,觸發(fā)器置0;

當/SD=0,/RD=0時,出現(xiàn)輸出競爭現(xiàn)象,為非法輸入電平(正常應(yīng)用時應(yīng)避免出現(xiàn)這種情況);

當/SD=1,/RD=1時,輸出保持不變。

綜上所述,基本RS觸發(fā)器具有置0、置1和保持功能;但輸入信號不能同時為0,是具有約束條件的觸發(fā)器。

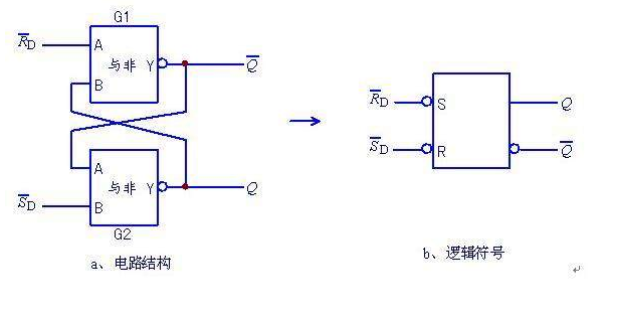

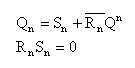

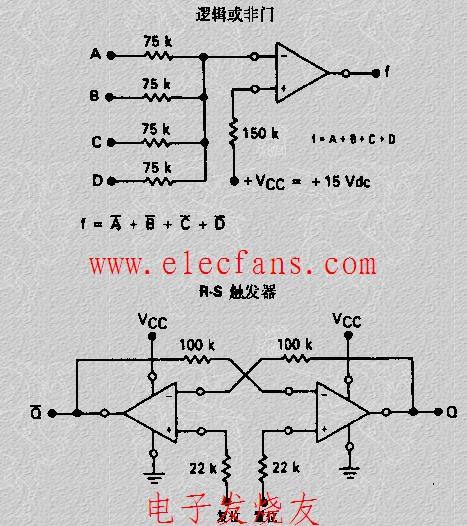

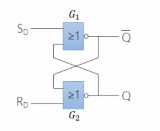

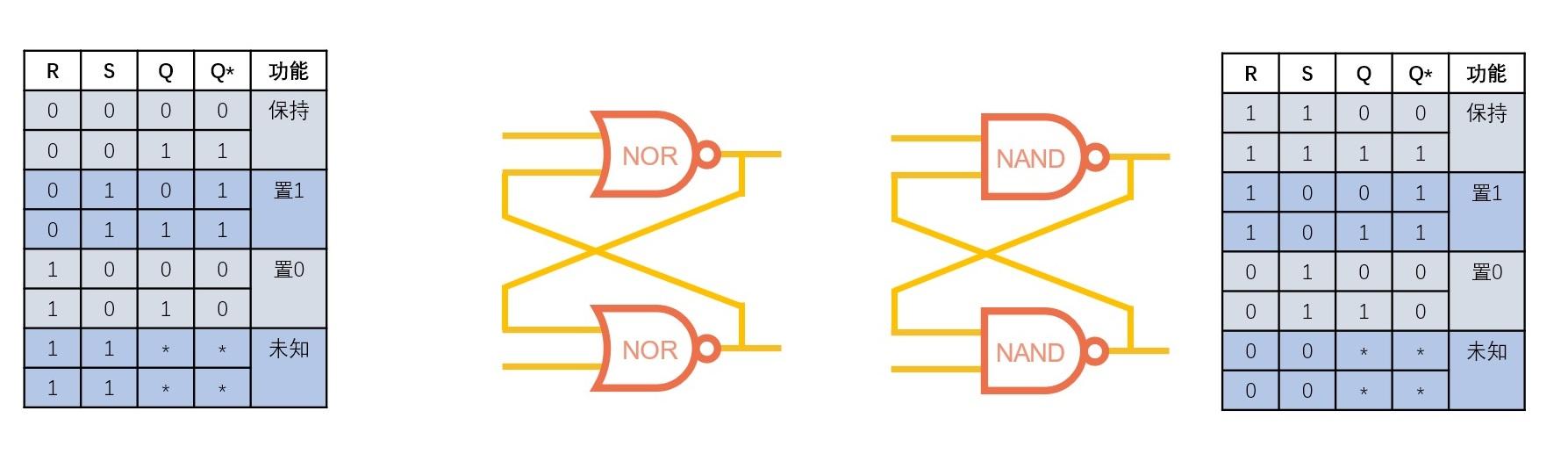

2)由或非門構(gòu)成的基本RS觸發(fā)器

用兩個或非門交叉耦合,也可構(gòu)成基本RS觸發(fā)器,其電路結(jié)構(gòu)和邏輯符號如圖2所示。

具有記憶功能門電路之基本RS觸發(fā)器、同

圖2 與或非門構(gòu)成的基本RS觸發(fā)器

RD和SD分別為復(fù)位(置0)和置位(置1)端,與圖1電路有所不同,它們均是高電平有效。其信號輸入也有四種組合。當RD=0,SD=1時,觸發(fā)器置1;當RD=1,SD=0時,觸發(fā)器置0;當二者都為1時,觸發(fā)器狀態(tài)不確定(為非法電平);當RD=0,SD=0時,觸發(fā)器保持原狀態(tài)不變。

與普通門、受控門電路相比,前者輸入為常態(tài)信號,輸出狀態(tài)取決于即時輸入;后者輸入為“瞬態(tài)”信號,有觸發(fā)特性,輸出有保持功能,輸出為輸入的“過去時”,輸入條件成立時輸出保持。輸入信號存在約束條件,限制了其實用性。RS基本觸發(fā)器是沒有實際應(yīng)用IC器件的,實際應(yīng)用器件是在此基礎(chǔ)上將性能提升后的IC產(chǎn)品,如同步RS觸發(fā)器,同步D觸發(fā)器等系列產(chǎn)品。

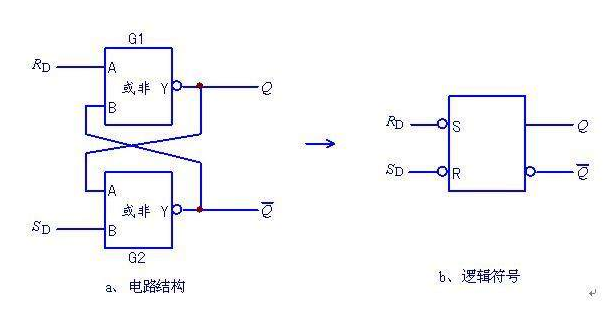

電路實例:三態(tài)R-S鎖存觸發(fā)器CC4044B。內(nèi)部電路結(jié)構(gòu)與引腳功能見下圖。

圖3 CD4044B三態(tài)R-S鎖存器

將基本的R-S觸發(fā)器加以改造,如在輸出側(cè)增設(shè)傳輸開關(guān),就可得到具有三態(tài)傳輸功能的R-S觸發(fā)器。從其內(nèi)部電路結(jié)構(gòu)可看出,a)增加了EN使能控制端,高電平為通態(tài),低電平為關(guān)態(tài);b)增加了受控輸出級,為三態(tài)輸出模式,當EN端為低電平時,輸出級相對于外部電路,為高阻態(tài)(三態(tài))。

從檢修角度出發(fā),我們需要注意的著重點是在線如何確定芯片好壞,并找到(引腳功能、尺寸適宜的)替代元件。

檢修要點:

a)在高阻(傳輸關(guān)斷)態(tài),輸出端電平不取決于輸入信號,而由電路設(shè)計者人為限定(由外加上拉、下拉電阻確實靜態(tài)高、低電平);

b)在正常傳輸(EN端為高電平)狀態(tài),具有基本R-S觸發(fā)器的工作特性:可置0、可置1、輸出保持。可以通過對此三特性的驗證來確定芯片好壞。

和普通門電路不同,現(xiàn)在的輸出是“過去時”,不是對即時的輸入信號作出的反映。欲確實電路好壞,需人為變動一下輸入電平——進行置0或置1操作,據(jù)輸出端做出的反映,確實判斷芯片的好壞。一定條件下,我們可以在輸入端做出“人為動作”,來迫使輸出端作出相應(yīng)的反應(yīng)。其實任何器件,都不難找到相應(yīng)的檢修和判斷方法,器件的正常工作與否即使如雪泥鴻爪,也總會“有跡可尋”。為此,需要研究觸發(fā)器的輸入電路形式,并據(jù)此采用相應(yīng)的“人為動作”,而不會導(dǎo)致在線器件(如觸發(fā)器的前級電路)的損壞。

對器件檢測最好的方法,是上電檢測輸入、輸出狀態(tài)得出結(jié)論,遠比測量引腳電阻、摘下后放入IC測試儀進行檢測,更為方便和準確。這是因為其外圍電路及供電條件,已經(jīng)提供了最為優(yōu)良的檢測條件!

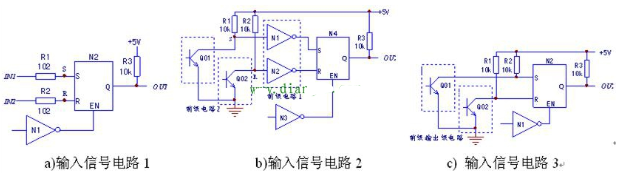

觸發(fā)器的輸入信號電路形式:

圖4 觸發(fā)器輸入信號電路形式

圖4中a)電路,因輸入信號回路串入了R1、R2隔離電阻,因而前級輸入電路是何形式不再重要。該觸電器為高電平信號輸入有效,可知其常態(tài)(或靜態(tài))R、S輸入端應(yīng)該為低電平。在首先確實EN端為高電平(確實電路為通態(tài))情況下(若EN端為低電平,說明處于關(guān)態(tài)——高阻態(tài),需查低電平原因并排除之),若測Q端為低電平,此時將圖中S點與+5V短接一下(即輸入置1信號),再測Q端應(yīng)由0V變?yōu)?V高電平,并保持。說明N2芯片是好的。反之,若Q端為高電平,將圖中R點與+5V短接一下(即輸入置0信號),而Q端就變?yōu)榈碗娖讲⒈3帧7駝t說明芯片已壞。

圖4中b)電路,其信號輸入前級電路為反相器電路,其內(nèi)部輸出級為電壓互補放大器結(jié)構(gòu),N1、N2輸出端靜態(tài)為低電平,此時若貿(mào)然將N4的R、S端與+5V短接制造人為高電平信號,則因造成N1、N2輸出級對+5V電源短路而損壞N1、N2器件。在N1、N2的輸出端無法做手腳,則進而往輸入端電路查找,總能找到動手的地方。該前級電路2為開路集電極輸出結(jié)構(gòu),接有R1、R2上拉電阻。此時將Q01、Q02的集電極與供電地短接一下,即能方便地制造置0或置1信號,從而確實N4觸發(fā)器電路的好壞。

同理,處理EN端電路,也可用相似方法,制造通態(tài)信號,以創(chuàng)造觸發(fā)器的動作檢測條件。

圖4中c)電路,該電路是高電平有效觸發(fā)方式,因而制造高電平的置1或置0信號,僅需短接Q01、Q02的發(fā)射結(jié)使其處于截止狀態(tài)即可。

另外,若前級電路為三態(tài)門,將三態(tài)門處于高阻態(tài)時,此時可在N2的R、S端隨意制造高、低電平信號,如將R、S端接地或接+5V。但若三態(tài)門處于通態(tài)時,則應(yīng)在三態(tài)門的輸入端想辦法,制造信號了。

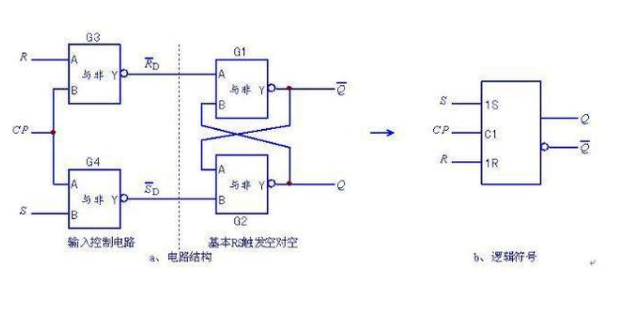

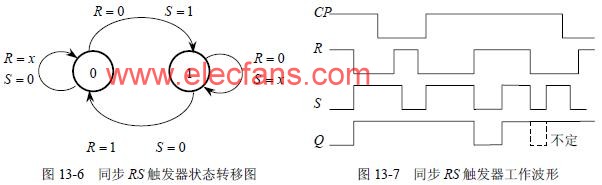

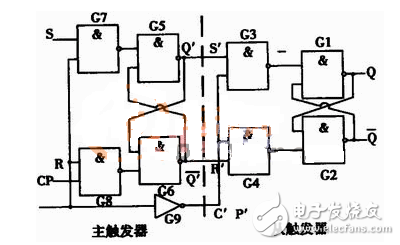

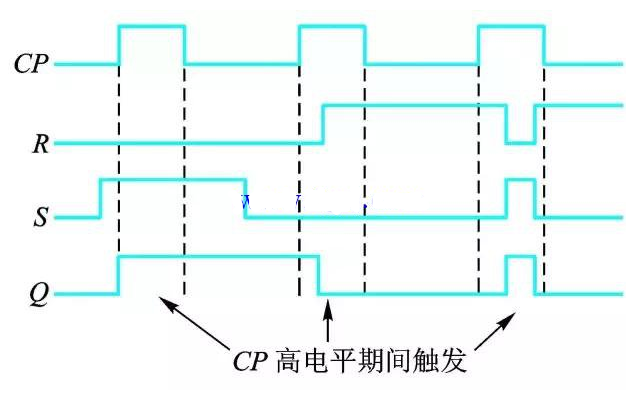

3)同步RS觸發(fā)器

基本RS觸發(fā)器只要輸入信號變化,輸出狀態(tài)就會立即發(fā)生相應(yīng)變化,這不但使得電路的抗干擾能力變差,也給多個觸發(fā)器的同步工作帶來不便。在實際應(yīng)用中,通常要求觸發(fā)器的狀態(tài)按一定的時間節(jié)拍變化,即在時鐘脈沖到達時,才根據(jù)輸入信號改變狀態(tài);沒有時鐘信號時,即使輸入信號改變,也不影響觸發(fā)器的輸出狀態(tài)。為此,增加時鐘脈沖輸入端CP以及相應(yīng)的輸入控制電路,就有了同步RS觸發(fā)器這一類數(shù)字芯片。

同步RS觸發(fā)器的電路結(jié)構(gòu)和邏輯符號如圖5所示。

圖5同步RS觸發(fā)器

與非門G1、G2構(gòu)成基本RS觸發(fā)器,G3、G4構(gòu)成輸入控制電路。工作原理如下:

①CP=0期間,與非門G3、G4被封鎖,/RD=1,/SD=1。因此,無論輸入信號R、S如何變化,都不會影響觸發(fā)器的輸出Q和/Q,即觸發(fā)器狀態(tài)保持不變。

②CP=1期間,與非門G3、G4打開,輸入信號R、S反相后加到由G1、G2構(gòu)成的基本RS觸發(fā)器電路,使Q和/Q的狀態(tài)發(fā)生變化。

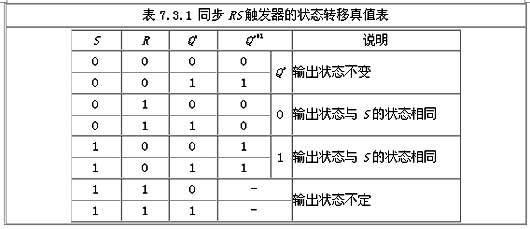

同步RS觸發(fā)器的功能或狀態(tài),可由狀態(tài)轉(zhuǎn)移表來描述(此不贅述)。

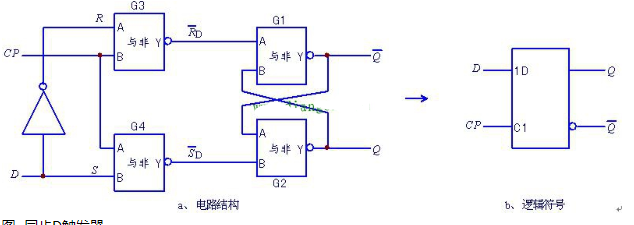

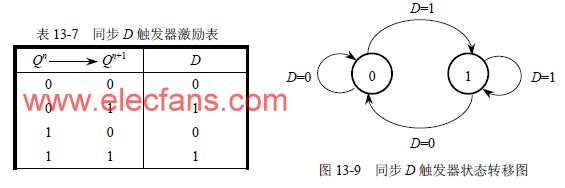

4)同步D觸發(fā)器

同步RS觸發(fā)器在R、S同時為1且同時失效后,觸發(fā)器狀態(tài)不確定,說明其功能仍不完善。D觸發(fā)器針對這一問題作出改進,解決了觸發(fā)器狀態(tài)不確定的問題。

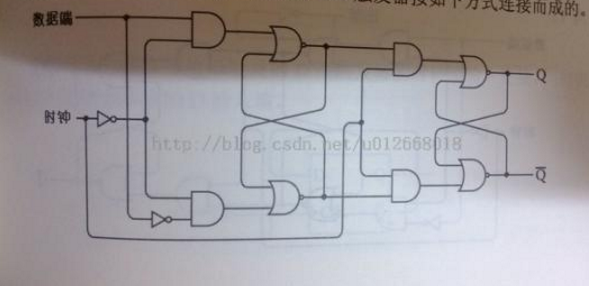

由于只要令R、S不同時為1,觸發(fā)器就不會出現(xiàn)狀態(tài)不穩(wěn)定,最簡單的方法就是令S=/R,此時僅將S作為輸入端(用D表示),就得到了D觸發(fā)器。仍然是由RS觸發(fā)器演變而來,是RS 觸發(fā)器S=/R的特例,其電路結(jié)構(gòu)和邏輯符號如圖6所示。

圖6 同步D觸發(fā)器

工作原理如下:

①CP=0期間,與非門G3、G4被封鎖,/RD=1,/SD=1。因此,無論輸入信號R、S如何變化,都不會影響觸發(fā)器的輸出Q和/Q,即觸發(fā)器狀態(tài)保持不變。

②CP=1期間,與非門G3、G4打開,觸發(fā)器輸出狀態(tài)隨D而變化,完成置0、置1和保持等三種邏輯功能。

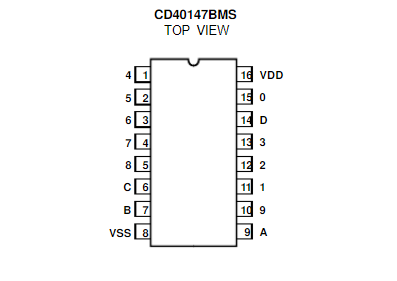

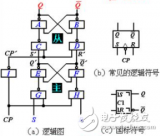

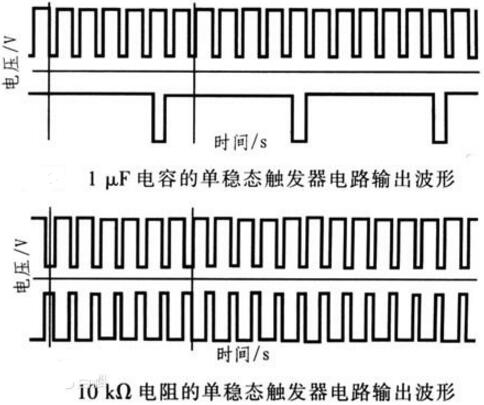

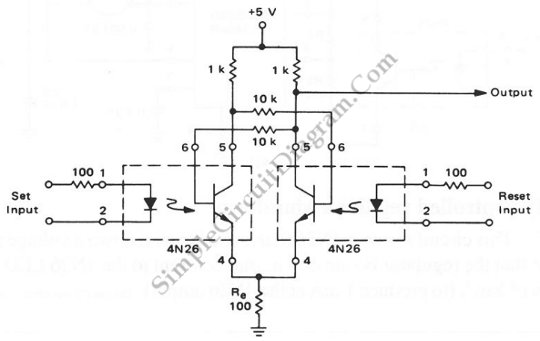

5)雙主-從D型觸發(fā)器電路檢修舉例

觸發(fā)器系列電路形式太多,一下子完全搞明白是不必要的(不可能全部記住,用得多的會自然掌握)。以雙主-從D型觸發(fā)器CD4013為例,在尚未全面深刻掌握原理及內(nèi)部電路結(jié)構(gòu)的前提下,能否根據(jù)端子功能快速掌握其檢修方法呢?答案是肯定的。

控制電路的核心部件為雙D觸發(fā)器,型號為CD4013,內(nèi)含兩個獨立的D觸發(fā)器。從R、S或C端子接受上升沿觸發(fā)信號,能使輸出狀態(tài)產(chǎn)生翻轉(zhuǎn)。常用來組成單穩(wěn)態(tài)、雙穩(wěn)態(tài)、無穩(wěn)態(tài)電路。如圖7-10所示,是內(nèi)部一路D觸發(fā)器的引腳功能圖。

圖7 CD4014的引腳功能圖

我們先掌握CD4013的兩個應(yīng)用模式,從中領(lǐng)會其電路原理及動作模式:

a)雙穩(wěn)態(tài)電路。在數(shù)據(jù)端D和時鐘端C都接地的情況下,在置位端S加一個脈沖高電平,則Q輸出端變?yōu)楦唠娢唬ū恢梦唬辉趶?fù)位端R加一個脈沖高電位,輸出端Q變?yōu)榈碗娢唬ū粡?fù)位)。端為Q端的反相輸出。

根據(jù)此原則(或滿足此檢測條件下),CD4013“變身”為普通R-S觸發(fā)器,在R、S端施加瞬時高電平信號,即可完成置0、置1及保持功能檢測。

b)數(shù)據(jù)檢出電路。置位端S和復(fù)位端R都接地的情況下,在C端時鐘脈沖作用下,D數(shù)據(jù)端的數(shù)據(jù)(0或1)被傳輸至輸出端Q。D端只有0或1兩個數(shù)據(jù)狀態(tài),C端上升沿脈沖作用期間,D端的數(shù)據(jù)為Q端所檢出。

根據(jù)此原則(或滿足此檢測條件下),可在其時鐘端人為施加“0”或“1”信號,檢測Q端和D端數(shù)據(jù)傳輸狀態(tài),由此準確判斷芯片好壞。

由上述,因而對如我——一位較懶惰的檢修人員來說,檢測數(shù)字電路的好壞,無需研究其繁雜的時序圖,也不用管它傳輸頻率是多少和具體的傳輸數(shù)據(jù)是什么,電路僅為高低電平信號處理器,或僅為傳輸一個直流5V和直流0V的信號電路。輸出是此兩種狀態(tài),而輸入信號亦為此兩種狀態(tài)。完全可用0V和5V充當輸入端檢測信號,檢測輸出端的5V和0V變化,只要電路是聽話的講理的,就是好的電路。

電子發(fā)燒友App

電子發(fā)燒友App

評論