AD9238是美國模擬器件公司(ADI)在2002年8月推出的業界最快的12b雙通道模數轉換器。AD9238與ADI公司的驅動運算放大器配合可以給醫療成像、多通道通信等高端應用提供完整的解決方案。

AD9238分3種型號,采樣率最高分別可達20 MS/s,40 MS/s和65 MS/s。他可以提供與單通道A/D轉換器同樣優異的動態性能,但是比使用2個單通道A/D轉換器具有更好的抗串擾性能。

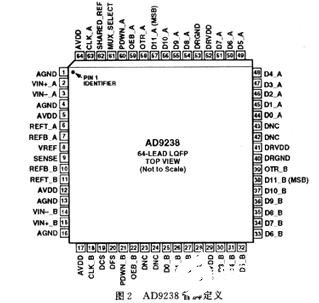

AD9238三種型號的功耗分別為180 mW,330 mW和600 mW,只有同類A/D轉換器的1/2。他采用64腳LQFP封裝(尺寸只有9 mm×9 mm),非常適合在對尺寸要求嚴格的場合中使用。

1、AD9238的主要特點:

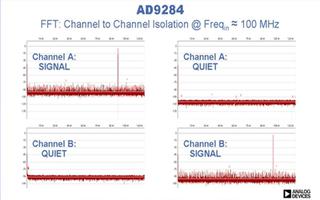

集成了2個12 b的單通道A/D轉換器AD9235(20/40/65 MS/s);采用單一3 V供電(2.7~3.6 V);RSN=70 dBc(最高采樣頻率時,AD9238-65,此值為典型值);RSFD=85 dBc(最高采樣頻率時,AD9238-65,此值為典型值);ENOB=11.3 b(有效位數,典型值);差分輸入時有500 MHz的3 dB帶寬;有片上的參考電壓和SHA;1~2Vp-p 的模擬輸入范圍;輸出數據格式為偏移二進制碼或者是二進制補碼;AD9238-65還帶有片上時鐘占空比調整電路;通道間串擾為-80 dBc@fIN=10 MHz。

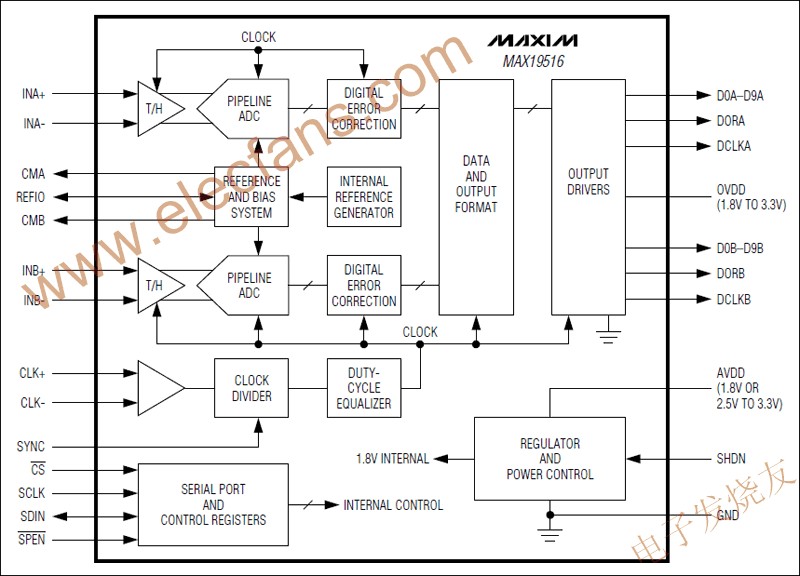

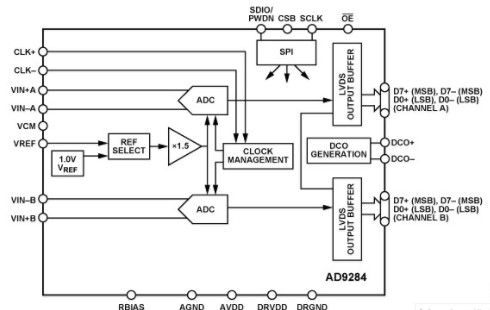

2、芯片內部結構及原理說明

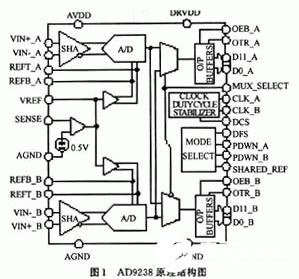

如圖1所示,AD9238由2個基于AD9235轉換器核的高性能A/D轉換器組成。這2個ADC通道除了共用內部的電壓參考源VREF,其他基本是獨立的。每個ADC通道都包含有1個前端采樣保持放大器(SHA)和1個流水線ADC。該流水線ADC分為三級,第一級是1個4 b的閃速(Flash)ADC,第二級是8個1.5 b的閃速ADC,第三級是1個4 b的閃速ADC。每一級都提供有充分的位數重疊來糾正前一級的錯誤,每級的量化輸出再加上數字誤差校正可以保證最后得到12 b的有效位數。流水線的結構允許前一級在完成某一采樣工作后進行新的采樣,而后一級仍在進行先前的采樣工作。

流水線的每一級(除了最后一級)都有一個低位數的DAC和一個乘法器來驅動下一級。乘法器用閃速ADC的輸出來控制開關電容DAC。DAC的輸出減去輸入信號再經放大后送入下一級流水線,乘法器這一級也叫做乘法DAC(MDAC)。每一級有1 b用來對前一級的錯誤進行數字校正。最后一級只包括一個閃速ADC。沖器。輸出緩沖器單獨供電,這樣可以方便地對輸出電壓進行調節。AD9238有64個管腳,管腳分布如圖2所示。

3、AD9238應用系統設計

A/D轉換器的應用屬于數字模擬混合電路設計,以下對AD9238應用系統設計時需要重點考慮的幾個問題進行詳細論述。

3.1 模擬輸入

AD9238的模擬輸入端(管腳2,3,14,15)是一個差分開關電容電路(SHA),他可以接收1-2Vp-p范圍的單端或者差分模擬輸入信號。

SHA電路根據時鐘信號選擇處于采樣模式或者是保持模式。在SHA電路的每個輸入端串接一個小的電阻可以減小從輸出級驅動源產生的瞬時峰值電流,并接一個電容可以提供動態負載電流。這個無源網絡組成了一個輸入低通濾波器。

REFT和REFB分別提供了內部正負差分電壓參考。 他們定義了ADC內核的電壓范圍,有關的關系如下:

內部電壓參考(VREF)的范圍是0.5~1.0 V,按照上述關系,外部電壓輸入范圍為1.0~2.0 V。當AD9238工作在最大的輸入范圍時(2Vp-p模式時),可以獲得最大的RSN(信噪比)性能,當工作在1Vp-p模式時,RSN會下降3 dB。

如前所述,AD9238可以采用單端或者差分模擬輸入。當工作在差分輸入模式時,會有比較好的性能。這時建議采用AD公司的差分運放AD8138作為ADC的驅動芯片。當AD9238工作在單端輸入模式時,ADC的性能會有所下降(如SFDR和SNR指標),但是比較適合低成本的應用,這時還是可以保證比較好的性能。

3.2時鐘信號

高速的ADC對時鐘的占空比很敏感,一般來說需要有50%(±5%)的占空比。AD9238給每個通道單獨提供時鐘(管腳CLK_A和CLK_B),當2個通道的采樣時鐘同頻同相時會有比較好的性能,當2個通道不同步時性能會有所下降。

AD9238-65內部有2個時鐘占空比調節器,可以將占空比調整到50%(當使能DCS管腳時)。另外兩種型號沒有這種功能。

時鐘信號的電源驅動應該和輸出數字信號驅動分開,以避免混入數字噪聲。時鐘信號的孔徑抖動對ADC的性能影響較大,所以最好采用抖動比較小的晶振作為時鐘源。

AD9238三種信號的最高時鐘頻率分別為20 MS/s,40 MS/s和65 MS/s,最低的時鐘頻率都為1 MS/s,當時鐘頻率低于1 MS/s時動態性能會下降。

3.3電源與接地

AD9238供電電壓范圍為2.7~3.6 V,分為模擬電源(AVDD,共4個管腳)和數字電源(DRVDD,共3個管腳)。每個通道可以獨立地工作在休眠模式(通過使能PWDN_A或者PWDN_B)。在這種模式下器件功耗很低。

AD9238的數字輸出驅動可以根據DRVDD的值設置成2.5 V或者3.3 V輸出。這樣可以適應不同系列的器件。

AD9238具有2種接地管腳:AGND(第1,4,13,16管腳)和DRGND(第28,40,53管腳)。模擬地(AGND)用作模擬信號的參考地,整個系統的模擬地應該盡量靠近這些管腳。數字地(DRGND)用做芯片數字部分對地電流的回路。在模擬電源和模擬地之間應該用4組旁路電路隔離開(每組有2個0.001μF和0.1μF的電容),在數字電源和數字地之間用3組旁路電路隔離開(每組有22個0.001μF和0.1μF的電容)。

3.4工作時序

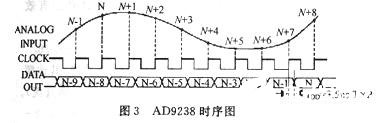

AD9238的數據輸出會有7個時鐘周期的流水線延遲,如圖3所示。開始采樣后前7個數據是無用的,應該在后端數字信號處理時舍棄掉。

AD9238兩個通道的12 b數字信號輸出(D0_A-D11_A和D0_B-D11_B)是獨立的。一般情況下,他們各自獨立的輸出轉換結果。當把AD9238兩個通道的時鐘輸入CLK_A,CLK_B和管腳MUX_SELECT連接在一起時,系統處于單通道輸出工作狀態。此時當時鐘上升沿到來時,轉換數據分別送給各自對應的通道;當時鐘下降沿到來時,轉換數據分別送給相反的通道。這樣在一個時鐘周期內,數據結果可以從一個通道輸出,另外一個不用的輸出通道可以通過管腳OEB_A(或OEB_B)關閉掉。可以看到,這時數據率是采樣率的2倍。

3.5 數字輸出數據格式

AD8138輸出數據為TTL/CMOS兼容電平(可以設置成2.5V或者3.3V),通過設置DFS可以使AD8138輸出數據格式為偏移二進制碼(DFS接AGND)或者是二進制補碼(DFS接AVDD)。

另外,管腳OTR_A和OTR_B為溢出標志位,當某個通道的輸入模擬信號幅度超出范圍,對應通道的溢出標志位會輸出高電平。

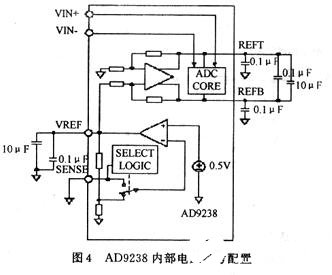

3.6 電壓參考

AD8238內部有一個穩定精確的0.5 V電壓參考。調整AD9238的參考電壓可以改變輸入信號范圍,調整的方法有2種:內部參考和外部參考。輸入范圍根據參考電壓的改變做線性變化。當把SENSE(第9腳)接地時,VREF 被設置成1 V,此時器件采用內部參考,輸入信號范圍為2Vp-p。有關管腳的接法如圖4所示。

當把SENSE(第9腳)直接與VREF管腳連接時,輸入信號范圍為1Vp-p當在SENSE管腳、VREF管腳和模擬地三者之間串接2個電阻R1和R2時,輸入信號范圍為可改變的,即VREF=0.5×(1+R2/R1)。上述兩種情況都屬于內部電壓參考。

當把SENSE管腳接到AVDD時,內部參考無效,采用外部電壓參考。這種情況使用不多,不再做詳細介紹。

在設置電壓參考時,主要是改變SENSE管腳的接法,REFT和REFB管腳的接法如圖4所示。值得注意的是,AD8238對每個通道都提供了電壓參考,如果采用共享電壓參考模式可以取得較好的性能。此時需要把SHARED_REF管腳(第62腳)接高電平,2個通道的REFT和REFB管腳互相連接(即REFT_A接REFT_B,REFB_A接REFB_B),他們各自的去耦和隔離電容接法仍同圖4所示。

4、AD9238設計實例

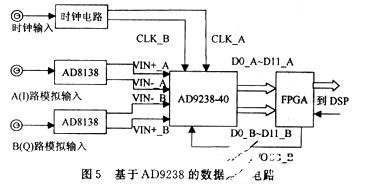

AD9238在通信接收機的射頻采樣中有很好的應用,現介紹一個在通信I/Q兩路數據采集中的具體設計實例。

如圖5所示,該數據采集電路由時鐘電路、運放驅動電路、A/D轉換電路、FPGA電路組成。FPGA主要完成和DSP芯片之間數據的緩沖、轉換及傳遞,利用握手信號實現異步通信。該電路工作在2Vp-p差分工作模式,采用內部電壓參考,最高采樣頻率可達40 MS/s。下面主要對運放驅動電路和A/D轉換電路做詳細的介紹。

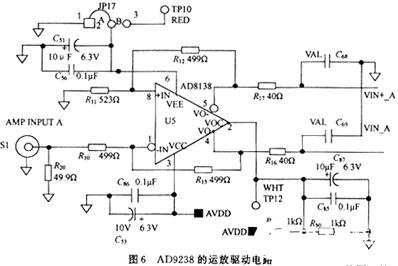

4.1 運放驅動電路

AD9238兩個通道分別采用一個AD8138做為運放驅動芯片。I/Q兩路中頻模擬信號分別經過2個AD8138變為差分信號送給A/D轉換器(第2,3,14,15管腳)。圖6給出了其中一路的具體電路圖,另一路與此基本相同。

4.2 A/D轉換電路

該部分電路是整個數據采集電路的核心,下面僅就原理圖設計的有關重要管腳進行說明,PCB設計不做詳細討論。

4.2.1 輸入信號

包括模擬輸入(管腳2,3,14,15)和時鐘輸入(管腳18,63),其中時鐘輸入由外部供給可調的時鐘,經過反 相器后送給A/D轉換器。

另外還有2個通道的輸出使能(管腳22,59),由FPGA提供,低電平有效,可以根據通信系統需要控制A/D轉換器實時的開始或者停止采樣。

4.2.2 電壓參考

包括的主要管腳是第6,7,8,9,10,11,62個管腳,在3.6中已經對這些管腳的接法做了詳細的討論。該數據采集電路板采用2 VP-P差分工作模式,使用內部電壓參考,兩通道工作在共享電壓參考模式。

4.2.3 電源和地

AD9238有4組模擬電源和模擬地管腳(第5,12,17,64為AVDD,第1,4,13,16為AGND)、3組數字電源和數字地管腳(第29,49,52為DRVDD,第28,40,53為DRGND),他們的具體接法見3.3說明。值得注意的是,在進行PCB設計時,電路的模擬部分(模擬電源、模擬地等)和數字部分(數字電源、數字地等)應該分開布局,然后把模擬地和數字地單點連接。

4.2.4 輸出信號

轉換后得到12位I/Q兩路的數字信號(D0_A-D11_A和D0_B-D11_B)分為2個通道輸出給FPGA。溢出標志(OTR_A和OTR_B)為高電平有效,可外接一發光二級管做為電路溢出指示燈。

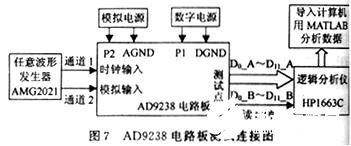

4.3 電路測試方法

在電路板設計制作完成后要對其進行測試,圖7為該數據采集板的測試連接圖。

采用任意波形發生器產生時鐘信號和模擬信號(2個通道共用)提供給試驗板,這樣可以方便地對不同頻率和幅度的信號進行調試;穩壓電源分別給電路板提供模擬電源和數字電源;邏輯分析儀在讀時鐘驅動下讀取采集到的兩路12 b數字信號,導出后可在電腦上進行分析計算。

4.4 測試結果

衡量A/D轉換器最重要的指標是有效位數和采樣頻率。

測試有效位數的方法是:由邏輯分析儀采集到每個通道的8192點12 b二進制補碼數據,導入計算機中;運用Matlab軟件分析其頻譜,計算出信噪比和信納比。然后根據信納比(SINAD)計算出有效位數,有效位數:

SNOB=(SINAD-1.74)dB/6.02。

其中:SINAD=信號功率/其他頻譜成分功率和(包括諧波,不包括直流)。

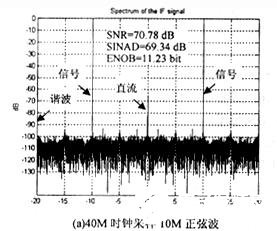

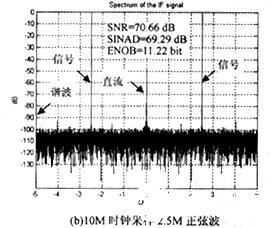

根據上述方法,對基于AD9238-40 的數據采集電路板進行了測試,在采樣頻率為40 MS/s和10 MS/s時僅就單個通道進行了測試,得出的結果如圖8所示。

從圖8的2個頻譜圖可以看到,在上述兩種采樣頻率下,AD9238-40的信噪比可以達到70 dB以上,有效位數可以達到11 b以上,達到了設計要求。

圖8 兩種采樣頻率下的2個頻譜圖

限于篇幅,僅給出了單個通道的測試結果,有關雙通道之間幅相一致性測試、串擾測試等對系統整體影響不大,所以不做詳細討論。

5、結語

本文對雙通道高速A/D轉換器AD9238的原理和應用做了介紹。可以看到,在雙通道或多通道數據采集電路應用中,AD9238是非常有用的。相對于采用單通道A/D轉換器的電路來說,AD9238具有功耗低、尺寸小、雙通道幅相一致性好等獨特的優點,而且AD9238還具有同樣優異的SNR和SFDR性能。

責任編輯:gt

電子發燒友App

電子發燒友App

評論