本文主要介紹了采樣保持電路圖大全(五款采樣保持電路設計原理圖詳解),采樣保持電路(采樣/保持器)又稱為采樣保持放大器。當對模擬信號進行A/D轉換時,需要一定的轉換時間,在這個轉換時間內,模擬信號要保持基本不變,這樣才能保證轉換精度。采樣保持電路即為實現這種功能的電路。

2018-02-23 09:59:44 95716

95716

主要是關于:采樣保持名詞解釋、采樣保持電路工作原理、采樣保持電路功能、采樣保持電路作用以及采樣保持電路設計。

2022-10-20 09:37:34 5059

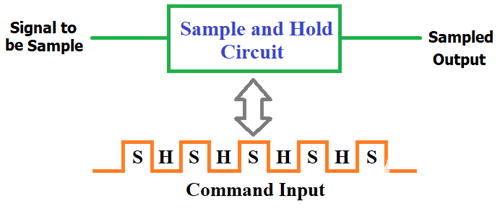

5059 采樣保持電路從模擬輸入信號中獲取樣本并保持特定時間段,然后輸出輸入信號的采樣部分。該電路僅對幾微秒的輸入信號進行采樣。

2022-11-08 17:29:18 6704

6704

AD9254-150EBZ,用于AD9254的評估板是單芯片,1.8V單電源,14位,150 MSPS模數轉換器(ADC),具有高性能采樣保持放大器(SHA)和 - 芯片電壓參考。寬帶寬,真正的差分

2020-07-22 11:46:37

求51單片機差分采樣電路(采集電流互感器輸出的交流信號)。我直接將電流互感器的采樣電阻兩端接到單片機的兩個I/O口,才樣很不準,那位高手有跟好的電路麻煩推薦下

2014-06-16 11:03:59

DC745A,演示電路采用LTC2433-1,16位高性能DS模數轉換器。 LTC2433-1具有0.12 LSB線性度,0.16 LSB滿量程精度,5mV失調和1.45mV RMS噪聲。輸入

2020-03-11 09:40:46

本應用筆記介紹了輸入端相同值電阻的不同容差如何改變全差分ADC的THD性能。電阻器的成本隨著容差的每個較低增量而顯著變化 概觀該MAX11905是一個20位全差分SAR模擬數字轉換器(ADC),在

2018-12-17 22:13:40

差分放大電路利用電路參數的對稱性和負反饋作用,有效地穩定靜態工作點,以放大差模信號抑制共模信號為顯著特征,廣泛應用于直接耦合電路和測量電路的輸入級。但是差分放大電路結構復雜、分析繁瑣,特別是其對差模

2018-12-06 14:20:41

本帖最后由 gk320830 于 2015-3-7 19:04 編輯

采樣保持電路

2012-08-14 09:40:39

HMC661LC4B是一款SiGe單芯片、全差分、單列、采樣保持(T/H)放大器,面向寬帶信號采樣系統提供前所未有的帶寬和動態范圍性能。此款放大器在18 GHz的帶寬范圍內提供精密的信號采樣,在DC至超過5 GHz的輸入頻率范圍內具有9/10位線性度、1.05 mV噪聲和

2019-07-16 03:33:37

,但該ADC結構既可以單端方式驅動,也可以差分方式驅動。然而,使用差分變壓器或差分運放驅動一般可以獲得最佳性能。圖20:典型開關電容CMOS 采樣保持器的簡化輸入電路在跟蹤模式下,差分輸入電壓施加

2022-04-06 14:04:47

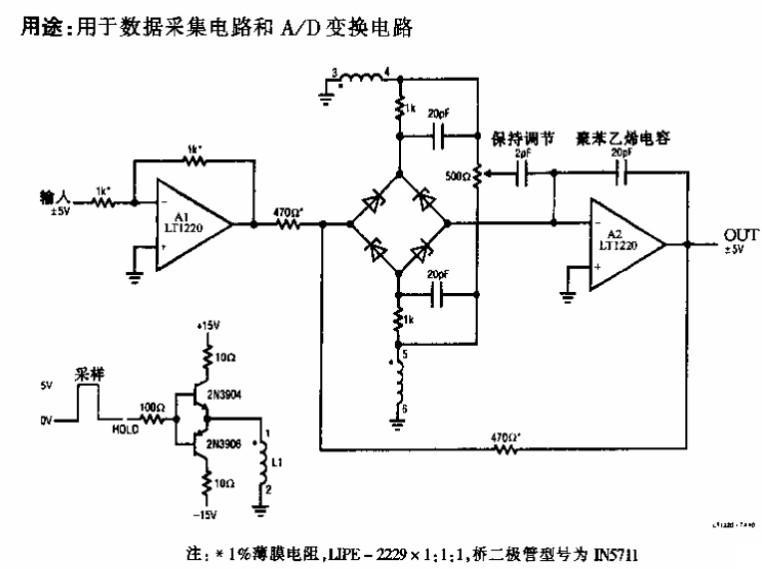

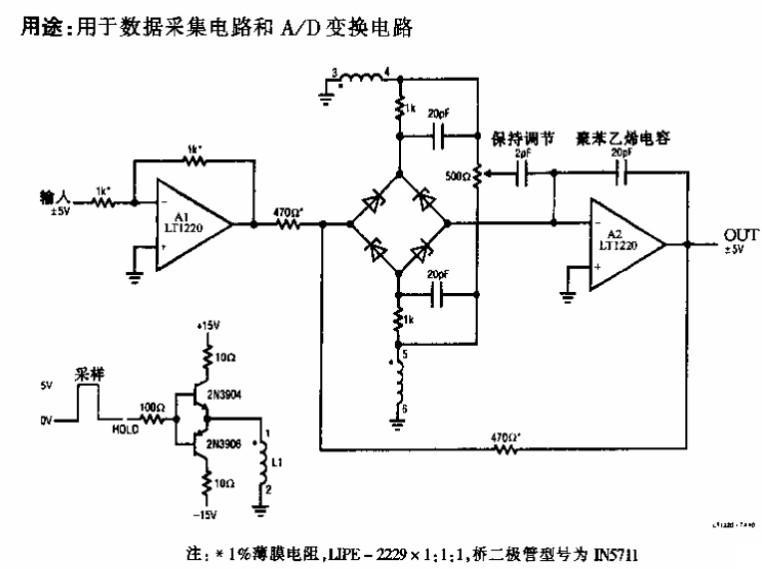

以減小開關漏電流的影響;在高速場合也可用晶體管、場效應管來作為開關。然而,一般目前常采用性能優越的集成式采樣/保持器。隨著大規模集成電路技術的發展,目前已生產出多種集成采樣/保持器,如可用于一般要求

2018-01-08 14:23:45

檢測電路,以適應于不同電機及不同控制方式的要求;同時由于采用了高性能的MCU,更多類型的通信接口可被靈活應用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

DC746A,LTC2412CGN演示板,2通道24位差分ADC。演示電路采用LTC2412,這是一款雙通道,24位高性能DS模數轉換器。 LTC2412具有2ppm線性度,2.5ppm滿量程精度,0.1ppm偏移和0.16ppm噪聲

2020-03-11 09:53:41

DC586A,LTC2431CMS演示板,MS10封裝的20位差分ADC,演示電路采用20位高性能模數轉換器LTC2431。 LTC2431具有3ppm線性度,10ppm滿量程精度,1ppm偏移和0.56ppm噪聲

2020-03-12 10:39:25

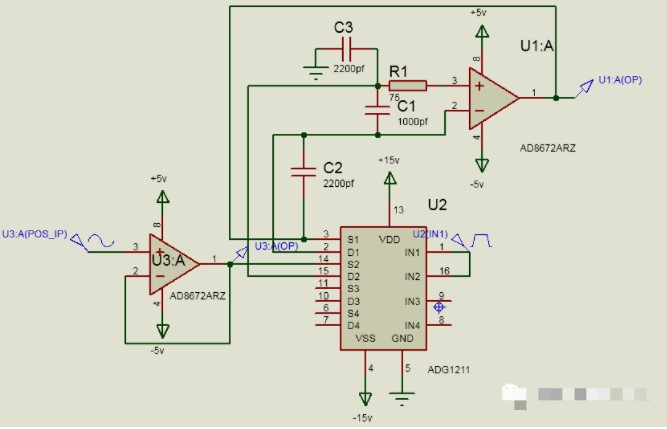

采樣保持放大器經常用于信號處理系統中,AD781是Analog Devices公司生產的快速采樣保持放大器,它具有采樣時間短、下降速度慢、保持誤差小、功耗低、功能齊備、體積小等優點,十分適用于高速

2023-11-23 07:05:20

AD9233-105EBZ,用于評估AD9233的評估板,12位,105 MSPS,1.8V模數轉換器,具有高性能采樣保持放大器(SHA)和片內基準電壓源。該產品采用多級差分流水線架構,具有輸出糾錯

2019-11-11 07:16:29

DC1384A-A,演示電路采用帶有SPI接口的16位高性能差分模數轉換器LTC2452。輸入是雙極性的,具有Ref-to Ref +范圍。該調制器的專有采樣技術將平均輸入電流降低至比典型Δ-ΣADC低50nA的數量級。 LTC2452采用8引腳,3x2mm DFN封裝,具有易于使用的SPI接口

2020-05-05 14:02:15

異常(波形幅度表現為截底),可能的原因?

問題2:采用單端接入IN0時,在信號源和頻率板之間接入了10k低通濾波器(用公司),大信號測試結果SNR為89 db,是否為ad7699單端接入時的真實水平?(PDF上SNR典型值為92.5 db)

問題3: ad7699是否支持全差分的輸入方式?

2023-12-13 06:56:52

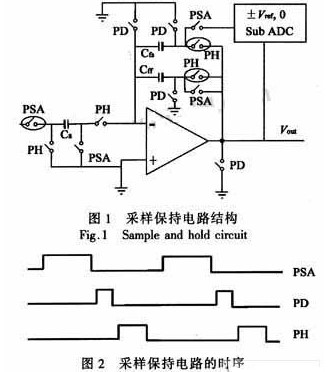

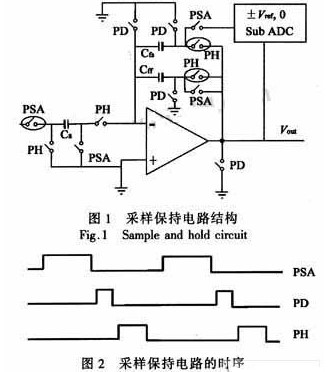

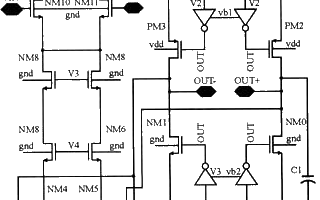

非常重要的組成部分。在這些應用中,如何在保持高采樣頻率下降低功耗是一個很重要的設計要點。整體而言,流水線型結構A/D轉換器是同時實現低功耗、高采樣率和高分辨率的合理選擇。在流水線結構的A/D轉換電路中

2019-07-15 07:01:36

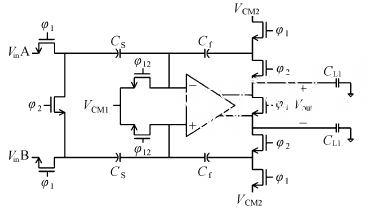

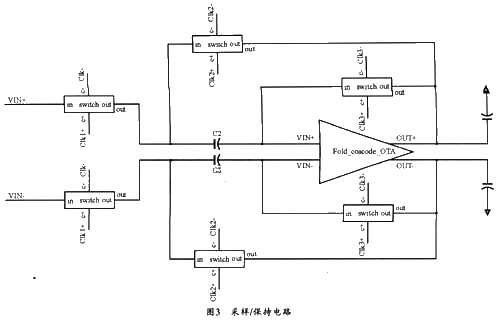

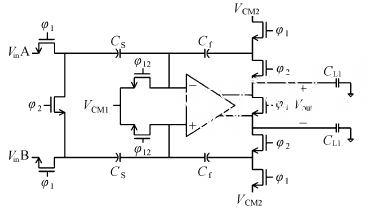

穩定時間短等優點。適用于高速的流水線ADC.同時采用了下極板采樣技術和全差分結構。全差分結構可以消除電路的共模失調誤差,抑制襯底噪聲。下極板采樣技術的應用則可以幾乎完全抑制了在采樣時刻由于開關的電荷

2018-10-08 15:47:53

提問:我們可以使用儀表放大器生成差分輸出信號嗎?隨著對精度要求的不斷提高,全差分信號鏈組件因出色的性能脫穎而出。這類組件的一個主要優點是可通過信號路由拾取噪聲抑制。由于輸出會拾取這種噪聲,輸出經常

2021-10-15 06:30:00

全差分儀表放大器具有其他單端輸出放大器所沒有的優勢,它具有很強的共模噪聲源抗干擾性,可減少二次諧波失真并提高信噪比,還可提供一種與現代差分輸入ADC連接的簡單方式。低功耗全差分儀表放大器電路怎么設計?

2021-04-06 08:11:07

電路將全差分5V信號轉換為全差分0V至5V信號 -LTC2379-18的正常輸入范圍。該電路對于產生全差分輸出的傳感器非常有用

2020-04-03 09:59:24

大神們好,最近有個問題,我的傳感器信號經過調理電路之后是一個峰峰值0.6V左右的正弦信號,然后經過濾波之后單端送入AD中采樣,采樣結果受到嚴重的工頻干擾的影響,現在想增加一個差分電路的方式送入AD,請問這樣對抑制工頻干擾有幫助沒有,在設計過程中需要注意的事項,謝謝嘍。

2015-11-11 14:59:49

AD9246-105EBZ,AD9246評估板是單片,1.8V單電源,14位,105 MSPS模數轉換器,具有高性能采樣保持放大器(SHA)和片內基準電壓源。該產品采用多級差分流水線架構,具有輸出糾錯邏輯,可在105 MSPS數據速率下提供14位精度,并確保在整個工作溫度范圍內無失碼

2020-07-20 10:16:13

本文提出一種高性能全數字式正弦波逆變電源的設計方案。該方案分為前后兩級,前級采用推挽升壓電路將輸入的直流電升壓到350V左右的母線電壓,后級采用全橋逆變電路,逆變橋輸出經濾波器濾波后,用隔離變壓器

2018-10-10 17:09:10

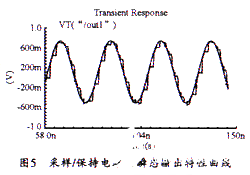

摘要本文提出一種高性能全數字式正弦波逆變電源的設計方案。該方案分為前后兩級,前級采用推挽升壓電路將輸入的直流電升壓到350V左右的母線電壓,后級采用全橋逆變電路,逆變橋輸出經濾波器濾波后,用隔離

2018-11-21 16:36:23

如何使用全差分放大器實現單端至差分轉換?如何使用有源匹配電路改善寬帶全差分放大器的噪聲性能?

2021-04-13 06:40:17

可以使用儀表放大器生成差分輸出信號嗎?隨著對精度要求的不同提高,全差分信號鏈組件因出色的性能脫穎而出,這類組件的一個主要優點是可通過信號路由拾取噪聲抑制。由于輸出會拾取這種噪聲,輸出經常會出現誤差

2019-09-11 11:51:20

的線性性能;采用全差分結構、底極板采樣來消除電荷注入和時鐘饋通。該采樣保持電路能夠直接應用于高速高精度模/數轉換器等各種高速模擬系統中。

2021-04-20 06:45:33

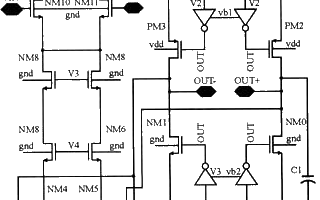

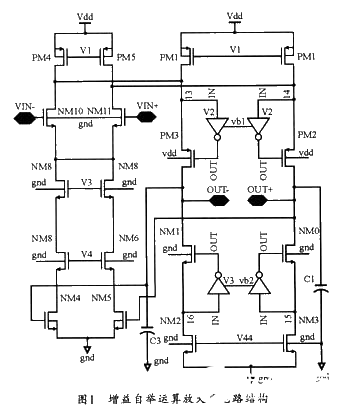

為了解決傳統S/H電路失真大和靜態工作點不穩定的問題,采用0.25 μm BiCMOS工藝,設計了一款高速率、高精度的10位全差分BiCMOS S/H電路。文中改進型自舉開關電路和雙通道開關電容共模反饋電路(CMFB)設計具有創新性。

2021-04-21 06:24:21

利用差動放大器實現低損失、高性能全波整流器的電路是什么樣的?

2019-08-02 07:00:51

本文介紹了一種基于SiGe BiCMOS、開環全差分結構的SH。采樣速率可以達到800 Msps,采樣精度可以達到8 bit,能夠適應無線通信領域的要求。

2021-04-14 06:36:13

怎么實現高速采樣保持電路的設計?

2021-10-11 07:42:17

系統。 芯片采用CMOS工藝設計,內部電路結構基于R-2R電阻網絡結構設計,并在全電源 電壓范圍內實現16bit的動態范圍。 TM8211可通過采用數字串行總線數據輸入,采 用快速R-2R網絡結構來支持

2015-05-17 20:29:05

請問各位關于全差分SARADC下極板采樣的邏輯控制,有沒有相關了文章介紹的比較詳細啊,求推薦,感激不盡!

2021-06-25 07:25:37

本文介紹了一種基于SiGe BiCMOS、開環全差分結構的SH。采樣速率可以達到800 Msps,采樣精度可以達到8 bit,能夠適應無線通信領域的要求。

2021-04-08 06:07:31

本文通過對比較器進行特殊的處理,去掉了ADC中的采樣保持電路,并且引入運放共享(op-amp shar-ing)技術,從而完成了一個分辨率為10bit、采樣頻率為60 MHz、功耗為15 mW的全差分流水線低功耗ADC的設計。

2021-04-22 06:41:39

外行不懂模電,請教個問題!感謝大家如果采用輸出為0-5A的電流互感器,下圖差分電路中,采樣電阻R應該選用多大阻值的?

2022-09-22 16:25:27

大家好,遇到一個疑惑,要對原來做的系統改進,原系統用的是偽差分ADC,單端信號輸入,現在想改為真差分ADC,但是傳感器輸出的是單端信號,所以在ADC之前要用一個單端轉差分的模塊,就想問一下,這么做的效果在理論上是不是會好點,還有全差分ADC與偽差分ADC相比優勢在哪里,謝謝。

2023-12-15 08:22:16

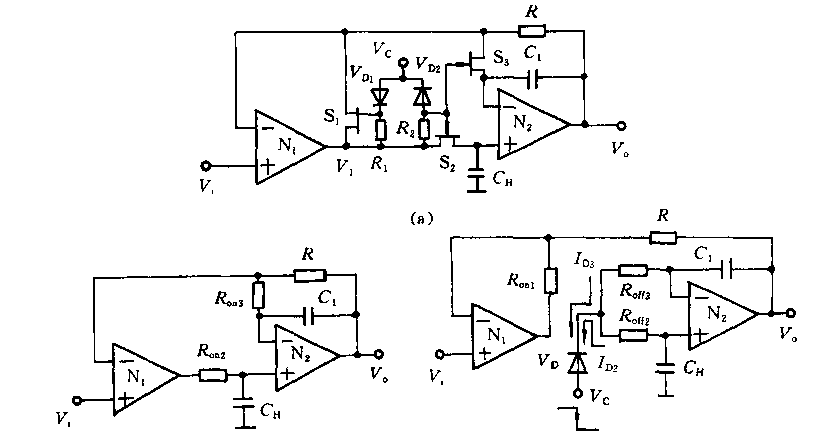

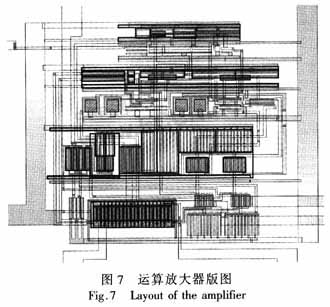

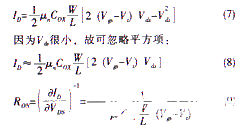

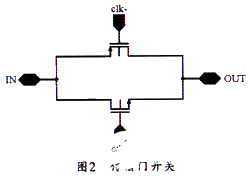

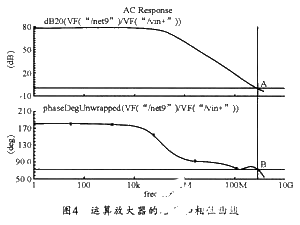

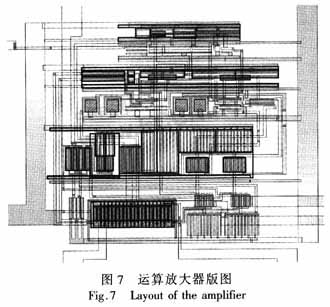

采樣保持電路的結構分為哪幾種?如何去設計運算放大器?描述自舉開關是如何實現的?怎樣對運算放大器進行仿真驗證?

2021-04-20 06:59:17

差分信號適合于需要大信噪比、高抗擾度和較低二次諧波失真的電路,例如高性能ADC驅動和高保真度音頻信號處理等應用。《模擬對話》曾刊載過一篇相關文章——“多功能、低功耗、精密單端差分轉換器”1,其中

2019-04-14 08:30:01

采樣保持電路(采樣/保持器)又稱為采樣保持放大器。當對模擬信號進行A/D轉換時,需要一定的轉換時間,在這個轉換時間內,模擬信號要保持基本不變,這樣才能保證轉換精度。采樣保持電路即為實現這種功能的電路

2011-07-28 10:21:06

傳感器與電流互感器, 分流電阻器加隔離運放的方案在線性度、帶寬和漂移等性能更好。在電機驅動器中,通常會在功率板用隔離采樣運放來對相電流,母線電流和母線電壓等進行采樣,如下圖1: 圖1 電機驅動器電壓電流采樣 下圖所示,是使用隔離運放來進行相電流采樣的常見結構和內部原理圖。圖2…

2022-11-07 07:19:42

引言影響接收機速度、性能的一個重要電路單元AD轉換部分就顯得愈發重要。影響接收機速度、性能的一個重要電路單元AD轉換部分是非常重要的,而AD轉換前端的采樣保持電路又直接關系到AD芯片的轉換

2021-07-27 06:12:53

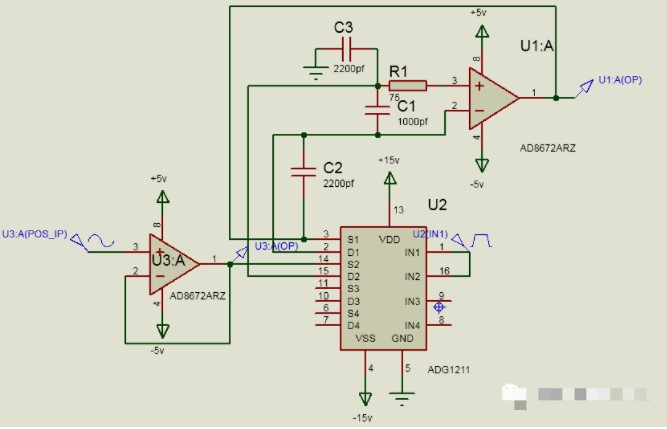

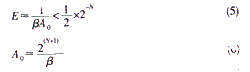

介紹了一種利用雙采樣技術的高性能采樣/保持電路結構,電路應用于10bits50MS/s 流水線ADC 設計中。電路結構主要包含了增益自舉運算放大電路和柵壓自舉開關電路。增自舉運算放大

2009-12-26 16:39:10 28

28 對采樣保持電路的原理、工作方式、電路的參數以及保持電容器電容量大小的選定進行了分析。關鍵詞:采樣;保持;電容

Abstract:This paper analyses the principle of~mapling a

2010-04-13 08:54:05 64

64 在常規高速采樣保持電路(SHC)中采樣速率主要受到保持電容器被充電到輸入電平期間的采集時間的限制。本文描述一種新的電路結構,其采樣速率僅僅由保持時間決定。就時鐘饋通而

2010-04-28 09:57:45 63

63 一種新型高速采樣保持電路摘要 : 本文提出了一種新型的基于運算放大器的開關電容采樣保持電路結構。采用速度補償解決了高速高分辨采樣保持電

2010-05-24 15:44:21 49

49 一種100MHz采樣頻率CMOS采樣/保持電路

摘要: 設計了一種高速采樣保持電路。該電路采用套筒級聯增益自舉運算放大器,可在達到高增益高帶寬的同時最大程度地減

2010-05-24 15:52:26 38

38

為提高中頻采樣系統性能,降低板級噪聲,加大采樣頻率的靈活性,設計并實現一種高性能中頻采樣系統。該系統利用AD9518-4實現可配置的采樣時鐘,根據不同的采樣要

2010-12-07 13:40:23 22

22 采樣保持電路

2009-01-02 01:06:50 1471

1471

采樣保持放大器

采樣保持電路(采樣/保持器)又稱為采樣保持放大器。當對模擬信號進行A/D轉換時,需要一定的轉換時間,在這個轉換時間內,模擬信號要保持基本不變,這

2009-03-11 18:29:56 3785

3785

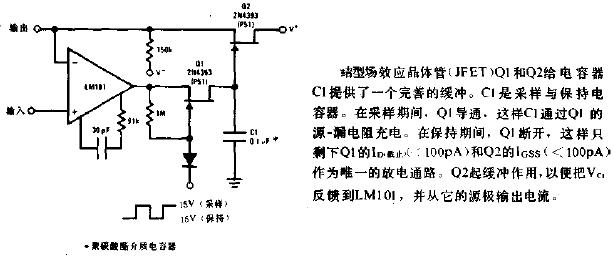

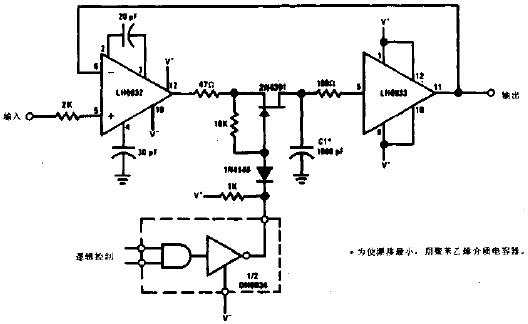

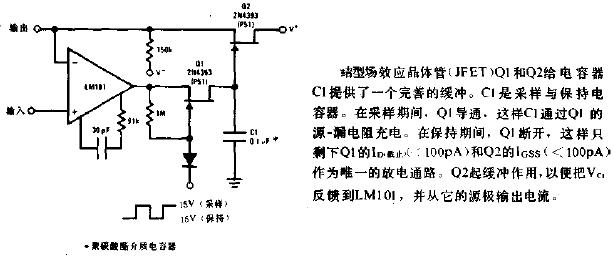

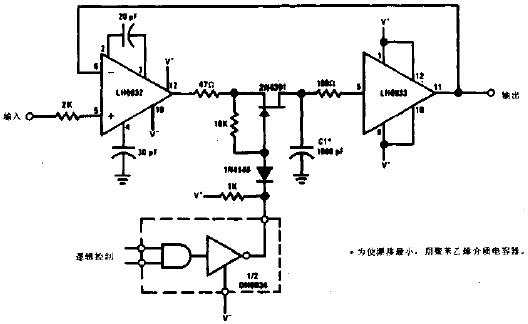

×1000采樣與保持電路圖

2009-04-09 09:23:26 799

799

采樣與保持電路圖

2009-04-09 09:23:54 1253

1253

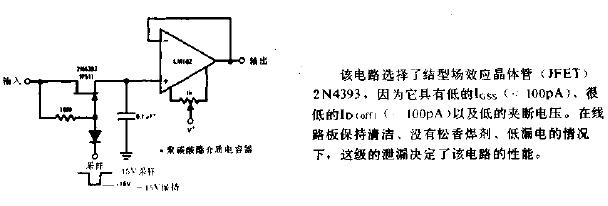

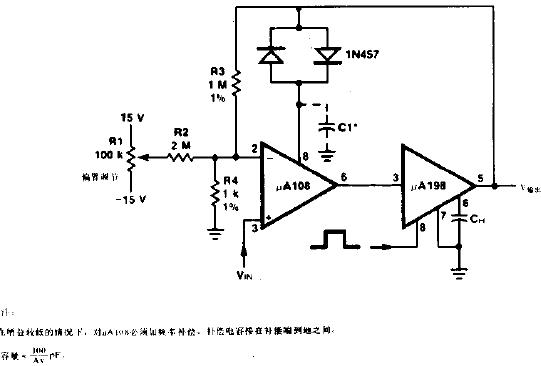

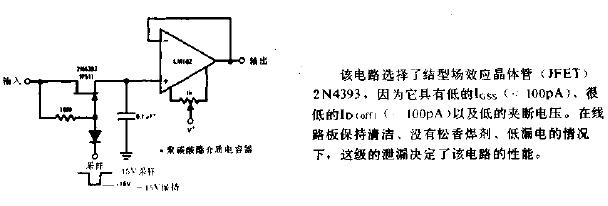

低漂移采樣與保持電路圖

2009-04-09 09:24:27 568

568

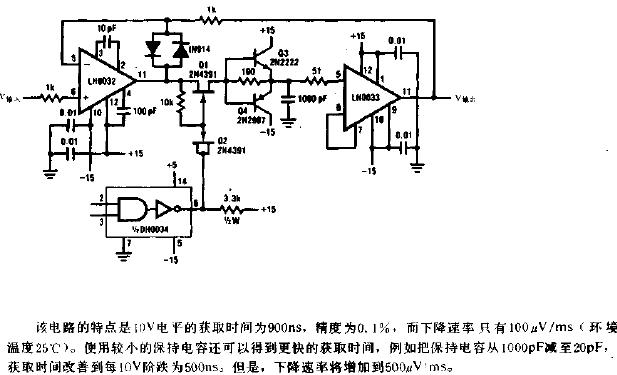

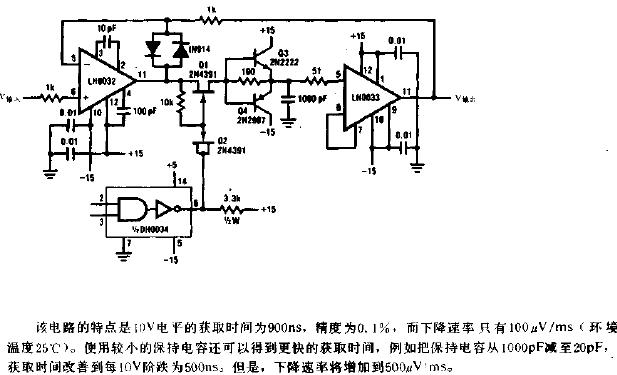

高精度采樣與保持電路圖

2009-04-09 09:25:48 1428

1428

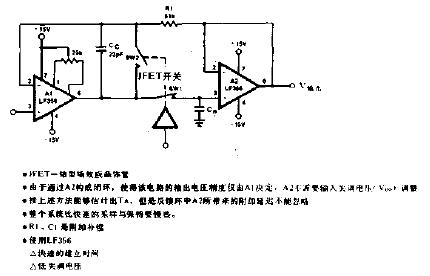

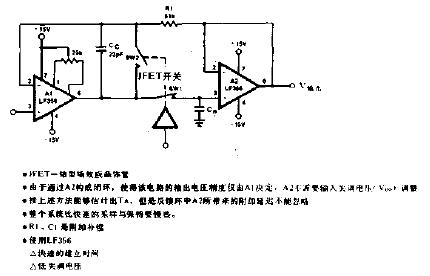

高速采樣與保持電路圖1

2009-04-09 09:26:15 667

667

高速采樣與保持電路圖2

2009-04-09 09:26:58 612

612

高速采樣與保持電路圖3

2009-04-09 09:27:24 619

619

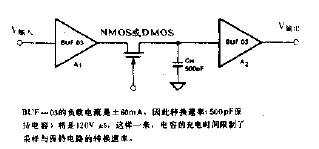

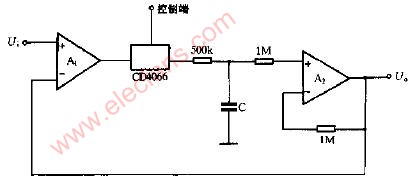

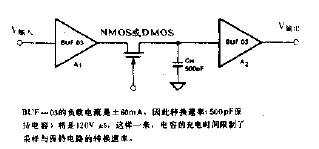

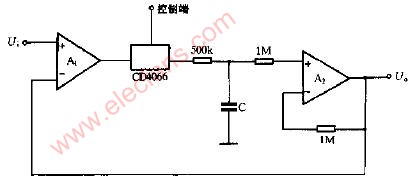

失調量可調的采樣與保持電路圖

2009-04-09 09:28:47 386

386

采樣保持電路(S/H)原理

A/D轉換需要一定時間,在轉換過程中,如果送給ADC的模擬量發生變化,則不能保證精度。為此,在ADC前加入采樣保持電路,如圖8-30所示。采樣保持電路有兩種

2009-04-12 12:01:35 22785

22785

采樣信號保持電路圖

2009-05-08 14:28:55 1034

1034

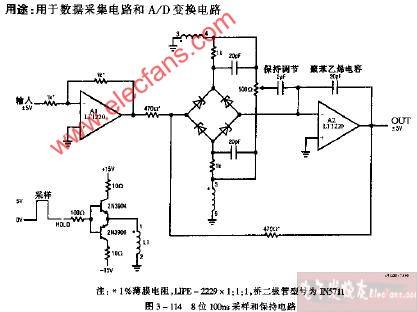

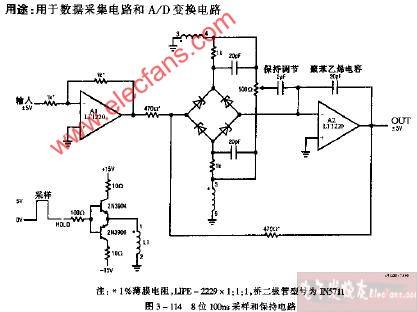

8位100ms采樣和保持電路圖

2009-06-29 09:56:42 613

613

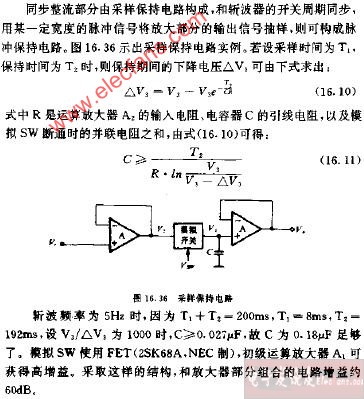

采樣保持電路圖

2009-07-08 11:40:58 976

976

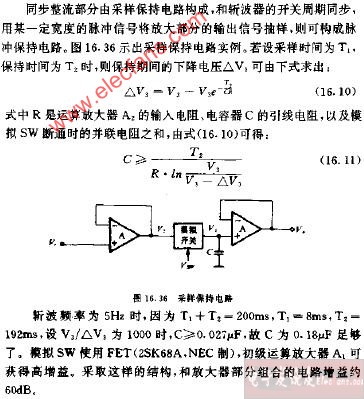

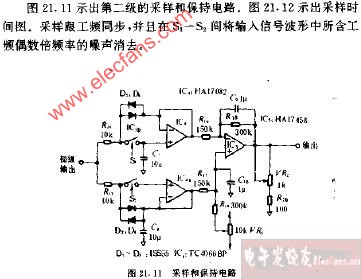

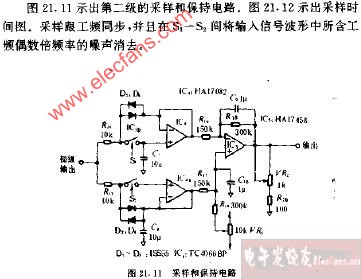

第二級采樣和保持電路圖

2009-07-09 12:26:15 514

514

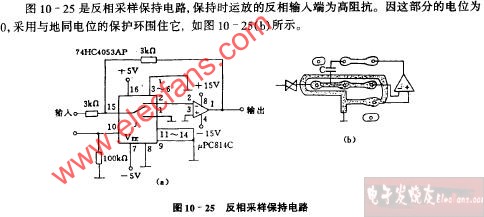

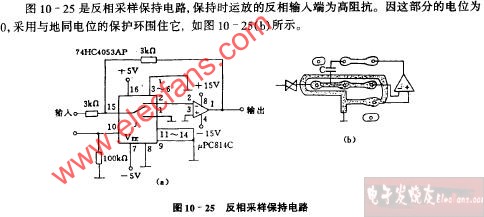

反相采樣保持電路圖

2009-07-17 14:43:55 647

647

同相采樣保持電路圖

2009-07-17 14:51:13 712

712

DS1843 高速采樣/保持電路

DS1843是一款采樣/保持電路,對于電路板空間受限的快速信號采集

2009-11-16 17:57:24 1318

1318

采樣時間為20US的中速采樣和保持電路

電路的功能

所謂采樣和保持

2010-05-05 15:53:51 1382

1382

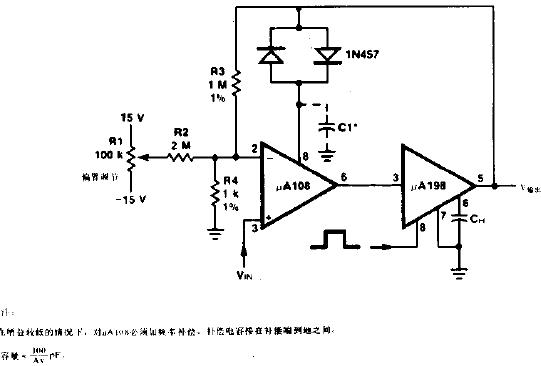

單片采樣保持電路

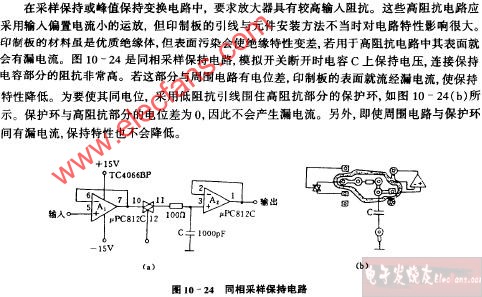

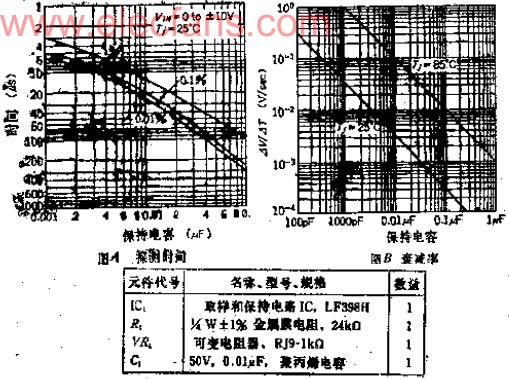

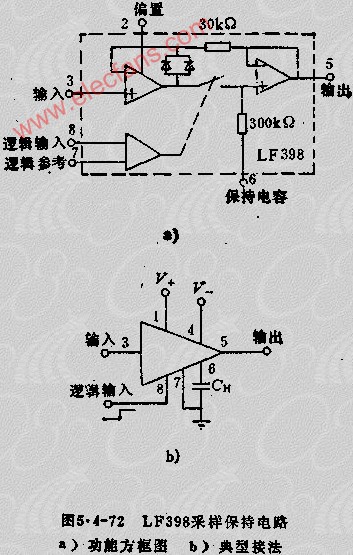

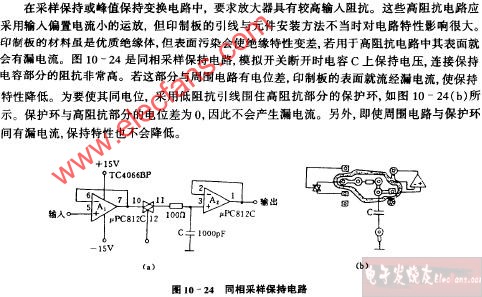

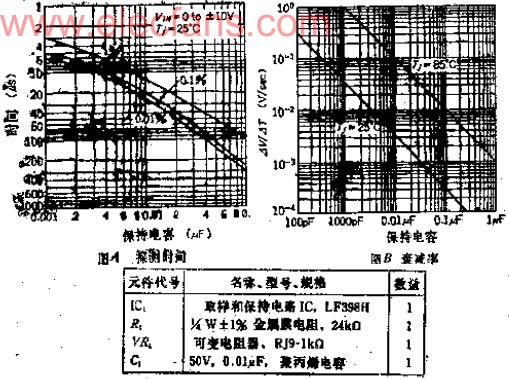

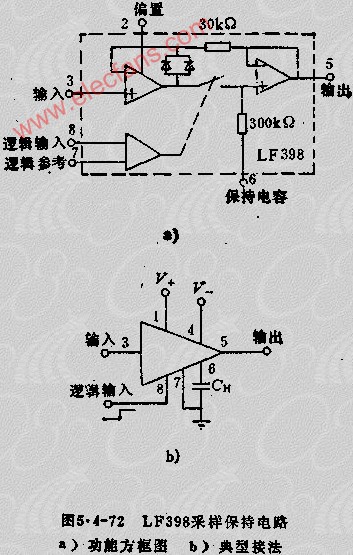

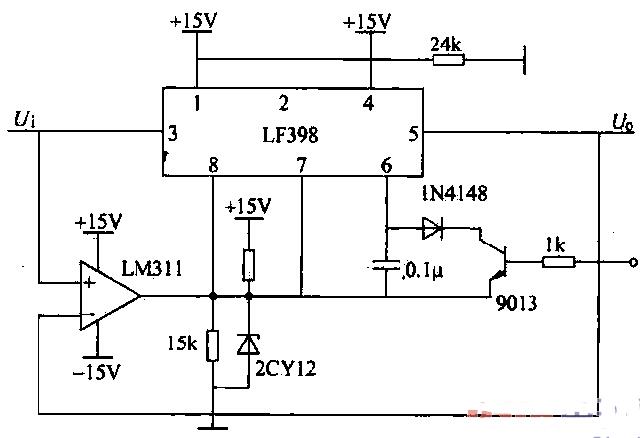

現在已有多種單片采樣保持電路的產品。圖5.4-72是單片采樣保持電路LF398。該電路在作為單位增益跟隨器使用時,其DC增益精度為0.002%到0.01

2010-05-23 18:19:30 2995

2995

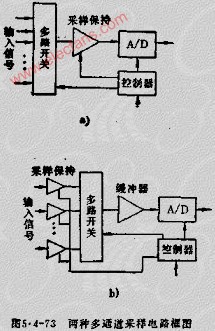

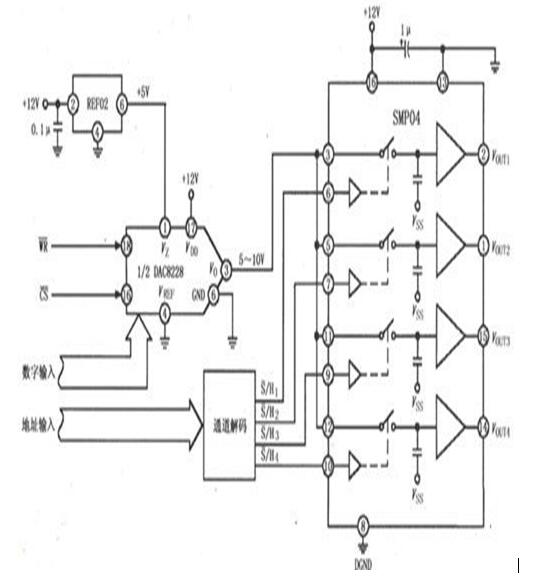

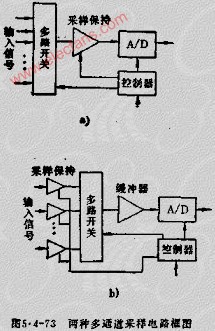

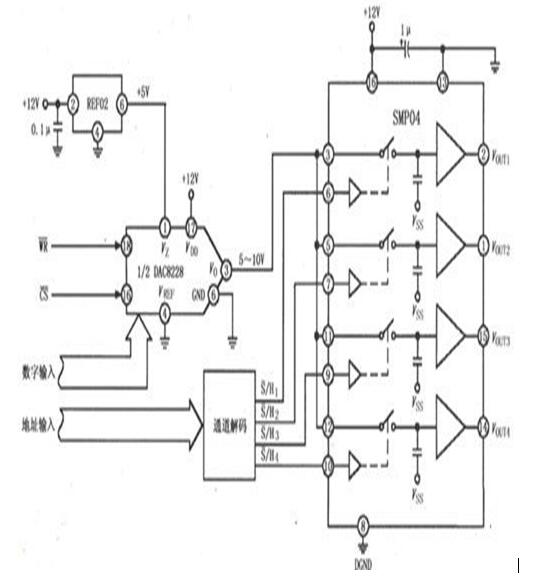

多通道采樣電路結構

由于輸入信號的數目,輸入信號的電平和采樣速度快慢的不同,多通道采樣電路的結構不

2010-05-23 18:54:51 958

958

本文采用一種全差分電荷轉移型結構的采樣保持電路,這種結構可以很好地消除與輸入信號無關的電荷注入和時鐘饋通;通過底極板采樣技術,消除與輸入信號相關的電荷注入和

2010-06-07 14:46:26 2585

2585

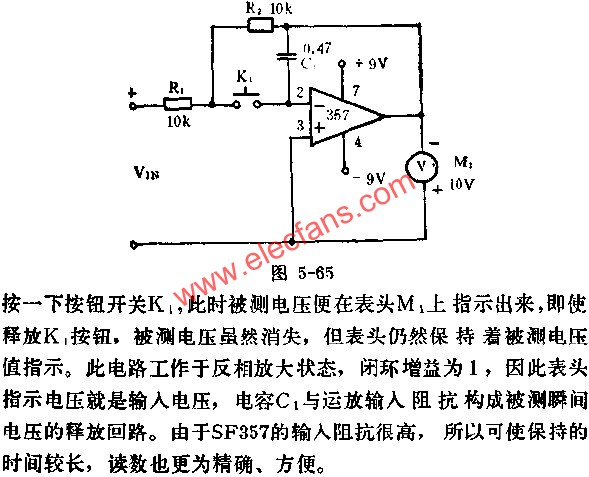

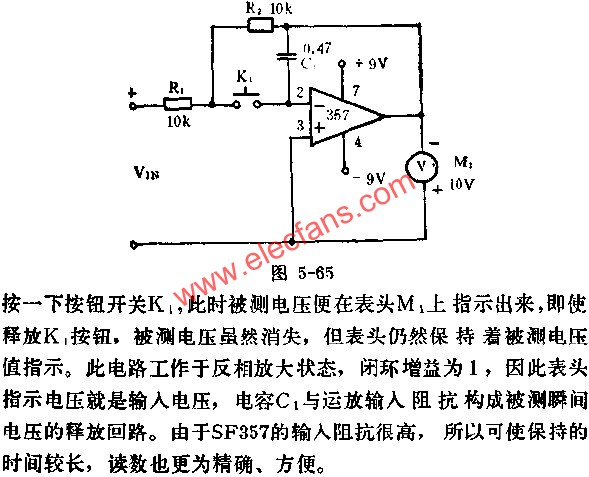

圖中所示是用SF357運放組成的電壓采樣保持電路.這種電壓采樣保持電路可以方便地觀察任一時間內的被測瞬間電

2010-10-08 12:53:57 12120

12120

Monolithic Sample-and-Hold Circuits采樣保持電路SHC

2015-11-30 18:31:05 112

112 介紹了一種以采樣/ 保持器L F398 芯片為主要器件的峰值保持電路。該電路具有結構簡單、調試方便、性能優良等優點可廣泛應用于各種脈沖分析系統。

2016-03-16 14:48:35 131

131 摘要 :本文介紹了一種以采樣/ 保持器 L F398 芯片為主要器件的峰值保持電路。該電路具有結構簡單、調試方便、性能優良等優點 ,可廣泛應用于各種脈沖分析系統。

2017-11-04 10:07:35 24454

24454

的模塊,采樣保持電路的性能直接決定了整個ADC的性能,在以上系統中對功耗的要求十分嚴格。本設計在實現高速高精度采樣保持功能的同時,還實現了MDAC功能,這樣既能降低ADC功耗又能減少芯片面積。

2019-06-13 08:19:00 4768

4768

采樣保持電路(S/H)是數據采集系統尤其是模數轉換器(A/D)的一個重要組成部分。近幾十年來無線通訊的迅速發展,使得數據的傳輸速率越來越快。復雜度不斷提高的調制系統和電路使得模數轉換器(ADC)的采樣頻率達到射頻的數量級,與此同時,模數轉換器的精度也超過12位以上。

2019-12-18 07:54:00 4366

4366

關鍵詞:AD9101 , 采樣保持放大器 , 接口電路 如圖所示為AD9101用于快速(Flash)采樣的接口電路。當信號頻率增加時,傳統的快速采樣電路不得不犧牲動態范圍以換取整體性能的穩定。圖中

2019-01-28 18:48:01 347

347 的基本特點與AD781相同。AD783采用模擬器件公司的ABCMOS制造工藝,ABCMOS工藝綜合了高性能、低噪聲雙極性電路和低功率CMOS邏輯,提供一個精確、高速和低功率的SHA。AD783有J級、A級、S級3個溫度等級,其引腳排列如圖所示。

2019-01-31 07:40:01 1374

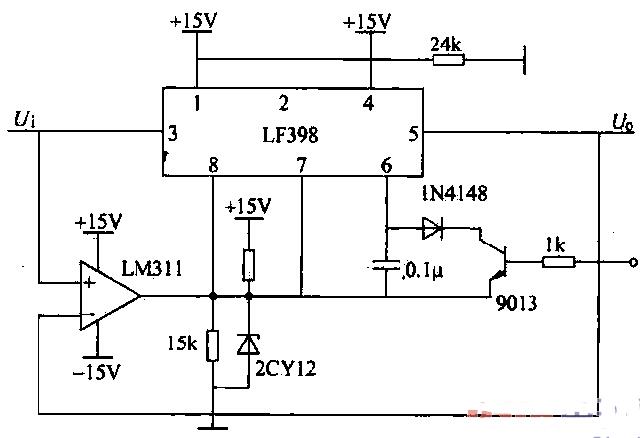

1374 峰值電壓采樣保持電路:峰值電壓采樣保持電路如圖12-50所示。峰值電壓采樣保持電路南一片采樣保持器芯片LF398和一塊電壓比較器LM311構成。LF398的輸出電壓和輸入電壓通過LM3J1進行比較t當U.》Uo時.

2020-01-21 17:21:00 14502

14502

采樣保持電路能夠跟蹤或者保持輸入模擬信號的電平值。在理想狀況下,當處于采樣狀態時,采樣保持電路的輸出信號跟隨輸入信號變化而變化。

2020-03-31 16:48:01 1306

1306

采樣/保持電路是模數轉換器的重要組成部分,它的性能決定著整個A/D轉換器的性能。隨著科學技術的發展,系統對A/D轉換器的速度和精度要求越來越高,因此,設計一個高性能的采樣/保持電路就顯得尤為重要。

2021-03-23 10:34:50 5161

5161

在可編程邏輯控制器(PLC)輸出模塊中存在每通道采樣保持架構,它采用開關電容和緩沖器作為采樣保持放大器(SHA),以便存儲單通道高性能DAC的選定輸出樣本。這些樣本通過-一個模擬開關或多路復用器在不同保持電容之間切換。

2023-03-17 15:22:45 1341

1341

ADI公司推出的AD9251是雙通道、14位ADC,70MHz模擬輸入頻率下具備73.5dB的SNR和85dB的SFDR,80MSPS的產品每通道功耗僅為86mW。AD9251集成高性能采樣保持電路

2022-05-06 10:35:25 509

509

![]()

![]()

![]()

![]()

![]()

![]()

![]()

電子發燒友App

電子發燒友App

評論