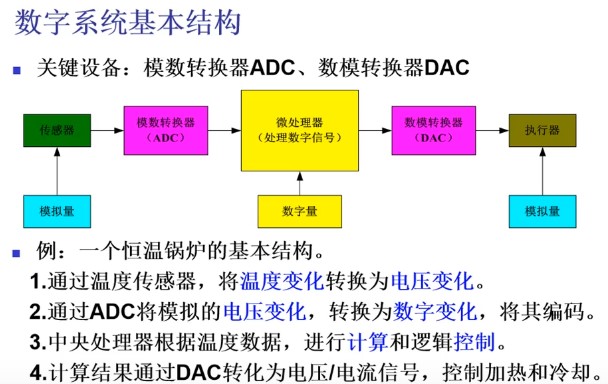

1、概述

AD5532是美國(guó)ADI公司推出的一款32通道、14位串行輸入、電壓輸出型單片集成數(shù)模轉(zhuǎn)換器。它還內(nèi)置一個(gè)額外的A/D轉(zhuǎn)換器,能將外部電壓采樣數(shù)據(jù)傳遞至相應(yīng)D/A單元,可以實(shí)現(xiàn)精度高達(dá)±0.018%的無(wú)限采樣保持功能。AD5532具有串行輸人、多通道模擬輸出等特性,適用于對(duì)性能、功耗要求高,模擬通道需求多的測(cè)控系統(tǒng)。

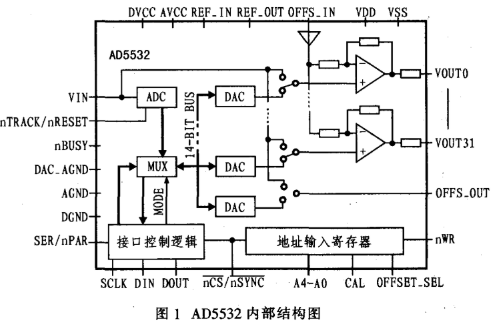

2、內(nèi)部結(jié)構(gòu)及引腳功能

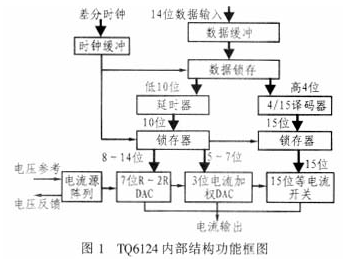

圖1所示為AD5532的內(nèi)部結(jié)構(gòu)框圖,AD5532片內(nèi)集成1個(gè)A/D轉(zhuǎn)換單元(專為ISHA模式設(shè)置)和32個(gè)D/A轉(zhuǎn)換單元,每個(gè)D/A轉(zhuǎn)換單元均配有一個(gè)輸出緩沖器。此外,片上還有串行、并行邏輯電路易于外部控制器相連。在D/A轉(zhuǎn)換模式下,需要通過(guò)串行輸入方式將14 bit的數(shù)據(jù)傳送到32個(gè)D/A轉(zhuǎn)換寄存器中的某一個(gè),隨后,該數(shù)據(jù)將轉(zhuǎn)換為模擬輸出VOUT0~VOUT31(帶有增益和偏移)。

AD5532的引腳功能描述如下:

AVCC:模擬供電電壓,范圍為4.75 V~5.25 V,只向D/A轉(zhuǎn)換器內(nèi)核供電;

VDD:正電源端,范圍為8 V~16.5 V;

VSS:負(fù)電源端,電壓范圍-4.75 V~-16.5 V;

DGND:數(shù)字地,數(shù)字電路的參考點(diǎn);

DVCC:數(shù)字電源端數(shù)字信號(hào)供電電壓,范圍為2.7 V~5.25 V;

DAC_GND:所有D/A轉(zhuǎn)換模塊的參考地;

REF_IN:VOUT0~VOUT31的參考輸入電壓;

REF_OUT:內(nèi)部參考輸出電壓,提供3 V電壓;

VOUT:32個(gè)通道的輸出;

VIN:無(wú)限采樣/保持模擬輸入電壓,在D/A轉(zhuǎn)換模式時(shí),該引腳接地;

A4~A0:并行模式下端口地址,5個(gè)地址引腳選定32個(gè)通道。A4是通道地址的MSB,A0是通道地址的LSB。每個(gè)引腳均有內(nèi)部上拉電阻,因此,這些引腳懸空時(shí),默認(rèn)為邏輯高電平;

CAL:并行模式下控制32個(gè)D/A轉(zhuǎn)換單元同步向VIN采樣,接內(nèi)部下拉電阻,因此,該引腳懸空時(shí),默認(rèn)為邏輯低電平;

nCS/nSYNC:低電平時(shí),在并行模式下,片選使能;在串行模式下為幀同步;

nWR:在并行模式下有效,寫信號(hào),低電平有效,配合nCS/nSYNC引腳可通過(guò)并口確定地址,內(nèi)部下拉電阻,懸空時(shí)默認(rèn)為邏輯低電平;

OFFSET_SEL:并行模式下有效,偏移選擇,高電平有效,用于選擇偏移通道,內(nèi)部下拉電阻,懸空時(shí)默認(rèn)為邏輯低電平;

SCLK:串行模式下的串行時(shí)鐘輸入,工作頻率為14 MHz,20 MHz時(shí)工作在ISHA模式。

DIN:串行模式下的串行數(shù)字輸入,在SCLK下降沿?cái)?shù)據(jù)有效,內(nèi)部上拉電阻,懸空時(shí)默認(rèn)為邏輯高;

DOUT:串行模式下的串行數(shù)字輸出,在SCLK上升沿?cái)?shù)據(jù)輸出;

SER/nPAR:允許用戶選擇串行接口或并行接口模式,當(dāng)拉為低電平時(shí),選擇并行接口模式,當(dāng)拉為高電平時(shí),選擇串行接口模式。內(nèi)部下拉電阻懸空時(shí)默認(rèn)為邏輯低;

OFFS_IN:偏移輸入,改變其輸入電壓調(diào)節(jié)VOUT的輸出范圍;

OFFS_OUT:偏移輸出,連接至OFFS_IN可調(diào)節(jié)VOUT的輸出范圍;

BUSY:使能采樣輸入電壓,該引腳下降時(shí),采樣輸入信號(hào),上升時(shí),采樣完成;

nTRACK/nRESET:該引腳保持高電平時(shí),一旦通道被選中,采樣VIN;該引腳保持低電平時(shí),直接切換至GAIN/OFFSET環(huán)節(jié)輸入至VIN,選定通道在nTRACK的上升沿采樣VIN。該引腳也可用于將器件復(fù)位至上電復(fù)位階段。內(nèi)部上拉電阻,懸空時(shí)默認(rèn)為邏輯高電平。

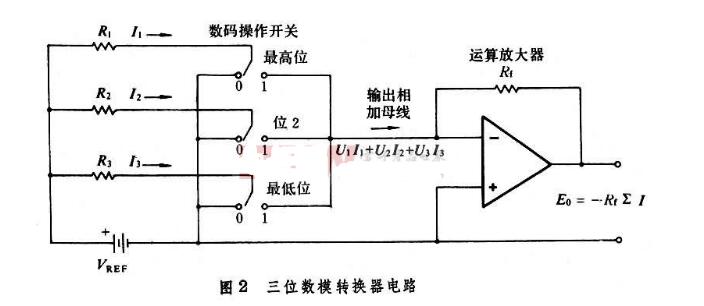

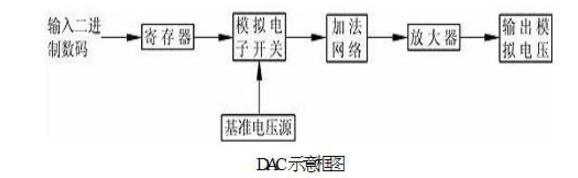

3、工作原理

AD5532提供串并行兩種控制方式,數(shù)字/模擬轉(zhuǎn)換、無(wú)限采樣/保持、回讀以及采樣回讀四種工作模式,其中并行控制方式只在無(wú)限采樣/保持模式下起作用。

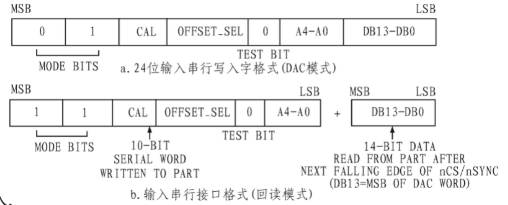

圖2的a、b分別是DAC模式和回讀模式下的數(shù)據(jù)傳輸格式。這兩種模式下的數(shù)據(jù)傳輸格式基本相同,只是MODE BIT不同。圖b中DIN引腳上的數(shù)據(jù)在輸入A0位后自動(dòng)忽略,DOUT在第2個(gè)nCS/nSYNC下降沿后輸出相應(yīng)DAC寄存器中DB13~DB0位。

串行數(shù)據(jù)傳輸格式的前2位為工作模式位。CAL位在DAC工作模式下是測(cè)試位,為‘1’時(shí)32個(gè)DAC寄存器同時(shí)置‘1’或‘0’。OFFSET_SEL位為‘1’時(shí)表示選用OFFSET通道,A4~A0位忽略。A4~A0位為地址位,這5位數(shù)據(jù)確定相應(yīng)的DAC,A4為MSB,A0為L(zhǎng)SB。DB13~DB0位中的數(shù)據(jù),寫入由A4~A0確定的DAC寄存器,其中,DB13為MSB,DB0為L(zhǎng)SB。

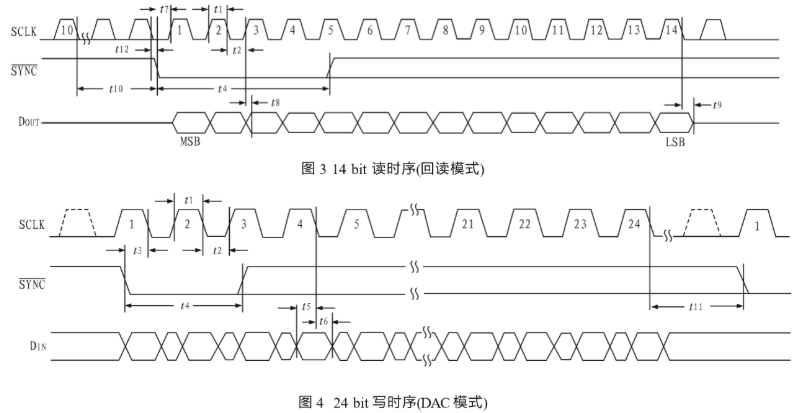

圖3和圖4所示分別為AD5532的串行讀、寫時(shí)序。在連續(xù)或非連續(xù)串行時(shí)鐘下。在nCS/nSYNC的第一個(gè)下降沿復(fù)位計(jì)數(shù)串行時(shí)鐘計(jì)數(shù)器,確保相應(yīng)位移入或移出串行寄存器。一旦在所選的工作模式下移人或移出數(shù)據(jù)位后,SCLK信號(hào)被忽略。下一次串行數(shù)據(jù)傳輸時(shí)首先利用nCS/nSYNC的下降沿復(fù)位計(jì)數(shù)器。

回讀模式下,nCS/nSYNC的下降沿后第一個(gè)SCLK的上升沿時(shí)DOUT離開(kāi)高阻狀態(tài)并在其上升沿輸出數(shù)據(jù),一旦到達(dá)SCLK的第14個(gè)下降沿DOUT返回高阻狀態(tài)。DIN上的數(shù)據(jù)在nCS/nSYNC下降沿后的第一個(gè)SCLK的下降沿被鎖存并在后續(xù)的SCLK下降沿連續(xù)鎖存。串行接口僅在SYNC的下降沿時(shí)輸入/輸出數(shù)據(jù)。

4、 典型應(yīng)用

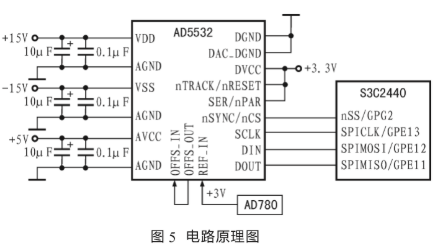

圖5所示為AD5532在DAC工作模式下的典型應(yīng)用原理圖。其中VDD提供+15 V電壓,VSS提供-15 V電壓,AVCC提供+5 V電壓,與三星公司S3C2440相連,DVCC提供+3.3 V電壓。由于本系統(tǒng)僅需DAC功能,所以將SER/nPAR及nTRACK/nRESET引腳電壓拉高,串行輸入/輸出引腳與S3C2440的相應(yīng)SPI引腳相連。其余未涉及引腳如果是輸入端最好接地或拉高。

S3C2440采用兩種方式實(shí)現(xiàn)與AD5532的串口通信:一是采用串行外圍設(shè)備接口(SPI接口);二是通過(guò)直接編程控制相應(yīng)I/O引腳實(shí)現(xiàn)通信功能(軟件SPI方式)。前者SPI模塊在一系列寄存器設(shè)置后,由硬件自動(dòng)實(shí)現(xiàn)數(shù)據(jù)的移入和移出完成串行通信;后者是通過(guò)軟件控制I/O端口,逐位將數(shù)據(jù)由端口發(fā)送或接收。由于AD5532串行接口在D/A輸出時(shí)接收24位數(shù)據(jù),而回讀時(shí)只需10位數(shù)據(jù),不符合S3C2440的SPI接口傳輸時(shí)8位數(shù)據(jù)對(duì)齊要求。故本系統(tǒng)采用軟件SPI方式,根據(jù)D/A輸出模式與回讀模式下數(shù)據(jù)傳輸格式編寫相關(guān)函數(shù)。

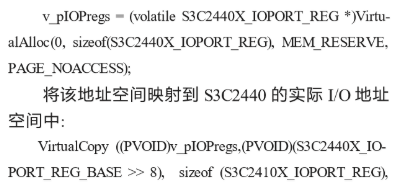

系統(tǒng)采用Windows CE.NET4.2操作系統(tǒng),程序運(yùn)行空間分成內(nèi)核態(tài)與用戶態(tài),且所有地址均為虛擬地址。由于應(yīng)用程序無(wú)法訪問(wèn)I/O引腳的控制與數(shù)據(jù)寄存器,所以編寫函數(shù)前需先按照WindowsCE.NET驅(qū)動(dòng)程序方式編寫:先申請(qǐng)某一內(nèi)存地址空間,然后將該地址空間映射到I/O引腳的寄存器,最后對(duì)該地址相應(yīng)位進(jìn)行讀寫操作,模擬AD5532所需的串行傳輸方式控制器件。申請(qǐng)地址空間:

完成了上述步驟,可通過(guò)讀寫v_pIOPregs實(shí)際控制相應(yīng)引腳。

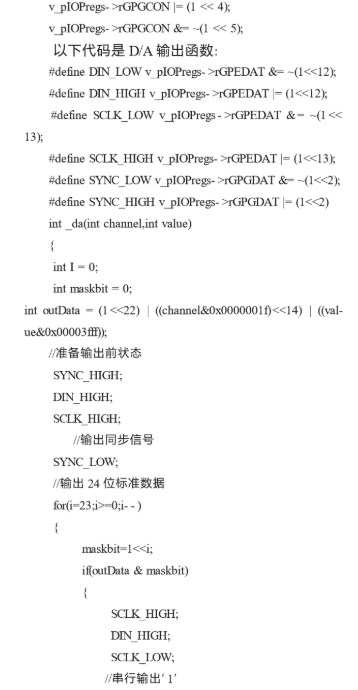

SPICLK/GPE13,SPIMOSI/GPE12,SPIMISO/GPE11引腳輸人/輸出狀態(tài)設(shè)置:

以上函數(shù)中channel取0~31,被移位到低14位時(shí),表示選擇的通道;value取低14位,表示輸出的具體值。

將以上代碼加入到應(yīng)用程序源代碼中,就可根據(jù)需要調(diào)用函數(shù)訪問(wèn)AD5532進(jìn)行D/A輸出。當(dāng)然,在編譯前,還需要找到pkfunc.h,ceddk.h,Winbase.h文件,并將其放置在源代碼目錄下,并申請(qǐng)內(nèi)存空間及映射內(nèi)存空間代碼文件頭include進(jìn)去,否則應(yīng)用程序最后無(wú)法編譯,提示找不到相應(yīng)函數(shù)。

5、 結(jié)束語(yǔ)

采用AD5532串行模式進(jìn)行D/A轉(zhuǎn)換具有速度快、精度高、功耗低、占用口線少的優(yōu)點(diǎn),非常適用于需要多通道,寬范圍模擬信號(hào)輸出的場(chǎng)合。該系統(tǒng)電路已在實(shí)驗(yàn)中調(diào)試通過(guò)。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論