幾乎所有的電子系統都需要針對一個或多個處理器以及許多相關外圍IC的多個時鐘信號,以建立該系統的運行節奏。這些時鐘信號通常由石英晶體產生,頻率范圍可以從幾MHz到幾百MHz。

雖然許多集成電路都需要這些時鐘信號,但在大多數設計中采用多個晶體作為主時鐘源并不現實,也不是所期望的方式。其原因是,使用多個獨立的時鐘源會帶來這些時鐘與靶標同步的問題,提高了系統成本,同時增大了對于電路板面積的要求。相反,設計者幾乎總是選擇使用一個單一的主時鐘振蕩器作為時鐘源,再將時鐘信號分配給整個系統中的各個組件。

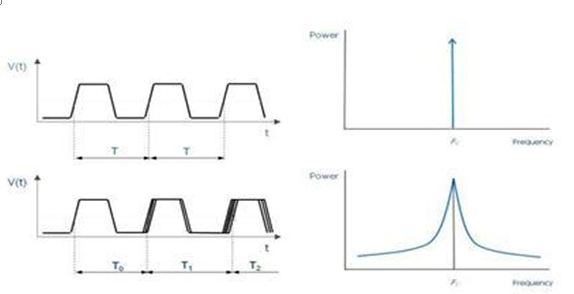

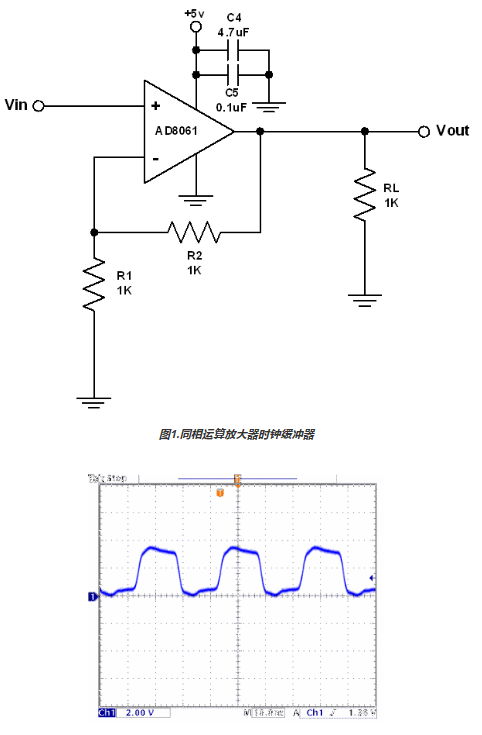

但這種解決方案也不是沒有挑戰。首先,所有的時鐘都不是完美的,每個時鐘,即使是在一個精心設計的振蕩電路中的一個精準晶體,也會圍繞其標稱頻率產生一些相關的抖動和微小的時序變化,如圖1a所示,這相當于在頻域中的相位噪聲,見圖1b。

主時鐘的固有缺點只是問題的開始。時鐘振蕩器通常不能支持所有必須的負載,也不能驅動連接信號源與負載之間的電路布線或電纜。

圖1:有兩種同樣有效的方式來分析抖動:a)在時域中,采用一個完美的時鐘(頂部)和具有抖動的時鐘(底部),顯示細微的時間差別(相移)。b)在頻域中,采用同樣完美的時鐘(頂部)和具有抖動的時鐘(底部),顯現出圍繞標稱值的頻率偏移。

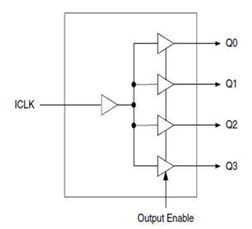

為了克服這一驅動能力的不足,需要一個專門的時鐘緩沖器IC用于在樹狀拓撲架構下升壓和“扇出”主時鐘,如圖2所示。緩沖器功能簡單,并只完成一項工作:它以時鐘源作為其輸入,并且提供能夠盡可能完美復制時鐘輸入的多個輸出。

圖2:根據所用的時鐘樹拓撲架構,在時鐘源和最終時鐘負載之間可以采用一個或多個時鐘緩沖器。

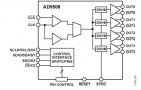

盡管這種功能往往不是很引人注目,也不可能得到太多的關注和重視,但它在系統整體性能、信號完整性、以及系統和電路的一致性、可靠性方面起著重要作用。目前市場上有可以驅動2個、4個、8個甚至更多負載的緩沖器IC,能夠緊密配合設計的需要,無需額外的成本費用或電路板空間,如圖3所示。

圖3:類似IDT 5PB11xx的時鐘緩沖器可提供扇出數4(指定于1:4緩沖器);簡單的功能圖無需顯示內部的設計細節。

采用一個緩沖器:簡單,但不是沒有挑戰

理想的時鐘緩沖器能夠傳輸得到升壓的輸入時鐘,但不能有任何附加的抖動、延遲、失真、或其他不利因素。像所有其他組件一樣,這種理想的時鐘緩沖器并不存在,而一些器件卻可以很接近、非常接近理想情況。顯然,緩沖器會占據PCB空間、消耗功率、并增加成本,它們還會把自身的抖動增加到時鐘的內在抖動上。但現實中沒有可行的替代方案,因此,我們的目標必須是要獲得與應用良好匹配的時鐘緩沖器。

這里重要的是要理解為什么緩沖器的低抖動如此至關重要。從網絡設備、高端PC到儀器設備,當今許多電子產品所允許的抖動指標非常小。很多這些產品的典型抖動值約為100 fs(飛秒,為10-15秒,或十億分之一秒的百萬分之一),比幾年之前認為是高性能的指標高出一個量級。

一般情況下,緩沖器的抖動遠比時鐘的抖動要小,所以主要抖動源是時鐘,而不是其緩沖器。緩沖器輸出驅動的所有負載的復合抖動是時鐘和緩沖器抖動值的均方根(rms)組合。例如,一個時鐘具有抖動400fs(均方根值),其緩沖器抖動為50fs(均方根值),結果只有5fs的有效附加均方根抖動,所以緩沖器對于組合均方根抖動的貢獻比時鐘小很多。(請注意,這里只是抖動的一個頂級特性,抖動是一個多方面的、非常復雜的問題;見附文“抖動表征和測試。”)

對于抖動期望在收緊

既然緩沖器對于整體抖動的貢獻如此之小,為何還要關心使用更好、具有更低抖動的緩沖器呢?簡言之,當今電子產品的系統時鐘速度發展趨勢和要求在影響所需的參數。隨著系統性能和時鐘速度提高,時鐘必須比上一代產品有更低的抖動。其結果是,具有更低抖動的時鐘緩沖器對于保證負載端的性能要求非常重要。

通過對粗略數字的基本分析可以使這一點更加清晰。在時鐘和緩沖器的抖動相等時(這種情況在時鐘抖動不斷縮小時可能發生),得到的抖動均方根值為√2(≈1.4)比單獨的時鐘要高,幾乎增加50%以上。其結果是,各個負載端的時鐘信號性能與時鐘的原始值相比顯著降低。因此,隨著時鐘性能變好,具有更低的抖動時,關鍵是要降低緩沖器的抖動,甚至更多,這樣緩沖器對于整體抖動的貢獻可以最小化。

傳統上,電路設計者對于過度抖動問題的解決途徑需要在緩沖器性能參數之間進行不令人滿意的折衷。他們可以選擇具有低抖動的緩沖器,但要做到這一點,這些緩沖器要消耗更高的電流和/或電壓。簡而言之,更低的抖動需要更大的電流。不幸的是,這意味著緩沖器用戶陷入較高功耗、更多低能效組件的困境,從而降低了電池供電產品的運行時間,增大了散熱量,這些都是不依賴于電源以及是否有足夠的散熱措施都必須要考慮的。

現在的好消息是,這種傳統的折衷已經不再需要。IDT公司全新系列的時鐘緩沖器基于經過驗證的IC工藝,同時采用了設計和拓撲結構方面的創新,實現了極低的抖動但功耗并沒有增加,同時還具有更小的芯片尺寸,能夠采用一系列的電源軌供電運行。例如,IDT 5PB11xx系列LVCMOS扇出緩沖器在12 kHz 到 200 MHz范圍內具有低于50fs的均方根附加相位抖動,而內核電流只有15mA。

通過仔細分析在此頻率范圍內的均方根附加相位抖動曲線可以更明顯地看到這些得到的好處。圖4a展示的是在5PB11xx緩沖器輸入端來自于200-MHz時鐘源的抖動,而圖4b則示出了相同的參數,但是在緩沖器輸出端。即使在最高頻率(這是最具挑戰性的區域)時,附加抖動僅為31.6 fs。IDT公司產品系列的其他器件具有不同的輸出扇出和配置變化,但都具有類似的低附加抖動。

圖4:即使在200MHz輸入時,由IDT 5PB11xx增加到時鐘信號的附加性抖動影響只有約32fs。

除了獨特的低抖動、低功耗特性外,IDT5PB11xx緩沖器也具有其它性能優勢。它可以采用1.8V到3.3V之間的寬范圍電壓供電運行,而性能不會降低。因此在一個具有多個電源軌的較大設計中,可以在不同的地方采用同樣的部件,甚至在多個產品中采用同一部件。這不僅簡化了物料清單(BOM),同時也降低了因使用多個新部件而導致出現的附加性設計“意外”自然風險。

5PB11xx的信道與信道輸出偏移(skew)(輸出信道之間的相對時序差)僅為50ps,這對于保持多個外圍負載之間的同步至關重要。該緩沖器以一個微小的2 ×2mm DFN封裝供貨,這種小尺寸是許多先進的便攜式應用非常需要的。5PB11xx同時也可以及較大的3.9 ×4.9mm SOIC封裝供貨,可用于以往的設計進行性能升級,或用于電路板空間不是很緊張的新項目設計。

當然,雖然工作在200 MHz、性能經過大幅度改善的5PB11xx器件簡化了設計挑戰,但它并不能完全消除電路設計者的責任。在200 MHz頻率下,仍然要應用良好的設計規范,包括12至18英寸(30到45cm)長的緩沖器與負載之間最大電路板布線長度,采用PCB板上的平衡布線以降低噪聲和接地回路影響等等,同時也需要遵循其它的標準高頻設計準則。

一些設計師或許在下述兩種緩沖器之間難以抉擇:一種具有較低抖動,但有較高并難以承受的功耗;另一種具有低功耗,抖動指標卻遜色不少。IDT公司的全新時鐘緩沖器產品系列不需要再有這種折衷。除了封裝和引腳與已有產品兼容外,它們也可以更小的封裝提供,這意味著設計師不僅可以在新設計中采用該緩沖器,同時可以在已有設計中利用這些器件的優勢。

抖動表征和測試

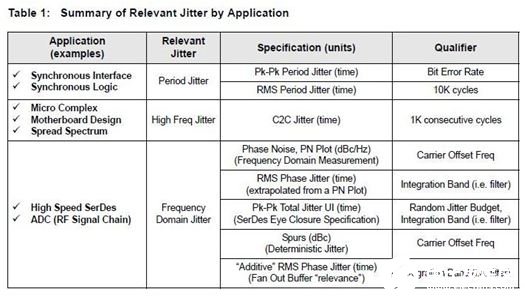

抖動是一個簡短的術語,但卻是一個擁有許多技術細節的復雜主題。不僅有許多類型的抖動,同時也有不同的度量方法來評估抖動,抖動類型和值的大小依照具體的應用而有不同的結果,欲了解更多信息,請參閱附表。兩個信息量很大的參考文獻是AN-815理解抖動單位和AN-827時鐘抖動的應用關聯。

表:使抖動指標與具體的應用匹配需要深刻理解各種不同抖動是以何種合理的方式測量得到以及他們的影響。

在評估抖動時,重要的是設計師要針對多個抖動指標做“樹狀分析”,分析它們如何匯合在一起,確保抖動結果在一定范圍內,并且抖動的系統級影響可以接受。同樣重要的是對于那些計劃實際測試并確認其抖動分析的工程師,必須要了解在當今設計中非常快的時鐘和非常低的低抖動帶來的挑戰。在設計、安裝、測試設備、計算等確認測量過程的每一個環節,都存在一些復雜而微妙的因素,有時侯很容易進行一些不當的測試,可在不經意間誤導并生成一些數字,導致對結果的過于樂觀或者過于悲觀。

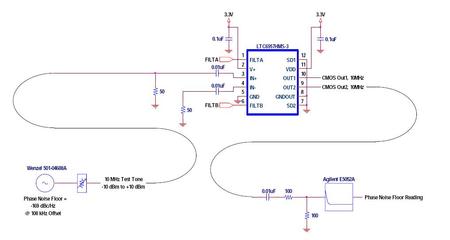

作為一家時鐘發生器和緩沖器IC的領先廠商,IDT公司擁有針對這些測試的豐富經驗,所有器件正在使用是德科技(KeysightTechnologies ,以前的安捷倫)的E5502相位噪聲測量解決方案等儀器進行測試,見圖SB-1。該儀器經專門設計,可用于在設計評估和生產階段測量非常低的相位噪聲。它采用一個具有參照源技術的相位檢測器來測量時鐘或緩沖輸出的單邊帶(SSB)相位噪聲特性。該測試裝置的設計不僅始于高精度信源,同時也采用一個獨特結構,可以抵消掉許多內部錯誤,這些錯誤因而就不會影響到被測器件上的最終數據。

圖SB-1:盡管噪聲和其他因素會影響測量效果,是德科技(安捷倫)E5502相位噪聲測量解決方案采用先進的架構以及精密的信源來實現極低抖動值的精準測量。

沒有任何一個單一的數字可以簡單地匯總所有應用中的抖動。哪些指標對于給定的設計是最相關的,并且這些是如何由時鐘組件供應商測量得出,了解這些對于在特定情況下作出最佳選擇非常關鍵。這將使設計人員在考慮設計優先性和制約性的情況下正確理解數據表的參數。

責任編輯:gt

電子發燒友App

電子發燒友App

評論