針對π網(wǎng)絡(luò)石英晶體參數(shù)測試系統(tǒng),采用以STM32F103ZET6型ARM為MCU控制DDS產(chǎn)生激勵信號。該測試系統(tǒng)相對于傳統(tǒng)的PC機(jī)測試系統(tǒng)具有設(shè)備簡單、操作方便,較之普通單片機(jī)測試系統(tǒng)又具有資源豐富、運算速度更快等優(yōu)點。AD9852型DDS在ARM控制下能產(chǎn)生0~100 MHz掃頻信號,經(jīng)試驗數(shù)據(jù)分析得到信號精度達(dá)到0.5×10-6,基本滿足設(shè)計要求。該系統(tǒng)將以其小巧、快速、操作方便、等優(yōu)點被廣泛采用。

產(chǎn)生正弦激勵信號一般可以通過振蕩電路或直接數(shù)字頻率合成器(Direct Digital Frequency Synthesis,DDS),DDS較振蕩電路具有相位噪聲小、雜散抑制好、可產(chǎn)生連續(xù)波信號、掃頻信號和頻率捷變信號等優(yōu)點。石英晶體電參數(shù)測試中激勵信號的指標(biāo)如幅度、頻率的穩(wěn)定性對后續(xù)的測量精度至關(guān)重要。所以系統(tǒng)采用AD9852型DDS作為信號源。石英晶體電參數(shù)測試系統(tǒng)中,DDS可以同時產(chǎn)生多路正弦信號,并可對信號的頻率、幅度、相位精確控制,用以測量石英晶體電參數(shù),隨著對石英晶體頻率精度的要求越來越高,DDS的信號源設(shè)計及控制具有重要現(xiàn)實意義。

1π網(wǎng)絡(luò)法測試原理

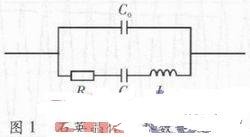

在串聯(lián)諧振狀態(tài)下,石英晶體等效電路模型如圖1所示,C0為靜態(tài)電容;L1為動態(tài)電感;Rr是串聯(lián)諧振電阻;C1為動態(tài)電容。

其等效阻抗為

![]()

式中,ω為信號源所輸出信號的角頻率,ω=2πf;Zs為π網(wǎng)絡(luò)的等效阻抗。根據(jù)式(1)可以畫出石英晶體阻抗一頻率特性曲線如圖2所示,f0為石英晶體的串聯(lián)諧振頻率,f1為并聯(lián)諧振頻率,本系統(tǒng)需要測量石英晶體的串聯(lián)諧振頻率。

由圖2可以看出,當(dāng)信號源頻率為f1時,石英晶體的阻抗最小;當(dāng)信號源頻率為時石英晶體的阻抗最大。利用這個特性可以得到石英晶體的串聯(lián)諧振頻率、并聯(lián)諧振頻率等參數(shù)。石英晶體電參數(shù)測試方法有3種:阻抗計法、π網(wǎng)絡(luò)最大傳輸法、π網(wǎng)絡(luò)零相位法。π網(wǎng)絡(luò)最大傳輸法是將石英晶體插入一個π網(wǎng)絡(luò)中,不斷改變π網(wǎng)絡(luò)一端激勵信號的頻率,在另一端測量輸出信號電壓值,當(dāng)電壓達(dá)到最大值時的頻率即為串聯(lián)諧振頻率。其特點是測試設(shè)備較復(fù)雜,不易捕獲峰值電壓時的頻率,精度較高;π網(wǎng)絡(luò)零相位法原理;π網(wǎng)絡(luò)零相位法是將石英晶體插入一個π網(wǎng)絡(luò)中,在一端不斷輸出掃頻信號,用矢量電壓表檢測π網(wǎng)兩端的相位差,當(dāng)相位差為零時的頻率即為串聯(lián)諧振頻率。π網(wǎng)絡(luò)最大傳輸法與π網(wǎng)絡(luò)零相位法的主要差別是沒有鑒相電路,將這兩種方法統(tǒng)稱為π網(wǎng)絡(luò)法。

2石英晶體測試系統(tǒng)

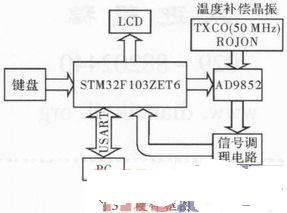

硬件框圖系統(tǒng)采用π網(wǎng)絡(luò)法,硬件框圖如圖3所示。系統(tǒng)以STM32F103ZET6型ARM為的MCU;AD9852型DDS用來產(chǎn)生正弦激勵信號;TXCO(ROJON)型溫度補(bǔ)償晶振給DDS提供參考頻率,此溫度補(bǔ)償晶振標(biāo)稱頻率50 MHz;LCD作為人機(jī)交換接口用以顯示參數(shù)和波形;4×4鍵盤可以輸入預(yù)置參數(shù),也可以作為功能按鍵控制系統(tǒng)工作;信號調(diào)理電路對激勵信號濾波以及放大跟隨,通過π網(wǎng)絡(luò)的信號經(jīng)處理反饋到STM32F103ZET6的A/D端口,對輸出信號進(jìn)行處理。MCU通過串口(USART)和上位機(jī)通信,上位機(jī)發(fā)送控制指令控制MCU工作,MCU將測試數(shù)據(jù)反饋給上位機(jī)。系統(tǒng)重點是利用STM32F103ZET6控制A139852產(chǎn)生掃頻信號,難點是對π網(wǎng)絡(luò)輸出端信號的處理。

3系統(tǒng)測試流程圖

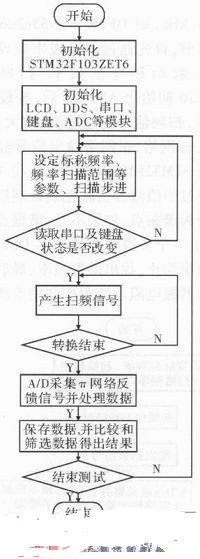

石英晶體測試參數(shù)測試儀在通電復(fù)位后首先初始化STM32F103ZET6內(nèi)部寄存器,然后再初始化系統(tǒng)各功能模塊包括LCD、DDS、USART、鍵盤、ADC等。在初始化完成之后通過鍵盤或上位機(jī)設(shè)定被測石英晶體的標(biāo)稱頻率、掃描的起始和終止頻率以及掃描步進(jìn),參數(shù)設(shè)置完成后,通過上位機(jī)發(fā)送控制指令或鍵盤功能按鍵控制系統(tǒng)工作,在串口和鍵盤未產(chǎn)生中斷時,DDS會產(chǎn)生與設(shè)置參數(shù)相應(yīng)的掃頻信號,LCD實時顯示π網(wǎng)絡(luò)反饋到STM32F103ZET6的ADC管腳的波形,待轉(zhuǎn)換結(jié)束后MCU處理并保存數(shù)據(jù),測試結(jié)果送回上位機(jī)并在LCD上顯示。具體流程圖如圖4所示。

4 DDS掃頻輸出控制

系統(tǒng)對DDS信號源設(shè)計的核心是控制產(chǎn)生0~100 MHz掃頻信號,信號的質(zhì)量直接決定測試精度。由于采用溫度補(bǔ)償晶振給AD9852提供50 MHz參考頻率信號,因為AD9852產(chǎn)生的正弦信號是用于測試石英晶體參數(shù)的,所以對其參考頻率信號穩(wěn)定度要求嚴(yán)格,TXC0(ROJON)型溫度補(bǔ)償晶振頻率負(fù)載波動±10%時,穩(wěn)定度最大為±0.1×10-6,滿足系統(tǒng)精度需求。根據(jù)AD9852的文檔得到其輸出的最大頻率為

![]()

式中,fc為AD9852內(nèi)部參考頻率;fmax為DDS最大輸出頻率。fc可以通過AD9852地址為0x1e的寄存器4倍頻,所以輸出正弦波最大頻率為100 MHz.測試時,先通過上位機(jī)或鍵盤輸入測試晶體的標(biāo)稱頻率及掃描步進(jìn),然后以標(biāo)稱頻率為中心設(shè)置適當(dāng)?shù)钠鹗紥呙桀l率及終止掃描頻率。假設(shè)一個步進(jìn)對應(yīng)的頻率控制字為DFTW,則每個步進(jìn)頻率

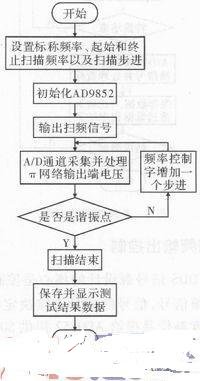

假設(shè)步進(jìn)為1 kHz,則DFTW=0x53e2d623.AD9852進(jìn)行掃頻輸出前,首先通過鍵盤或串口設(shè)置石英晶體的標(biāo)稱頻率、起始和終止頻率、掃描步進(jìn)頻率,STM32F103ZET6初始化AD9852后,按設(shè)定參數(shù)輸出相應(yīng)掃頻信號,掃頻信號經(jīng)過濾波、放大、跟隨等信號調(diào)理電路進(jìn)入π網(wǎng)絡(luò),π網(wǎng)絡(luò)輸出信號經(jīng)過放大限幅處理后反饋到STM32F103ZET6的12位A/D輸入端,在采集數(shù)據(jù)經(jīng)過中值濾波去除毛刺處理后保存數(shù)據(jù)并比較判斷是否為諧振點,如果不是,諧振點將頻率控制字FTW會加上一個步進(jìn)頻率控制字DFTW,如此直到掃描到終止頻率為止,找出諧振頻率,最后根據(jù)公式算出石英晶體的諧振電阻。流程圖如圖5所示。

5結(jié)束語

針對石英晶體參數(shù)測試系統(tǒng),介紹了利用STM32F103ZET6控制AD9852作為信號源的方法。這種方法結(jié)合了傳統(tǒng)PC機(jī)及普通單片機(jī)測試系統(tǒng)的優(yōu)點,避開了前兩者的缺點,可以快速地測試石英晶體電參數(shù)。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論