前言: 偶數(shù)分頻容易得到:N倍偶數(shù)分頻,可以通過由待分頻的時鐘觸發(fā)計數(shù)器計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,使得下一個時鐘從零開始計數(shù)。以此循環(huán)下去

2020-12-28 15:49:20 2620

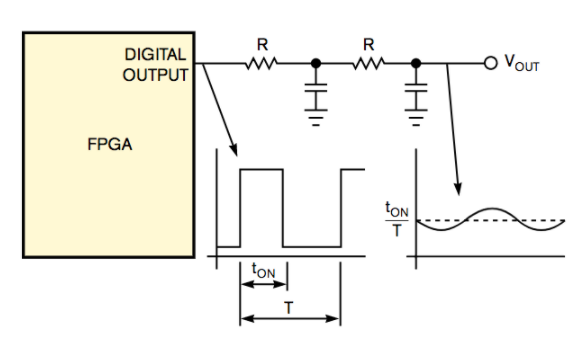

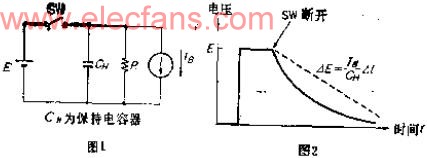

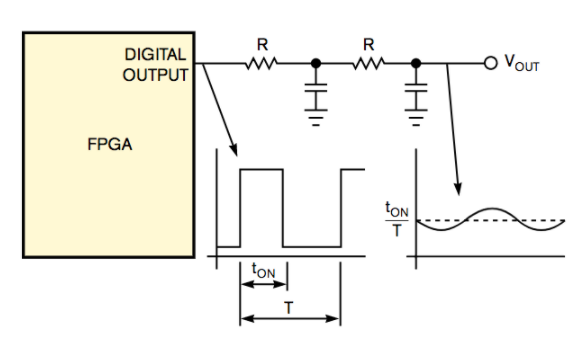

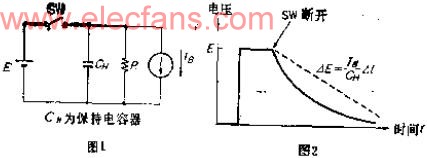

2620 當(dāng)您需要一些模擬輸出并且您的系統(tǒng)中有FPGA時,您可能選擇使用PWM模塊和簡單的低通濾波器,如圖1所示?。FPGA的輸出通常是具有固定頻率,可變占空比的波形,由計數(shù)器和數(shù)字比較器生成(清單

2021-05-13 16:22:44 4592

4592

假設(shè)時鐘分頻是N,則設(shè)置一個計數(shù)器,計數(shù)長度是N(即從0計數(shù)到N-1),然后在計數(shù)器為計數(shù)到(N-1)/2的時候,翻轉(zhuǎn)一下分頻時鐘信號。

2020-11-06 13:59:47 9658

9658

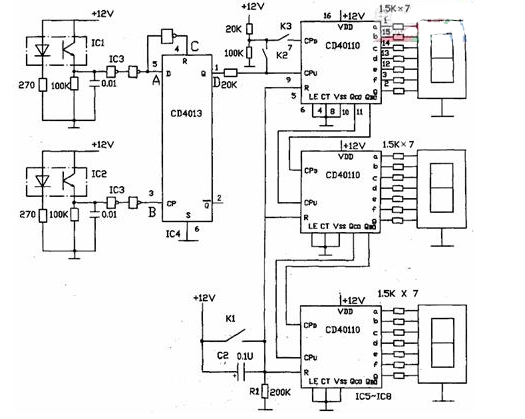

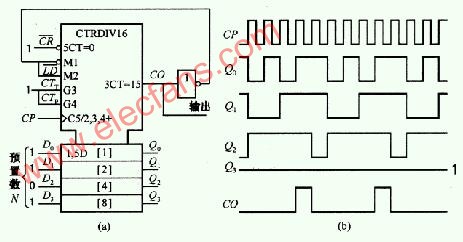

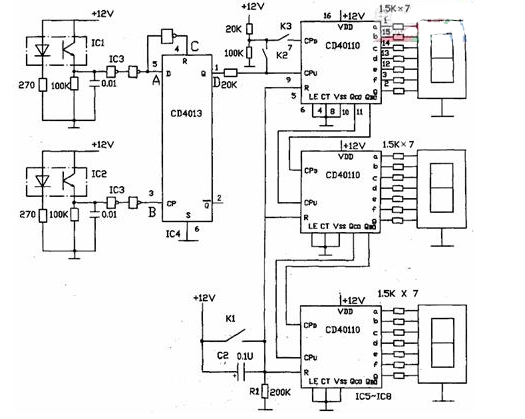

1.1 方波產(chǎn)生電路 555定時器構(gòu)成多諧振蕩電路。電路幅值與占空比可調(diào),產(chǎn)生的方波為單極性,波形上升沿較陡 1.2 分頻電路 由十六進(jìn)制計數(shù)器74LS163和觸發(fā)器HEF4013構(gòu)成分頻電路

2020-11-18 10:41:01 9065

9065

偶數(shù)倍分頻:偶數(shù)倍分頻應(yīng)該是大家都比較熟悉的分頻,通過計數(shù)器計數(shù)是完全可以實現(xiàn)的。如進(jìn)行N倍偶數(shù)分頻,那么可以通過由待分頻的時鐘觸發(fā)計數(shù)器計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,輸出時鐘進(jìn)行翻轉(zhuǎn),并給

2013-05-01 08:44:05

奇N分頻代碼分享

2016-06-30 22:25:38

使用計數(shù)器計數(shù)不成功,有個老師指導(dǎo)說“每次是能計數(shù)器, 計數(shù)器值會清零 "就說了這幾句,奈何我太菜了 無法理解怎么弄。有大神指導(dǎo)下如何實現(xiàn)計數(shù)操作

2020-05-31 22:35:28

計數(shù)器是什么?如何使用計數(shù)器?計數(shù)器有哪些應(yīng)用呢?

2022-02-28 11:08:08

; 2、掌握中規(guī)模集成計數(shù)器的使用及功能測試方法 3、運用集成計數(shù)計構(gòu)成1/N分頻器二、 實驗原理計數(shù)器是一個用以實現(xiàn)計數(shù)

2009-10-11 10:00:11

DAQ通道屬性,只有計數(shù)器輸出,沒有計數(shù)器輸出,不知道原因出在哪里

2022-08-13 22:10:32

,分享給大家吧。——高手應(yīng)該是這樣做時鐘信號的。禁止用計數(shù)器分頻后的信號做其它模塊的時鐘,而要用改成時鐘使能的方式。否則這種時鐘滿天飛的方式對設(shè)計的可靠性極為不利,也大大增加了靜態(tài)時序分析的復(fù)雜性。時鐘

2018-08-08 11:13:26

#(25_000_000, 25) clk_div_inst(// 分頻實例, 25M 分頻,25的計數(shù)器位寬.clk_in (clk_in) , .out_pulse (led_clk

2019-03-13 04:25:51

模塊用來對外來的計數(shù)時鐘進(jìn)行分頻,這里有個分頻計數(shù)器,通過它來實現(xiàn)對時鐘的分頻功能。與之對應(yīng)的有個分頻器寄存器TIMx_PSC,用來配置和存放分頻比、分頻系數(shù)。計數(shù)模塊用來對來自分頻器輸出的計數(shù)脈沖

2020-05-27 08:00:00

原語只用用全局時鐘處理,不能作為接口使用。也不知道有什么辦法可以解決??(2)在用計數(shù)器分頻后的信號做為下級的時鐘信號時間好像也會有警告 生成了 門控時鐘,這個問題好像在與計數(shù)器分頻后的信號不能在做分支同時給于下面幾級做時鐘信號,這樣可能會在級點上產(chǎn)生邏輯門電路吧。

2015-06-16 19:34:01

觀察輸出波形并加以記錄。電路有用到:74ls90 pdf .三分頻電路d觸發(fā)器構(gòu)成2分頻電路用多級2進(jìn)計數(shù)器的分頻電路脈沖分頻電路雙穩(wěn)態(tài)分頻電路圖任意分頻電路圖1/60分頻電路用VHDL語言實現(xiàn)3分頻電路SN7474N構(gòu)成簡單的分頻電路[此貼子已經(jīng)被作者于2009-6-22 8:04:20編輯過]

2009-06-22 08:02:10

參考計數(shù)器第一次溢出。當(dāng)這種情況發(fā)生時,輸入信號的下一個下降沿停止兩個計數(shù)器。然后,可以使用參考值和輸入計數(shù)器的計數(shù)值來計算輸入頻率。為了開始測量CycLy,使用一個控制寄存器,它重置DFFS并重新加載

2018-11-02 14:47:59

最近在看《現(xiàn)代操作系統(tǒng)》,他提到了時鐘維持實際時間,在每個時鐘滴答將計數(shù)器加1即可實現(xiàn)。但要注意位溢出(32位計數(shù)器),可以通過以下方法解決:使用64位計數(shù)器:缺點是這種方法使得計數(shù)器加一操作的代價很高,1s內(nèi)維護(hù)很多次計數(shù)器。我不太懂紅色字體的意思

2018-05-04 11:36:41

上升沿觸發(fā)計數(shù)器進(jìn)行模三計數(shù),當(dāng)計數(shù)器計數(shù)到鄰近值進(jìn)行兩次翻轉(zhuǎn),比如可以在計數(shù)器計數(shù)到1時,輸出時鐘進(jìn)行翻轉(zhuǎn),計數(shù)到2時再次進(jìn)行翻轉(zhuǎn)。即是在計數(shù)值在鄰近的1和2進(jìn)行了兩次翻轉(zhuǎn)。這樣實現(xiàn)的三分頻占空比為1

2019-06-14 06:30:00

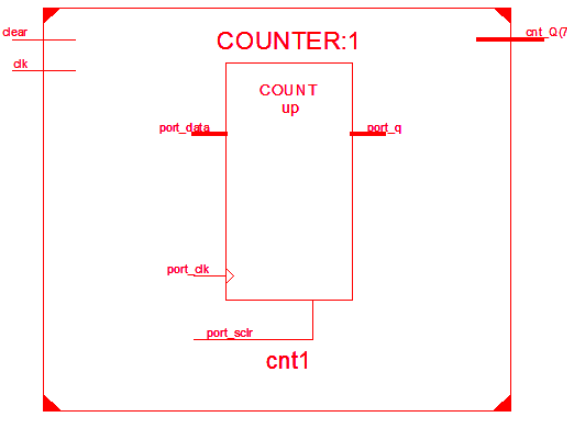

CLK,經(jīng)過分頻器后輸出標(biāo)準(zhǔn)秒脈沖CLK1,作為計數(shù)器的計數(shù)時鐘。計數(shù)器按照“00-01-02…22-23-00-01”的規(guī)律計數(shù),每增加1秒,計數(shù)器加1,信號Result[7:4]代表計數(shù)器輸出結(jié)果

2022-07-05 15:14:27

的時鐘觸發(fā)計數(shù)器進(jìn)行計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。以此循環(huán),就可以實現(xiàn)偶數(shù)倍分頻。以10分頻為例,相應(yīng)的verilog

2014-06-19 16:15:28

–是一個定時器,供能–計數(shù)。每隔一段時間就喂狗–計數(shù)清零,重新計時,程序出錯不能喂狗,得復(fù)位。獨立看門狗獨立看門狗是基于一個12位的遞減計數(shù)器和一個8位的預(yù)分頻器。他有一個內(nèi)部獨立的40KHz的RC

2021-07-30 07:24:12

我想知道我們?nèi)绾问褂么a而不是 UI 更改 STM32 中定時器的預(yù)分頻器和計數(shù)器周期的值。請幫忙。

2023-02-02 08:17:12

上升沿觸發(fā)計數(shù)器進(jìn)行模三計數(shù),當(dāng)計數(shù)器計數(shù)到鄰近值進(jìn)行兩次翻轉(zhuǎn),比如可以在計數(shù)器計數(shù)到1時,輸出時鐘進(jìn)行翻轉(zhuǎn),計數(shù)到2時再次進(jìn)行翻轉(zhuǎn)。即是在計數(shù)值在鄰近的1和2進(jìn)行了兩次翻轉(zhuǎn)。這樣實現(xiàn)的三分頻占空比為1

2019-07-09 09:11:47

定時 / 計數(shù)器的功能計數(shù):記錄脈沖的個數(shù),從而可以測量位移、速度、流量等物理量。計時:通過已知頻率的脈沖進(jìn)行計數(shù),可以實現(xiàn)精確計時。產(chǎn)生PWM波:產(chǎn)生不同占空比的PWM波,實現(xiàn)數(shù) / 模轉(zhuǎn)換,從而

2021-10-27 07:36:03

的干預(yù)情況下根據(jù)觸發(fā)條件捕捉定時器計數(shù)值或自動產(chǎn)生輸出波形。定時/計數(shù)器部分:輸入的時鐘源具有4種選擇,所選定的時中源又可以1、2、4或8分頻作為計數(shù)頻率,Timer_A可從通過選擇4種工作模式靈活的完成定時/計數(shù)功能捕獲/比較器:用于捕獲事件發(fā)生的時間或產(chǎn)生時間間隔,獲比較功能的引入主要是為

2022-02-15 06:30:58

描述帶預(yù)分頻器的 Arduino 射頻頻率計數(shù)器SAB6456 預(yù)分頻器用于除以 64/256,上限為 1 GHz。固件可在:https ://github.com/imsaiguy/Frequency-Counter-Board

2022-07-04 07:02:14

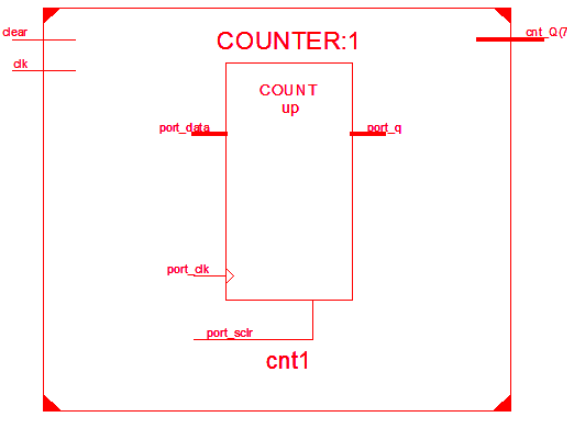

時序邏輯電路設(shè)計之計數(shù)器實驗?zāi)康模阂?b class="flag-6" style="color: red">計數(shù)器為例學(xué)會簡單的時序邏輯電路設(shè)計實驗平臺:芯航線FPGA核心板實驗原理: 時序邏輯電路是指電路任何時刻的穩(wěn)態(tài)輸出不僅取決于當(dāng)前的輸入,還與前一時刻輸入形成

2019-01-24 06:35:16

計數(shù)器(Counter)由基本的計數(shù)單元和控制門所組成,是在數(shù)字系統(tǒng)中對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制功能,且兼有分頻功能的儀器。計數(shù)器按進(jìn)位制不同,分為二進(jìn)制計數(shù)器和十進(jìn)制計數(shù)器;按

2021-12-08 08:32:28

)分頻器、預(yù)分頻器與計數(shù)器兩大類,覆蓋的頻率范圍都包含我需要的2GHz,我想知道,(1)和(2)這兩類分頻器有什么不同嗎?是否是輸入信號格式要求不同?第(1)的手冊中沒有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

) 輸出比較單元A(OCR1A) 的一個特質(zhì)是定義T/C 的TOP 值( 即計數(shù)器的分辨率)。 TOP 值還用來定義通過波形發(fā)生器產(chǎn)生的波形的周期。 由于在任意模式下寫TCNT1 都將在下一個定時器

2018-06-26 01:35:21

誰能說說計數(shù)器和分頻器有什么異同呢?

2013-06-20 16:55:20

最近在學(xué)習(xí)DAQ方面內(nèi)容,嘗試寫了一個通過計數(shù)器I/O產(chǎn)生PWM波形的程序。上次做的好像有點問題,這次做了點修改,并附上程序,望大神幫忙看下。

2017-08-19 14:10:08

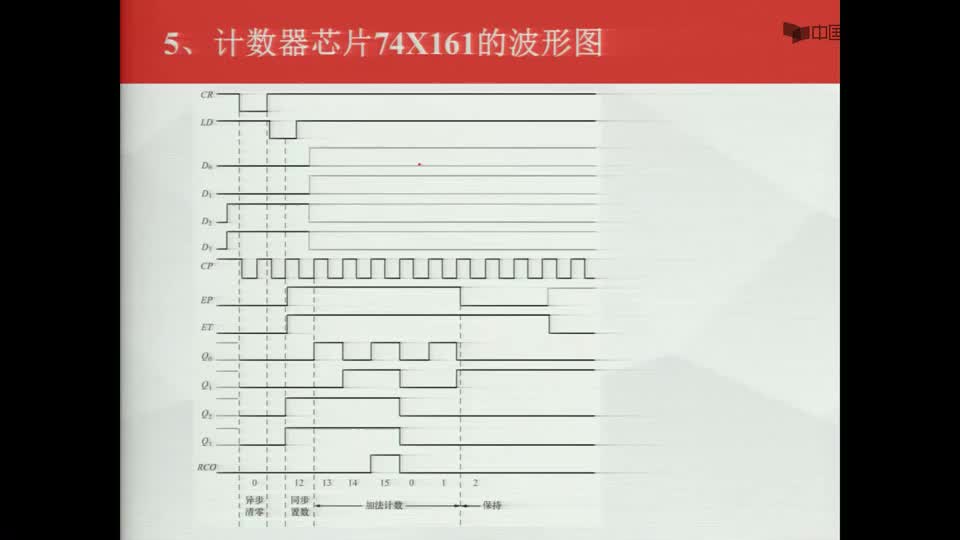

④ 構(gòu)成脈沖分頻器集成十進(jìn)制計數(shù)器【74LS290】集成十進(jìn)制計數(shù)器【74LS390】1. 集成四位二進(jìn)制計數(shù)器【74LVC161】(1) 邏輯符號CR:CR:CR: 異步置0端。優(yōu)先級最高。PE:PE:PE:并行置數(shù)端。次高優(yōu)先級。TC:TC:TC:進(jìn)位信號。CEP,CET:CEP

2021-07-29 07:20:09

面試官問道針對一個大數(shù)分頻器(比如1千分頻1萬分頻)的計數(shù)器,有什么好方法可以節(jié)省一點資源? 當(dāng)時想了很久,就說按實際分頻用到多少位就分配幾位,避免一些無用寄存器的使用。然后他搖了搖頭,我向他請教

2016-08-16 16:39:47

32位的計數(shù)器。內(nèi)部計數(shù)器對觸點信號的計數(shù),是在觸點每通斷一次時,其當(dāng)前值就+1或-1(32位雙向計數(shù)器)如下圖16-1所示,觸點X0每通斷一次,內(nèi)部計數(shù)器C0的當(dāng)前值就+1,如圖中的“4”。所以

2022-02-16 07:47:32

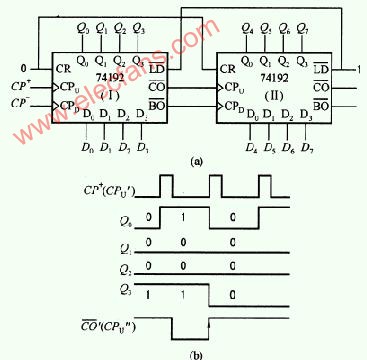

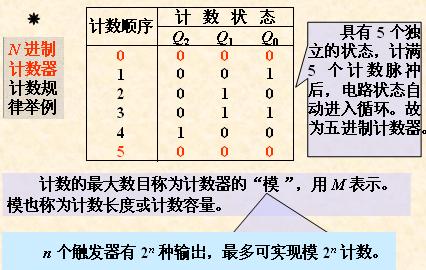

計數(shù)器的級連使用

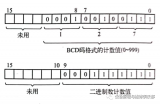

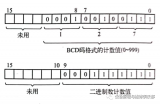

一個十進(jìn)制計數(shù)器只能顯示0~9十個數(shù),為了擴(kuò)大計數(shù)器范圍,常用多個十進(jìn)制計數(shù)器級連使用。

2007-11-22 12:53:25 3379

3379

60進(jìn)制計數(shù)器,由于24進(jìn)制、60進(jìn)制計數(shù)器均由集成計數(shù)器級聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 15785

15785

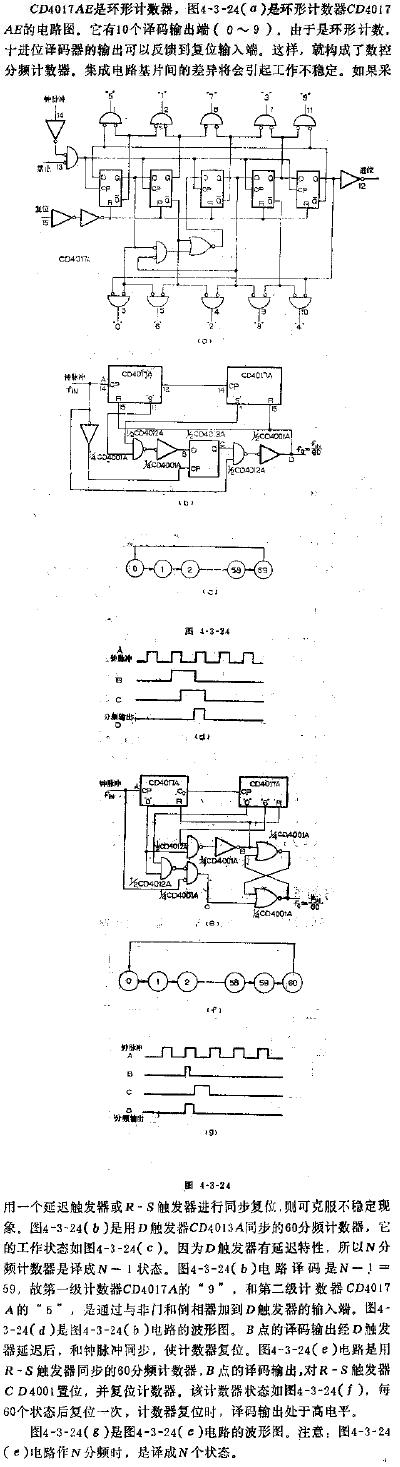

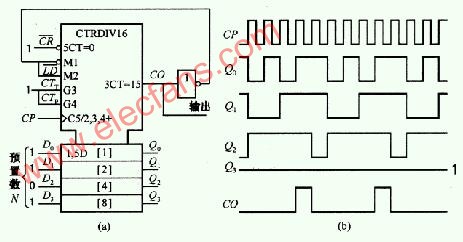

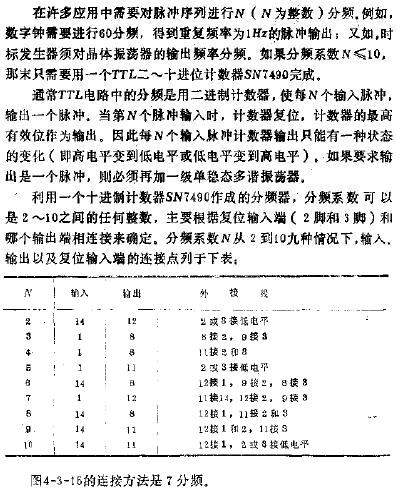

CMOS可編程N分頻計數(shù)器電路圖

2009-03-29 09:55:36 808

808

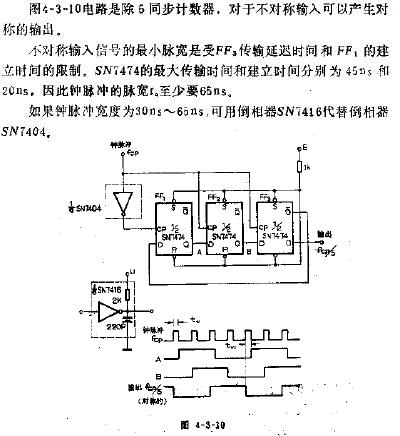

有對稱輸出的計數(shù)器

2009-04-10 10:28:41 590

590

TTL十進(jìn)位計數(shù)器構(gòu)成的分頻器

2009-04-11 10:14:57 1163

1163

輸出波形對稱的奇次分頻計數(shù)器

2009-04-11 10:24:22 654

654

用CMOS集成電路構(gòu)成的數(shù)控分頻計數(shù)器

2009-04-11 10:27:52 697

697

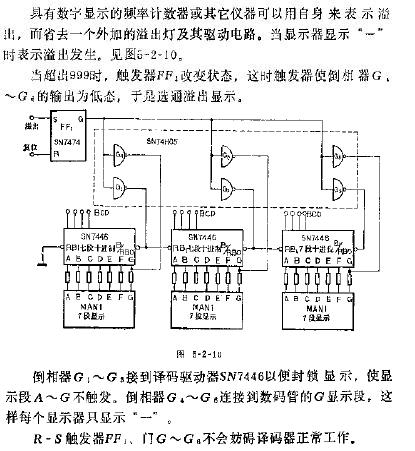

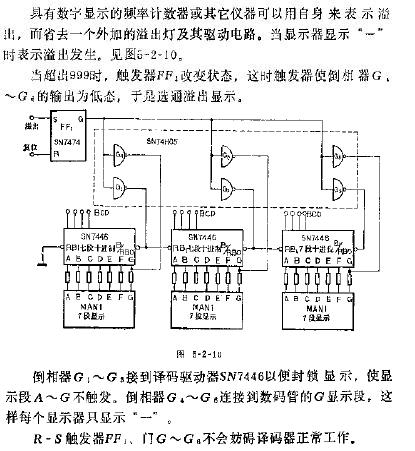

利用計數(shù)器的輸出顯示溢出狀態(tài)

2009-04-11 10:42:23 1320

1320

用多級2進(jìn)計數(shù)器的分頻電路

2009-06-12 14:30:26 1193

1193

圖3是可逆、可預(yù)置計數(shù)器CD4029構(gòu)成的任意N分頻減法計數(shù)電路,U/D接“L”電平進(jìn)行減法計數(shù),B/D接“L”電平按BCD輸出碼進(jìn)行計數(shù),低位的Co進(jìn)位到高位的CT輸

2009-06-22 07:44:38 4899

4899

計數(shù)器

計數(shù)器的作用與分類

計數(shù)器(Counter)用于計算輸入脈沖個數(shù),還常用于分頻、定時等。

2009-09-30 18:30:15 1414

1414

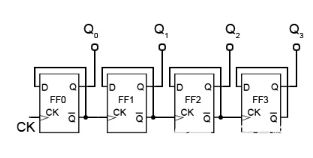

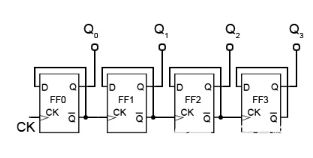

同步二進(jìn)制計數(shù)器

1. 同步與異步二進(jìn)制加法計數(shù)器比較態(tài)序表和工作波形一樣電路結(jié)構(gòu)不同: 異步二進(jìn)制加法

2009-09-30 18:37:29 11186

11186

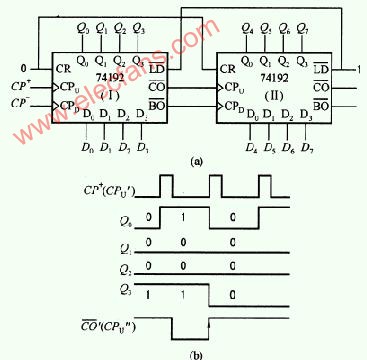

計數(shù)器級聯(lián)及波形圖

2010-01-12 13:56:56 4299

4299

可編程分頻器電路

可編程分頻器:計數(shù)器可以對計數(shù)脈沖分頻,改變計數(shù)器的模便可以改變分頻比。根據(jù)這個原理,可以用集成計數(shù)

2010-01-12 13:58:07 3187

3187

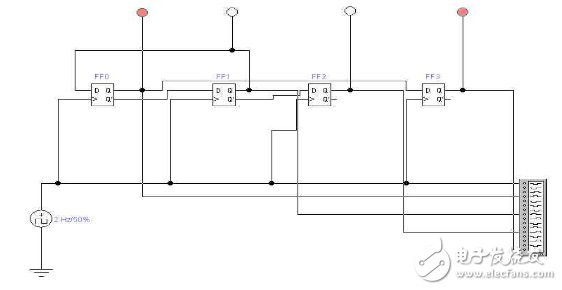

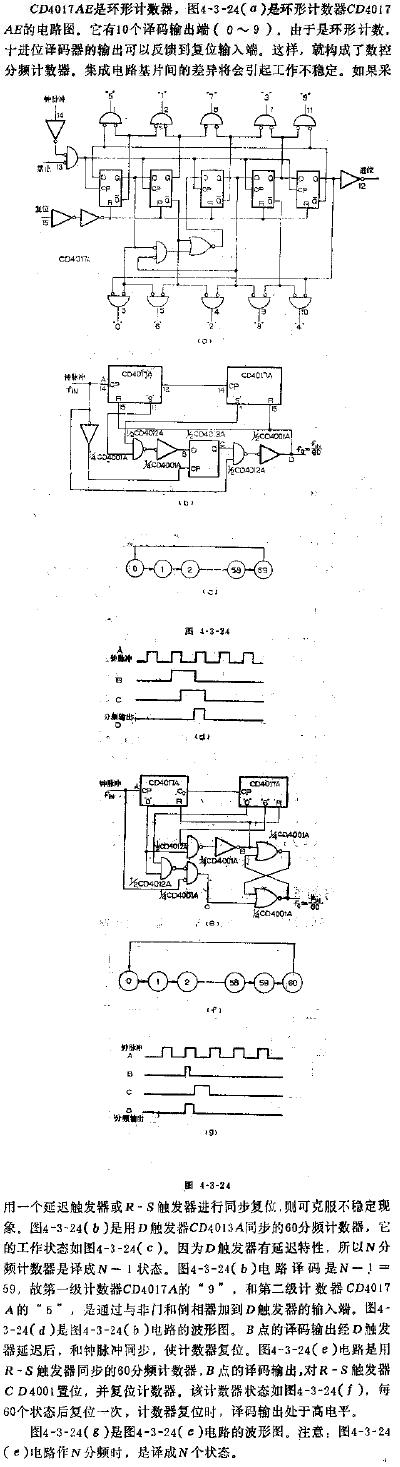

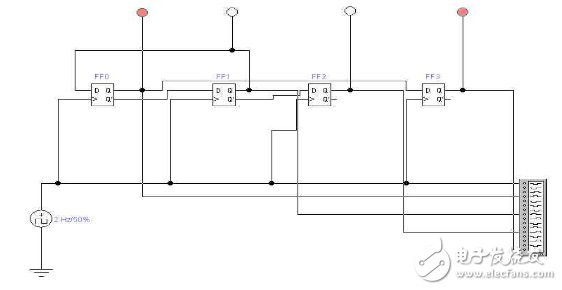

環(huán)形計數(shù)器和扭環(huán)形計數(shù)器

移位寄存器也可以構(gòu)成計數(shù)器,稱為移位型計數(shù)器。它有兩種結(jié)構(gòu):環(huán)形計數(shù)器和扭環(huán)形計數(shù)器。

2010-01-12 14:07:46 9173

9173 計數(shù)器,計數(shù)器的工作原理是什么?

在數(shù)字系統(tǒng)中使用最多的時序電路是計數(shù)器。計數(shù)器不僅能用于對時鐘脈沖進(jìn)行計數(shù)還可以用于分頻、定時,產(chǎn)生

2010-03-08 13:50:14 59934

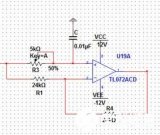

59934 正負(fù)不對稱波形的雙極性峰值輸出電路

電路的功能

這是一種輸入為

2010-05-05 14:52:06 2185

2185

一、定時/計數(shù)器PWM設(shè)計要點 根據(jù) PWM 是利用微處理器的數(shù)字輸出來對模擬電路進(jìn)行控制的特點,在使用ATmega128的定時/計數(shù)器設(shè)計輸出PWM時應(yīng)注意以下幾點: 1.首先應(yīng)根據(jù)實際的情況,

2011-09-06 11:36:20 1929

1929 計數(shù)器原理圖介紹。計數(shù)器原理圖介紹。計數(shù)器原理圖介紹

2015-12-25 09:37:05 14

14 HL配套C實驗例程分頻器1(計數(shù)器實現(xiàn)),配合開發(fā)板學(xué)習(xí)效果更好。

2016-04-11 17:14:06 7

7 計數(shù)器是用來累計和寄存輸入脈沖個數(shù)得時序邏輯部件,是數(shù)字系統(tǒng)中用途最廣泛的基本部件。計數(shù)器不僅能用于時鐘脈沖的計數(shù),還可以用于分頻,定時,產(chǎn)生節(jié)拍脈沖及進(jìn)位數(shù)字運算等,是數(shù)字系統(tǒng)、計算機系統(tǒng)必不可缺少的部件。

2016-05-05 17:40:59 0

0 集成計數(shù)器實現(xiàn)N進(jìn)制計數(shù)集成計數(shù)器實現(xiàn)N進(jìn)制計數(shù)集成計數(shù)器實現(xiàn)N進(jìn)制計數(shù)

2016-06-08 14:28:43 0

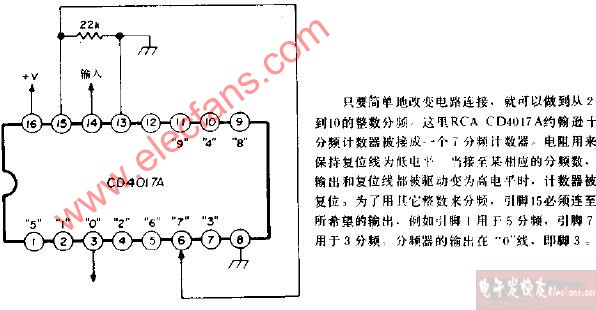

0 約翰遜MC14017B是五級十進(jìn)制計數(shù)器內(nèi)置代碼轉(zhuǎn)換器。 高速運行和約翰遜spike-free輸出是通過使用十進(jìn)制計數(shù)器的設(shè)計。 十個解碼輸出通常是低,只在適當(dāng)?shù)氖M(jìn)制時間走高。 輸出的正向變化的時鐘脈沖。 這部分可用于分頻應(yīng)用程序以及十進(jìn)制計數(shù)器或十進(jìn)制譯碼顯示應(yīng)用程序。

2017-04-06 09:03:48 28

28 HL開發(fā)板配套C實驗例程100例之分頻器1(計數(shù)器實現(xiàn)),很好的單片機C語言資料。

2017-09-01 09:28:27 4

4 計數(shù)是一種最簡單基本的運算,計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成

2017-09-25 10:13:37 8

8 計數(shù)是一種最簡單基本的運算,計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成

2017-10-23 17:48:48 15

15 環(huán)形計數(shù)器是由移位寄存器加上一定的反饋電路構(gòu)成的,用移位寄存器構(gòu)成環(huán)形計數(shù)器的一般框圖,它是由一個移位寄存器和一個組合反饋邏輯電路閉環(huán)構(gòu)成,反饋電路的輸出接向移位寄存器的串行輸入端,反饋電路的輸入端根據(jù)移位寄存器計數(shù)器類型的不同,可接向移位寄存器的串行輸出端或某些觸發(fā)器的輸出端。

2018-01-16 14:54:44 42895

42895

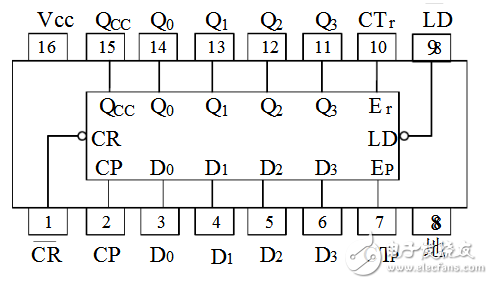

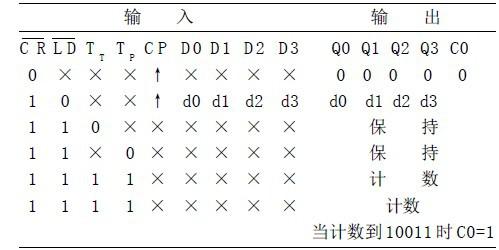

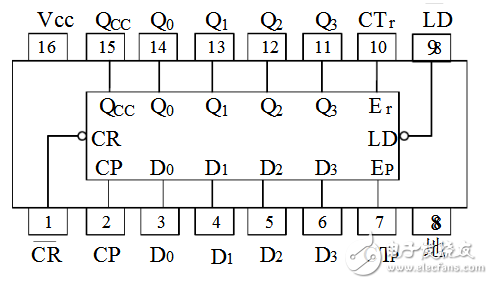

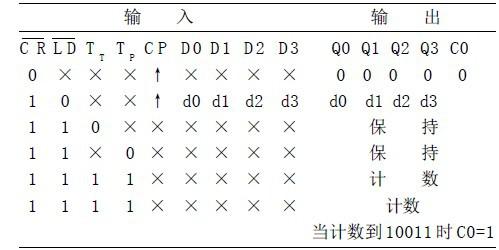

本文主要介紹了計數(shù)器74ls161工作原理(分頻電路、真值表、邏輯功能)。74LS161為二進(jìn)制同步計數(shù)器,具有同步預(yù)置數(shù)、異步清零以及保持等功能。CP是時鐘脈沖信號端,CLK是異步清零端,LD

2018-01-17 19:14:24 317507

317507

計數(shù)是一種最簡單基本的運算,計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成

2018-02-24 15:31:08 45454

45454 本文主要介紹了cd40110計數(shù)器電路圖大全(七款cd40110計數(shù)器電路設(shè)計原理圖詳解)。利用交流電源50Hz的輸出頻率通過分頻,可以取得各種不同頻率的時基脈沖。該電路選用lmin的時間長度作為

2018-03-04 11:09:50 34417

34417

功能,并且具有進(jìn)位信號輸出,可串接計數(shù)使用。重點分析了構(gòu)成N進(jìn)制計數(shù)器、以74LS163為基礎(chǔ)設(shè)計一個6分頻電路等。

2018-05-08 14:27:23 59407

59407

本文主要介紹了74ls161分頻電路圖大全(脈沖分頻電路\同步加法計數(shù)器)。計數(shù)器又稱為分頻器。N進(jìn)制計數(shù)器的進(jìn)位輸出脈沖就是計數(shù)器輸入脈沖的N分頻。N進(jìn)制計數(shù)器可直接作為N分頻器。用同步加法計數(shù)器

2018-05-08 14:41:38 102553

102553

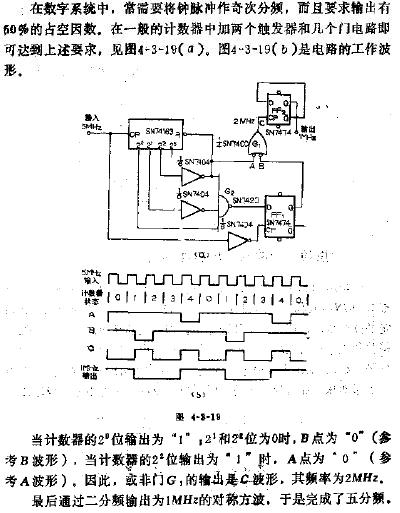

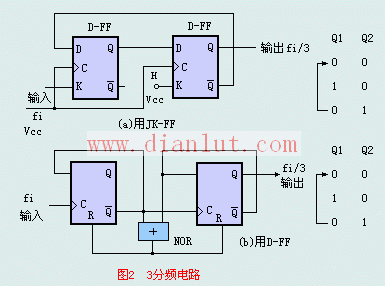

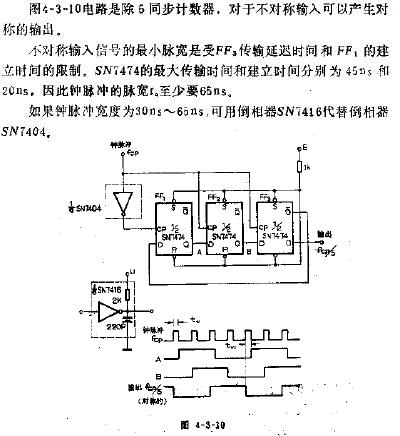

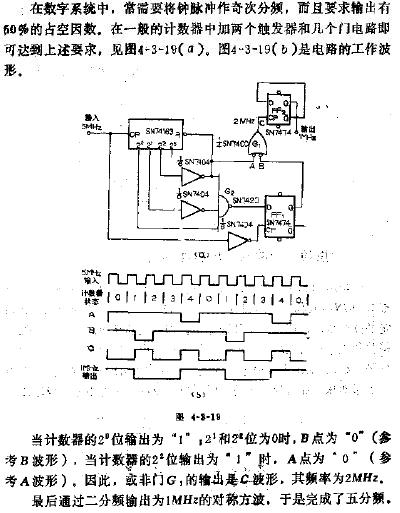

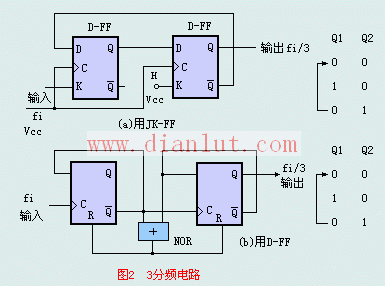

三分頻電路,在電路圖中,在一般的利用常規(guī)計數(shù)器對數(shù)字脈沖進(jìn)行奇數(shù)分頻時,即使輸入是對稱信號, 輸出也得不到占空比為50%的分頻輸出,其原因是內(nèi)部觸發(fā)器采用的是統(tǒng)一的上升沿(或下降沿)進(jìn)行觸發(fā)。

2018-08-13 11:08:34 110927

110927

計數(shù)器是數(shù)字邏輯系統(tǒng)中的基本部件, 它是數(shù)字系統(tǒng)中用得最多的時序邏輯電路,其主要功能就是用計數(shù)器的不同狀態(tài)來記憶輸入脈沖的個數(shù)。除此以外還具有定時、分頻、運算等邏輯功能。 計數(shù)器不僅能用于對時鐘脈沖的計數(shù), 還可使用于定時、分頻、產(chǎn)生節(jié)拍脈沖以及進(jìn)行數(shù)字運算等。只要是稍微復(fù)雜一些的

2019-05-30 08:24:00 14106

14106

關(guān)鍵詞:74LS109 , 74LS113 , 分頻電路 如圖所示為對稱輸出的三分頻電路。在一般的利用常規(guī)計數(shù)器對數(shù)字脈沖進(jìn)行奇數(shù)分頻時.即使輸入是對稱信號,輸出也得不到占空比為50%的分頻輸出

2018-09-28 09:47:01 1726

1726 關(guān)鍵詞:SN74193 , 分頻器 如圖所示為具有奇次和偶次分頻的分頻電路。 該電路可進(jìn)行2~32(包括奇次和偶次)分頻。同步計數(shù)器SN74193的計數(shù)輸入是由多路調(diào)制器SN74153的輸出1Y供給

2018-10-03 18:34:01 589

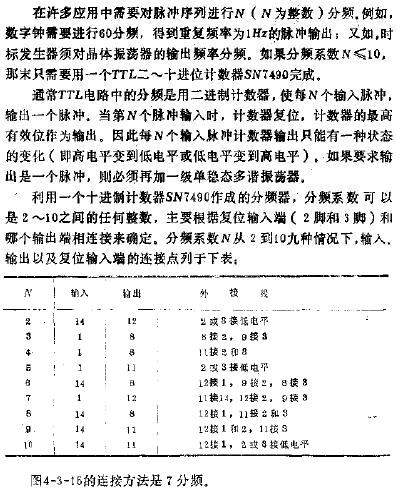

589 頻率為1Hz的脈沖輸出;又如,時標(biāo)發(fā)生器需對晶體振蕩器的輸出頻率進(jìn)行分頻。如果分頻系數(shù)N≤10,則只需用一塊TTL二-十進(jìn)制計數(shù)器SN7490即可實現(xiàn)。通常的TTL電路中的分頻是用二進(jìn)制計數(shù)器,使每N個輸入脈沖輸出一個脈沖。當(dāng)?shù)贜個脈沖輸入時,計數(shù)器復(fù)位,計數(shù)器的最高有

2018-10-03 18:46:02 2984

2984 偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進(jìn)行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進(jìn)行計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2019-02-01 01:49:00 1029

1029

計數(shù)是一種最簡單基本的運算,計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成

2019-01-24 14:35:40 63344

63344 計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成,計數(shù)單元則由一系列具有存儲信息功能的各類觸發(fā)器構(gòu)成,這些觸發(fā)器有RS觸發(fā)器、T觸發(fā)器、D觸發(fā)器及JK觸發(fā)器等。

2019-12-23 07:07:00 1354

1354

計數(shù)器的工作是通過每個時鐘脈沖將計數(shù)器的內(nèi)容提前一個計數(shù)來計數(shù)。當(dāng)被時鐘輸入激活時推進(jìn)其數(shù)字或狀態(tài)序列的計數(shù)器被稱為以“遞增計數(shù)”模式操作。同樣,當(dāng)被時鐘輸入激活時減少其數(shù)字或狀態(tài)序列的計數(shù)器被稱為以“倒計數(shù)”模式操作。在UP和DOWN模式下工作的計數(shù)器稱為雙向計數(shù)器。

2019-06-23 07:47:00 12721

12721

使用計數(shù)器來做分頻,首先計數(shù)。例如采用16計數(shù)器。每來一次外部時鐘,記一次數(shù),當(dāng)計數(shù)到16時,計數(shù)器輸出一個方波。然后重新計數(shù)。當(dāng)再次達(dá)到16時再次輸出,這樣就形成了16分頻。

2019-10-08 10:44:10 36237

36237 所謂非對稱PWM輸出模式它是相對基于中心對稱計數(shù)時的對稱PWM輸出而言的。當(dāng)計數(shù)模式為中心對齊,某個輸出通道利用一個比較寄存器做PWM輸出時,其對應(yīng)的PWM輸出波形呈中心對稱,如下圖所示:

2020-05-14 09:21:58 8759

8759

計數(shù)器與分頻電路實驗課件下載

2021-05-25 10:22:09 7

7 什么是計數(shù)器芯片? 一般來說,計數(shù)器芯片就是用來實現(xiàn)計數(shù)這種最基礎(chǔ)運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)

2021-07-13 14:09:37 12367

12367 計數(shù)器(Counter)由基本的計數(shù)單元和控制門所組成,是在數(shù)字系統(tǒng)中對脈沖的個數(shù)進(jìn)行計數(shù),以實現(xiàn)測量、計數(shù)和控制功能,且兼有分頻功能的儀器。計數(shù)器按進(jìn)位制不同,分為二進(jìn)制計數(shù)器和十進(jìn)制計數(shù)器

2021-11-25 18:06:07 32

32 實時計數(shù)器(RTC)對計數(shù)器寄存器中的(預(yù)分頻)時鐘周期進(jìn)行計數(shù),并將計數(shù)器寄存器的內(nèi)容與周期寄存器和比較寄存器進(jìn)行比較。RTC 可以在比較匹配或溢出時產(chǎn)生中斷和事件。它將在計數(shù)器值等于比較寄存器

2022-01-26 13:45:36 4398

4398 電子發(fā)燒友網(wǎng)站提供《帶預(yù)分頻器的Arduino射頻頻率計數(shù)器.zip》資料免費下載

2022-07-06 09:26:04 0

0 電子發(fā)燒友網(wǎng)站提供《內(nèi)插倒數(shù)頻率計數(shù)器FC510預(yù)分頻器(LMX2324)開源.zip》資料免費下載

2022-08-08 11:32:02 0

0 異步計數(shù)器是那些輸出不受時鐘信號影響的計數(shù)器。由于異步計數(shù)器中的觸發(fā)器提供有不同的時鐘信號,因此在產(chǎn)生輸出時可能會有延遲。設(shè)計異步計數(shù)器所需的邏輯門數(shù)量非常少,所以它們的設(shè)計很簡單。異步計數(shù)器的另一個名稱是“波紋計數(shù)器”。

2022-10-11 17:16:44 3994

3994

偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進(jìn)行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進(jìn)行計數(shù),當(dāng)計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進(jìn)行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2022-11-21 09:41:24 751

751 S7-1200的計數(shù)器為IEC計數(shù)器,用戶程序中可以使用的計數(shù)器數(shù)量僅受CPU的存儲器容量限制。

2023-01-29 09:31:56 6124

6124 在數(shù)字電子產(chǎn)品中,計數(shù)器是由一系列觸發(fā)器組成的時序邏輯電路。顧名思義,計數(shù)器用于計算輸入在負(fù)或正邊沿轉(zhuǎn)換中出現(xiàn)的次數(shù)。根據(jù)觸發(fā)觸發(fā)器的方式,計數(shù)器可以分為兩類:同步計數(shù)器和異步計數(shù)器。了解這兩種計數(shù)器的工作原理以及它們之間的區(qū)別。

2023-03-25 17:31:07 18647

18647

加計數(shù)器(S_CU)在計數(shù)初始值預(yù)置輸入端S上有上升沿時,PV裝入預(yù)置值,輸入端CU每檢測到一次上升沿,當(dāng)前計數(shù)值CV加1(前提是CV 小于999);當(dāng)前計數(shù)值大于0時,Q輸出為高電平“1”;當(dāng)R端子的狀態(tài)為“1”時,計數(shù)器復(fù)位,當(dāng)前計數(shù)值CV為“0”,輸出也為“0”。加計數(shù)器指令和參數(shù)見圖2

2023-04-27 15:38:22 1437

1437

基于51單片機的分頻器1(計數(shù)器實現(xiàn))例程源代碼

2023-05-18 09:54:09 0

0 電子發(fā)燒友網(wǎng)站提供《在Verilog HDL中使用分頻器的8位計數(shù)器的設(shè)計.zip》資料免費下載

2023-06-15 10:14:44 0

0 計數(shù)是一種簡單的運算,計數(shù)器就是讓這種運算實現(xiàn)的電路。計數(shù)器主要是對脈沖數(shù)進(jìn)行計數(shù),從而達(dá)到測量、計數(shù)、分頻以及控制的目的。智能計數(shù)器使用的是全貼片的封裝工藝,抗干擾力強,沐渥科技研發(fā)的智能計數(shù)器

2022-08-08 17:39:27 294

294

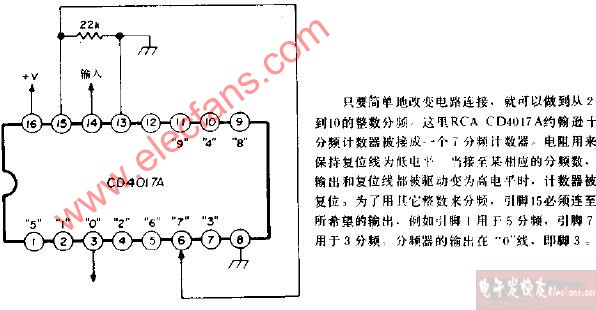

4017計數(shù)器是一種廣泛應(yīng)用于數(shù)字電路中的集成電路,它可以用來計數(shù)和控制電子設(shè)備。4017計數(shù)器有10個輸出引腳,可以依次輸出從0到9的十個數(shù)字,因此也被稱為“十進(jìn)制計數(shù)器”或“分頻計數(shù)器”。在本文

2023-12-15 09:24:28 729

729 計數(shù)器是一種被廣泛應(yīng)用于各個領(lǐng)域的實用工具,在我們的日常生活中隨處可見。無論是進(jìn)行時間統(tǒng)計,協(xié)助工作任務(wù)的完成,還是用于科學(xué)研究和編程技術(shù),在各個領(lǐng)域都起到了重要的作用。本文將詳細(xì)介紹計數(shù)器

2024-02-03 10:04:14 589

589

電子發(fā)燒友App

電子發(fā)燒友App

評論