概述:CD4060是一款14級二進制串行計數(shù)/分頻器,它是由一振蕩器和14級二進制串行計數(shù)器位組成,振蕩器的結(jié)構(gòu)可以是RC或晶振電路,CR為高電平時,計數(shù)器清零且振蕩器使用無效。所有的計數(shù)器位均為主從觸發(fā)器。

2021-04-08 07:40:14

如何用multisim軟件仿真雙時鐘加/減計數(shù)器CT74LS192和譯碼器CC4511和譯碼器SM4205構(gòu)成的30進制加法計數(shù)器和30進制減法計數(shù)器,求仿真接線圖。PCB打樣找華強 http://www.hqpcb.com/3 樣板2天出貨

2012-10-07 21:13:28

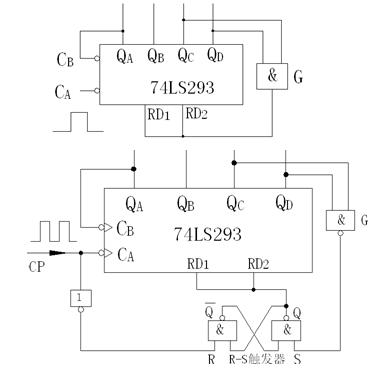

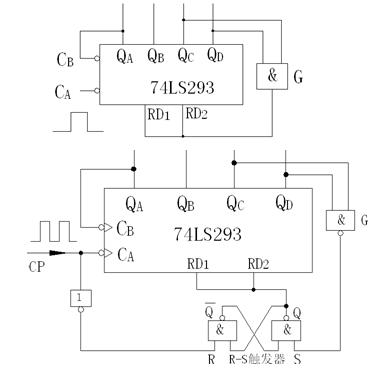

緩沖器74283 TTL 4位二進制全加器74290 TTL 二/五分頻十進制計數(shù)器74293 TTL 二/八分頻四位二進制計數(shù)器74295 TTL 四位雙向通用移位寄存器74298 TTL 四2輸入

2011-08-01 16:25:44

用protues 怎么做多級十進制分頻器

2016-06-04 07:55:03

十進制 好,那就讓我們來看看十進制 所謂十進制就是以10為基數(shù)的計數(shù)體制,其計數(shù)規(guī)律是逢十進一。 圖1.3.1展示了十進制的位號和位權(quán)之間關(guān)系的圖解。位號3210-1-2-3十進制數(shù)

2009-04-06 23:47:02

計數(shù)器。4、用74390兩個宏連接成八位十進制異步計數(shù)器。5、用74161用清零和置數(shù)法組成六進制和十二進制計數(shù)器。6、分別用D觸發(fā)器和同步計數(shù)器加譯碼電路的方法構(gòu)成7進制電路實現(xiàn)如下編碼:[0→2→5

2009-10-10 11:47:02

剛開始接觸Multisim,我用的是Multisim14,今天畫了一個電路圖 實現(xiàn)十進制計數(shù)器顯示的功能,但仿真是報錯 Transient time point calculation did not converge ,找不出原因,希望大家?guī)臀艺艺义e在哪里了哈

2016-08-14 20:18:16

計數(shù)器。如圖9-4所示為一個由CC40192十進制計數(shù)器接成的6進制計數(shù)器。(2) 利用預(yù)置功能獲M進制計數(shù)器圖9-5為用三個CC40192組成的421進制計數(shù)器。外加的由與非門構(gòu)成的鎖存器可以克服器件

2009-10-11 10:00:11

內(nèi)含有共陰、共陽十進制計數(shù)器的原理圖和芯片文檔

2013-12-03 16:03:53

隨著fpga學(xué)習(xí)深入,有以下問題求高手幫忙1,復(fù)位信號往往高扇出,那復(fù)位越少越好,有的就不需要復(fù)位,比如分頻器的計數(shù),那哪些地方都可以不復(fù)位呢?2,verilog中使用數(shù)值判斷之類的,使用十進制

2014-03-06 19:49:09

本帖最后由 lianyicq 于 2015-7-23 08:49 編輯

請教一個簡單的問題,在Proteus下用4個帶復(fù)位端的邊沿觸發(fā)JK觸發(fā)器構(gòu)成一個十進制加法計數(shù)器,清零信號在狀態(tài)為

2015-07-20 11:27:01

; S92 Q2 Q1 GNDT4290(T1290、74LS290、T210),是一個二-五-十進制計數(shù)器,能夠進行二進制、五進制計數(shù)、通過簡單聯(lián)線組成十進制計數(shù)

2008-07-05 13:41:26

請問給位大神,只用觸發(fā)器和簡單的邏輯門怎樣設(shè)計一個同步清零的二十進制的計數(shù)器

2013-10-16 22:00:52

這是一個可以對照顯示0~9這10個數(shù)字的二進制和十進制的電路。二進制數(shù)字用4個發(fā)光二極管顯示;它們排成一行,亮表示1,滅表示0。十進制數(shù)字用一個數(shù)碼管表示。數(shù)字的變化采用CD4040組成加法計數(shù)器,手動加1計數(shù)。

2021-04-27 07:21:40

具體的思路是這樣的十進制加法:開關(guān)高電平,從0計數(shù)到9,然后又跳到0十進制減法:開關(guān)低電平,從9計數(shù)到0,然后又跳到9這倆都是循環(huán)的還有就是要清零,按下j1之后,數(shù)碼管馬上顯示0,計數(shù)器重新從0開始

2013-12-25 20:47:27

求一份關(guān)于數(shù)電的四位十進制的加減法計數(shù)器!!!感謝各路大神!!!

2016-03-10 13:28:19

1、實現(xiàn)一個24進制加法計數(shù)器的設(shè)計本實驗設(shè)計實現(xiàn)一個24進制的加法計數(shù)器,它由晶體振蕩器、分頻器、計數(shù)器和數(shù)碼管顯示器組成,圖6.1是該加法計數(shù)器的示意圖。晶體振蕩器產(chǎn)生穩(wěn)定的50MHz的脈沖信號

2022-07-05 15:14:27

這種方式只消耗不多的邏輯單元就可以達到對時鐘的操作目的。2、整數(shù)倍分頻器的設(shè)計2.1 偶數(shù)倍分頻 偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻

2014-06-19 16:15:28

我想知道我們?nèi)绾问褂么a而不是 UI 更改 STM32 中定時器的預(yù)分頻器和計數(shù)器周期的值。請幫忙。

2023-02-02 08:17:12

目錄一、頂層程序二、系統(tǒng)產(chǎn)生測試信號單元三、400HZ分頻器單元四、控制信號單元五、8位十進制計數(shù)器5.1一位十進制計數(shù)器六、鎖存器單元七、LED控制頂層程序7.1 400Hz分頻器7.2 計數(shù)器

2022-01-18 07:36:48

描述帶預(yù)分頻器的 Arduino 射頻頻率計數(shù)器SAB6456 預(yù)分頻器用于除以 64/256,上限為 1 GHz。固件可在:https ://github.com/imsaiguy/Frequency-Counter-Board

2022-07-04 07:02:14

模M的十進制加/減可逆計數(shù)器設(shè)計、仿真與實驗學(xué)習(xí)目標:熟悉常用MSI集成計數(shù)器的功能和應(yīng)用,掌握利用集成計數(shù)器構(gòu)成任意進制計數(shù)器的一般設(shè)計方法;學(xué)會利用EDA軟件(Proteus)對模M的可逆計數(shù)器

2009-09-16 15:06:52

請教一個數(shù)電的問題,我想設(shè)計一個可預(yù)置數(shù) 六十進制 (從60開始倒計時)減法計數(shù)器 ,可是我做出來的只能從59開始倒計時,不知道怎么改進啊,求賜教啊。 附件為我做的Proteus 的電路仿真。

2013-05-09 00:03:04

求74ls161十進制減計數(shù)器接法,有電路圖最好,我正在用multisim軟件來仿真,謝謝了!!

2013-05-22 10:58:35

`朋友們好!我想求一個,可加減計數(shù)器0-99999 ,6位。能給出仿真電路和程序那就太好了。`

2013-06-05 16:20:03

求高手幫忙,整一個FPGA 8位 計數(shù)器 十進制 的怎么搞!

2012-11-02 00:18:20

計數(shù)器(Counter)由基本的計數(shù)單元和控制門所組成,是在數(shù)字系統(tǒng)中對脈沖的個數(shù)進行計數(shù),以實現(xiàn)測量、計數(shù)和控制功能,且兼有分頻功能的儀器。計數(shù)器按進位制不同,分為二進制計數(shù)器和十進制計數(shù)器;按

2021-12-08 08:32:28

EDA初學(xué)者,求各位同路人幫忙設(shè)計一個十進制計數(shù)器,用VHLD語言

2014-04-27 09:59:48

)分頻器、預(yù)分頻器與計數(shù)器兩大類,覆蓋的頻率范圍都包含我需要的2GHz,我想知道,(1)和(2)這兩類分頻器有什么不同嗎?是否是輸入信號格式要求不同?第(1)的手冊中沒有提到相噪,是否(1)比(2)的相噪

2019-01-11 13:39:43

誰能說說計數(shù)器和分頻器有什么異同呢?

2013-06-20 16:55:20

本人用原理圖輸入法設(shè)計二位十進制計數(shù)器,下面是一本書上的圖:用Quartus 2編譯時出現(xiàn)下面錯誤:請求各位大俠解決 啊,謝謝了。

2011-05-14 14:14:18

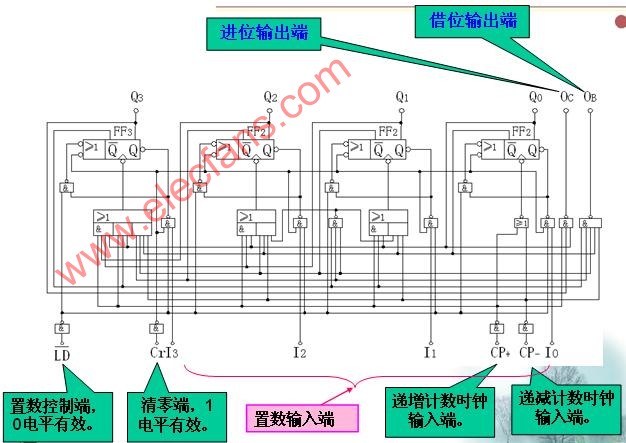

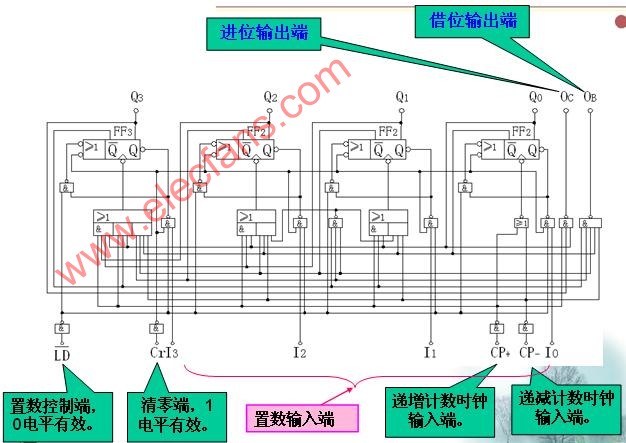

④ 構(gòu)成脈沖分頻器集成十進制計數(shù)器【74LS290】集成十進制計數(shù)器【74LS390】1. 集成四位二進制計數(shù)器【74LVC161】(1) 邏輯符號CR:CR:CR: 異步置0端。優(yōu)先級最高。PE:PE:PE:并行置數(shù)端。次高優(yōu)先級。TC:TC:TC:進位信號。CEP,CET:CEP

2021-07-29 07:20:09

面試官問道針對一個大數(shù)分頻器(比如1千分頻1萬分頻)的計數(shù)器,有什么好方法可以節(jié)省一點資源? 當時想了很久,就說按實際分頻用到多少位就分配幾位,避免一些無用寄存器的使用。然后他搖了搖頭,我向他請教

2016-08-16 16:39:47

TTL 二進制同步可逆計數(shù)器

2009-08-03 09:05:53 26

26 4026 CMOS 7段顯示十進制計數(shù) 分頻器:

2009-08-08 09:08:02 29

29 CD4017 十進制計數(shù)/分配器 *CD4020 14位二進制串行計數(shù)器/分頻器 *CD4022 八進制

2006-04-17 21:18:42 3874

3874 十進制計數(shù)器

二進制計數(shù)器具有電路結(jié)構(gòu)簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特別是當二進制數(shù)的位數(shù)較多時,閱讀非常困難,還

2007-06-20 13:46:05 4188

4188 十進制可逆計數(shù)器74LS192引腳圖管腳及功能表

2011-05-19 11:22:27 121074

121074 計數(shù)器的級連使用

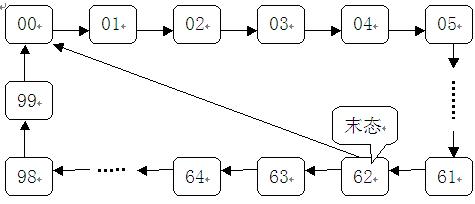

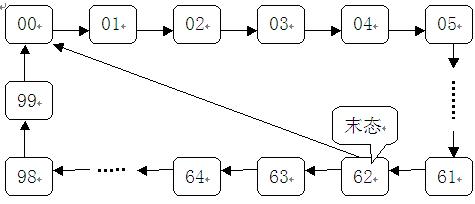

一個十進制計數(shù)器只能顯示0~9十個數(shù),為了擴大計數(shù)器范圍,常用多個十進制計數(shù)器級連使用。

2007-11-22 12:53:25 3379

3379

2位十進制可加減計數(shù)器電路-74LS190應(yīng)用電路

2007-12-07 00:12:12 9926

9926

十進制計數(shù)器工作原理

同二進制計數(shù)器相比,十進制計數(shù)器較為復(fù)雜。分析步驟一般是:

2008-01-21 13:15:22 28596

28596

60進制計數(shù)器,由于24進制、60進制計數(shù)器均由集成計數(shù)器級聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 15785

15785

用16進制計數(shù)器先級聯(lián)后預(yù)置數(shù)構(gòu)成的63

2008-07-05 13:54:55 2831

2831

先級聯(lián)后預(yù)置數(shù)構(gòu)成的63進制計數(shù)器:我們同樣也可以先用級聯(lián)法組成10i計數(shù)器、或16i計數(shù)器,再用預(yù)置

2008-07-05 13:58:00 1507

1507

兩片4位二進制數(shù)加法計數(shù)器74LS161級聯(lián)成五十進制計數(shù)器。

2009-03-28 10:10:23 34301

34301

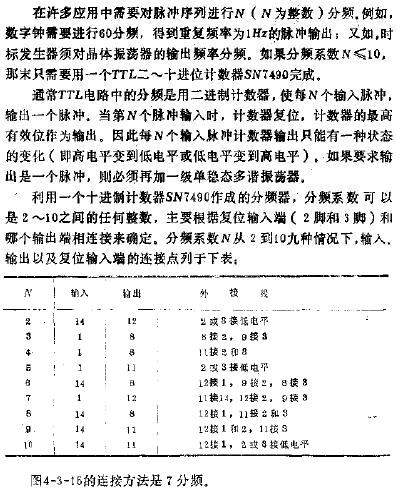

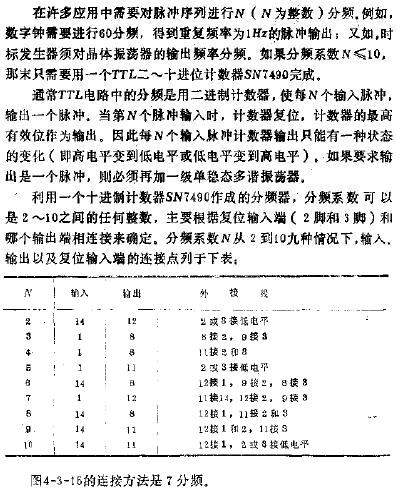

TTL十進位計數(shù)器構(gòu)成的分頻器

2009-04-11 10:14:57 1163

1163

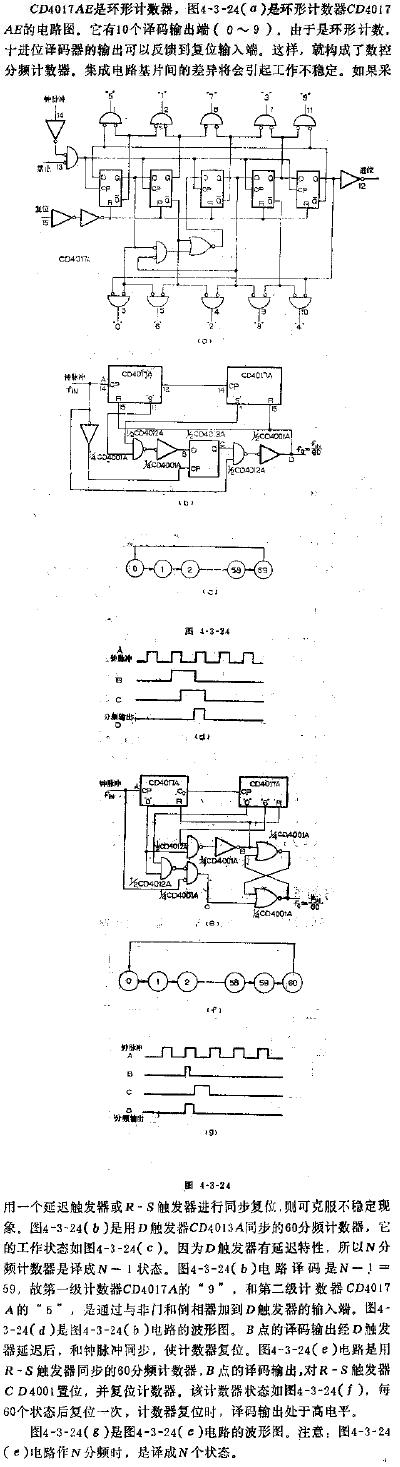

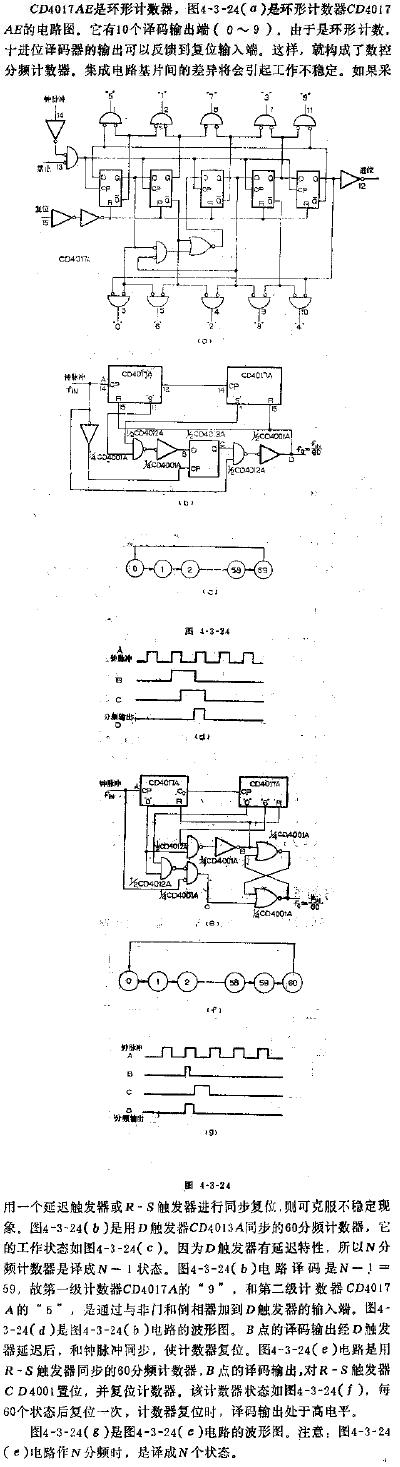

用CMOS集成電路構(gòu)成的數(shù)控分頻計數(shù)器

2009-04-11 10:27:52 697

697

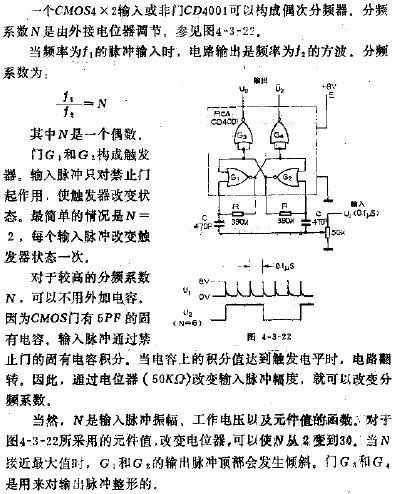

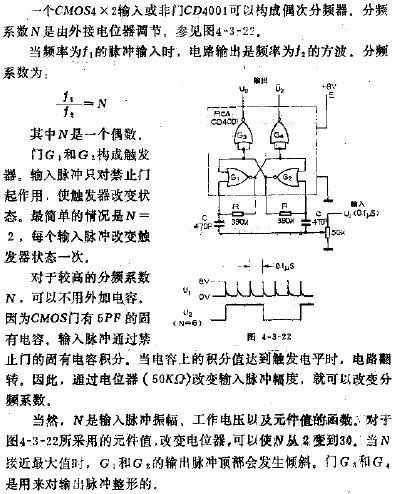

由CMOS門構(gòu)成的可調(diào)分頻器

2009-04-11 10:28:20 962

962

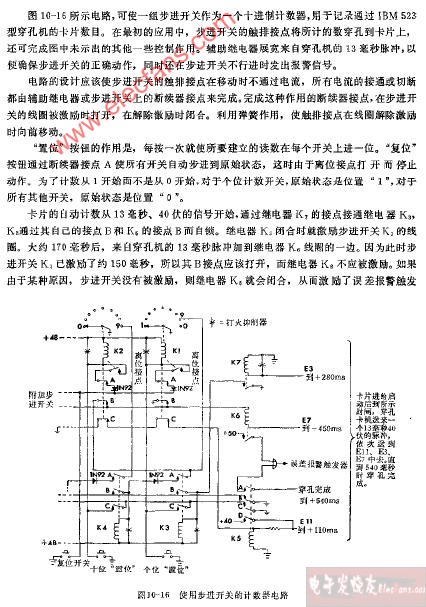

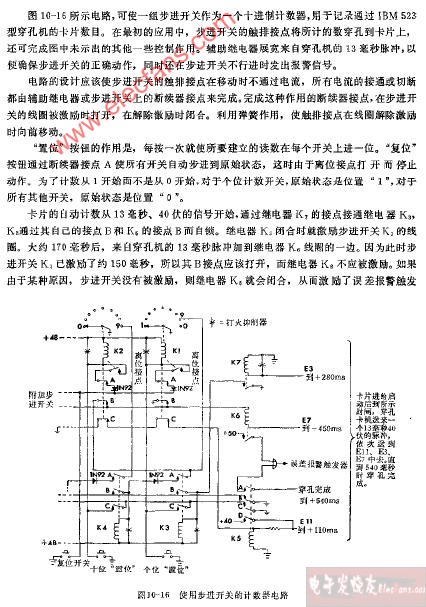

步進開關(guān)作為十進制計數(shù)器電路圖

2009-06-30 13:08:13 944

944

8421碼同步十進制遞增計數(shù)器

2009-09-24 11:09:34 6125

6125

T1192型同步十進制可逆計數(shù)器

2009-09-24 11:10:59 1352

1352

異步十進制遞增計數(shù)器

2009-09-24 11:12:05 1195

1195

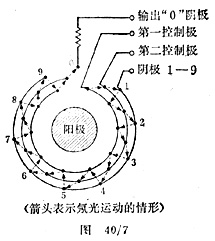

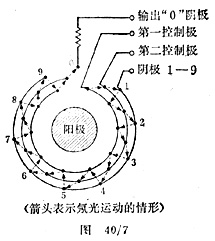

十進制計數(shù)管 十進制計數(shù)管是由中央的圓板狀陽極和圍繞著它放置的三十根線狀的電極組成。這些線狀電極三根一組,共十組,每

2009-10-13 15:05:12 1490

1490

可編程分頻器電路

可編程分頻器:計數(shù)器可以對計數(shù)脈沖分頻,改變計數(shù)器的模便可以改變分頻比。根據(jù)這個原理,可以用集成計數(shù)

2010-01-12 13:58:07 3187

3187

十進制計數(shù)器,十進制計數(shù)器原理是什么?

二進制計數(shù)器具有電路結(jié)構(gòu)簡單、運算方便等特點,但是日常生活中我們所接觸的大部分都是十進制數(shù),特

2010-03-08 13:19:54 24108

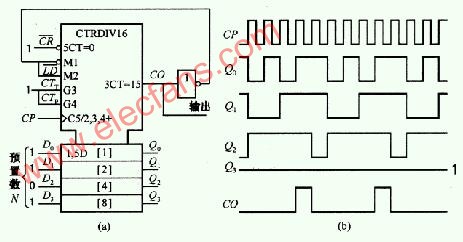

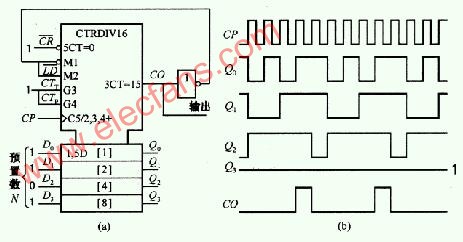

24108 圖中所示是用C180 2-10進制同步加法計數(shù)器組成的時基分頻器(多級串行計數(shù))線路.圖中晶體振蕩器采用振蕩頻率為

2010-10-19 15:03:29 1574

1574

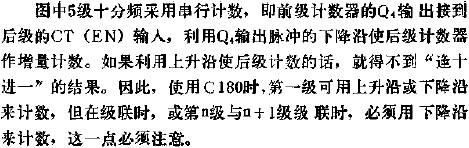

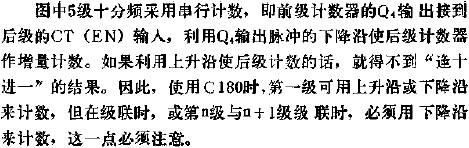

分頻器及量程選擇電路 分頻器是由多級計數(shù)器完成,目的是得到不同的標準時基信號。采用4片雙十進制中規(guī)模計數(shù)器CD4518級聯(lián)可獲得10

2010-11-06 11:57:17 1834

1834

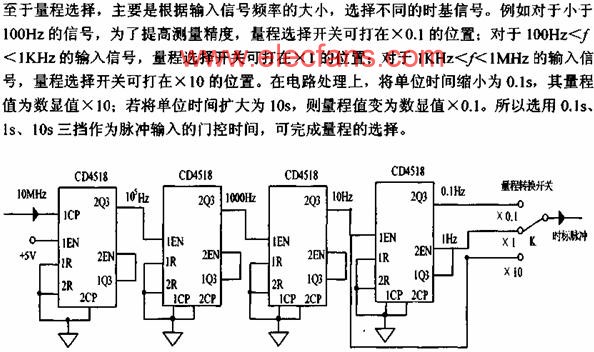

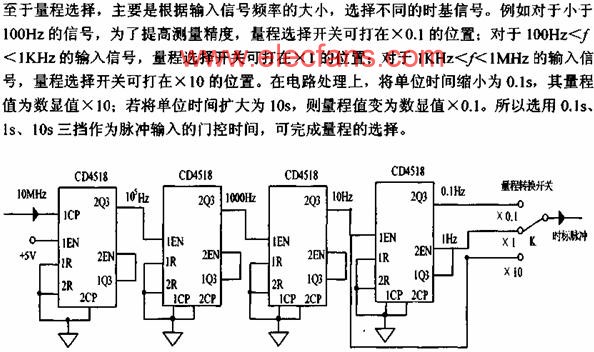

使用一片ICM7217A配4只共陰極LED數(shù)碼管,可構(gòu)成4位十進制可逆計數(shù)器,其

2010-12-10 13:55:24 7311

7311

數(shù)字電子技術(shù)--中規(guī)模集成計數(shù)器及其應(yīng)用--同步、異步二五十進制計數(shù)器-PPT

2016-03-22 14:33:06 0

0 HL配套C實驗例程分頻器1(計數(shù)器實現(xiàn)),配合開發(fā)板學(xué)習(xí)效果更好。

2016-04-11 17:14:06 7

7 CD4017 十進制計數(shù)器的應(yīng)用實驗

2022-05-11 16:58:25 0

0 約翰遜MC14017B是五級十進制計數(shù)器內(nèi)置代碼轉(zhuǎn)換器。 高速運行和約翰遜spike-free輸出是通過使用十進制計數(shù)器的設(shè)計。 十個解碼輸出通常是低,只在適當?shù)?b class="flag-6" style="color: red">十進制時間走高。 輸出的正向變化的時鐘脈沖。 這部分可用于分頻應(yīng)用程序以及十進制計數(shù)器或十進制譯碼顯示應(yīng)用程序。

2017-04-06 09:03:48 28

28 集成計數(shù)器常見的是多位二進制計數(shù)器及十進制計數(shù)器,當需要實現(xiàn)其它進制計數(shù)器時,通常利用現(xiàn)有的集成計數(shù)器進行適當?shù)倪B接而構(gòu)成。對于當設(shè)計要求沒有限定計數(shù)器的狀態(tài)編碼時電路設(shè)計的靈活性問題已有文獻進行

2017-11-09 16:36:16 81

81 針對任意進制(N進制)計數(shù)器的設(shè)計目的,采用反饋復(fù)零法對基于同步十進制計數(shù)器7415160進行設(shè)計,分別采用異步清零法實現(xiàn)了6進制計數(shù)器和同步置數(shù)法實現(xiàn)7進制計數(shù)器的設(shè)計,通過應(yīng)用EWB軟件對所設(shè)

2017-12-21 17:08:37 62805

62805

60進制計數(shù)器,由于24進制、60進制計數(shù)器均由集成計數(shù)器級聯(lián)構(gòu)成,且都包含有基本的十進制計數(shù)器,從設(shè)計簡便考慮,芯片選擇同步十進制計數(shù)器

2017-12-22 13:55:48 153475

153475

使用兩片74LS161芯片級聯(lián)的形式來構(gòu)成六十進制計數(shù)器,一片控制個位,為十進制;另一片控制十位,為六進制。

2018-01-17 13:58:47 56134

56134

本文主要介紹了74ls160十進制計數(shù)器電路的設(shè)計與實現(xiàn)。74LS160是二~十進制同步可預(yù)置計數(shù)器,1腳Cr為清零端,低電平有效.2腳CP為時鐘脈沖輸人端,上升沿觸發(fā).3~6V腳D1一D4為數(shù)據(jù)

2018-01-18 15:14:45 199667

199667

本文主要介紹了74ls160構(gòu)成24進制計數(shù)器電路設(shè)計。本設(shè)計采用異步清零。由兩片十進制同步加法計數(shù)器74LS160和一片與非門74LS00以及相應(yīng)的電阻開關(guān)組成。由外加送來的計數(shù)脈沖送入兩個計數(shù)器

2018-01-18 15:43:05 153589

153589

74LS290為異步二-五-十進制加法計數(shù)器。本文為大家介紹74ls290構(gòu)成31進制計數(shù)器電路。

2018-01-25 14:36:39 17741

17741

74ls290是一個二,五,十進制計數(shù)器,本文為大家介紹由74ls290構(gòu)成的各種進制計數(shù)器的電路。

2018-01-26 09:26:11 112216

112216

本文主要介紹了74ls163實現(xiàn)十進制計數(shù)器電路。改變74LS163二進制計數(shù)器為十進制計數(shù)器,即用一FDS4435BZ個與非門,其兩個輸人取自QA和QD,輸出接清零端α‘R。當?shù)?個脈沖結(jié)束時

2018-05-08 11:31:20 48594

48594

功能,并且具有進位信號輸出,可串接計數(shù)使用。重點分析了構(gòu)成N進制計數(shù)器、以74LS163為基礎(chǔ)設(shè)計一個6分頻電路等。

2018-05-08 14:27:23 59407

59407

本文主要介紹了74ls161分頻電路圖大全(脈沖分頻電路\同步加法計數(shù)器)。計數(shù)器又稱為分頻器。N進制計數(shù)器的進位輸出脈沖就是計數(shù)器輸入脈沖的N分頻。N進制計數(shù)器可直接作為N分頻器。用同步加法計數(shù)器

2018-05-08 14:41:38 102553

102553

本文主要介紹了兩個74LS192級聯(lián)構(gòu)成兩位十進制計數(shù)器。以兩個74LS192級聯(lián)構(gòu)成兩位十進制計數(shù)器控制實現(xiàn)0.0~9.9V的切換為例。低位計數(shù)器輸出Qo、Qi、Q2、Q3分別提供0.1V

2018-05-09 09:52:23 56277

56277

,S8424是兩組RS T觸發(fā)器.S8480是4×2輸入與非門。二-八進制撥盤開關(guān)用來確定分頻器的分頻系數(shù),以保證觸發(fā)器復(fù)位。如果采用二-十進制撥盤開關(guān),另外再加一個觸發(fā)器和兩個二極管。則可構(gòu)成分頻系數(shù)為1~10的分頻器。

2018-10-03 18:37:02 427

427 關(guān)鍵詞:SN74150 , SN7442 , SN7490 , 數(shù)字分頻器 如圖所示為數(shù)字分頻電路。該電路由3塊集成電路構(gòu)成,分頻系數(shù)可以從1~9變化。計數(shù)器SN7490輸出的二-十進制數(shù)送至譯碼器

2018-10-08 07:58:01 1750

1750 偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進行計數(shù),當計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2019-02-01 01:49:00 1029

1029

40110 為十進制可逆計數(shù)器/鎖存器/譯碼器/驅(qū)動器,具有加減計數(shù),計數(shù)器狀態(tài)鎖存,七段顯示譯碼輸出等功能。

2019-04-30 08:00:00 6

6 十進制計數(shù)器是人們最常用的計數(shù)器,但在某些特殊的計數(shù)場合下,也需要其他進制的計數(shù)器。

2020-01-14 09:46:48 7192

7192

電子秒表一般由振蕩器、分頻器、計數(shù)器、譯碼器、顯示器等幾部分組成。其中振蕩器和分頻器組成標準秒信號發(fā)生器,由不同進制的計數(shù)器、譯碼器和顯示器組成計時系統(tǒng)。信號送入計數(shù)器,累計結(jié)果以分、秒、分秒的數(shù)字顯示出來,分、分秒由十進制計數(shù)器構(gòu)成,秒由六十進制計數(shù)器構(gòu)成。

2020-10-16 08:00:00 1

1 芯片74ls160是十進制計數(shù)器,這種同步可預(yù)置十進計數(shù)器是由四個D型觸發(fā)器和若干個門電路構(gòu)成。

2021-06-05 14:35:38 14045

14045 電子發(fā)燒友網(wǎng)站提供《帶預(yù)分頻器的Arduino射頻頻率計數(shù)器.zip》資料免費下載

2022-07-06 09:26:04 0

0 二進制編碼的十進制是一個串行數(shù)字計數(shù)器,可計數(shù)十位數(shù)字,它會為每個新的時鐘輸入重置。由于它可以通過10種獨特的輸出組合,因此也被稱為“十進制(BCD)計數(shù)器”。十進制計數(shù)器可以計數(shù)0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 15920

15920

偶數(shù)倍分頻器的實現(xiàn)非常簡單,只需要一個計數(shù)器進行計數(shù)就能實現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時鐘觸發(fā)計數(shù)器進行計數(shù),當計數(shù)器從0計數(shù)到N/2-1時,將輸出時鐘進行翻轉(zhuǎn),并給計數(shù)器一個復(fù)位信號,以使下一個時鐘開始從零計數(shù)。

2022-11-21 09:41:24 751

751 本方案是一個基于 FPGA ?的十進制計數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進制計數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實現(xiàn)。

2022-12-20 14:52:25 2

2 雙十進制紋波計數(shù)器-74HC_HCT390

2023-02-15 19:06:31 0

0 帶 10 個解碼輸出的 Johnson 十進制計數(shù)器-74HC_HCT4017

2023-02-16 20:29:32 0

0 帶 10 個解碼輸出的 Johnson 十進制計數(shù)器-74HC_HCT4017_Q100

2023-02-17 19:59:07 1

1 可預(yù)置同步BCD十進制計數(shù)器;異步復(fù)位-74HC160

2023-02-20 20:05:50 10

10 基于51單片機的分頻器1(計數(shù)器實現(xiàn))例程源代碼

2023-05-18 09:54:09 0

0 電子發(fā)燒友網(wǎng)站提供《在Verilog HDL中使用分頻器的8位計數(shù)器的設(shè)計.zip》資料免費下載

2023-06-15 10:14:44 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論