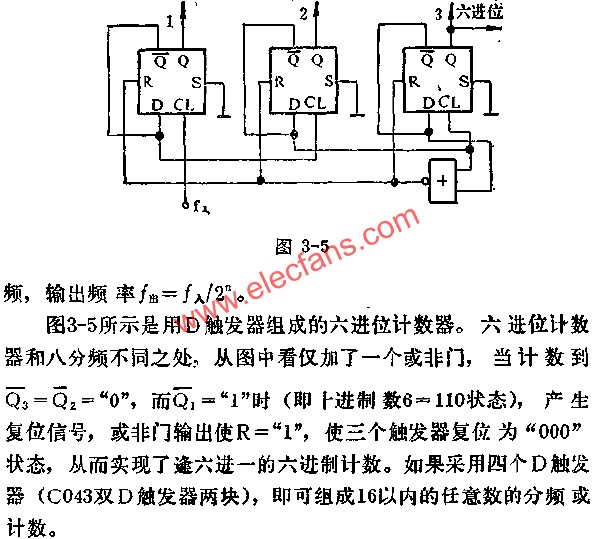

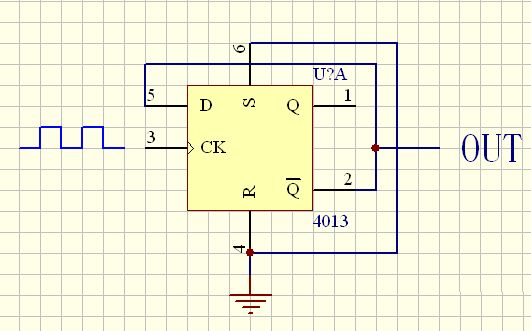

上例圖中A將D觸發器的D端和Q相連,即可組成二分頻電路,如果把三個D觸發器串行相連,如圖所示,則經過一

2010-09-20 03:40:48 12045

12045

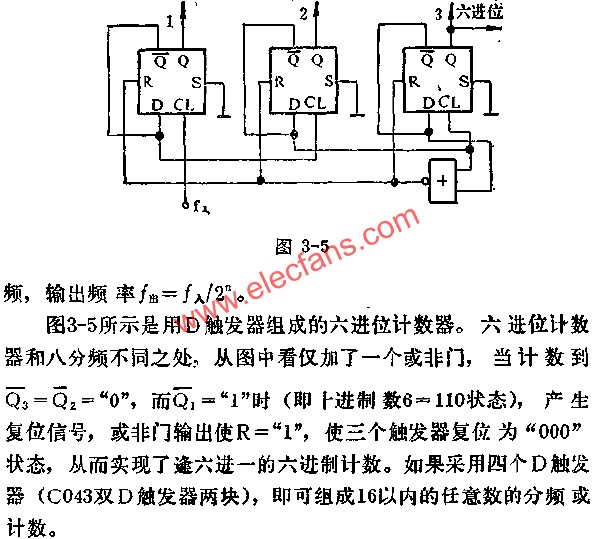

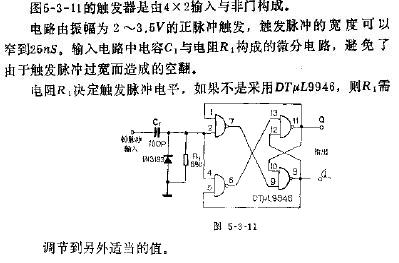

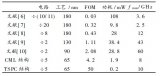

由3 個D 觸發器和少量邏輯門構成, 采用了同步工作模式, 其原理是由吞脈沖計數原理產生2 個占空比不同的五分頻信號A 和B

2011-11-25 15:16:42 30813

30813

概述:CD4060是一款14級二進制串行計數/分頻器,它是由一振蕩器和14級二進制串行計數器位組成,振蕩器的結構可以是RC或晶振電路,CR為高電平時,計數器清零且振蕩器使用無效。所有的計數器位均為主從觸發器。

2021-04-08 07:40:14

555定時器構成施密特觸發器時,其回差電壓為多少

2011-11-14 14:59:22

的典型功耗為10毫瓦。包含八個帶單軌輸出的觸發器緩沖時鐘和直接清除輸入各個觸發器的獨立數據輸入應用范圍包括:緩沖/存儲寄存器移位寄存器碼型發生器SN54HC161-SP與非門SN

2021-03-24 16:23:59

深亞微米的CMOS工藝制造高速分頻器。由于CMOS器件的價格低廉,因而高速CMOS分頻器有著廣闊的市場前景。那分頻電路由什么構成?你們知道2.4GHz動態CMOS分頻器設計難嗎?

2021-04-07 06:17:39

本帖最后由 gk320830 于 2015-3-7 18:17 編輯

跪求 !!分頻系數在一定范圍內可調的分頻器電路圖》。。

2013-08-29 18:19:29

請問有哪種可編程分頻器芯片啊?適合高頻,幾十兆到500兆。

2017-08-05 15:00:15

`有一種型號是SP8973A的分頻器芯片,哪位大神知道它可以用哪個型號的其他器件替換?我查到的是S8973,但是沒有數據依據,求大神解惑,小弟一個采購,對這類完全不懂,求幫助!`

2017-05-16 13:54:55

分頻器EDA設計代碼···僅供參考···

2013-12-09 12:26:46

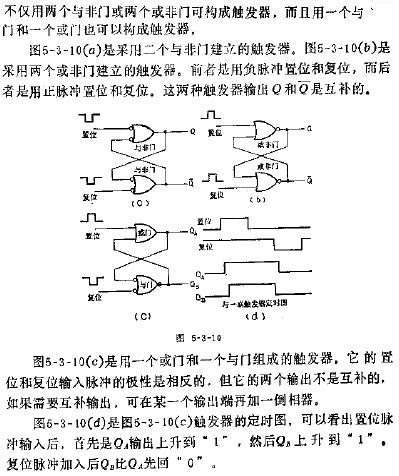

觸發器PPT電子教案:觸發器是構成時序邏輯電路的基本邏輯部件。? 它有兩個穩定的狀態:0狀態和1狀態;? 在不同的輸入情況下,它可以被置成0狀態或1狀態;? 當輸入信號消失后,所置成的狀態能夠保持

2009-09-16 16:06:45

觸發器實驗1)熟悉常用觸發器的邏輯功能及測試方法。2)了解觸發器邏輯功能的轉換。三.實驗內容及步驟 (1) 基本RS觸發器邏輯功能測試(2) JK觸發器邏輯功能測試(3) D觸發器邏輯功能的測試

2009-03-20 10:01:05

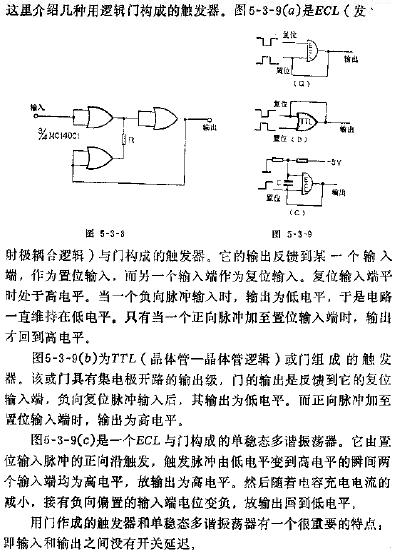

“復位”端。具有置位、復位功能的觸發器稱為R-S觸發器。雙穩態觸發器可用來構成各種計數器、分頻器和寄存器等。射極耦合觸發器又稱施密特觸發器,其原理電路如圖2。它也由兩級反相器直接耦合而成。第一級反相器

2012-06-18 11:42:43

D觸發器實現二分頻電路(D觸發器構成的2分頻電路)

2020-03-02 11:05:49

D觸發器組成的_2N_1_2分頻電路,幾種奇數分頻電路設計

2012-05-23 19:34:41

想開發一個相對小巧的DSP音頻分頻器模塊,可方便的加入到各種功放箱中。可設成2.3.4分頻可選。分頻點斜率可設。有單片MCU完成人機界面(簡單的)合芯片各控制功能。朋友推薦過ADAU1701剛簡單流覽了一下,沒法肯定是最好方案。當然上手快也很重要

2018-10-10 14:16:11

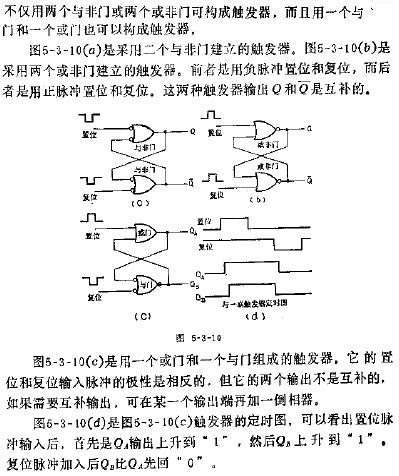

基本的SR NAND觸發器電路具有許多優點,并在順序邏輯電路中使用,但是它存在兩個基本的開關問題。1.必須始終避免設置= 0和復位= 0條件(S = R = 0)2.如果在啟用(EN)輸入為高時設置

2021-02-01 09:15:31

。 NB7V32M產生輸入時鐘的2分頻輸出副本,工作頻率高達10GHz,抖動最小。復位引腳在上升沿置位。上電時,內部觸發器將達到隨機狀態,復位允許系統中多個NB7V32M同步。 16mA差分CML輸出提供匹配的內部50歐姆端接,當外部接收器以50歐姆端接至VCC時,可確保400mV輸出擺幅

2019-02-20 09:41:47

R-S觸發器是最基本的一種觸發器,它由兩個“與非”門組成。它有兩個輸入端,分別稱為置“0”端(也稱為復位端、R端)和置“1”端(也稱為置位端、S端);它有兩個輸出端,分別稱為Q端和Q端。并且規定:當

2019-12-25 17:21:56

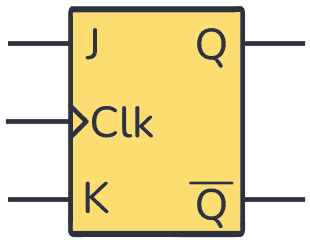

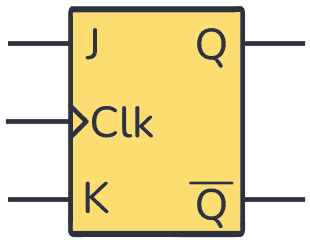

jk觸發器是什么原理jk觸發器特性表和狀態轉換圖

2021-02-26 08:18:24

跪求大神相告,在protel99se中哪個庫中有分頻器

2014-06-24 16:08:41

寄存器,由寄存器又可以組成存儲器。觸發器是由基本邏輯門電路構成的,它有兩種輸出穩定狀態,稱作為“1”狀態和“0”狀態,分別代表它所寄存的代碼為“1”和“0”;它有兩個輸入端,用于接收代碼“1”和“0

2019-12-25 17:09:20

什么是時序電路?SRAM是觸發器構成的嗎?

2021-03-17 06:11:32

邏輯可構成時序邏輯電路,簡稱時序電路。現在討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器。雙穩態:電子電路中。其雙穩態電路的特點是:在沒有外來觸發信號的作用下,電路始終處于原來的穩定狀態。在外

2016-05-21 06:50:08

雙D型觸發器構成的振蕩器電路實致上是一個可以靈活控制的波形信號發生器,其結構為圖1所示的一個由雙D型觸發器構成的振蕩器。該振蕩器的起振、停止可以控制,輸出波形的相位和占空比也可以調節,其工作波形如圖2所示。圖2 波形發生器工作邏輯圖

2009-05-25 00:41:49

觸發器構成異步觸發器,注意是上升沿還是下降沿觸發以下是列寫三個觸發器方程的過程,從Q2Q1Q0=000開始的狀態表沒有列寫,分析了無效狀態可以進入主循環。quaruts原理圖連線我本來是不想分析異步時序電路的,因為這不是課程的重點,奈何看到一些考研題目有這種折磨人的傻缺.

2021-09-06 08:20:26

存器,延遲觸發器,D型雙穩態,D型觸發器,或者簡稱為D觸發器,通常稱為D觸發器。的d觸發器是迄今最重要的時鐘控制的觸發器,因為它確保確保輸入S和R從未等于一在同一時間。D型觸發器由門控SR觸發器構成

2021-02-03 08:00:00

本帖最后由 weihu_lu 于 2014-6-19 16:25 編輯

作者:盧威虎1、前言 分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如

2014-06-19 16:15:28

【摘要】:介紹了基于FPGA的任意分頻系數的分頻器的設計,該分頻器能實現分頻系數和占空比均可以調節的3類分頻:整數分頻、小數分頻和分數分頻。所有分頻均通過VHDL語言進行了編譯并且給出了仿真圖。本

2010-04-26 16:09:01

新課第五章 觸發器5.1 概述1、觸發器具有“記憶”功能,它是構成時序邏輯電路的基本單元。本章首先介紹基本RS觸發器的組成原理、特點和邏輯功能。然后引出能夠防止“空翻”現象的主從觸發器和邊沿觸發器。同時,較詳細地討論RS觸發器、JK觸發器、D觸發器、T觸發器、T'觸發器的邏輯功能及其描述方法。

2009-04-02 11:58:41

如何用D觸發器實現2分頻 原理在線等

2016-07-03 19:37:58

如何用DAC和觸發器構成的恒流源?

2021-04-25 08:26:17

本帖最后由 gk320830 于 2015-3-5 20:47 編輯

如何用JK觸發器構成D觸發器 電路圖來人給個圖吧..

2011-11-14 15:21:03

NB7V33MMNGEVB,差分時鐘分頻器評估板。 NB7V33M是一個4分頻時鐘分頻器,具有異步復位功能。差分時鐘輸入包含內部50歐姆端接電阻,可接受LVPECL,CML和LVDS邏輯電平

2019-02-21 09:44:22

單片機內部有大量寄存器, 寄存器是一種能夠存儲數據的電路, 由觸發器構成。1.觸發器觸發器是一種具有記憶存儲功能的電路, 由門電路組成。 常見的觸發器包括: RS 觸發器、 D 觸發器和 JK觸發器

2022-01-20 07:13:51

。該數據可表示音序器的狀態、計數器的價值、在計算機內存的ASCII字符或任何其他的信息。有幾種不同類型的觸發器(flip-flops)電路具有指示器,如T(切換)、S-R(設置/重置)J-K(也可能稱為

2019-06-20 04:20:50

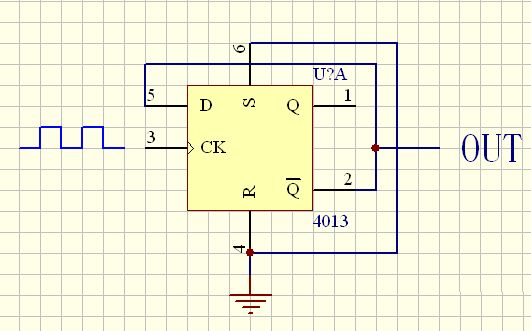

用CD4013雙D觸發器做的脈沖4分頻器

2021-05-13 07:25:00

模塊,如內核、閃存、存儲器和外設,這些模塊需要在不同頻率下運行。它們的最大運行速率可能受到所使用的實現技術、實施架構、功率目標、以及IP訪問時間等因素的限制。時鐘分頻器電路是必不可少的,它可以從主鎖相環

2012-12-11 14:43:20

是利用施密特觸發器和單穩態觸發器構成的整形電路對已有波形進行整形、變換得到。<br/>&nbsp;&nbsp;&nbsp

2009-09-24 09:38:04

我想對2GHz的正弦波(相位噪聲很低)進行16分頻,分頻出來的125M信號輸入給FPGA,想選用ADi的分頻器實現分頻功能,我有以下幾個問題:1.我查了ADi的分頻器,分為(1)時鐘分頻器,(2

2019-01-11 13:39:43

D觸發器結構的五分頻器邏輯電路

2019-09-11 11:29:19

PWM預分頻器、分頻器和定時器的分辨率是多少?

2020-12-07 06:07:09

請問一下D觸發器怎樣實現四分頻呢?

2023-05-10 14:34:08

電平觸發器和邊沿觸發器符號

2019-10-18 09:01:09

,我在我的項目中使用分頻器IP內核,錯誤似乎取決于分頻器輸入和輸出的寬度。如果我使用16位輸出和16位小數輸出,我得到正確的結果:切片邏輯分布:使用的LUT觸發器對的數量:850帶未使用的觸發器的數量

2020-07-16 11:53:30

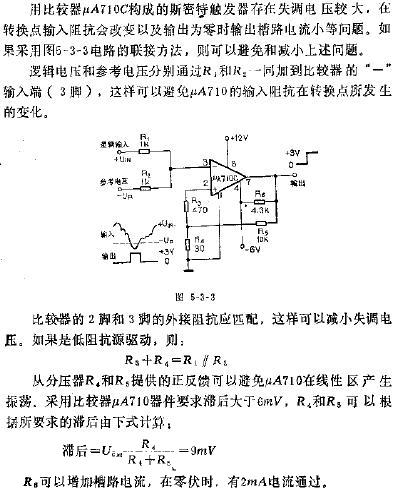

用運算放大器構成斯密特觸發器

2020-03-02 11:07:28

鎖存器的工作原理是什么?鎖存器的動態特性及其應用有哪些?觸發器的工作原理是什么?觸發器的電路結構是如何構成的?

2021-11-03 06:48:50

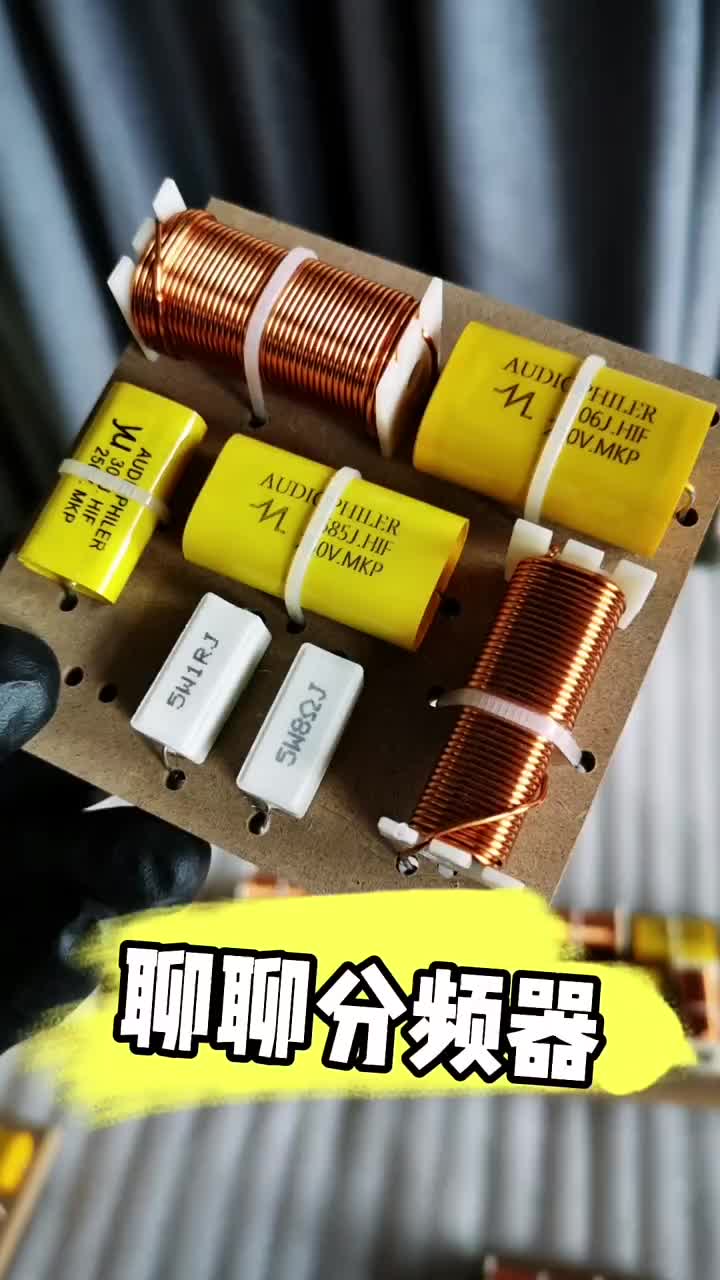

定阻型功率分頻器的設計與制作(三)-二階功率分頻器

2009-12-02 15:48:19 76

76 cd4013雙d觸發器

CD4013雙D觸發器做的脈沖4分頻器應用

-----------------------------. ┌─────

2008-01-09 23:48:45 4808

4808

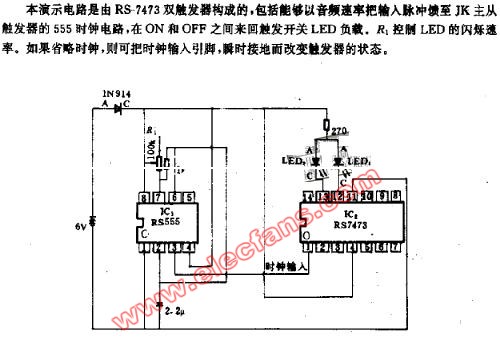

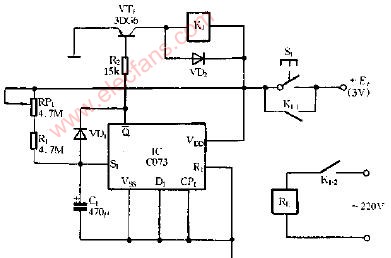

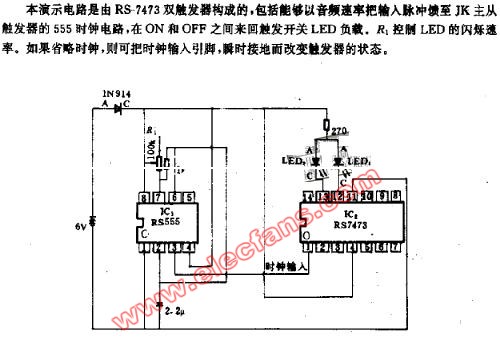

用雙觸發器構成的演示電路

2008-12-21 01:48:03 355

355

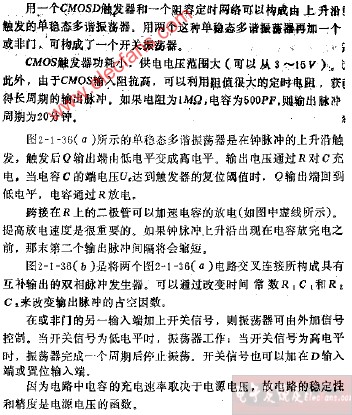

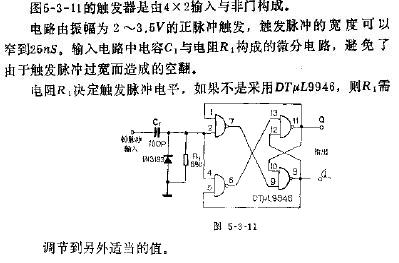

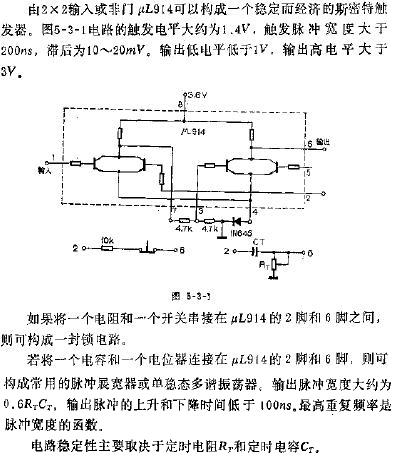

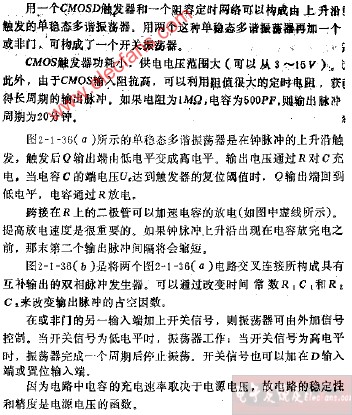

用CMOS“D”觸發器構成的脈沖發生器

2009-03-23 10:19:05 1603

1603

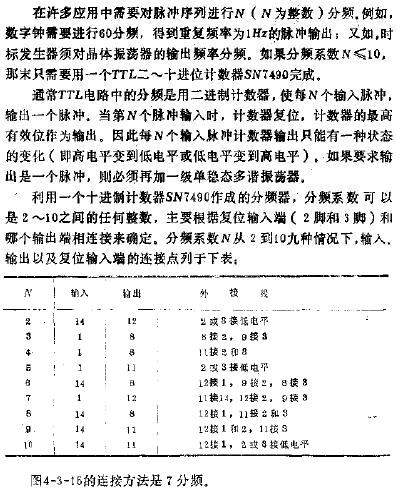

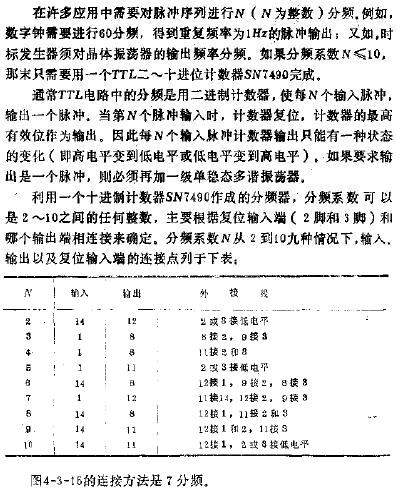

TTL十進位計數器構成的分頻器

2009-04-11 10:14:57 1163

1163

分頻系數可變的分頻器

2009-04-11 10:18:26 1206

1206

具有奇次和偶次分頻的分頻器

2009-04-11 10:22:12 880

880

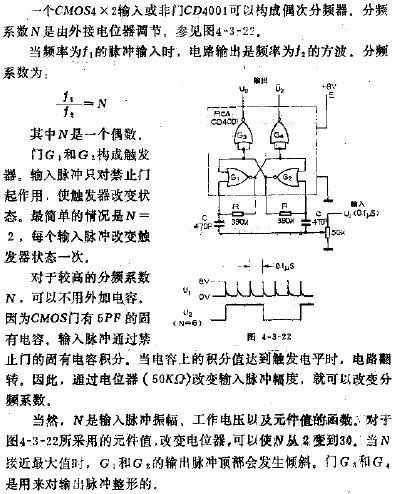

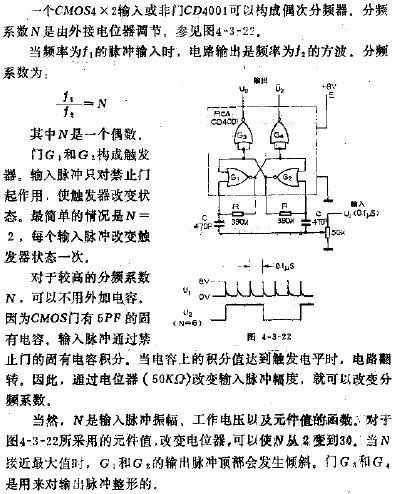

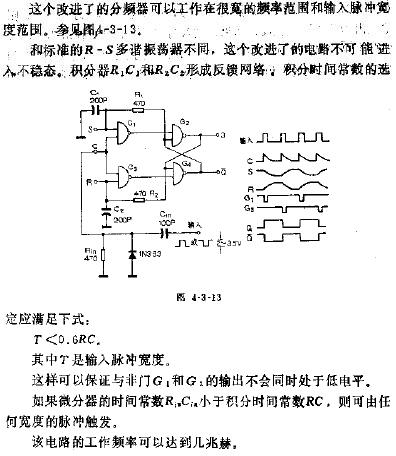

由CMOS門構成的可調分頻器

2009-04-11 10:28:20 962

962

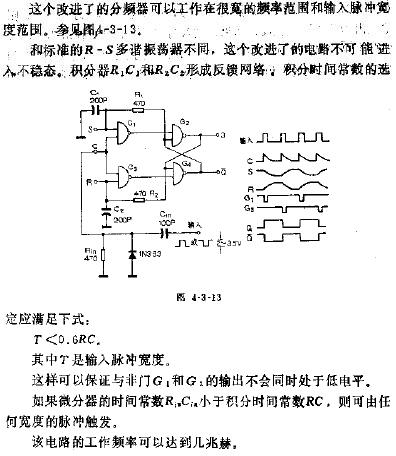

由R-S觸發器構成的分頻器

2009-04-11 10:28:43 961

961

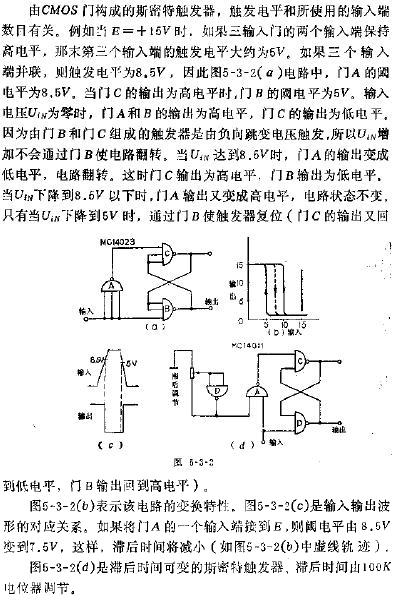

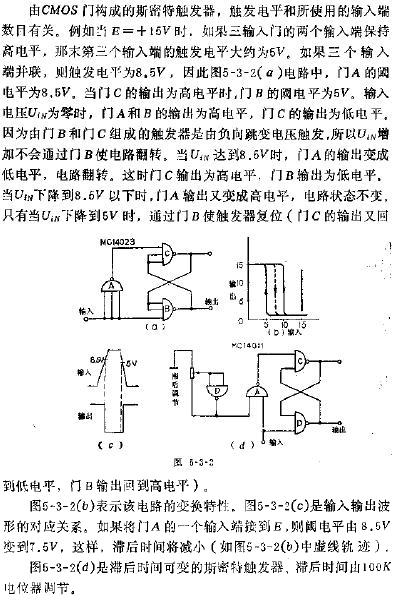

用CMOS門構成的斯密特觸發器

2009-04-13 10:22:33 1301

1301

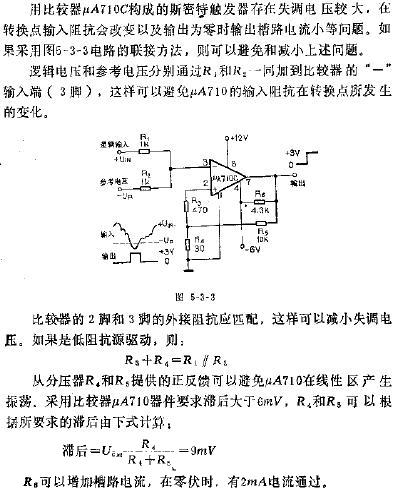

用比較器構成的斯密特觸發器

2009-04-13 10:22:59 1856

1856

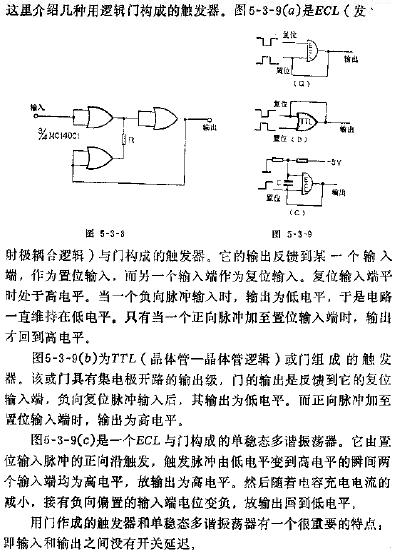

用門電路構成的觸發器I

2009-04-13 10:23:58 437

437

用門電路構成的觸發器II

2009-04-13 10:24:42 401

401

用門電路構成的觸發器III

2009-04-13 10:25:22 340

340

由或非門構成的斯密特觸發器

2009-04-13 10:26:26 1005

1005

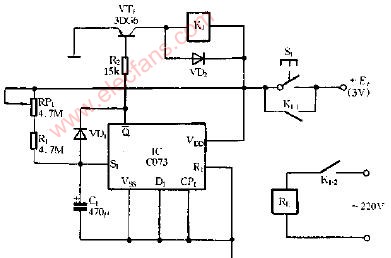

D觸發器構成的定時電路圖

2009-05-08 15:15:26 3366

3366

D觸發器實現二分頻電路(D觸發器構成的2分頻電路)&

2009-06-12 13:58:56 75438

75438

d觸發器構成2分頻電路

2009-06-22 07:36:33 7782

7782

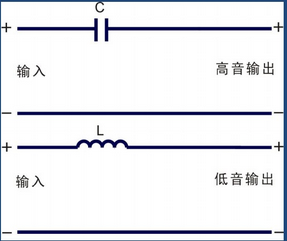

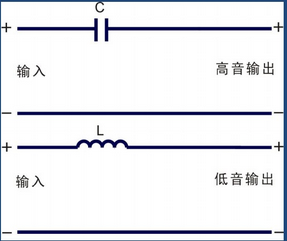

什么是分頻器 分頻器介紹

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放

2010-02-05 17:51:10 3676

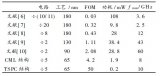

3676 本內容介紹了采用新觸發器的高速CMOS 前置分頻器 ,歡迎大家下載

2011-07-26 18:05:25 37

37 分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍

2011-08-17 16:50:45 1896

1896

。模擬分頻器可由注進鎖定等結構實現,一般具有工作頻率高、功耗低等優點,但是分頻范圍較小,芯片面積較大。數字分頻器基于觸發器結構,一般分頻范圍較寬,芯片面積較小,但相對于模擬分頻器其工作頻率較低,功耗較大。這里采用

2017-11-17 15:54:22 8

8 采用基于D 觸發器結構的五分頻器邏輯框圖如圖1所示。圖1 由3 個D 觸發器和少量邏輯門構成, 采用了同步工作模式, 其原理是由吞脈沖計數原理產生2 個占空比不同的五分頻信號A 和B, 然后對時

2018-04-18 14:04:00 8534

8534

分頻器分為主動式、被動式、脈沖分頻器三種。主動式電子分音器的原理就是要把適當頻率訊號傳給適當的單體,被動式分音器“功能、用途”是介于擴大器與喇叭之間,由于單一喇叭無法達到“全頻段響應”,脈沖分頻器利用漢穩態電路的計數功能實現分頻的電路,又稱為數字分頻器。

2018-01-10 15:36:20 10793

10793 本文開始介紹了什么是單穩態觸發器以及單穩態觸發器的電路組成,其次闡述了單穩態觸發器特點、門電路構成的單穩態觸發器、D觸發器構成的單穩態觸發器,最后詳細的闡述了時基電路構成的單穩態觸發器。

2018-03-27 09:24:23 71987

71987

電子分頻器根據是否采用放大器件分為無源型與有源型。其中無源型由阻容件構成,其結構簡單并且無其他附加失真,從綜合指標來看是音響電子分頻器中的佼佼者。

2018-08-10 15:45:37 9317

9317

,如本電路所示。電路中,集成電路μA795和μA747C構成標準的平方根電路。該電路的輸出是輸入電壓絕對值的正平方根。輸入是±0.5cosωt時,輸出則為cos( ωt/2)。觸發器9094、模擬開關Q1和Q2以及運算放大器μA747的一半構成“絕對值消除”電路。觸發器的觸發電平由R1確

2018-10-03 18:14:02 2369

2369 關鍵詞:MC4018 , 分頻器 如圖所示為數控分頻電路。 圖(a)為數控分頻器原理圖。它可以做到任意分頻系數且輸出為對稱方波。對于任意一個偶數N,可以寫成N=2M,而對于任意一個奇數N,則可

2018-10-03 18:23:01 526

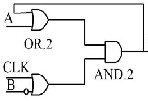

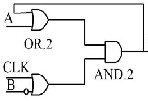

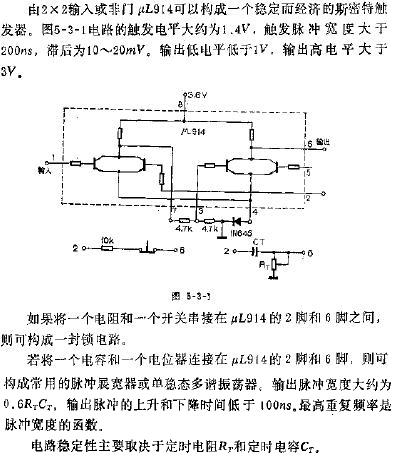

526 為f1的脈沖信號輸入時,電路輸出為頻率f2的方波,分頻系數為: N=f1/f2,其中N是偶數。 門G1和G2構成觸發器。輸入脈沖只對禁止門起作用,使觸發器改變狀態。最簡單的情況是N=2,這樣,每個輸入脈沖改變觸發器狀態一次。對于較高的分頻系數N,可以不用外加電容,因為CMOS門有5pF的固

2018-10-03 18:28:02 1856

1856 ,計數器的“借位”輸出除驅動觸發器SN7476外,還作為SN74193的寄存輸入脈沖。五位二進制數加在D0、D1、D2、D3、D4輸入端,由它確定分頻系數(2~32)。其中,D0是最低位。當D0=1時,多路調制器輸出脈沖的相位則根據觸發器的狀態確定。觸發器Q輸出為“0”時,多路調制器的輸出與鐘

2018-10-03 18:34:01 589

589 ,S8424是兩組RS T觸發器.S8480是4×2輸入與非門。二-八進制撥盤開關用來確定分頻器的分頻系數,以保證觸發器復位。如果采用二-十進制撥盤開關,另外再加一個觸發器和兩個二極管。則可構成分頻系數為1~10的分頻器。

2018-10-03 18:37:02 427

427 關鍵詞:SN74150 , SN7442 , SN7490 , 數字分頻器 如圖所示為數字分頻電路。該電路由3塊集成電路構成,分頻系數可以從1~9變化。計數器SN7490輸出的二-十進制數送至譯碼器

2018-10-08 07:58:01 1750

1750 本文檔的主要內容詳細介紹的是JK觸發器與RS觸發器到底是如何構成的有什么區別

2020-05-09 08:00:00 0

0 JK觸發器是一種可以設置、重置和切換的人字拖。它可用于制造計數器、事件檢測器、分頻器等等。

2023-06-29 11:48:23 34712

34712

計算機的時鐘節拍、頻率分頻、數據傳輸的幀同步等等。計數器可以通過級聯多個RS觸發器來實現,其中每個觸發器的輸出作為下一個觸發器的輸入。 頻率分頻器 RS觸發器可以用于構建頻率分頻器電路。頻率分頻器可以將一個輸入信號的頻率減小為

2023-11-17 16:03:44 751

751 如何用JK觸發器構成T觸發器 JK觸發器是一種基本的觸發器電路,由兩個輸入端J和K控制,以及兩個輸出端Q和Q'組成。JK觸發器的輸出可以持續性地保持其前一狀態或由輸入信號而改變。T觸發器是一種特殊

2024-02-06 14:11:11 425

425

電子發燒友App

電子發燒友App

評論