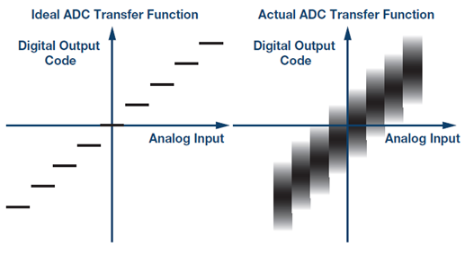

隨著高速模數(shù)轉(zhuǎn)換器 (ADC) 采樣率的提高,ADC 輸出數(shù)據(jù)中的代碼錯(cuò)誤(也稱為閃碼)問(wèn)題也隨之增加。代碼錯(cuò)誤定義為 ADC 輸出代碼中的錯(cuò)誤超過(guò)定義的閾值。閾值通常定義為誤差超過(guò) ADC 噪聲預(yù)期幅度的電平,以便在存在噪聲的情況下可以輕松識(shí)別誤差。

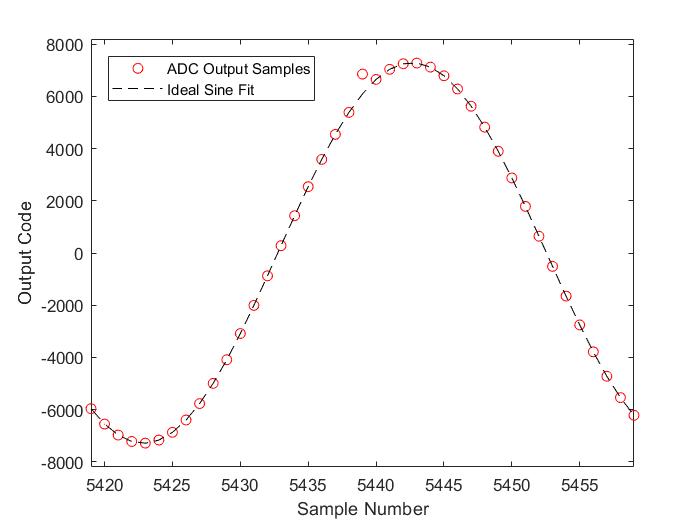

解釋誤差閾值定義的另一種方法是,誤差幅度的發(fā)生概率超過(guò)給定 ADC 假設(shè)的高斯分布噪聲的幅度的預(yù)期概率。圖 1顯示了在 ADC 的輸出樣本中發(fā)現(xiàn)的示例代碼錯(cuò)誤。與理想的正弦波擬合相比,錯(cuò)誤樣本清晰可見,并且遠(yuǎn)遠(yuǎn)超過(guò)圖中其他樣本的噪聲。

圖 1:帶有代碼錯(cuò)誤的 ADC 輸出示例。

ADC 的代碼錯(cuò)誤率 (CER),有時(shí)也稱為字錯(cuò)誤率 (WER) 或亞穩(wěn)態(tài)錯(cuò)誤率,定義為每個(gè)樣本的平均錯(cuò)誤數(shù),通過(guò)計(jì)算連續(xù)錯(cuò)誤之間的平均樣本數(shù)來(lái)測(cè)量。它通常被定義為一個(gè)數(shù)量級(jí),例如 10 –12個(gè)錯(cuò)誤/樣本。因此,錯(cuò)誤之間的平均時(shí)間取決于轉(zhuǎn)換器的采樣率。只有當(dāng) ADC 以測(cè)量 CER 的采樣率運(yùn)行時(shí),測(cè)量的 CER 才是準(zhǔn)確的。一般來(lái)說(shuō),降低采樣率可以將 CER 提高幾個(gè)數(shù)量級(jí)。

讓我們看看代碼錯(cuò)誤來(lái)自哪里,看看為什么采樣率是一個(gè)主要因素。

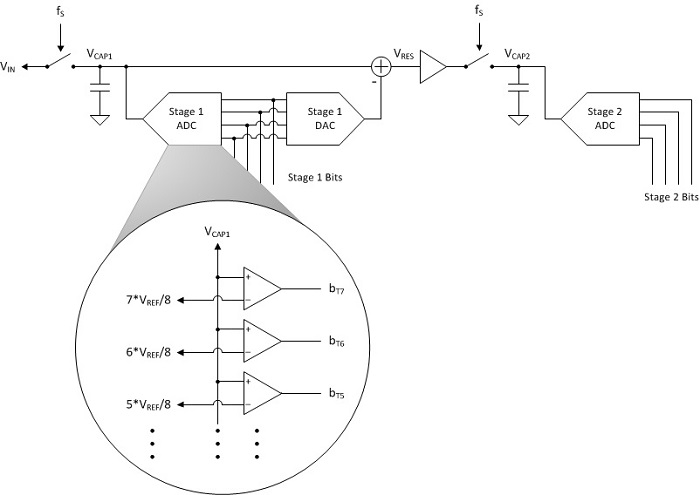

是什么讓 ADC 閃閃發(fā)光? 多步 ADC 架構(gòu),例如流水線閃存 ADC 或逐次逼近寄存器 (SAR) ADC,將采樣電壓分階段轉(zhuǎn)換為數(shù)字位,每個(gè)連續(xù)階段都依賴于前一階段的結(jié)果。考慮一個(gè)基本的流水線閃存高速 ADC,如圖2 所示。這個(gè)簡(jiǎn)化的 ADC 顯示了兩個(gè)轉(zhuǎn)換階段,其中每個(gè)連續(xù)的階段產(chǎn)生一個(gè)數(shù)字代碼,可以更精細(xì)地估計(jì)輸入信號(hào)。

所示 ADC 的操作如下:

第一級(jí)對(duì)輸入電壓進(jìn)行采樣,并使用第一級(jí) ADC 將模擬輸入信號(hào)粗略轉(zhuǎn)換為數(shù)字代碼。此階段的閃存 ADC 通過(guò)使用高速比較器將采樣電壓與由 ADC 的主參考電壓 (V REF ) 生成的靜態(tài)參考電壓進(jìn)行比較來(lái)工作。閃光比較器的輸出是代表輸入電壓的溫度計(jì)編碼數(shù)字樣本。

然后將轉(zhuǎn)換后的溫度計(jì)代碼直接發(fā)送到第一級(jí) DAC。該 DAC 輸出模擬電壓,對(duì)應(yīng)于粗略轉(zhuǎn)換的樣本。

從原始輸入電壓中減去第一級(jí) DAC 的輸出,得到量化誤差電壓或殘余電壓 (V RES )。然后將殘留物放大并重新采樣(流水線)用于第二階段。

第二級(jí) ADC 量化 V RES以獲得對(duì)原始模擬輸入電壓的更準(zhǔn)確(更高分辨率)的估計(jì)。

圖 2:流水線閃存 ADC 架構(gòu)框圖示例。

V RES創(chuàng)建過(guò)程引入了一個(gè)高速?zèng)Q策循環(huán)。在一個(gè)采樣時(shí)鐘周期內(nèi),采樣電壓必須由第一級(jí) ADC 轉(zhuǎn)換為數(shù)字代碼。數(shù)字代碼必須從第一級(jí) DAC 輸出,從原始輸入電壓中減去并由第二級(jí)重新采樣。高速?zèng)Q策環(huán)路會(huì)引入代碼錯(cuò)誤,因?yàn)殚W存 ADC 中的比較器有一個(gè)穩(wěn)定時(shí)間,該時(shí)間是采樣電壓和VREF之差的函數(shù)。

更簡(jiǎn)單地說(shuō),當(dāng)輸入電壓(V CAP1)接近比較器的參考電壓(例如 7 * V REF /8)時(shí),比較器需要更長(zhǎng)的時(shí)間來(lái)穩(wěn)定。理論上,如果 V CAP1無(wú)限接近比較器的參考電壓,則比較器將永遠(yuǎn)不會(huì)穩(wěn)定,因?yàn)樗鼘⒐ぷ髟谄渚€性區(qū)域。

噪聲會(huì)阻止這種情況實(shí)際發(fā)生,但如果比較器確實(shí)需要很長(zhǎng)時(shí)間才能穩(wěn)定,那么第一級(jí) DAC 可能會(huì)使用不正確的數(shù)字代碼來(lái)輸出量化的模擬電壓。結(jié)果是 V RES與第一級(jí) ADC 的實(shí)際數(shù)字輸出代碼不匹配。然后,第二級(jí) ADC 轉(zhuǎn)換錯(cuò)誤的 V RES,從而導(dǎo)致代碼錯(cuò)誤。

什么影響 CER?

您現(xiàn)在應(yīng)該有足夠的詳細(xì)信息,以便能夠就影響 CER 的因素得出一些結(jié)論。CER 顯然取決于采樣率。更快的采樣率減少了決策循環(huán)必須做出決策的時(shí)間。更短的決策時(shí)間導(dǎo)致比較器未及時(shí)穩(wěn)定的概率呈指數(shù)增長(zhǎng)。1另請(qǐng)注意,比較器的速度直接影響 CER,這是構(gòu)建 ADC 的工藝技術(shù)的一個(gè)強(qiáng)大功能。第三個(gè)因素是 ADC 的架構(gòu)。

具有高速?zèng)Q策循環(huán)的多步架構(gòu)容易受到較差 CER 的影響。有一些技術(shù)可用于降低這些架構(gòu)的 CER,例如使用更快的處理技術(shù)、實(shí)施時(shí)間交錯(cuò)或采用異步時(shí)鐘。2, 3另一方面,不使用高速?zèng)Q策回路的架構(gòu),例如折疊插值架構(gòu),可以使用多個(gè)比較器重新鎖存級(jí)而不影響任何后續(xù)級(jí),從而大大降低亞穩(wěn)態(tài)的概率。4

因此,與類似的流水線閃存或 SAR ADC 架構(gòu)相比,單步架構(gòu)本質(zhì)上具有更好的 CER。具有決策回路的多步架構(gòu)不能在沒(méi)有相應(yīng)速度降低的情況下使用比較器重新鎖定。

代碼錯(cuò)誤影響的示例

讓我們看一個(gè)代碼錯(cuò)誤如何影響示波器測(cè)量的示例。假設(shè) RS-485 發(fā)射器間歇性地輸出毛刺,工程團(tuán)隊(duì)正試圖在示波器上測(cè)量該毛刺以找出根本原因。假設(shè)毛刺很小,每隔幾天發(fā)生一次,并且示波器使用簡(jiǎn)單的電壓閾值檢測(cè)。還假設(shè)示波器以 10 GSPS 的速率進(jìn)行采樣,并且代碼錯(cuò)誤率為 10 –12個(gè)錯(cuò)誤/樣本。您是否更有可能從發(fā)射器中發(fā)現(xiàn)故障或從 ADC 中發(fā)現(xiàn)代碼錯(cuò)誤?讓我們來(lái)了解一下!

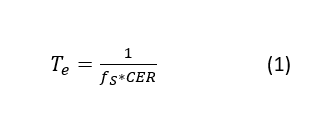

誤差之間的平均時(shí)間(以秒為單位)是 T e,您可以根據(jù)公式 1 從 CER 和 ADC 采樣率 (f S ) 計(jì)算得出:

以上面的 RS-485 毛刺示例為例,示波器的平均誤差間隔時(shí)間計(jì)算為 100 秒。如果每隔幾天就會(huì)出現(xiàn) RS-485 毛刺,那么將很難從被測(cè)設(shè)備中捕獲所需的毛刺,因?yàn)槭静ㄆ鲗⒊掷m(xù)觸發(fā)代碼錯(cuò)誤。

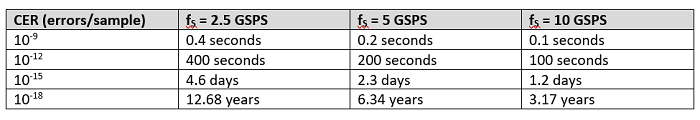

那么什么 CER 是可以接受的呢?表 1顯示了各種錯(cuò)誤率和采樣率的平均錯(cuò)誤間隔時(shí)間。在 10 GSPS 時(shí),需要遠(yuǎn)低于 10 –15 的代碼錯(cuò)誤率才能捕獲每隔幾天發(fā)生的故障。使用折疊插值 ADC 構(gòu)建的示波器(例如ADC12DJ5200RF)很有可能捕捉到毛刺,而不會(huì)因?yàn)槠?10 –18的低 CER 而導(dǎo)致間歇性代碼錯(cuò)誤導(dǎo)致誤觸發(fā)。

表 1:T e與 CER 和采樣率的關(guān)系。

代碼錯(cuò)誤對(duì)高速 ADC 應(yīng)用有不同程度的影響。示波器和基于脈沖的飛行時(shí)間 (ToF) 系統(tǒng)(例如 LiDAR 或激光距離測(cè)量)在使用簡(jiǎn)單閾值檢測(cè)時(shí)可能對(duì)代碼錯(cuò)誤更敏感,而通信或雷達(dá)系統(tǒng)可能不太敏感。

例如,通信系統(tǒng)經(jīng)常使用前向糾錯(cuò) (FEC),它可以克服 ADC 樣本數(shù)據(jù)中單個(gè)代碼錯(cuò)誤的影響。雷達(dá)使用基于匹配濾波器(相關(guān))的檢測(cè)算法,該算法使用長(zhǎng)波形來(lái)提高檢測(cè)精度,從而從本質(zhì)上減輕單個(gè)代碼錯(cuò)誤的影響。

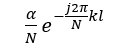

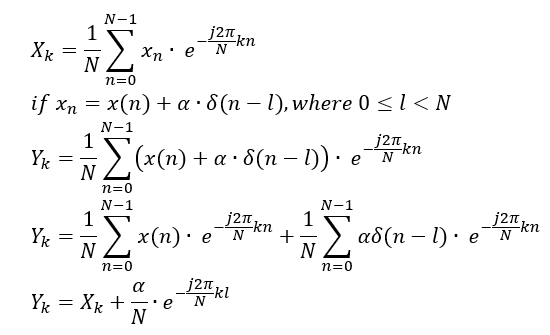

頻域中 的代碼錯(cuò)誤 代碼錯(cuò)誤的頻譜,如離散傅里葉變換 (DFT) 的輸出所示,是在所有頻率區(qū)間均值相等的升高的本底噪聲。下面的計(jì)算從輸出 X k的歸一化 DFT 的定義開始,到出現(xiàn)代碼錯(cuò)誤時(shí)的輸出頻譜 Y k。這

Y k中的項(xiàng)是在時(shí)域信號(hào)中表示為脈沖的單個(gè)碼錯(cuò)誤的頻率貢獻(xiàn)。真實(shí) DFT 的本底噪聲功率提高了

它與誤碼幅度的平方 α 2成正比,與 DFT 的平方長(zhǎng)度 N 2成反比。因此,使用較長(zhǎng)信號(hào)長(zhǎng)度或分析窗口的系統(tǒng)將受到代碼錯(cuò)誤的影響較小。

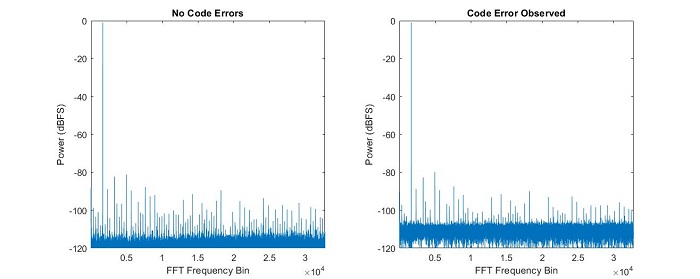

圖3說(shuō)明了由圖1中的碼錯(cuò)誤引起的升高的本底噪聲,其幅度為758碼。在將結(jié)果歸一化為 14 位轉(zhuǎn)換器的滿量程功率后,對(duì)于長(zhǎng)度為 65,536 的實(shí)際 DFT 計(jì)算得出的每個(gè) bin 的噪聲功率為 –110.98 dBFS/bin,

該結(jié)果與圖 3中被代碼錯(cuò)誤破壞的測(cè)量的本底噪聲相匹配。

圖 3:有和沒(méi)有代碼錯(cuò)誤的頻域。

結(jié)論代碼錯(cuò)誤在 高速 ADC的時(shí)域輸出中表現(xiàn)為不需要的脈沖。在頻域中,使用 DFT 進(jìn)行測(cè)量,代碼錯(cuò)誤會(huì)導(dǎo)致本底噪聲升高。雖然某些應(yīng)用程序可以忍受這些代碼錯(cuò)誤,但其他應(yīng)用程序(例如示波器或基于脈沖的 ToF)需要低錯(cuò)誤率才能成功。

代碼錯(cuò)誤是多步 ADC 架構(gòu)中比較器亞穩(wěn)態(tài)的結(jié)果,需要在前一階段快速做出高速?zèng)Q策,以便下一階段使用結(jié)果。采樣率、比較器速度和 ADC 架構(gòu)會(huì)影響 ADC 設(shè)計(jì)的 CER。

不需要高速?zèng)Q策環(huán)路的 ADC 架構(gòu)(例如折疊插值架構(gòu))本身就具有更好的 CER,因?yàn)樗鼈兡軌蛑匦骆i定比較器輸出,從而在沒(méi)有相應(yīng)速度降低的情況下降低亞穩(wěn)態(tài)概率。

ADC12DJ5200RF是一款超高速 ADC,提供業(yè)內(nèi)最低的可用 CER,使工程師能夠?yàn)闇y(cè)試和測(cè)量應(yīng)用實(shí)現(xiàn)高測(cè)量信心。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論