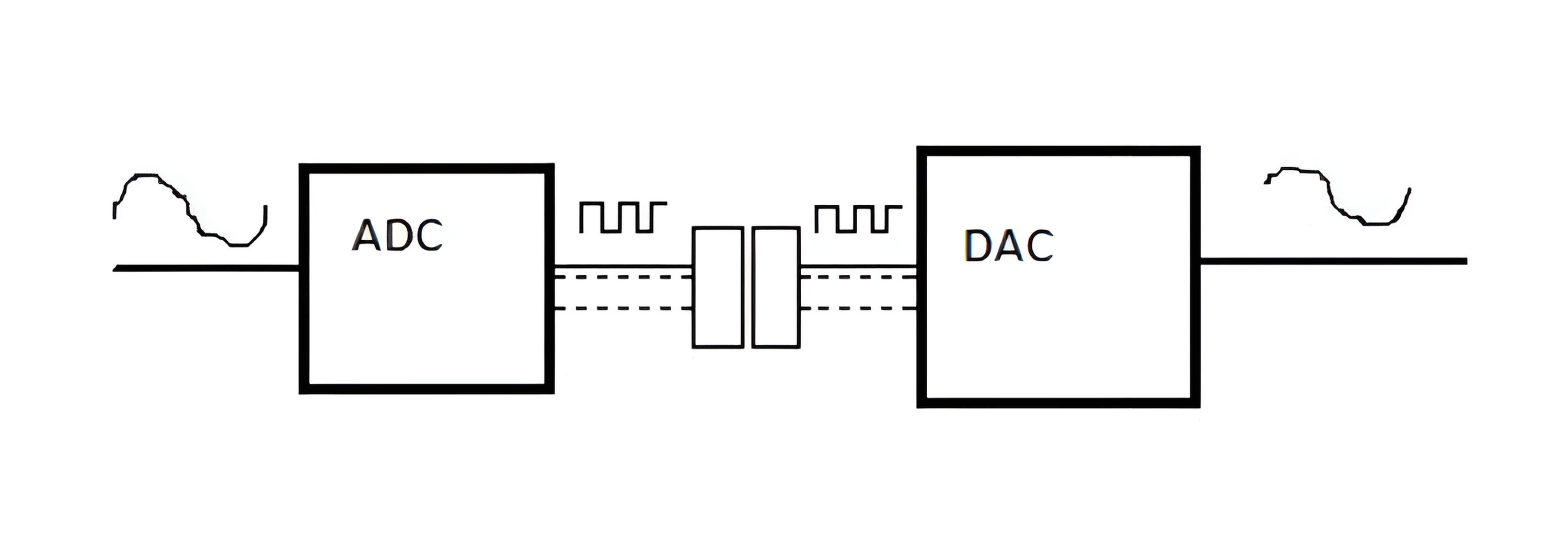

在現實世界中,常見的信號大都是模擬量,像溫度、聲音、氣壓等,但在信號的處理與傳輸中,為了減少噪聲的干擾,較多使用的是數字量。因此我們經常會將現實中的模擬信號,通過 ADC 轉換為數字信號進行運算、傳輸、儲存,再通過 DAC 轉換為模擬信號,呈現出來。

但要注意的是,現實中的模擬量連續的,意味著它有無限的分辨率,但轉換為數字量之后,將會丟失一定的精度,在時間和幅度上都會變成離散的值。

ADC 基本原理

ADC(Analog-to-Digital Converter)指模擬 / 數字轉換器,可將真實世界的模擬信號,例如溫度、壓力、聲音或者圖像等,轉換成更容易儲存、處理和發射的數字形式。

采樣

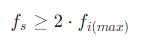

因為輸入的模擬信號是連續的,而將要輸出的數字信號是離散的,所以只能進行瞬時采樣,再將采樣值轉換為輸出的數字量,再重新開始下一輪的采樣。

為了能準確無誤用信號 v_svs 表示出模擬輸入信號 v_1v1,至少需要滿足采樣定理,即采樣頻率 f_sfs 在模擬輸入信號最高頻率分量fi(max) 的 2 倍以上(通常會取 3~5 倍,但太高的頻率需要更快的工作速度,需要綜合成本考慮):

只要滿足了采樣定理,即可用低通濾波器,將 v_svs 還原為 v_1v1。濾波器電壓傳輸系數應在低于 fi(max) 時保持不變,在 fs?fi(max) 前迅速下降為 0。

保持

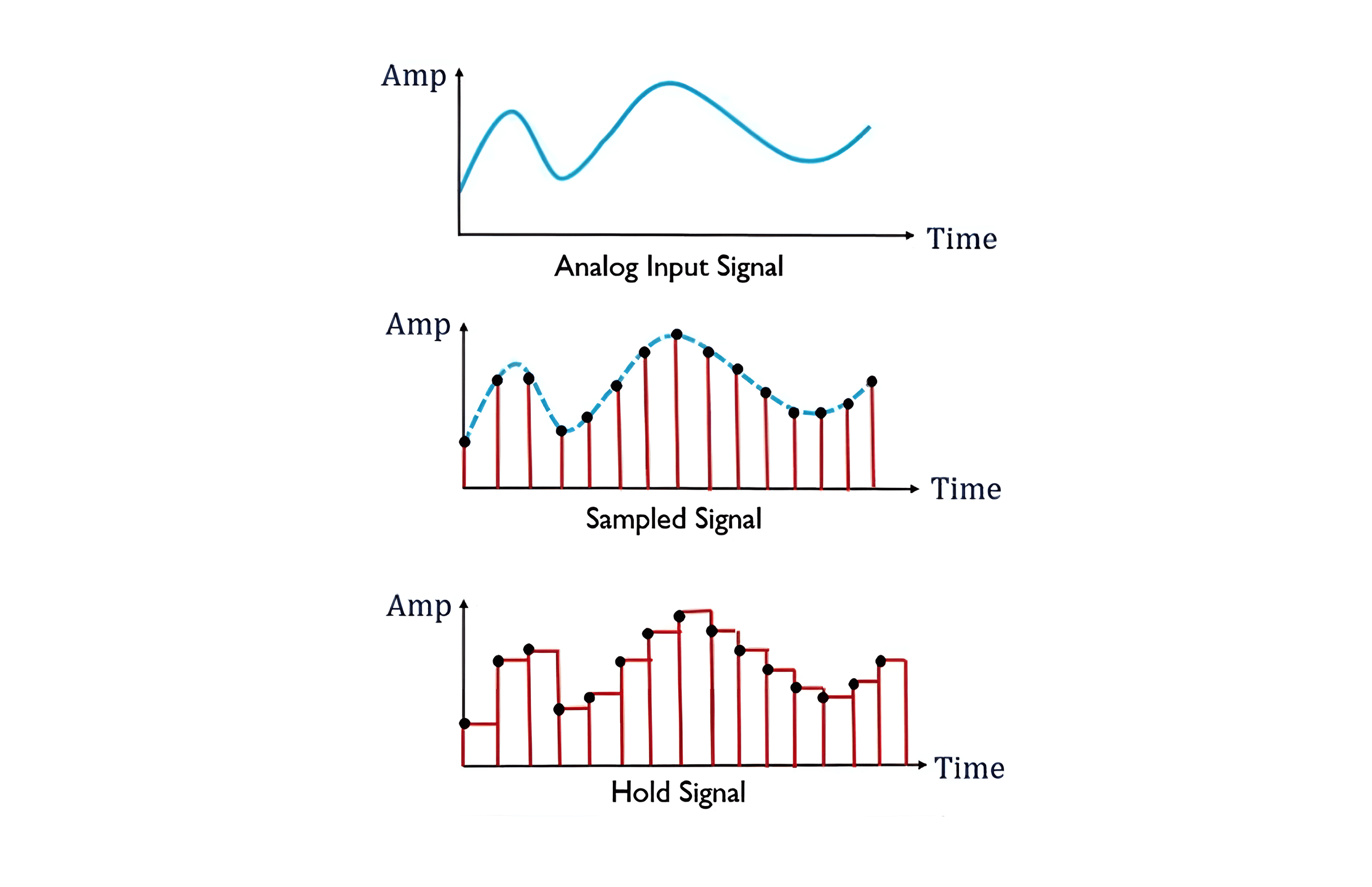

保持電路能夠采樣結束后,讓信號保持一段時間,使 ADC 有充分時間進行轉換。一般采樣脈沖頻率越高、采樣越密,采樣值就越多,采樣保持電路的輸出信號就越接近輸入信號的波形。采樣 - 保持電路的基本形式如下:

采樣 - 保持的基本步驟:

當采樣控制信號 vL 為高電平時,使 MOS 管 T 導通,v1 經過電阻 1 和 MOS 管 T,給電容 CH 充電。

若取 R1=RF,則充電結束后 v0=vc=?v1。

當采樣控制信號 vL 跌落回電平時,MOS 管 T 截止,電容 CH 上的電壓不會突變,所以 v0 也能保持一段時間,采樣結果得以被記錄下來。

量化

采樣得到的數字量,必須為某個規定的最小數值單位的整數倍,這個轉換過程稱為量化,所取的最小數量單位稱為量化單位 Δ。數字信號最低有效位 LSB 的 1 所代表的數量大小就等于 Δ。

因為模擬電壓是連續的,不一定能被 Δ 整除,因此會出現量化誤差。

量化級越細,量化誤差就越小,所用二進制代碼的位數就越多,電路也越復雜。

編碼

將量化的結果用二進制(或其他進制)表示出來,稱為編碼。

ADC 常見類型

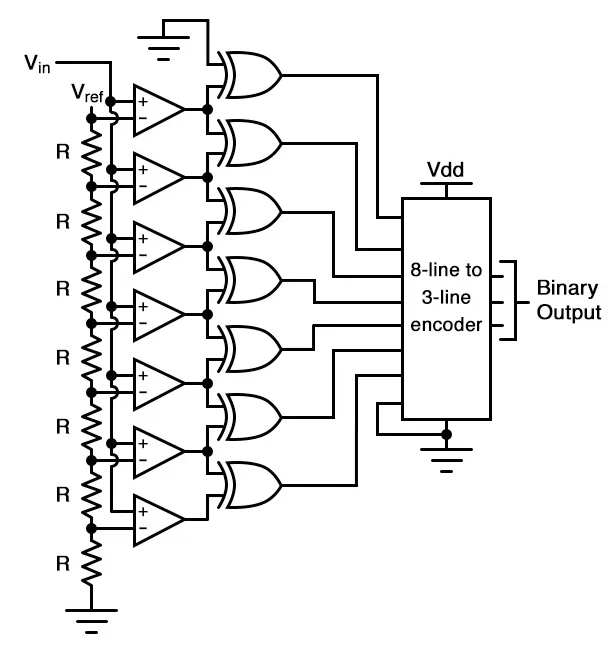

并聯比較型(Flash)

并聯比較型 ADC 又稱 Flash ADC,屬于直接 ADC,能將輸入的模擬電壓直接轉換為輸出的數字量,不需要經過中間變量轉換。它由一系列電壓比較器組成,每個比較器將輸入信號與唯一的分壓后的參考電壓進行比較。比較器的輸出連接編碼器電路的輸入,產生二進制的輸出。

不僅在操作理論方面是最簡單的,而且在速度方面也是最有效的 ADC 技術,僅受比較器和柵極傳播延遲的限制。不幸的是,對于任何給定數量的輸出位,它是最密集的組件

并聯比較型 ADC 的轉換速度是最快的,但缺點是需要使用很多電壓比較器和大規模的代碼轉換電路(常見的并聯比較型輸出大都在 8 位以下)。

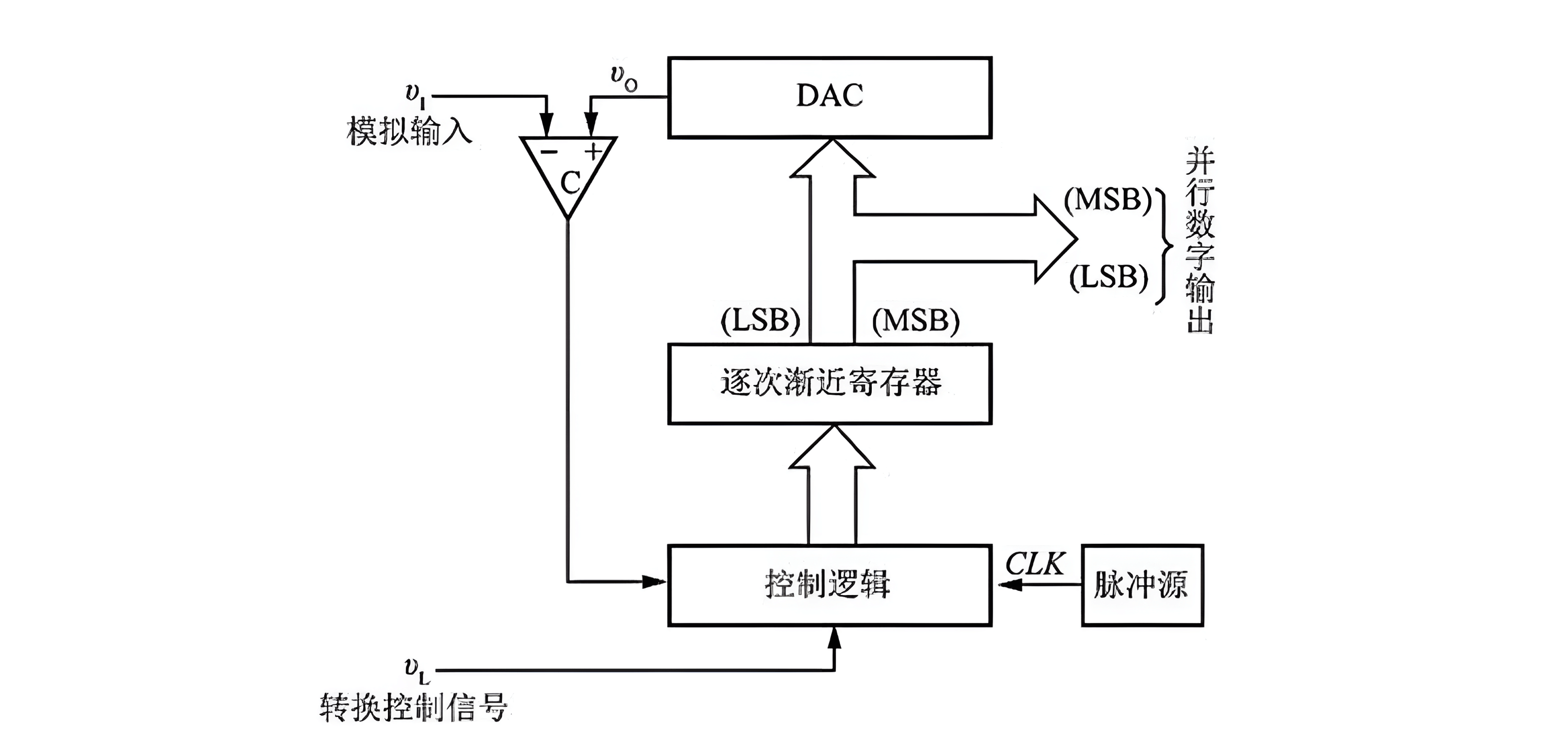

逐次逼近型

逐次逼近型(Successive Approximation)ADC 采用的是一種反饋比較型電路結構。由比較器、DAC、寄存器、時鐘脈沖源和控制邏輯等組成:

其原理是,設定一個數字量,通過 DAC 得到一個對應的輸出模擬電壓。將這個模擬電壓和輸入的模擬電壓信號從最高位開始順序地相比較,如果兩者不相等,則調整所取的數字量,直到兩個模擬電壓相等為止,最后所取的這個數字量就是所求的轉換結果。其過程像用天平去稱量位置重量的物體,先加大砝碼,再逐次添加或換用小砝碼。

逐次逼近型 ADC 的優點是速度高,功耗低,在低分辨率(12 位)下具有性價比優勢;缺點是轉換速率一般,電路規模中等。

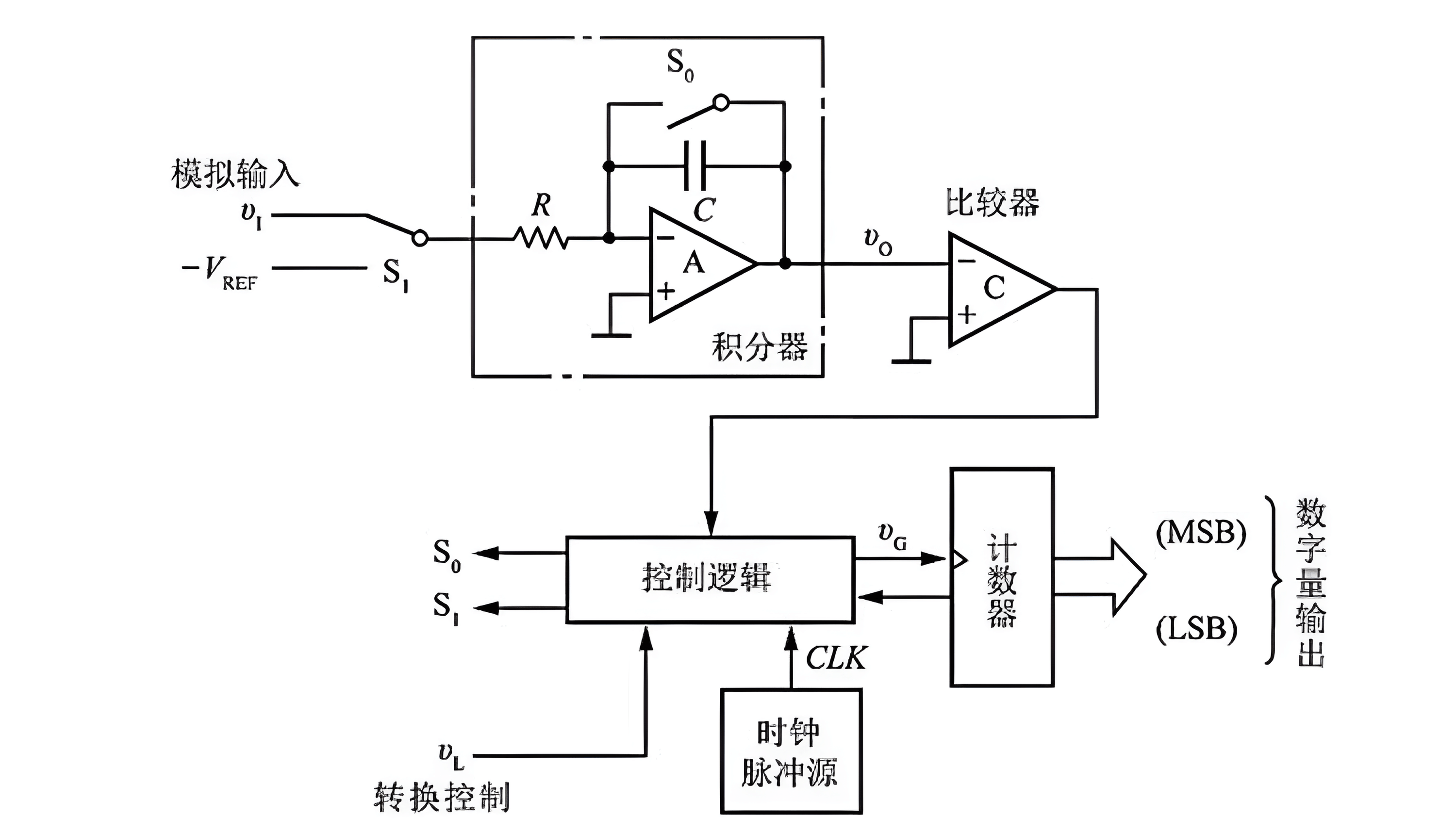

雙積分型(V-T)

雙積分型 ADC 是一種間接 ADC,它首先將輸入的模擬電壓信號轉換成與之成正比的時間寬度信號,隨后在此時間寬度內,對固定頻率的時鐘進行脈沖計數,計數的值就是正比于模擬輸入電壓的數字信號。因此,也將這種 ADC 稱為電壓 - 時間變換型(V-T)ADC。

雙積分型 ADC 由積分器、比較器、計數器、控制邏輯和時鐘信號源組成,如圖:

雙積分型 ADC 的優點是工作性能穩定(兩次積分,排除 RC 參數差異)、抗干擾能力強(積分受噪聲影響不大);缺點是轉換速率低(轉換精度依賴于積分時間)。

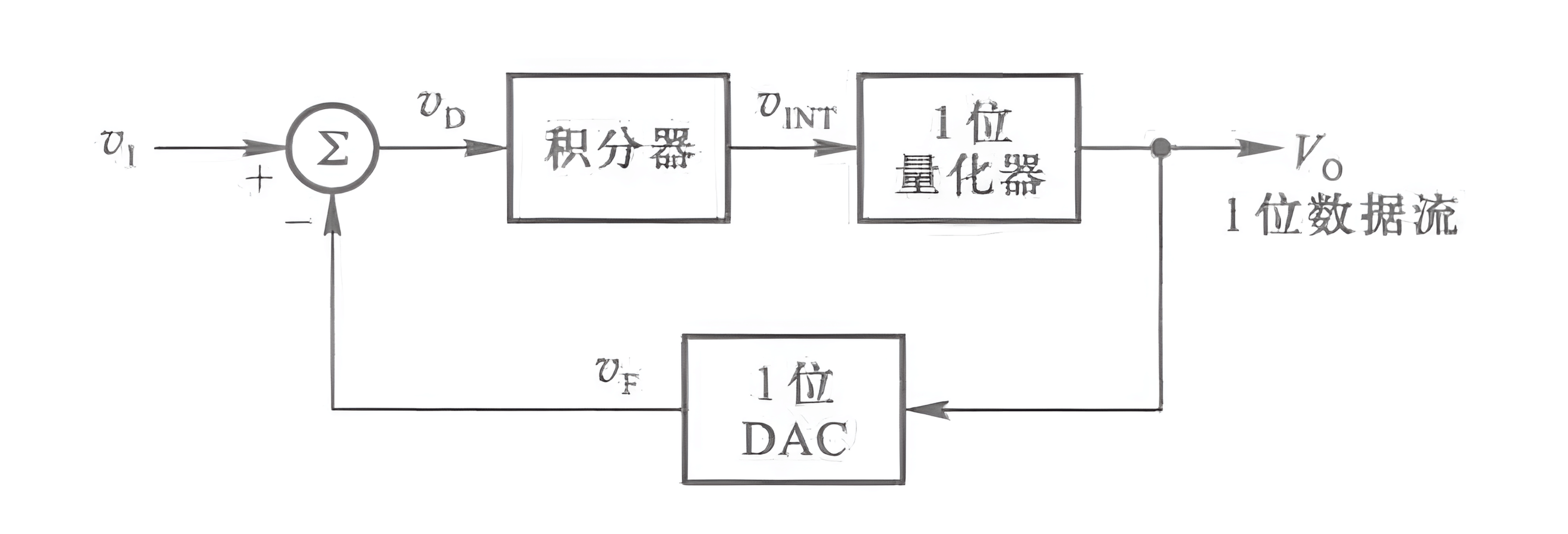

Σ-Δ 型

Σ-Δ 調制型 ADC 的原理與上文的并聯型與逐次逼近型 ADC 不同,它不是將采樣信號的絕對值進行量化編碼,而是將兩次相鄰采樣值之差(增量)進行量化與編碼的。其基本結構如下:

它由線性電壓積分器、1 位輸出量化器、1 位輸入 DAC 和一個求和電路組成。經過量化器處理輸出的數字信號 V0,經過 DAC 轉換為模擬信號VF,并負反饋至輸入端的求和電路,與輸入信號 v1 相減,得到差值 vD。積分器對 vD 作線性積分,輸出電壓 vINT 至量化器,由量化器量化為 1 位的數字量輸出。由于采用 1 為輸出的量化器,所以在連續工作的狀態下,輸出信號 V0 是由 0 和 1 組成的數據流。

Σ-Δ 調制型 ADC 的優點是可以容易地做到高分辨率測量;缺點是轉換速率低、電路規模大。

電壓 - 頻率變換型(V-F)

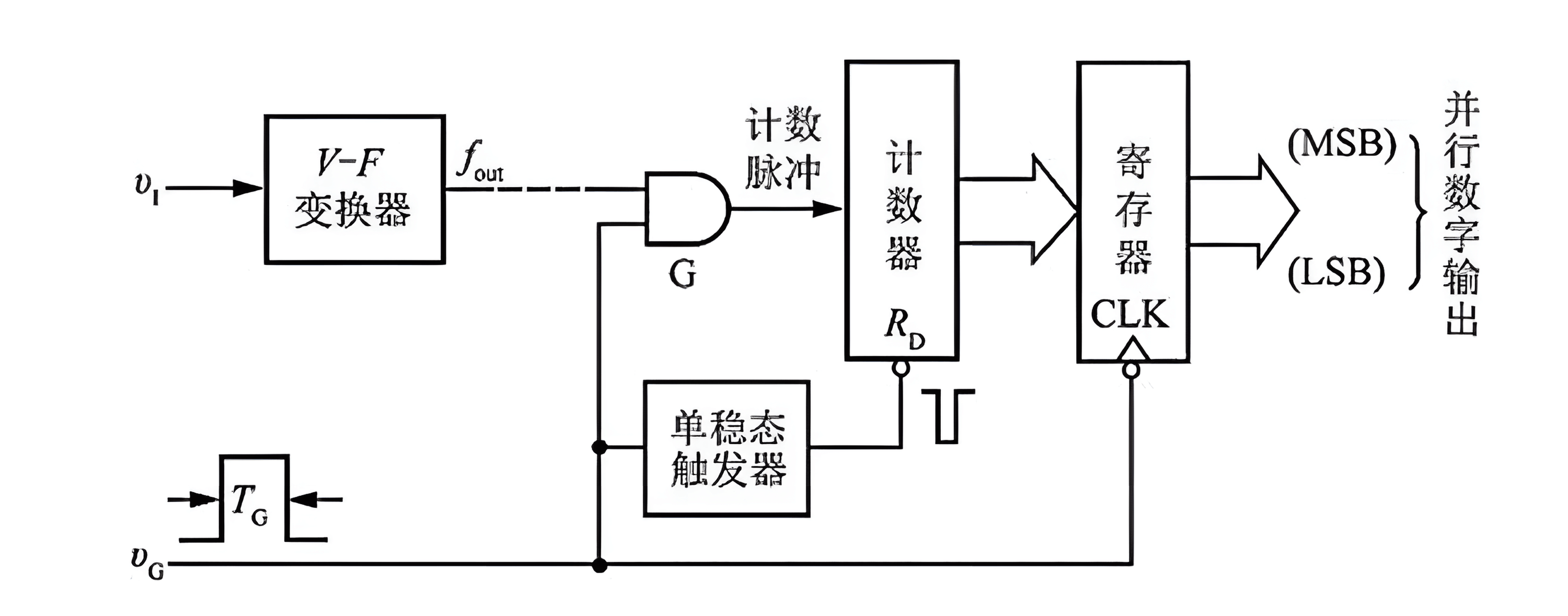

電壓 - 頻率變換型(V-F)ADC 是一種間接 ADC。主要由 V-F 變換器(也稱為壓控振蕩器 Voltage Controlled Oscillator,簡稱 VCO)、計數器及其時鐘信號控制閘門、寄存器、單穩態觸發器等幾部分構成:

其原理是:

將輸入的模擬電壓信號轉換為對應的頻率信號。

在固定的時間內對頻信號率計數。

計數結果正比于輸入電壓的幅值。

ADC 主要參數

分辨率:輸出數字量變化一個相鄰數值所需輸入模擬電壓的變化量,一般用二進制的位數表示,分辨率為 n 表示是滿刻度 Fs 的 2 的 n 次方分之一。

量化誤差:ADC 的有限位數對模擬量進行量化而引起的誤差。要準確表示模擬量,ADC 的位數需要很大甚至無窮大,所以 ADC 器件都有量化誤差。一個分辨率有限的 ADC 的階梯狀轉換特性曲線與具有無限分辨率的 ADC 轉化特性曲線之間的最大偏差就是量化誤差。

轉換速率:每秒進行轉換的次數。

轉換量程:ADC 所能測量的最大電壓,一般等于參考電壓,超過此電壓有可能損毀 ADC。當信號較小時可以考慮降低參考電壓來提高分辨率,改變參考電壓后,對應的轉換值也會改變,計算實際電壓時需要將參考電壓考慮進去,所以說一般參考電壓都要做到很穩定且不帶有高次諧波。

偏移誤差:ADC 輸入信號為 0 時,但 ADC 轉換輸出信號不為 0 的值。

滿刻度誤差:ADC 滿刻度輸出時對應的輸入信號與理想輸入信號值之差。

線性度:實際 ADC 的轉移函數和理想直線的最大偏移。

DAC 基本原理

DAC(Digital-to-Analog Canverter),指數字 / 模擬轉換器。可將數字量轉換為成比例的模擬電壓或電流。舉個例子,計算機可能產生范圍從 00000000 到 11111111 的數字輸出,DAC 將其轉換為范圍從 0 到 10V 的電壓。DAC 從基本原理上可以分兩類:電流求和型、分壓器型。

DAC 常見類型

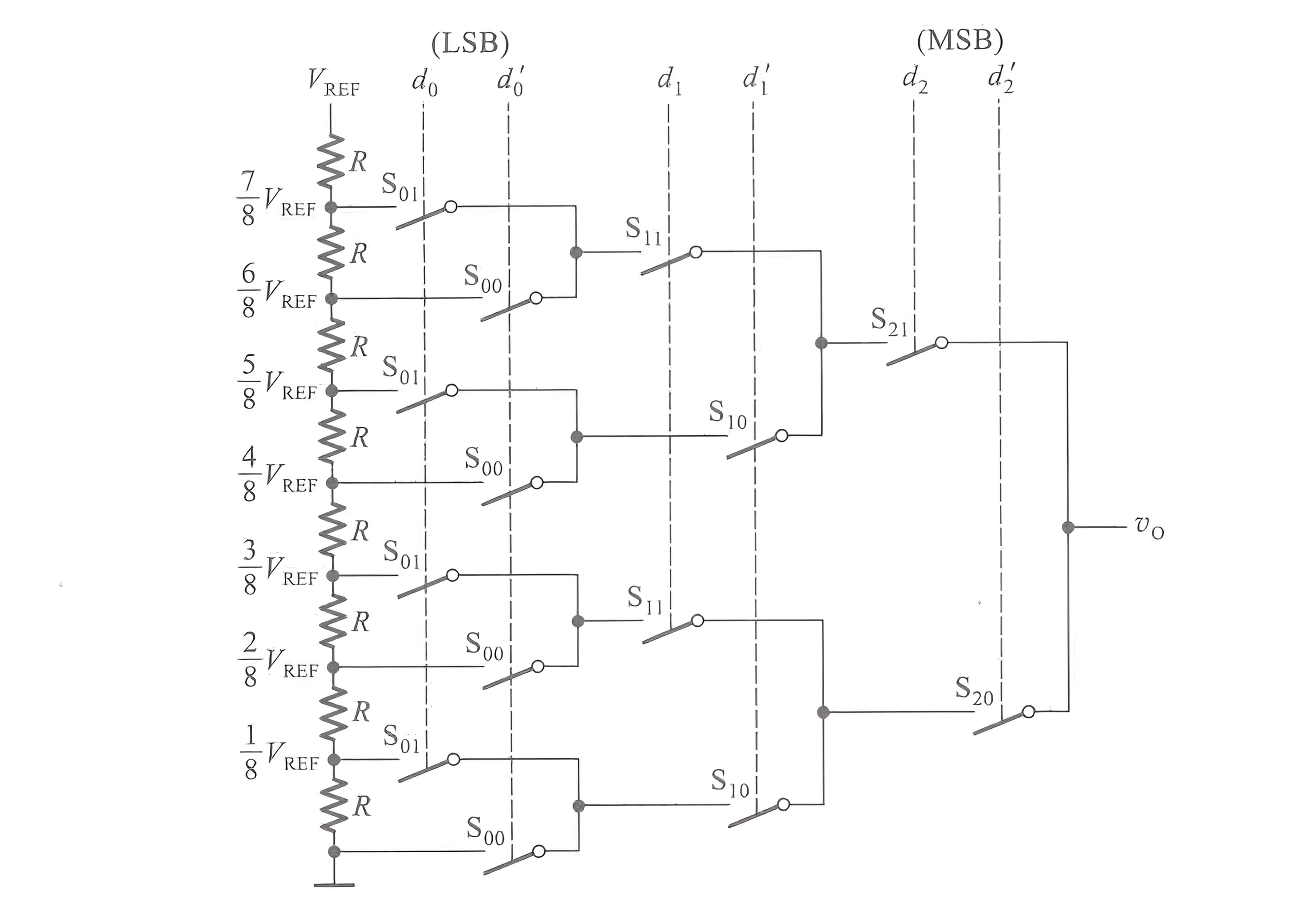

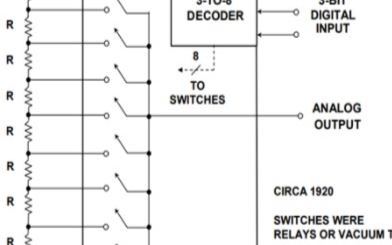

開關樹型

開關樹型 DAC 是最簡單粗暴的 DAC,由電阻分壓器和樹狀的開關網絡組成:

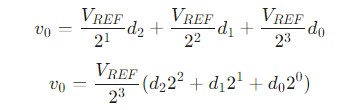

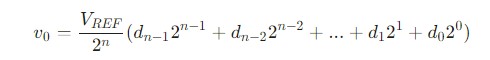

這些開關分別受 3 位輸入d0,d1,d2 控制,由此可得:

進一步看,對于 n 位二進制輸入的開關樹型 DAC,輸出為:

開關樹型 DAC 特點是電阻種類單一,且在輸出端基本不取電流的情況下,對開關導通電阻要求不高;但缺點是用的開關太多。

權電阻網絡

權指的是一個多位二進制數中,每一位 1 所代表的數值。例如,一個 n 位二進制數 從最高位(Most Significant Bit, MSB)到最低位(LSB)的權依次為

從最高位(Most Significant Bit, MSB)到最低位(LSB)的權依次為

權電阻網絡型 DAC(屬于電壓輸出型)的原理如下圖所示(4 位),它由權電阻網絡,4 個模擬開關和 1 個求和放大器組成:

其中,S0,S1,S2,S3 是 4 個電子開關,受 d0,d1,d2,d3 4 個信號的控制,輸入為 1 時開關撥到 VREF,輸入為 0 時開關接地。所以,當 di=1 時有之路電流 Ii 流向求和放大器,di=0 時之路電流為零。求和放大器是一個負反饋放大器,當反相輸入端 V? 的電位低于同相輸入端的電位 V+ 時,輸出端對地電壓 v0 為正;當 V_+V?>V+ 時,v0 為負。且當 V? 稍高于 V+ 時,即可在 v0 產生大幅度的負輸出電壓。v0 經 RF 反饋回 V?,使得 V? 降低回 V+(0V)。

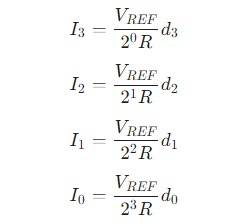

假設運算放大器為理想器件(輸入電流為零),則可得到:

又因為 V_≈0,因此各支路電流分別為:

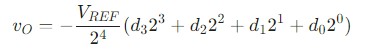

其中,d_ndn 可取 0 或 1。代入上式,并假設反饋電阻 時,可得到輸出電壓:

時,可得到輸出電壓:

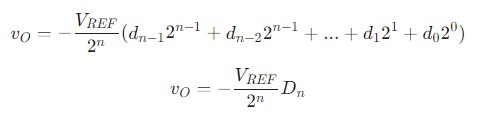

進一步看,對于 n 位權電阻網絡 DAC,當反饋電阻 時,輸出電壓計算公式是:

時,輸出電壓計算公式是:

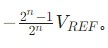

所以,輸出的模擬電壓正比于輸入的數字量 Dn,其變化范圍是 0 至

另外一方面,如果需要得到正輸出電壓,則應該提供負的 VREF。

權電阻網絡型 DAC 的優點是結構簡單,但缺點是個電阻阻值相差較大,在現實中有可能造成比較大的精度差。為了改善,可以采用雙極權電阻網絡,此處不展開說明,但仍無法從根本上解決。

倒 T 形電阻網絡

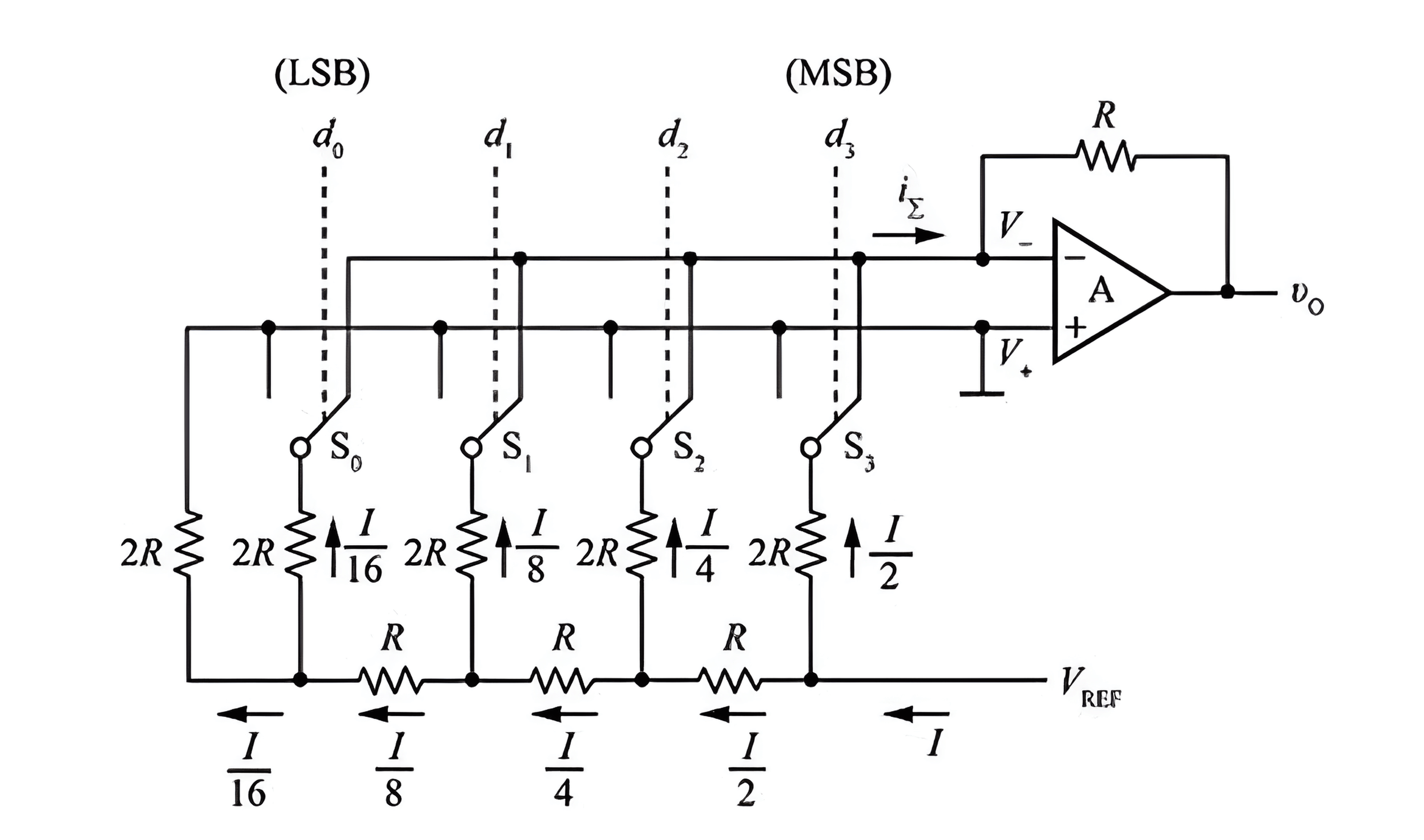

為了改善權電阻網絡 DAC 阻值相差太大的問題,可以采用倒 T 形電阻網絡 DAC,它只用了 R 和 2R 兩種阻值的電阻(所以也稱為 R2R DAC),對于控制精度有很大的幫助:

當求和放大器反饋電阻阻值為 R 時,輸出電壓:

可見,倒 T 形電阻網絡與權電阻網絡 DAC 的計算公式是相同的。

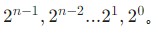

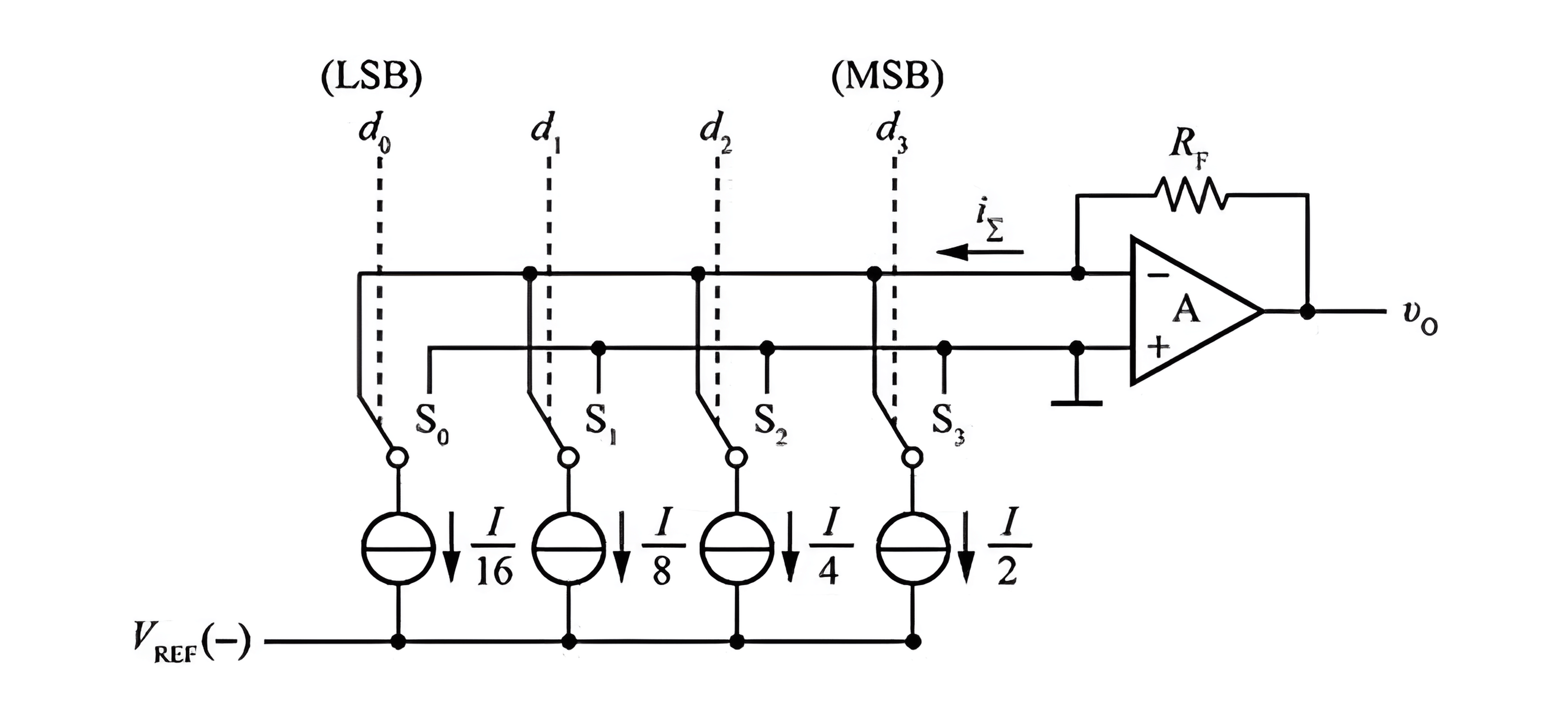

權電流型

在分析權電阻網絡與倒 T 形電阻網絡時,會將模擬開關當理想器件看待,但實際中它們存在一定的導通電阻和壓降,開關之間的一致性又有差別,所以會產生轉換誤差而影響精度。解決方法是采用權電流型 DAC,它有一組恒流源,每個恒流源電流大小依次為前一個的一半,與輸入二進制對應位的權成正比。采用恒流源使得每個支路電流大小不再受開關導通電阻和壓降的影響。

當輸入數字量的某位為 1 時,對應的開關將恒流源接至運算放大器的輸入端;當輸入代碼為 0 時,對應的開 關接地,故輸出電壓為:

DAC 主要參數

分辨率:最小輸出電壓(也就是輸入數字量為 1 時的電壓)與最大輸出電壓(也就是輸入數字量為最大,每一位都是 1 時的電壓)之比。一般通過輸入數字量的位數來表示。

轉換量程:DAC 能輸出的最大電壓,一般的關于參考電壓或其倍數。

建立時間:從輸入數字量到輸出模擬量之間的延時時間。

轉換精度:與 ADC 的轉換精度類似。

電子發燒友App

電子發燒友App

評論