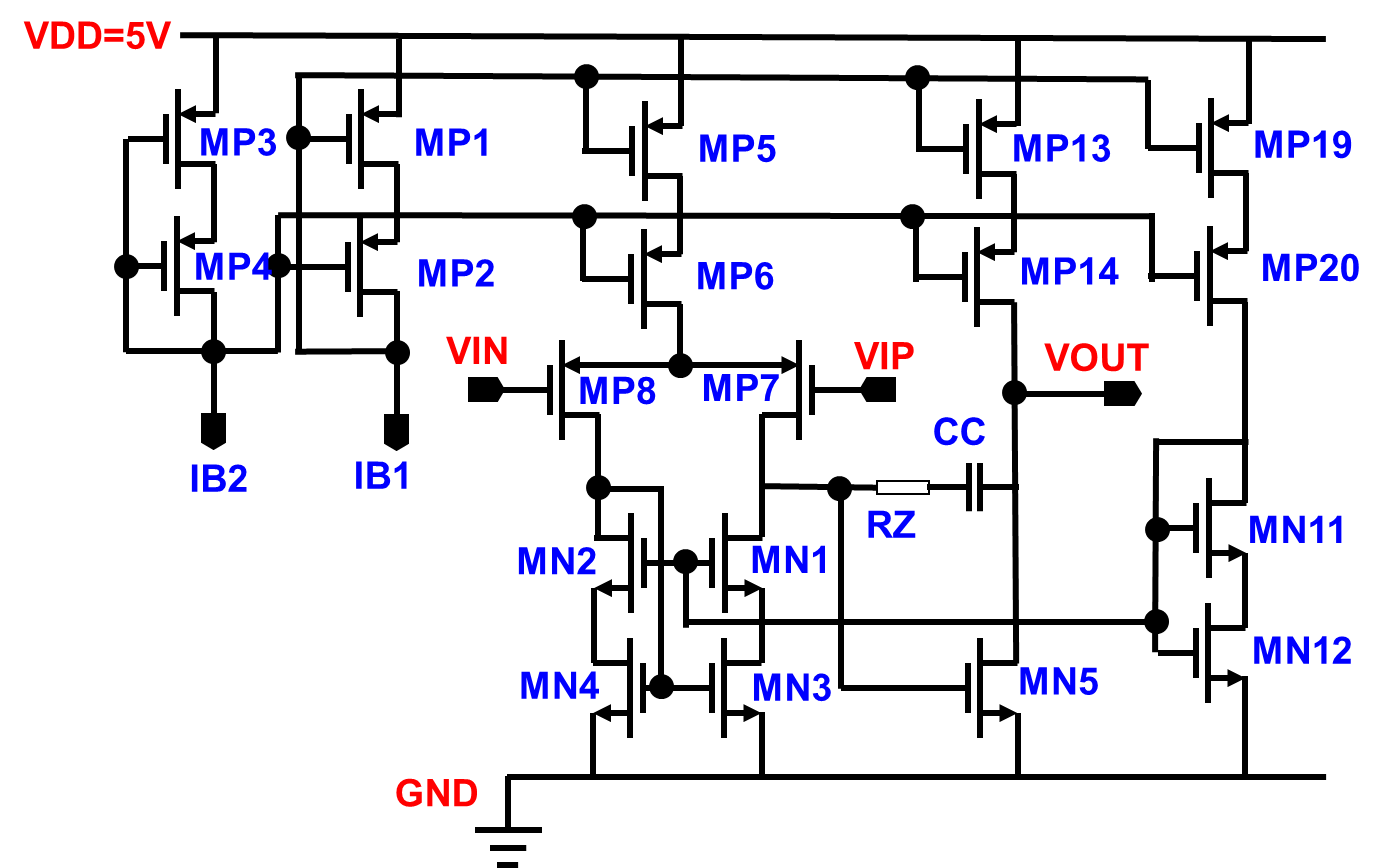

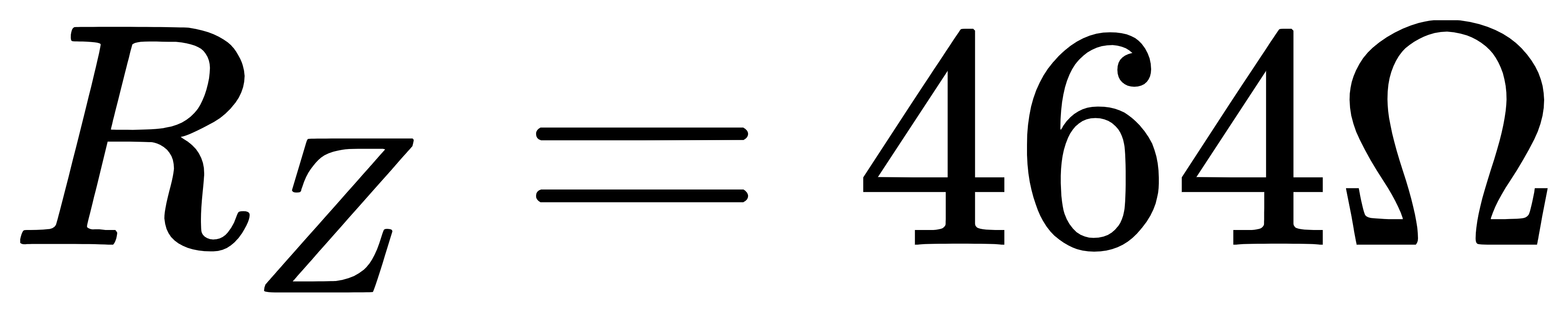

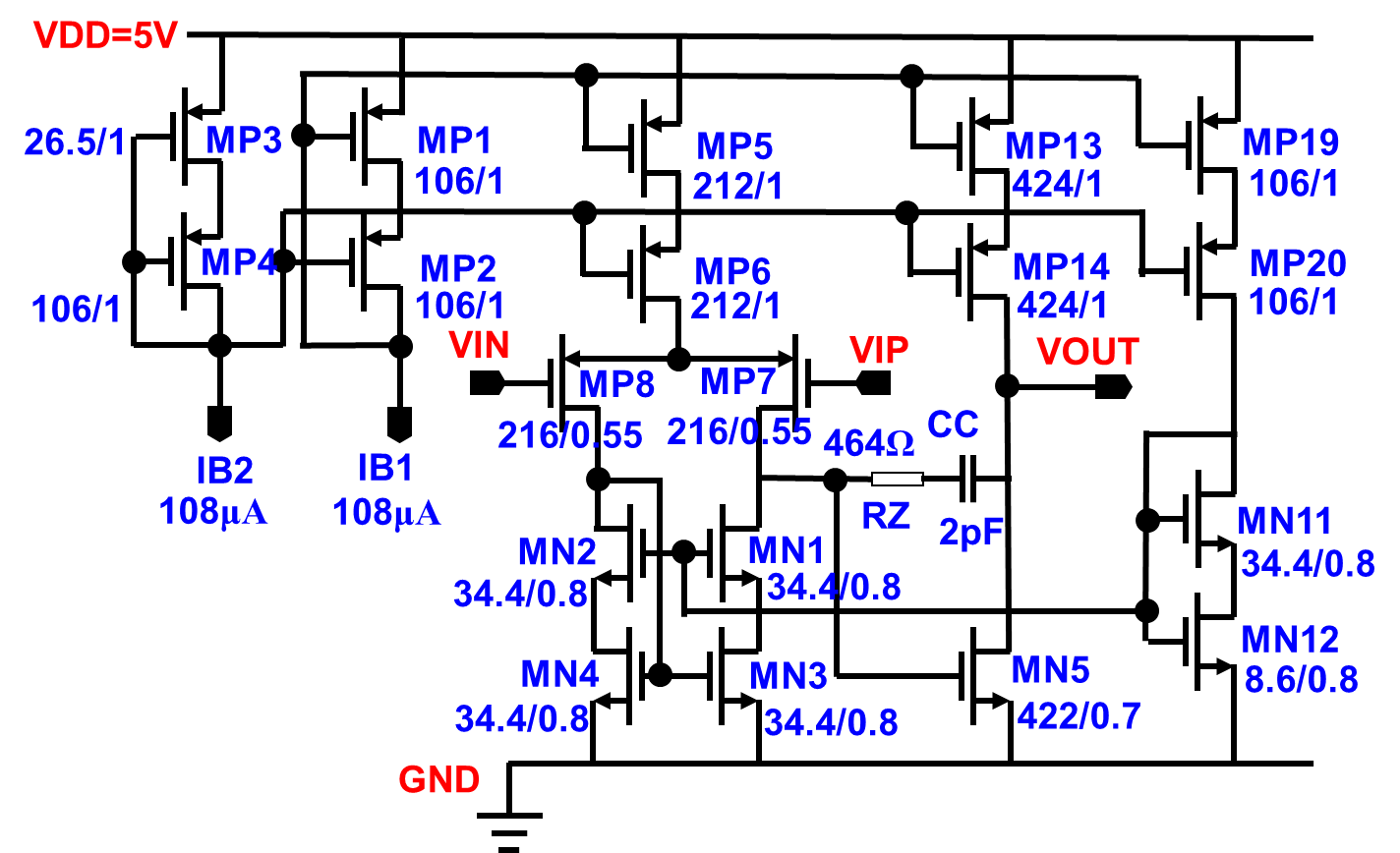

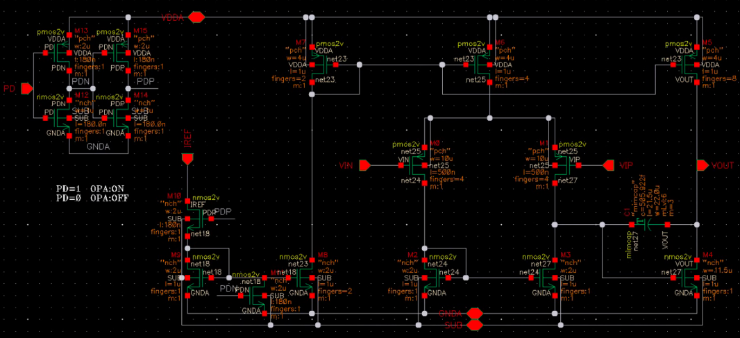

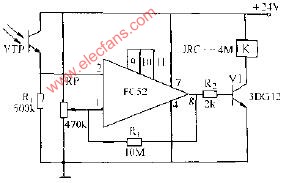

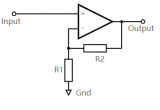

運(yùn)算放大器采用圖1所示的電路結(jié)構(gòu),電路中的電流源均采用共源共柵結(jié)構(gòu),可以獲得較高的共模抑制比和電流復(fù)制精度。 其性能指標(biāo)為增益帶寬積GBW=100MHz,負(fù)載電容CL=2pF。 本設(shè)計(jì)采用的工藝庫(kù)中NMOS的最小溝道長(zhǎng)度為0.5μm,PMOS的最小溝道長(zhǎng)度為0.55μm。

圖1 二級(jí)運(yùn)算放大器的電路結(jié)構(gòu)

2 設(shè)計(jì)過(guò)程

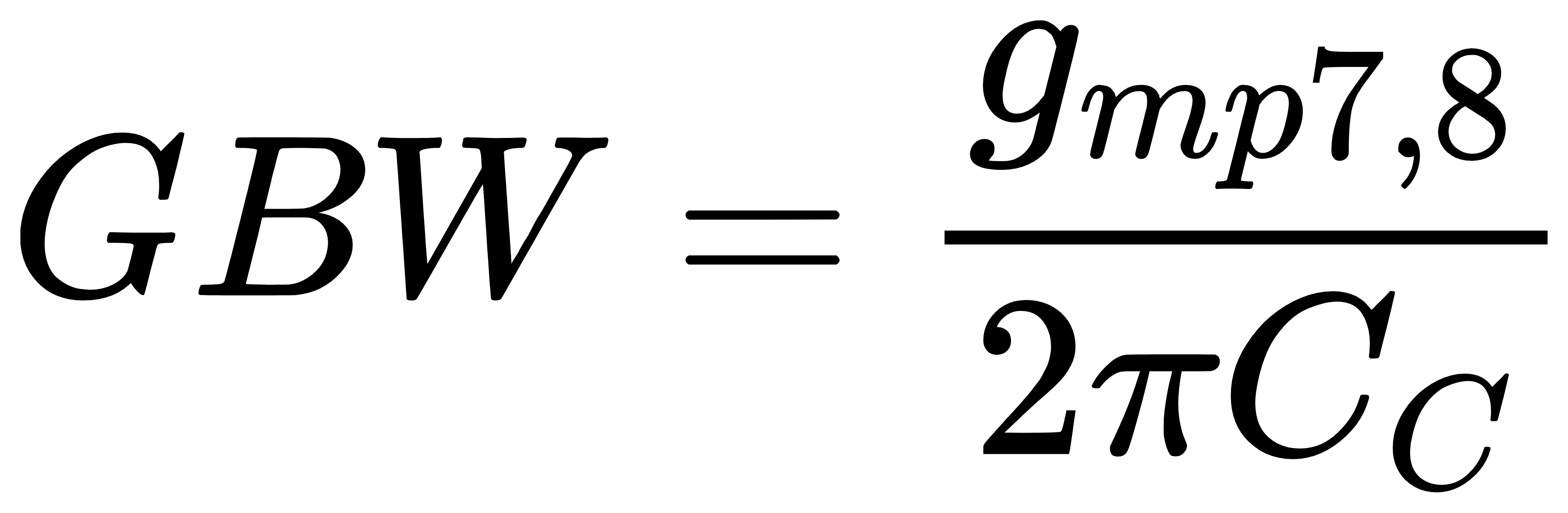

圖1所示的運(yùn)算放大器的增益帶寬積

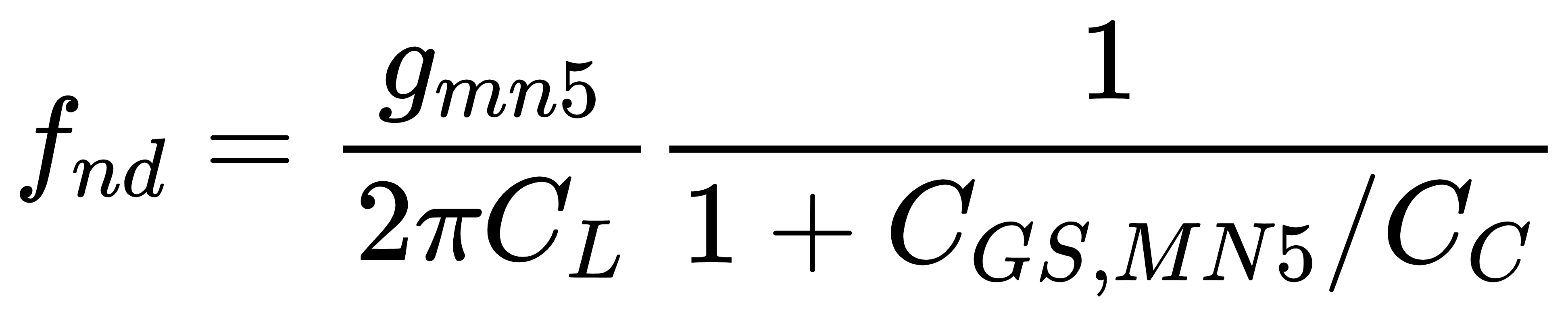

次主極點(diǎn)頻率

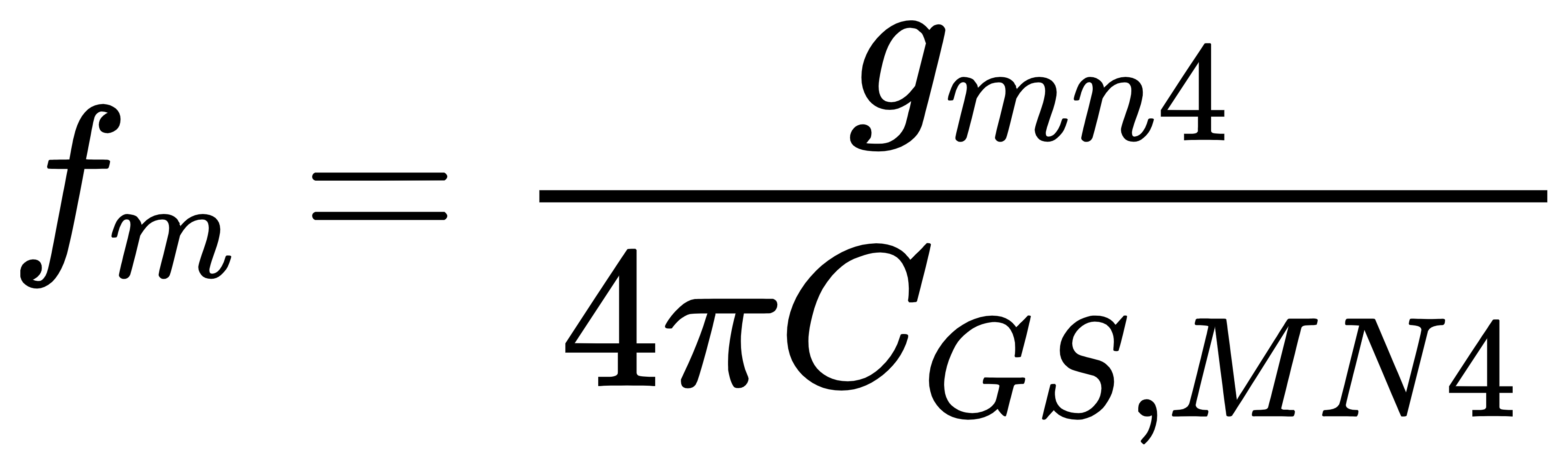

在第一級(jí)差分放大級(jí)的NMOS電流鏡負(fù)載處引入了零極點(diǎn)對(duì),極點(diǎn)頻率為

零點(diǎn)在左半平面,其頻率為2fm。

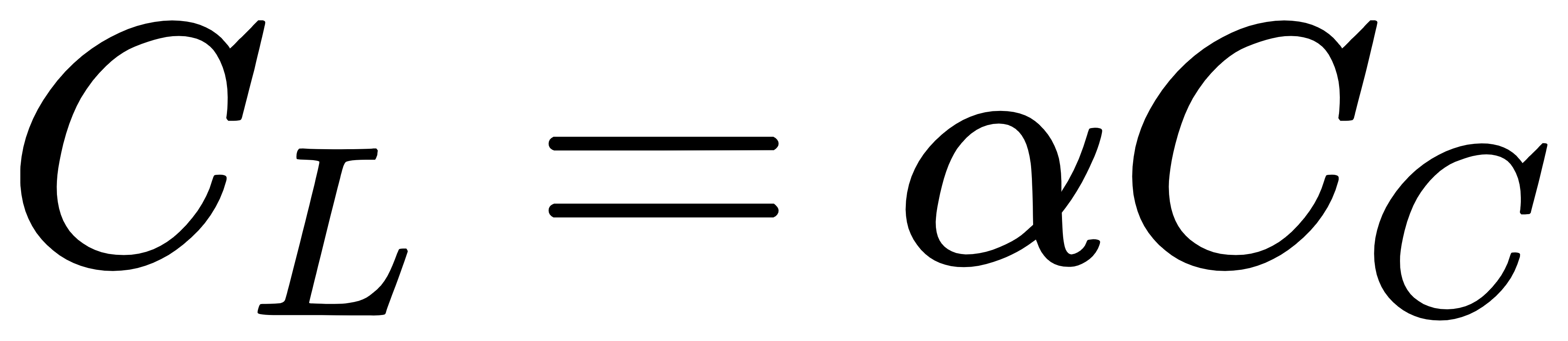

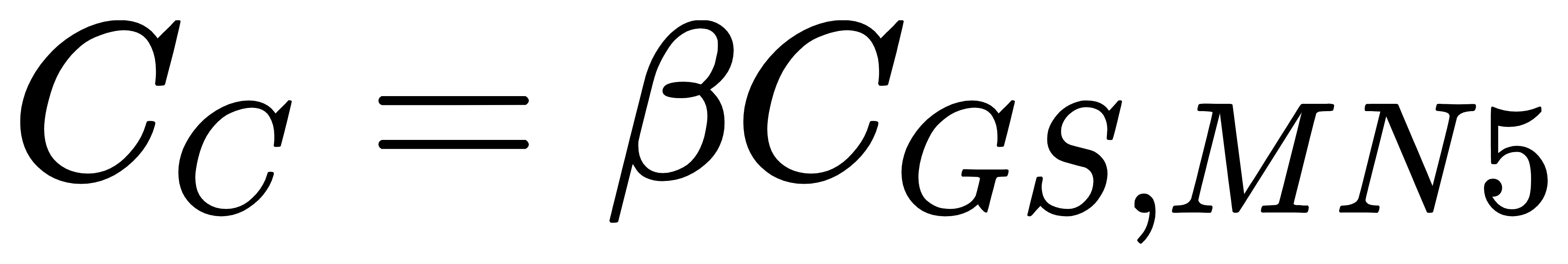

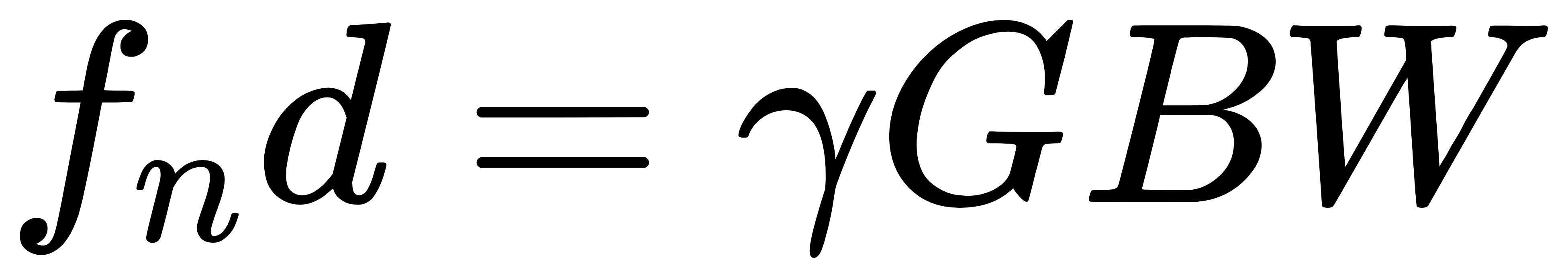

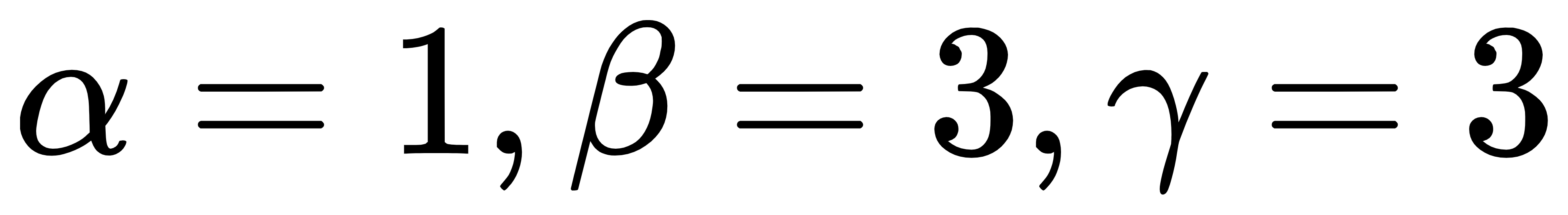

設(shè)有如下關(guān)系:

則可以取

2.1 確定MN5的L, W及ID

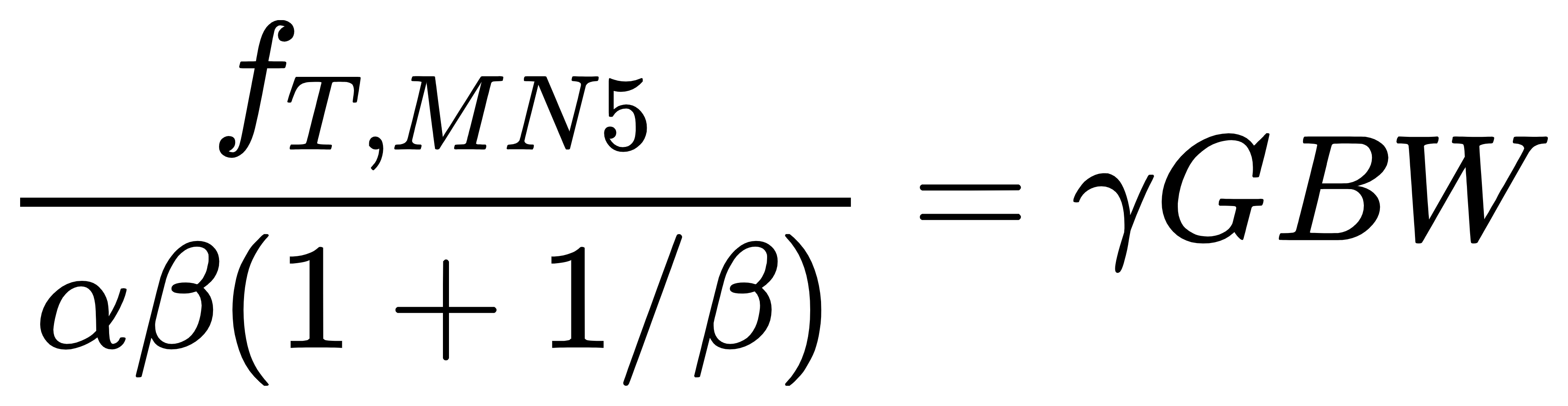

根據(jù)fnd的表達(dá)式和α、β、γ參數(shù)的定義可得

其中,fT,MN5為MN5晶體管的特征頻率。 代入數(shù)據(jù)可得

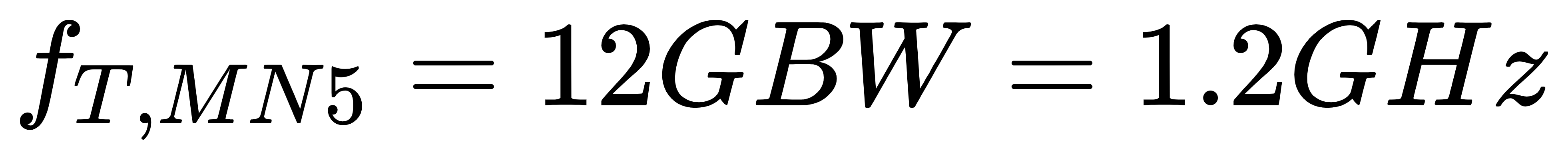

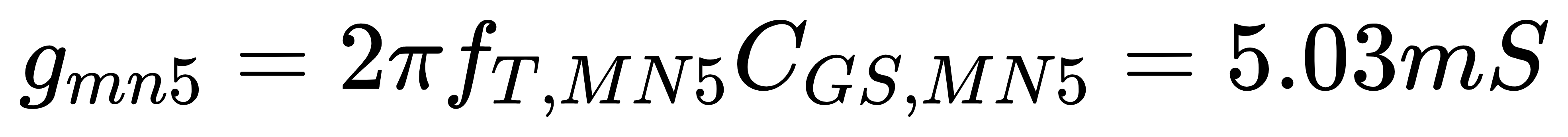

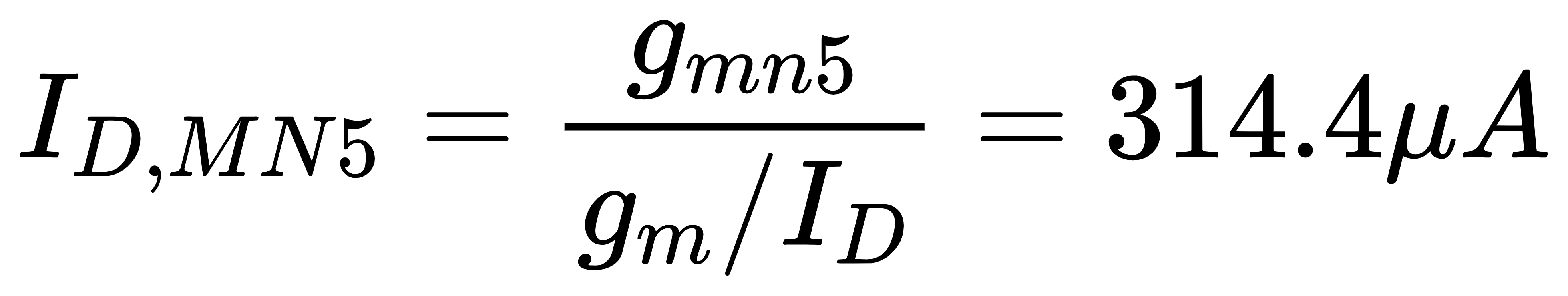

且有

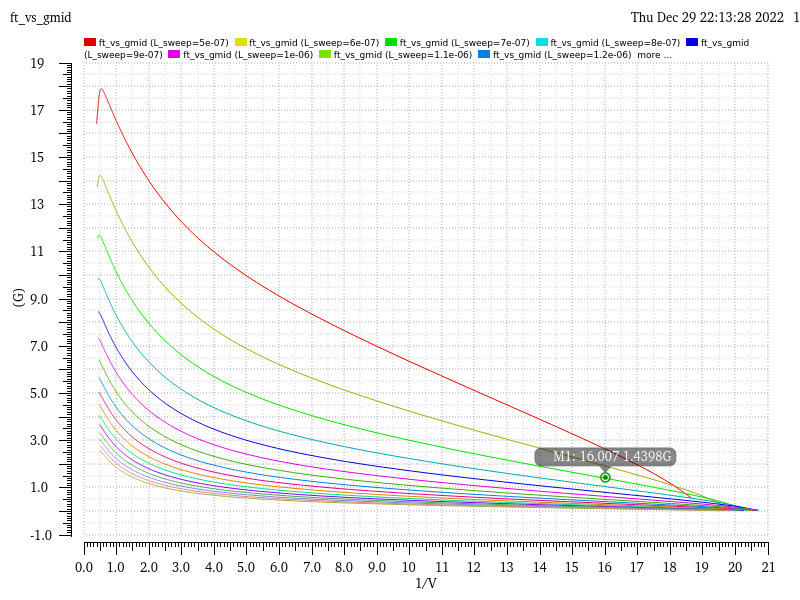

取gm/ID=16,可以得到

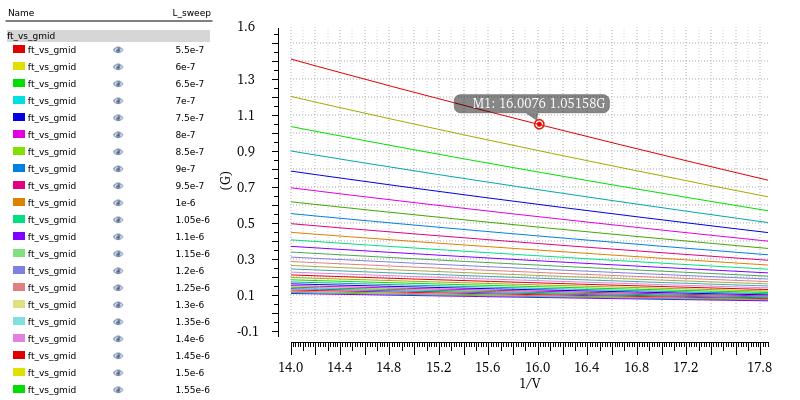

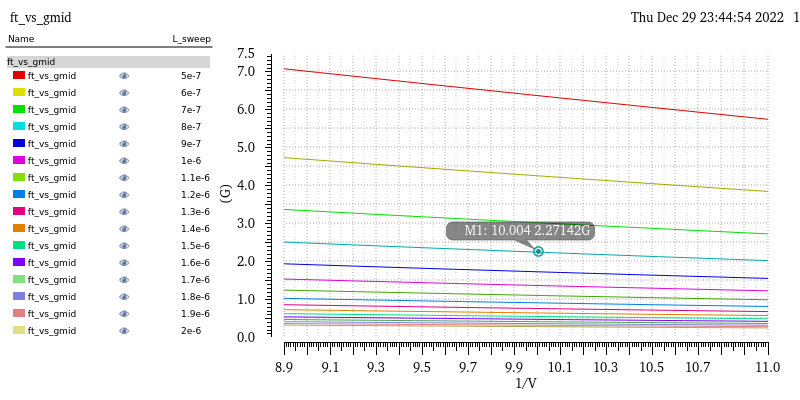

根據(jù)圖2所示的fT與gm/ID的關(guān)系曲線,可以得到MN5的溝道長(zhǎng)度為

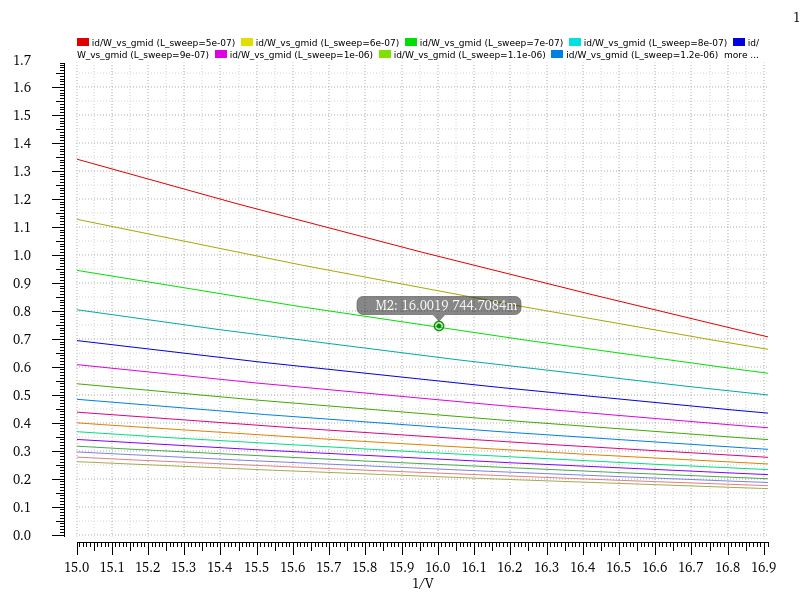

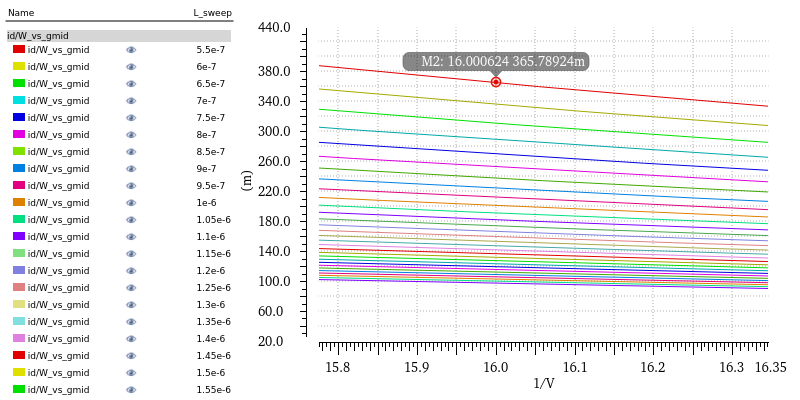

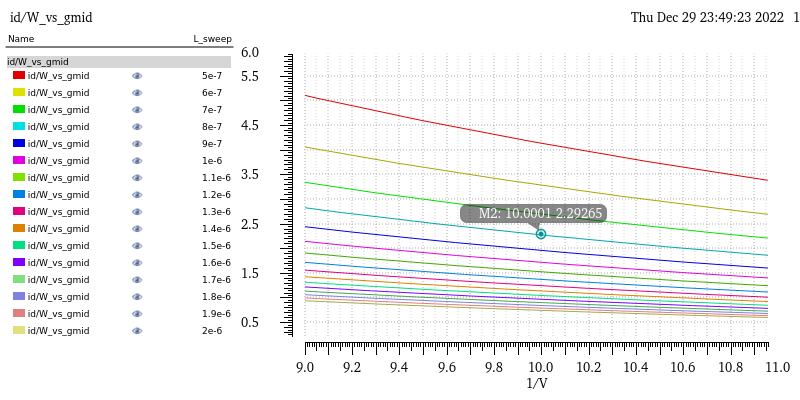

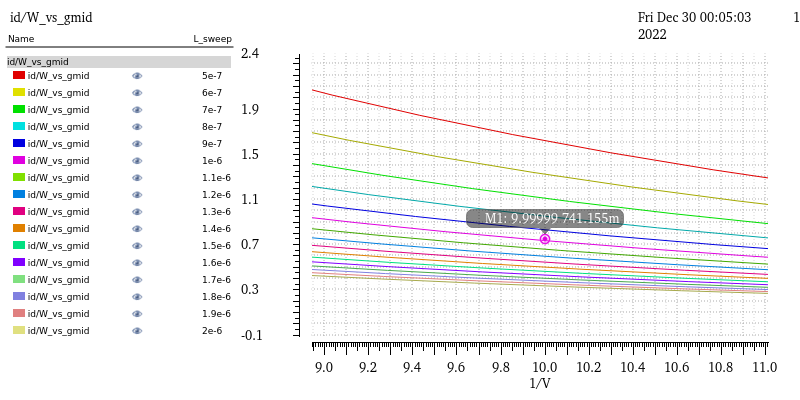

另外,根據(jù)圖3所示的ID/W與gm/ID的關(guān)系曲線,可以得到MN5的溝道寬度為

圖2 用于確定MN5溝道長(zhǎng)度的fT-gm/ID曲線

圖3 用于確定MN5溝道寬度的ID/W-gm/ID曲線

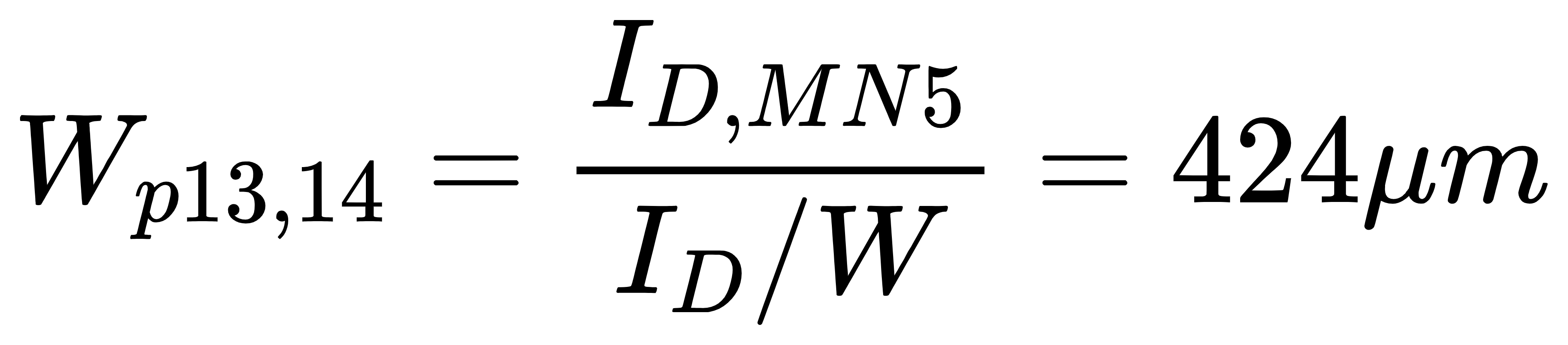

2.2 確定MP13和MP14的L及W

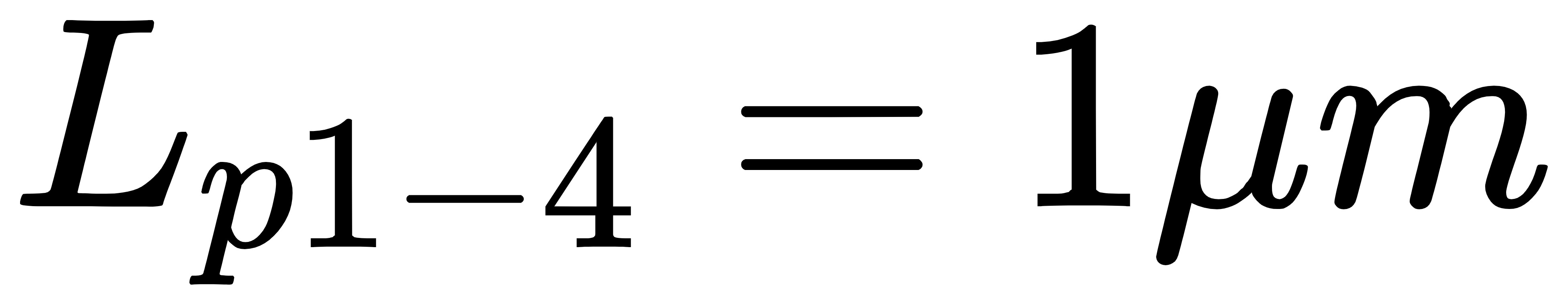

取所有PMOS電流源的gm/ID=10。 較小的gm/ID值有利于減小負(fù)載管的噪聲和減小閾值電壓失配引起的電流復(fù)制誤差。 電路對(duì)于MP13和MP14的溝道長(zhǎng)度沒有嚴(yán)格的約束條件,可以選擇溝道長(zhǎng)度

根據(jù)圖4所示的ID/W與gm/ID的關(guān)系曲線,可以得到

圖4 用于確定MP13和MP14溝道寬度的ID/W-gm/ID曲線

2.3 確定MP7和MP8的L, W及ID

由GBW的表達(dá)式可以計(jì)算出MP7和MP8的跨導(dǎo)為

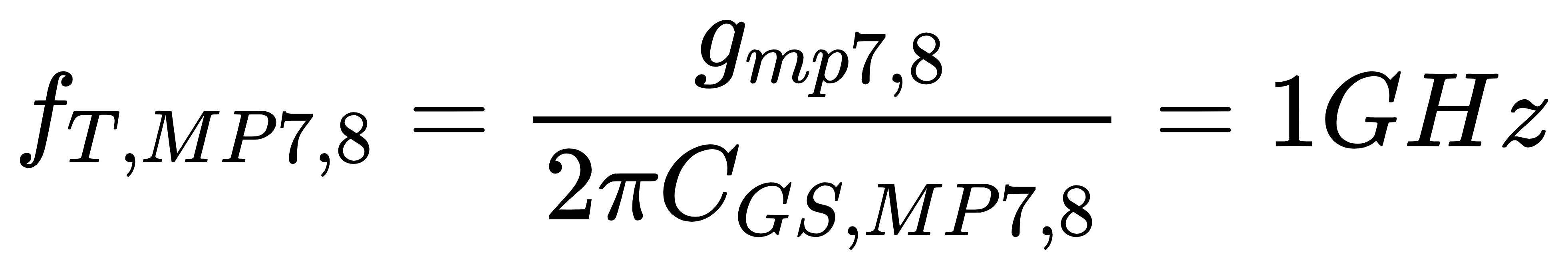

在運(yùn)算放大器的單位負(fù)反饋應(yīng)用中,由于輸出端與反相輸入端直接相連,使得CGS,MP8與CL并聯(lián),導(dǎo)致等效負(fù)載電容CL’=CL+CGS,MP8增大,增益帶寬積和相位裕度減小。 為了減小CGS,MP8的影響,可以通過(guò)設(shè)計(jì)使得CGS,MP8<0.1CL。 取CGS,MP8=0.2pF,可以計(jì)算出MP7和MP8的特征頻率為

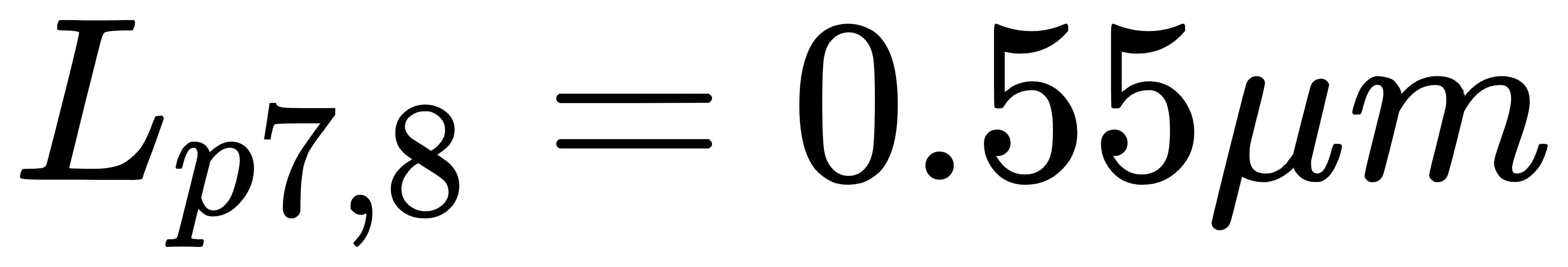

取gm/ID=16,則根據(jù)圖5所示的fT與gm/ID的關(guān)系曲線,可以得到MP7和MP8的溝道長(zhǎng)度為

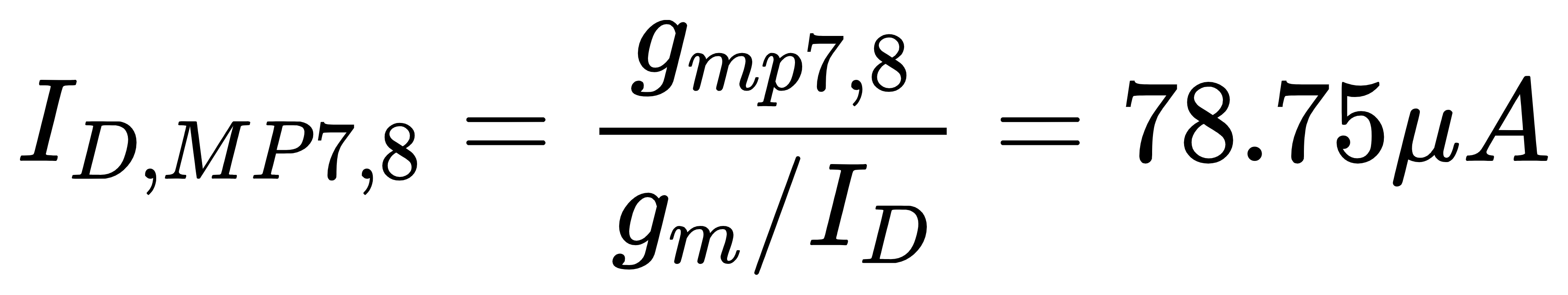

通過(guò)MP7和MP8的電流均為

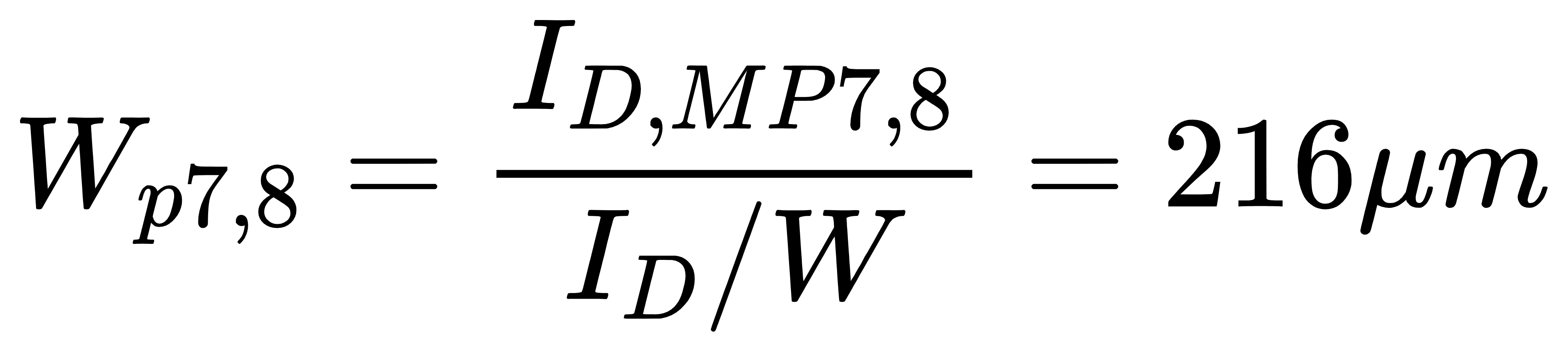

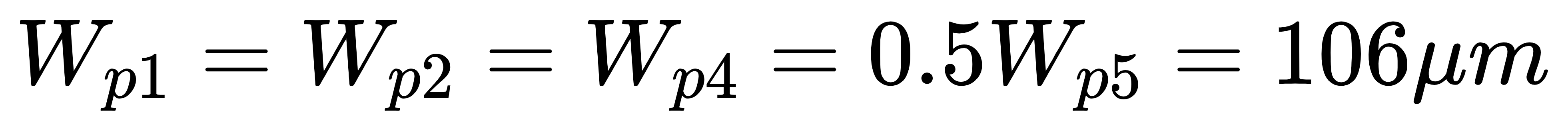

根據(jù)圖6所示的ID/W與gm/ID的關(guān)系曲線,可以得到MP7和MP8的溝道寬度為

圖5 用于確定MP7和MP8溝道長(zhǎng)度的fT-gm/ID曲線

圖6 用于確定MP7和MP8溝道寬度的ID/W-gm/ID曲線

2.4 確定MN1~MN4的L及W

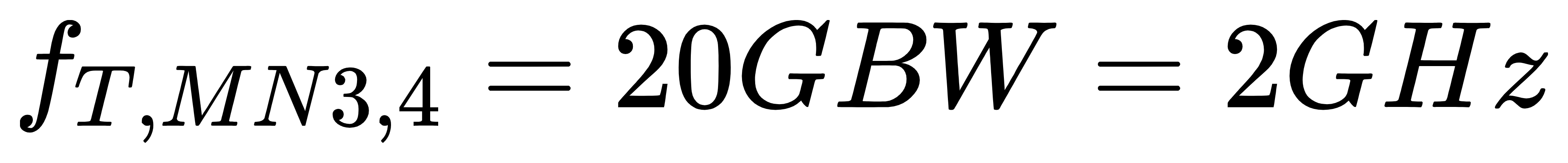

為了減小鏡像零極點(diǎn)對(duì)對(duì)于運(yùn)算放大器相位裕度的影響,可以將鏡像極點(diǎn)頻率設(shè)置到GBW的10倍處,即fm=10GBW。 據(jù)此,有

取gm/ID=10,根據(jù)圖7所示的fT與gm/ID的關(guān)系曲線,可以得到MN3和MN4的溝道長(zhǎng)度為

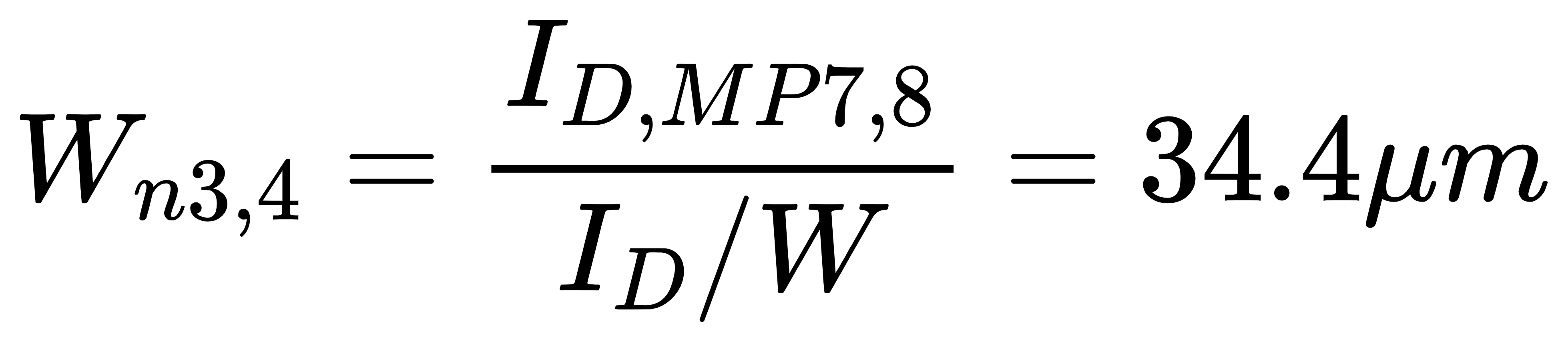

根據(jù)圖8所示的ID/W與gm/ID的關(guān)系曲線,可以得到MN3和MN4的溝道寬度為

MN1和MN2的溝道長(zhǎng)度和溝道寬度與MN3和MN4取相同值即可。

圖7 用于確定MN3和MN4溝道長(zhǎng)度的fT-gm/ID曲線

圖8 用于確定MN3和MN4溝道寬度的ID/W-gm/ID曲線

2.5 確定MP5和MP6的L及W

MP5, 6的溝道長(zhǎng)度取與MP13, 14相同的值,即

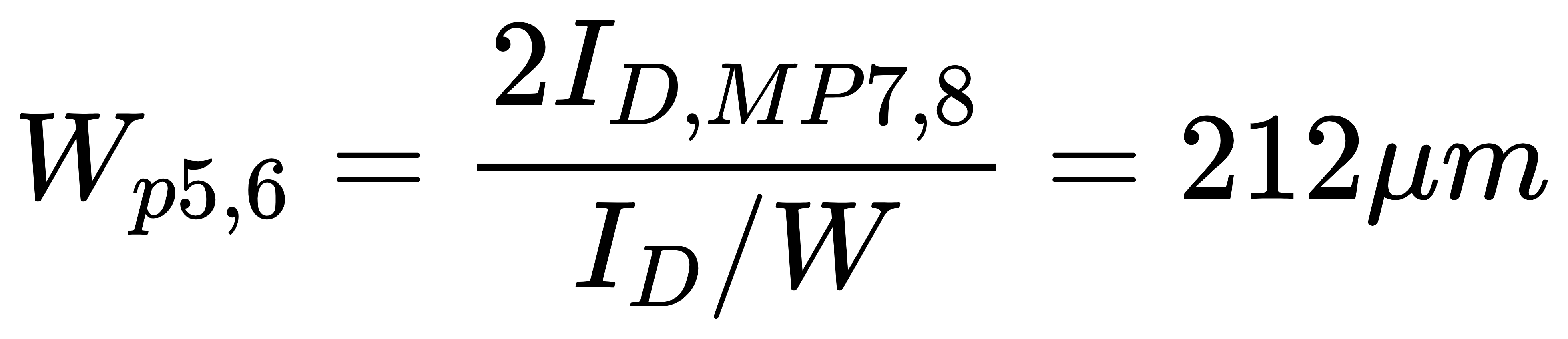

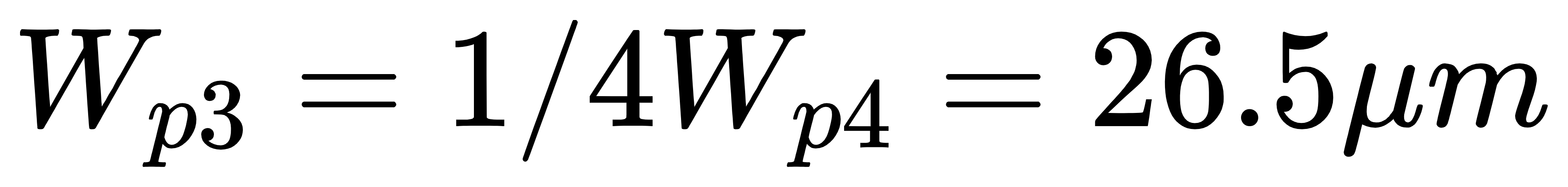

根據(jù)圖9所示的ID/W與gm/ID的關(guān)系曲線,可以得到MP5和MP6的溝道寬度為

圖9 用于確定MP5和MP6溝道寬度的ID/W-gm/ID曲線

2.6 確定偏置電路晶體管的尺寸

第一級(jí)差分對(duì)的尾電流源大小為ID,MP5=157.5μA,第二級(jí)的負(fù)載電流源大小為ID,MP13=314.4μA。 取IB1=IB2=78.75μA,則ID,MP5=2

IB1,ID,MP13=4 IB1。 因此可以確定MP1~4的尺寸為

取ID,MP19=ID,MP7,8=0.5 ID,MP5=IB1,因此

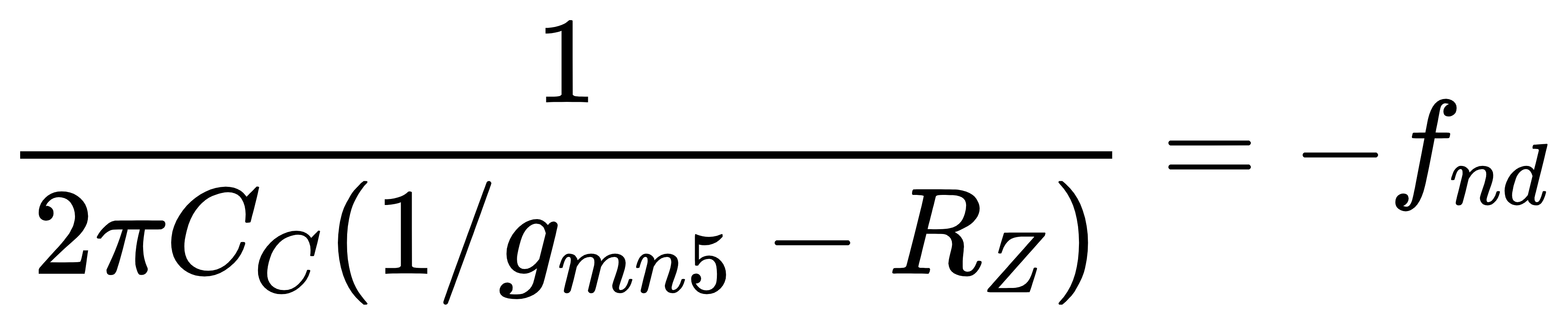

2.7 確定消零電阻RZ的大小

為了使消零電阻RZ可以將補(bǔ)償電容CC引入的右半平面零點(diǎn)移動(dòng)到左半平面,并且最好能夠和次主極點(diǎn)相抵消,則有

代入數(shù)據(jù)可得

3 電路仿真

3.1 增益帶寬積與相位裕度

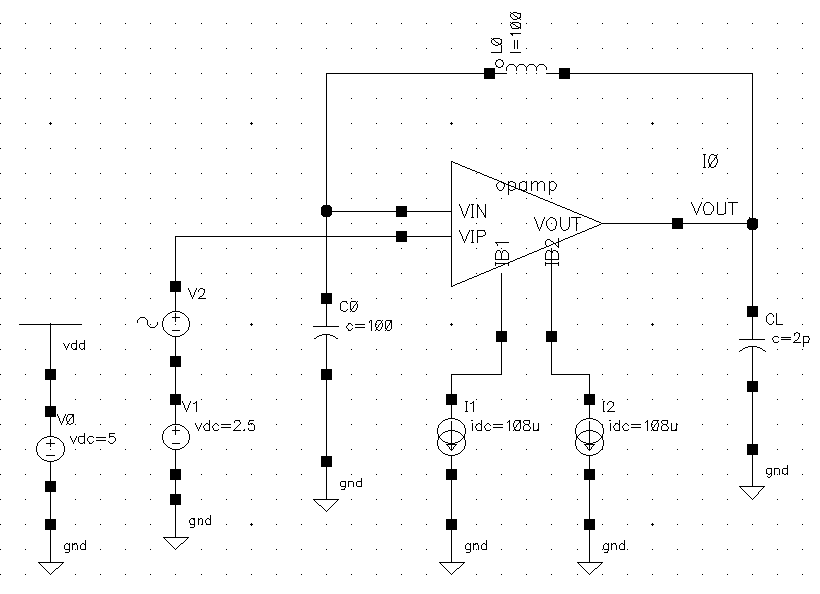

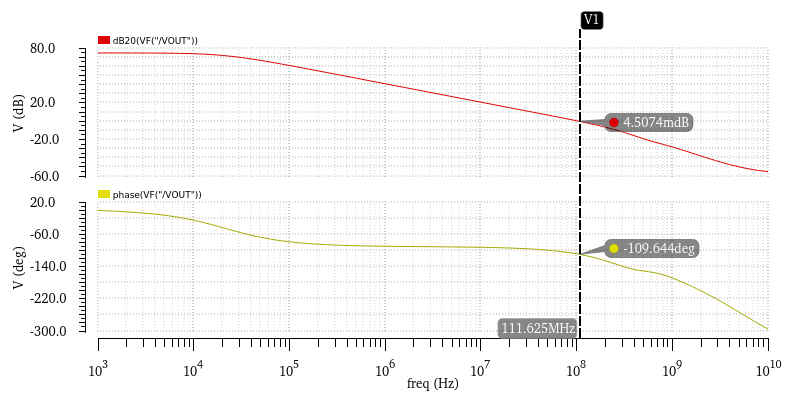

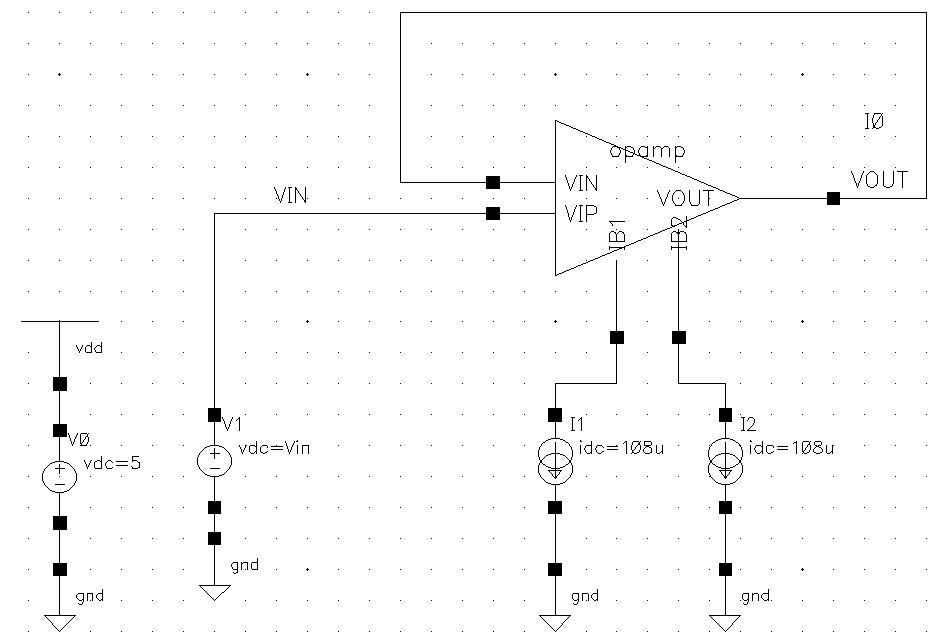

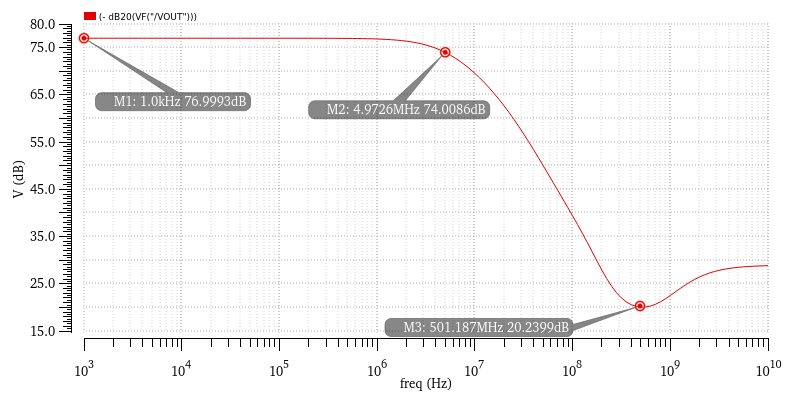

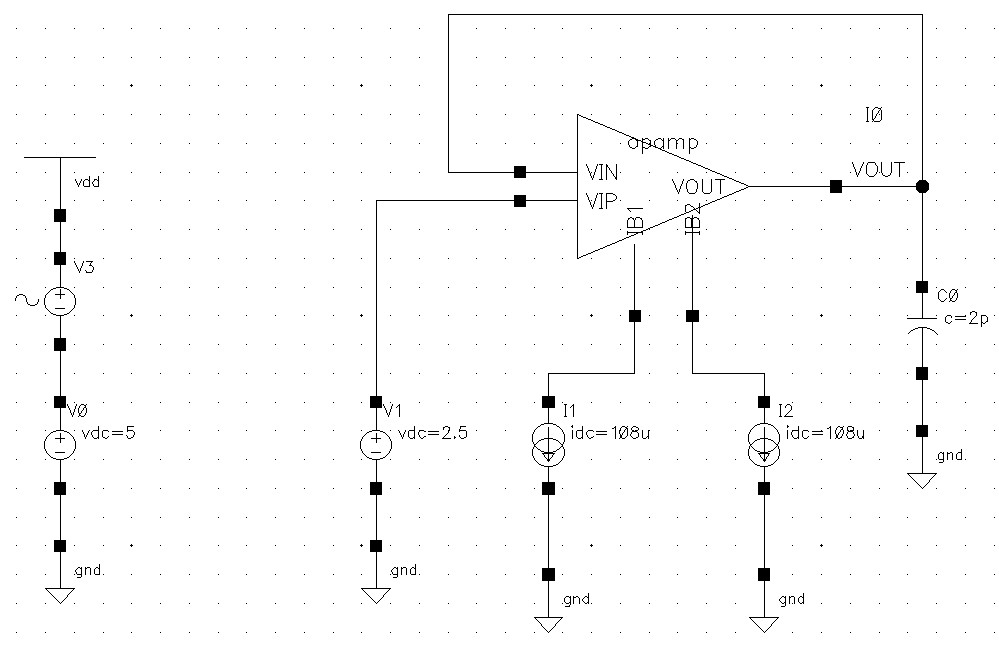

用于仿真GBW和PM的電路如圖10所示,其中的運(yùn)算放大器采用前文所設(shè)計(jì)的運(yùn)算放大器,對(duì)其施加共模電壓2.5V作為輸入端的靜態(tài)工作點(diǎn)電壓,負(fù)載電容CL=2pF。 經(jīng)過(guò)仿真,發(fā)現(xiàn)GBW只有82MHz,沒有達(dá)到100MHz。 為此,將IB1和IB2提高至108μA。 仿真結(jié)果如圖11所示,可以看出仿真結(jié)果為GBW=112MHz,PM=70?,低頻增益為75dB。

圖10 用于仿真GBW和PM的電路圖

圖11 GBW和PM的仿真結(jié)果

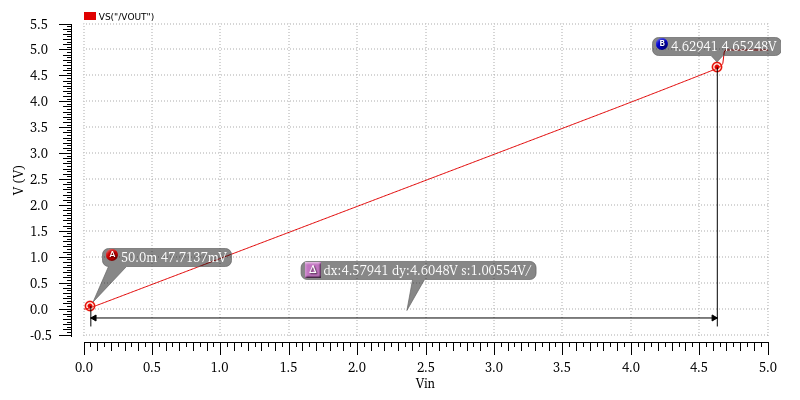

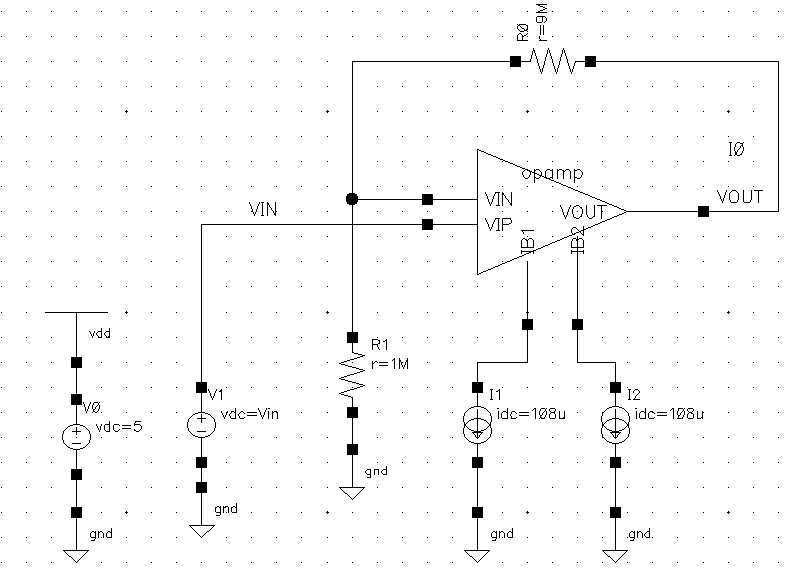

3.2 共模輸入范圍

用于仿真共模輸入范圍的電路圖如圖12所示。 共模輸入范圍的仿真結(jié)果如圖13所示,可以看出共模輸入范圍為0.05V至4.63V。 電壓跟隨器連接方式的運(yùn)算放大器在此范圍內(nèi)可以展現(xiàn)出很好的電壓跟隨特性,其電壓傳輸特性曲線的斜率為1。

圖12 用于仿真共模輸入范圍的電路圖

圖13 共模輸入范圍的仿真結(jié)果

3.3 輸出擺幅

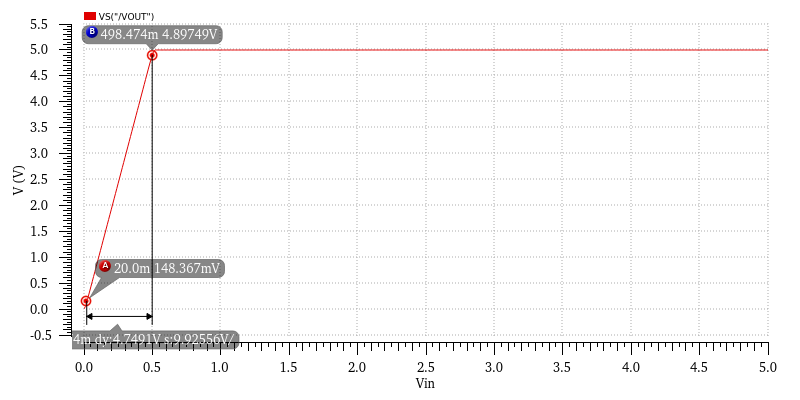

用于仿真輸出擺幅的電路如圖14所示。 在單位增益反饋結(jié)構(gòu)中,電壓傳輸曲線的線性受到共模輸入范圍的限制。 因此,若采用高增益反饋,傳輸曲線的線性部分與放大器輸出電壓擺幅一致。 圖14采用增益為10的同相放大器。 輸出擺幅的仿真結(jié)果如圖15所示,可以看出輸出電壓擺幅為0.15V至4.9V。

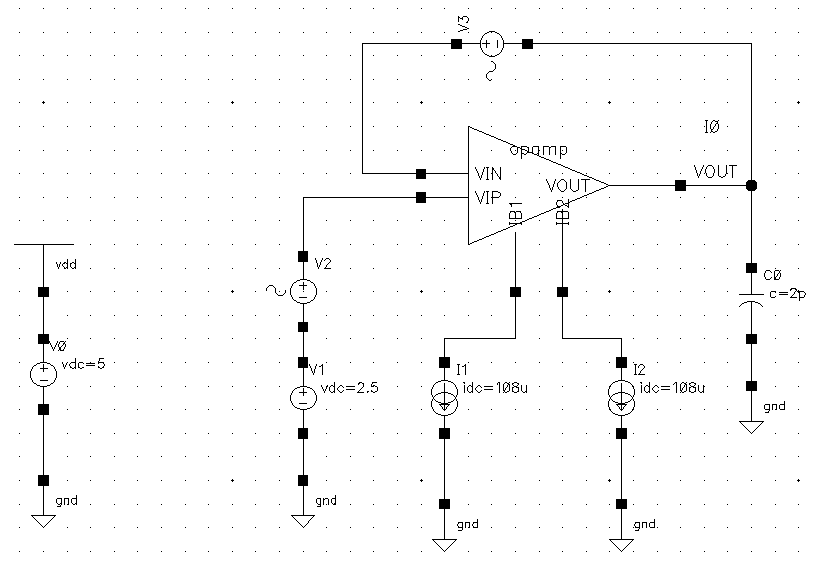

圖14 用于仿真輸出擺幅的電路圖

圖15 輸出擺幅的仿真結(jié)果

3.4 共模抑制比

用于仿真共模抑制比的電路如圖16所示。 仿真結(jié)果如圖17所示,可以看出低頻時(shí)的CMRR=77dB; 在5MHz處CMRR下降3dB; 在1kHz至10GHz頻段內(nèi),CMRR最小為20dB。

圖16 用于仿真共模抑制比的電路圖

圖17 共模抑制比的仿真結(jié)果

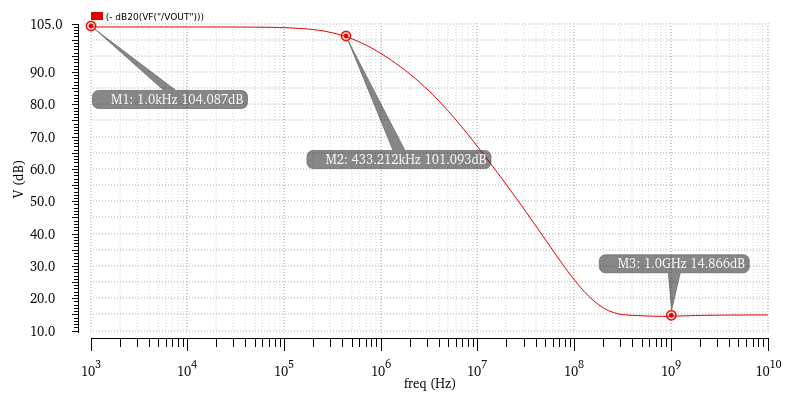

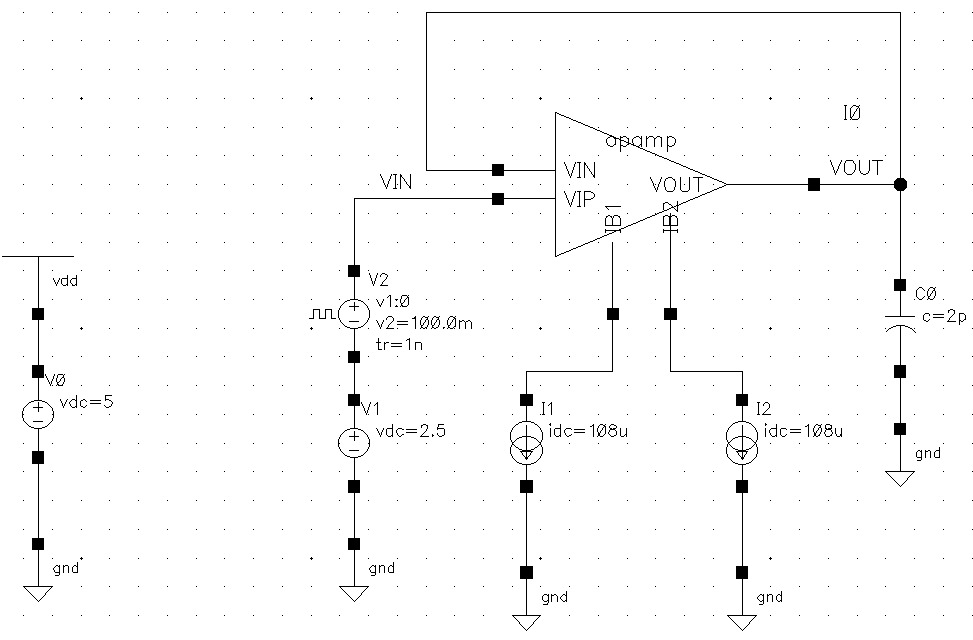

3.5 電源抑制比

用于仿真電源抑制比的電路如圖18所示,在電源線上引入小信號(hào)電壓波動(dòng)。 電源抑制比的仿真結(jié)果如圖19所示,可以看出,低頻下的PSRR=104dB; 在433kHz處,PSRR下降3dB; 在1kHz至10GHz頻段內(nèi),PSRR最小為15dB。

圖18 用于仿真電源抑制比的電路圖

圖19 電源抑制比的仿真結(jié)果

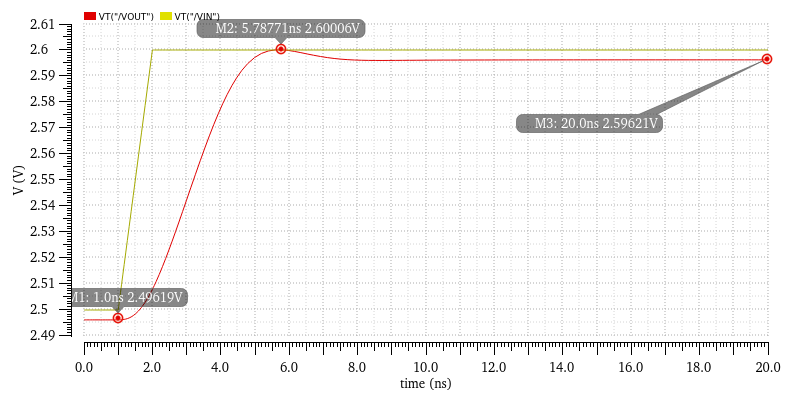

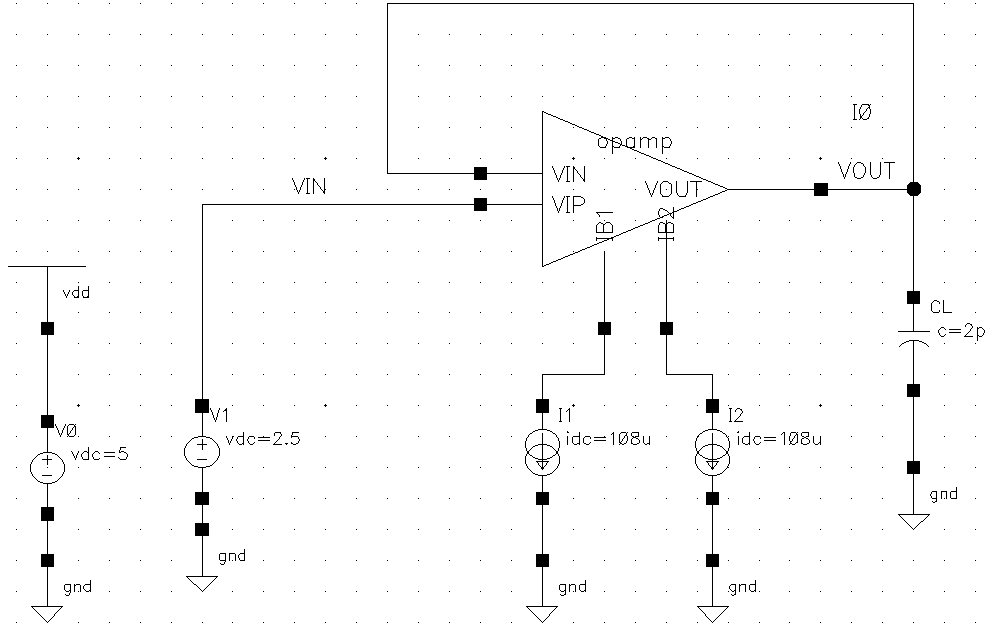

3.6 小信號(hào)建立特性

用于小信號(hào)建立特性仿真的電路圖如圖20所示,在輸入端施加0.1V的階躍小信號(hào)電壓。 小信號(hào)建立特性的仿真結(jié)果如圖21所示。 在圖21中,黃色曲線為輸入電壓的波形,紅色曲線為輸出電壓的波形。 從圖21可以看出,峰值時(shí)間tp=5.8ns?1ns=4.8ns,最大超調(diào)σp=(2.600V?2.596V)/2.596V=0.15%,振蕩次數(shù)N=1。

圖20 用于仿真小信號(hào)建立特性的電路圖

圖21 小信號(hào)建立特性的仿真結(jié)果

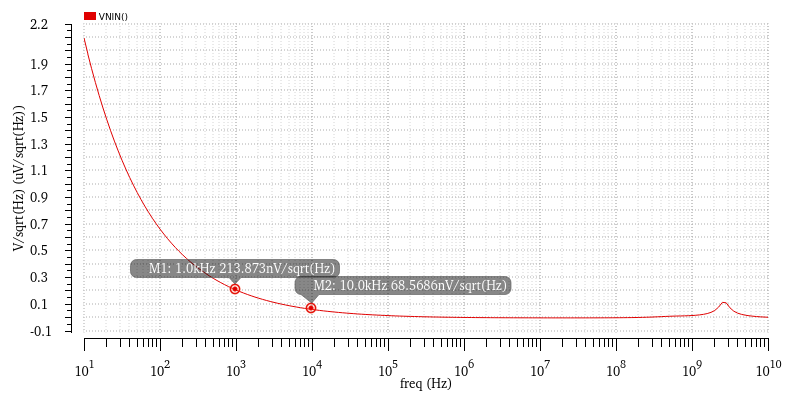

3.7 等效輸入噪聲

由于所設(shè)計(jì)的運(yùn)算放大器輸入端均為柵極,其輸入電阻為無(wú)窮大,因此可以只考慮等效輸入噪聲電壓,而忽略等效輸入噪聲電流。 用于仿真等效輸入噪聲的電路圖如圖22所示。 仿真結(jié)果如圖23所示,可以看出,在1kHz處,等效輸入噪聲電壓大小為214nV/√Hz; 在10kHz處,等效輸入噪聲電壓大小為68nV/√Hz。

圖22 用于仿真等效輸入噪聲的電路圖

圖23 等效輸入噪聲電壓的仿真結(jié)果

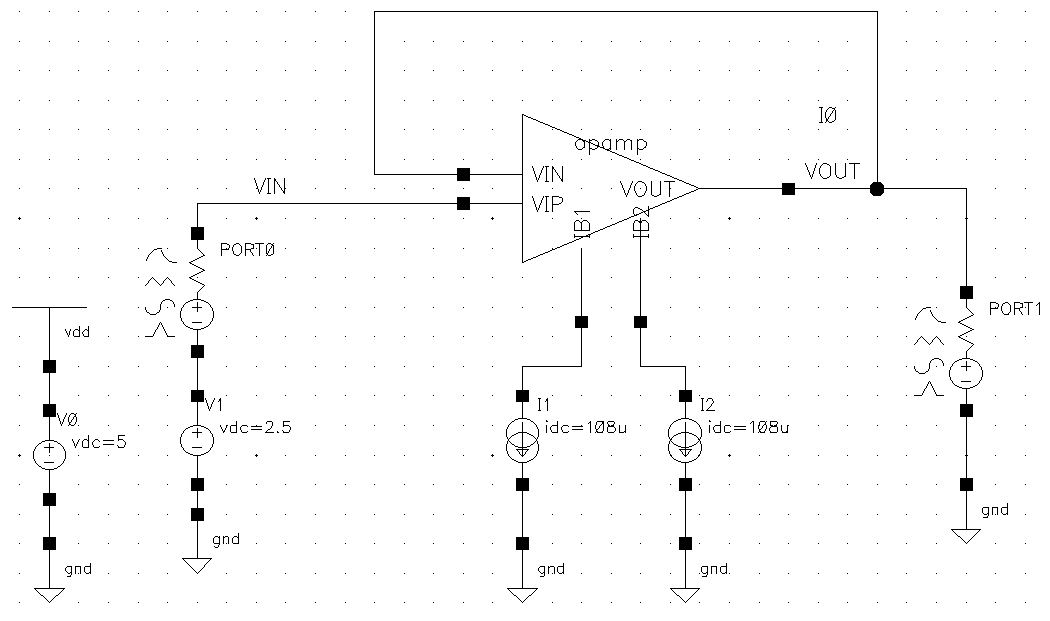

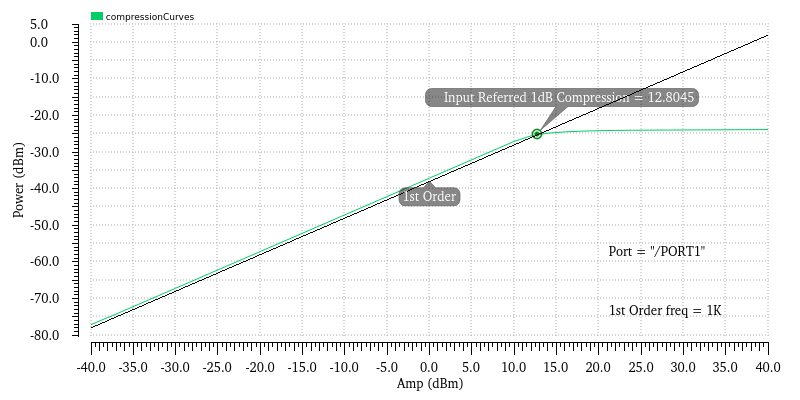

3.8 非線性

有許多性能指標(biāo)可以反應(yīng)電路的非線性,在這里選擇輸入1dB壓縮點(diǎn)作為衡量非線性的指標(biāo)。 用于仿真輸入1dB壓縮點(diǎn)的電路如圖24所示,為單位增益負(fù)反饋結(jié)構(gòu),其中輸入端口PORT0的頻率設(shè)為1kHz,源阻抗設(shè)為50Ω,產(chǎn)生正弦波信號(hào); 輸出端口PORT1的阻抗設(shè)為1MΩ。 仿真結(jié)果如圖25所示,可以看出輸入1dB壓縮點(diǎn)為+12.8dBm。

圖24 用于輸入1dB壓縮點(diǎn)的電路圖

圖25 輸入1dB壓縮點(diǎn)的仿真結(jié)果

4 電路參數(shù)匯總

將第2節(jié)中計(jì)算所得的電路參數(shù),以及在3.1節(jié)中調(diào)整的偏置電流IB1和IB2匯總到圖26中。

圖26 電路最終版本

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論