1.1 概述

ADC(Anlog to DigtialConverter, 模數轉換器), 用于實現模擬信號向數字信號的轉換。自然界中的聲光電等都是模擬信號,我們這里說的主要是電信號。而計算機系統只能處理二進制0和1這種信號,不能直接處理模擬信號,因此需要ADC將模擬信號轉換為數字信號,然后進一步處理。ADC是模數之間的橋梁。

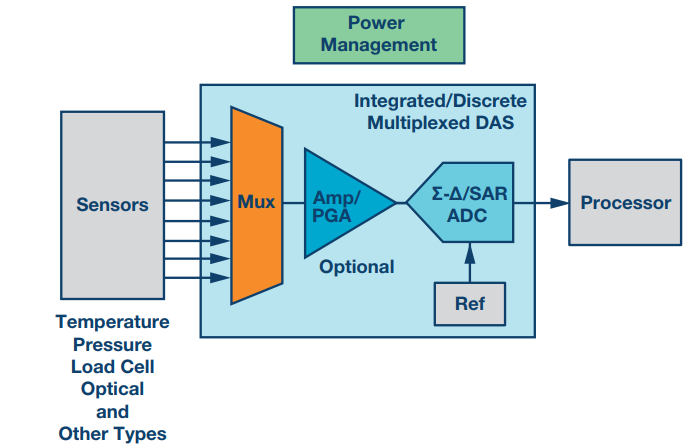

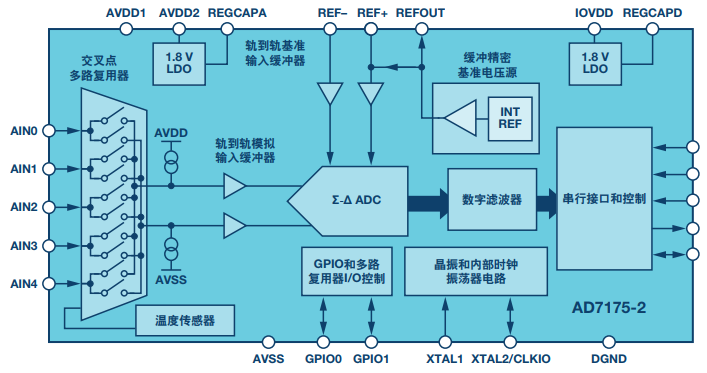

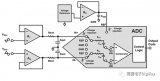

如上圖是一個典型多路復用數據采集系統,在這個系統中,可使用多個傳感器(Sensors)采集信號,并將多個輸入通道掃描至單個ADC中。ADC對傳感器采集的模擬信號進行模數轉換,將轉換結果數字信號通過串口(常見的一般是SPI、IIC等接口)送給處理器(Processor)使用,這就是一個典型的ADC使用場景。當然,在某些情況下,可使用在復用器(Mux)和ADC之間的緩沖器或可編程增益放大器對信號進行預處理,然后交由ADC處理。

1.2 ADC基礎知識

主要介紹ADC分類,使用場景及AD轉換基本原理。

1.2.1 分類

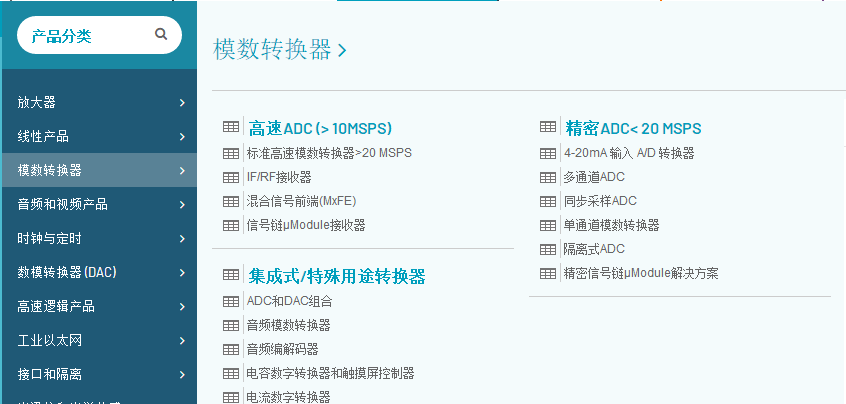

ADC的種類很多,按照不同的分類方法,可分為不同的類型。按照使用場景分,可以分為高速ADC、精密ADC、集成式/特殊用途ADC。

按轉換實現的方法分,有逐次逼近型(SAR)、Σ-Δ型、積分型、壓控變換型、流水線型等。

1.2.2 不同ADC的應用場景

逐次逼近型(SAR)、積分型、壓控變換型等主要用在中低速、中等精度數據采集中。分級型和流水線型主要用于處理高速瞬態信號、快速波形存儲與記錄、高速數據采集、視頻信號量化及高速數字通訊技術等領域。Σ-Δ型ADC主要應用于高精度數據采用的系統,多用于測量領域。芯海科技ADC就是此種類型,可用于于體重秤、嚴控芯片等場景。

1.2.3 ADC轉換的過程

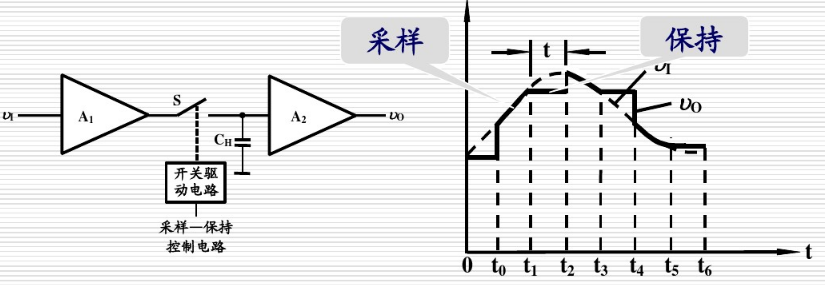

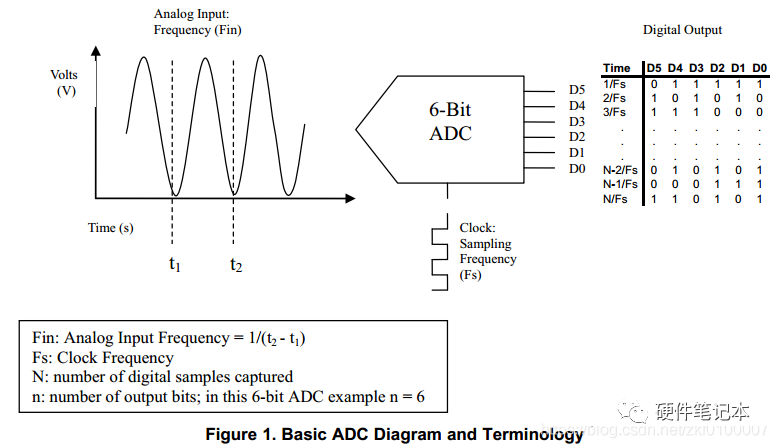

ADC采樣過程分為4步,即采樣、保持、量化和編碼。

采樣,將隨時間連續變化的模擬信號轉化為在時間t上離散的模擬量,采樣需滿足采樣定理(奈奎斯特定理)。保持,模數轉換都會消耗一定的時間,為了給后續的量化編碼提供一個穩定的值,在采樣電路后要求將所采樣的模擬信號保持一段時間(模擬上通過電容實現)。

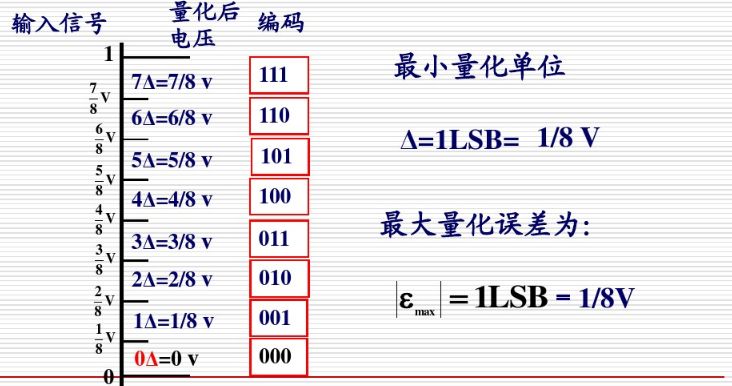

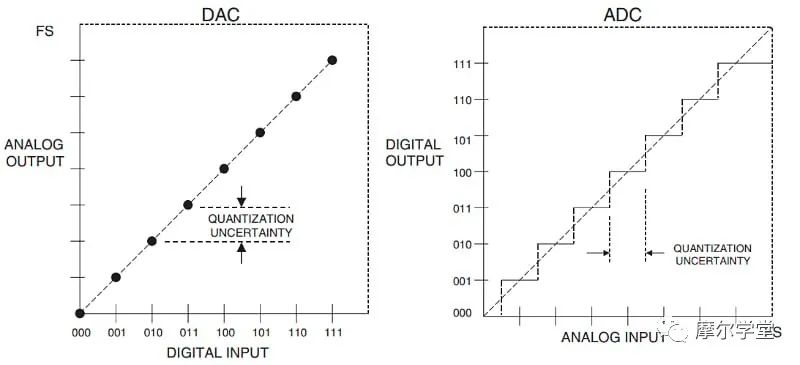

量化,數字信號在時間和幅值上都是離散的,因此采樣-保持電路的輸出電壓,還需按某種近似方程歸化到相應的離散電平上,這一轉化過程稱為量化。編碼,量化后的數值還需通過編碼用一個二進制代碼表示出來,經過編碼后得到的就是AD轉換結果的數字量,二進制編碼的位寬等于ADC的位寬。上圖示例是一個3 bit ADC,只舍不入量化方式(量化中把不足一個單位的部分舍棄),量化位數用3 bit來表示連續信號的幅值。信號滿量程為0~1V,因此最小量化單位Δ=1V/2^3=1/8V。量化位數越高,ADC的分辨率越高,量化誤差越小。一般ADC的分辨率使用LSB標識。

1.2.5 常見基本概念和參數

1) 位寬

即前一節提到的量化位數,常見的有8bit,10bit,12bit,16bit,24bit。比較少見的部分高速ADC有6bit~8bit。

2) 分辨率

ADC所能分辨的最小量化信號的能力,最小分辨能力Δ=輸入滿量程電壓/2^N。分辨率主要由ADC的位數(輸出數字量的位數)決定,也與輸入滿量程有一定的關系。如一個輸出滿量程為0~5V的ADC、8位的ADC,其最小變化量為5V/2^8,約為19.5mV。若將ADC的位寬增加為10位,則ADC的最小變化量為5V/2^10,約為4.88mV。

3) 量化誤差Σ

在量化過程中由于所采樣的電壓不一定能被Δ(最小量化單位)整除,所以量化前后存在一定誤差,此誤差稱為量化誤差。量化誤差屬于原理誤差,無法消除,理論上轉換器的位數越高,各離散電平之間的差值越小,量化誤差就越小。

4) INL

INL (IntergerNonLinear, 積分非線性), 指ADC實際轉換曲線與理想曲線在縱軸方向的差值,單位LSB,用于表示實際轉換曲線與理想的偏差程度。

5) DNL

DNL (DifferentialNonLinear, 微分非線性), 指ADC的實際量化臺階與對應于1LSB的理想值之間的差異。理想ADC偏差為0LSB。若DNL<1LSB,意味著傳輸函數具有單調性,沒有丟碼。

6) SNR

SNR (Signal NoiseRatio,信噪比), ADC輸出信號功耗和噪聲功耗的比值,用dB表示。SNR=10*log(P_signal/P_noise),其中信號頻譜圖中基波分量有效值,噪聲=總能量-信號能量和諧波能量。理想ADC的噪聲主要來自量化噪聲。

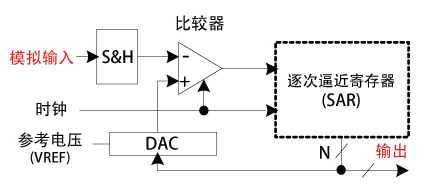

1.3 SAR型ADC原理

SAR(Successive Approximation, 逐次比較型), 包括一個比較器,一個數模轉換器、一個逐次逼近寄存器(SAR)和控制邏輯單元。將輸入的模擬信號與已知電壓(DAC,數模轉換)不斷進行比較,一個時鐘周期完成一次轉換,N位的ADC需要N個時鐘周期完成轉換,轉換完成后輸出二進制。

從上面描述可以看出,此種ADC有個問題,位寬越寬,轉換需要的時鐘周期越多,即如果想提高ADC分辨率,會限制采樣速率。所有此種ADC一般用在低速場景。

1.4 Σ-Δ型ADC原理

Σ-Δ型(Sigma-Delta-Converter, Σ-Δ型模數轉換器), 又稱為過采樣轉換器,它采用增量編碼方式,根據前一量值與后一量值的差值的大小進行量化和編碼。Σ-Δ型ADC主要由Σ-Δ型調制器和數字濾波器組成。調制器主要完成信號抽樣和增量編碼,給數字濾波器提供增量編碼。數字濾波器完成對Σ-Δ碼的抽取濾波,把增量碼轉換成高分辨率的線性脈沖碼調制的數字信號,因此抽取濾波器實際上相當于一個碼型變化器。

Σ-Δ型ADC一般精度可以做到很高,24位ADC中很多是此種類型。

1.5 關于ADC的驗證

1.5.1 可能的驗證方式

從1.3節框圖可以看出,ADC分為模擬部分和數字部分。因此推測大概有2種方式,一是用veriloga實現模擬部分功能模型,和數字部分一起,驗證環境中將整塊邏輯作為DUT進行驗證;另一種方式是驗證只驗證數字部分,數字部分驗證ok后提供代碼給模擬設計工程師,模擬設計使用ams仿真器進行仿真。

1.5.2 數字驗證項

拋開模擬,只看ADC數字實現部分,主要驗證項可能有,CRG、寄存器、接口、功能等。

電子發燒友App

電子發燒友App

評論