鎖相環英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現在簡單介紹一下鎖相環的工作原理。

2023-04-28 09:57:31 4380

4380

PLL(鎖相環)電路原理是什么?

2022-01-21 07:03:37

鎖相環仿真,可以參考一下!

2012-08-13 09:11:17

圖解實用電子技術叢書,介紹鎖相環(PLL)電路設計與應用,供大家參考

2016-06-21 22:51:39

鎖相環,而他們都是屬于軟件鎖環的范疇。在電力仿真軟件中,一般都有PLL模塊,只需要將該模塊應用一下即可實現鎖相環的功能,即該模塊可輸出系統相角。其實,所謂的PLL模塊就是實現上面說的這么一團東西的,在

2015-01-04 22:57:15

聽說鎖相環可以倍頻,倍頻時輸入輸出頻率都不一樣,如何鎖相呢?

2023-04-24 10:14:34

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成器

2018-10-31 15:08:45

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成器

2018-11-06 09:03:16

鎖相環控制頻率的原理鎖相環頻率自動跟蹤-------用鎖相環可以確保工作在想要的頻率點上如何理解以下兩段話?鑒相器是相位比較裝置, 它把輸入信號和壓控振蕩器的輸出信號的相位進行比較, 產生對應

2022-06-22 19:16:46

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

第十七章IP核之PLL實驗PLL的英文全稱是Phase Locked Loop,即鎖相環,是一種反饋控制電路。PLL對時鐘網絡進行系統級的時鐘管理和偏移控制,具有時鐘倍頻、分頻、相位偏移和可編程

2022-01-18 09:23:55

電荷泵鎖相環的基本原理是什么?電荷泵鎖相環的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環的相位噪聲與環路帶寬關系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環PLL原理與應用 第一部分:鎖相環基本原理 一、鎖相環基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

那個對講機的鎖相環的程序怎么寫?是基于STM32單片機的,鎖相環芯片使用的是LMX2337

2014-04-09 08:18:49

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號

2022-01-11 06:34:28

本人在進在做鎖相環的仿真,進行頻率跟蹤的用的,可是怎么做都放不出波形,可有會仿真鎖相環的?

2014-06-23 11:14:38

頻率合成器的主要性能指標鎖相環頻率合成器原理鎖相環頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

如題,AD9957的鎖相環一直失鎖,不用鎖相環輸出點頻信號時正常的,用了鎖相環后,PLL_LOCK信號一直為低,sync_clk輸出信號也不是穩定的周期信號,環路濾波器的值有點誤差,因為現有的器件沒有那么精確的電容電阻值,問下鎖相環的控制除了控制CFR3之外還有別的要注意的么?

2018-12-10 09:30:24

背景因項目國產化需要,使用國產化MCU(雅特力)ATF32F413CBT6替代STM32F103C8T6。該項目使用8M外部晶振作為系統時鐘來源,經PLL鎖相環倍頻至72M作為系統時鐘,在使用過程中

2022-02-11 06:40:12

Actel FPGA PLL鎖相環的最大能達到幾倍頻幾分頻?我在網上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊里面找到資料,想要確認一下。

2014-12-04 11:25:15

在我們設計工程中我們會用到100M,500M等時鐘,如果我們的晶振達不到我們就需要倍頻,再上一個文檔中我們了解到了分頻,可是倍頻我們改怎么做了,這里我們就用了altera的IP核鎖相環。今天我們將去

2019-06-17 08:30:00

說,上貨。

鎖相環使用教程

鎖相環是我們比較常用的IP核之一。PLL的英文全稱是Phase locked loop即鎖相環,是一種反饋電路。具有分頻、倍頻、相位偏移和占空比可調的功能。在XILINX

2023-06-14 18:09:08

LabVIEW鎖相環(PLL) 鎖相環是一種反饋電路,其作用是使得電路上的時鐘和某一外部時鐘的相位同步。PLL通過比較外部信號的相位和由壓控晶振(VCXO)的相位來實現同步的,在比較的過程中,鎖相環

2022-05-31 19:58:27

在使用K60的過程中發現自己pllinit()不清楚,才發覺自己鎖相環的概念還不懂,so,趕緊補補……鎖相環(PLL: Phase-locked loops)是一種利用反饋(Feedback)控制

2021-11-04 08:57:18

網上Multisim仿真鎖相環的帖子很少,本人最近經過摸索仿真了2倍及4倍頻。仿真基于Multisim自帶的PLL虛擬元件。參數設置是倍頻成功與否的關鍵。

2019-09-08 15:29:59

`可編程鎖相環(PLL)解決方案有多種尺寸和類型可供選擇。 PLL以整數N或小數N形式提供同時根據帶寬利用無源或有源環路濾波器。 可以通過3線串行接口對其進行快速編程同時提供非常低的雜散抑制和較小

2021-04-03 17:00:58

信號源的任何應用的理想選擇,并且利用微帶或陶瓷諧振器拓撲結構可提供出色的相位噪聲性能。測試儀器雷達系統SFS10500H-LF鎖相環SFS10625H-LF鎖相環SFS10640H-LF鎖相環

2021-04-03 17:05:46

或外部時鐘,頻率范圍為4~16MHz。LSI:低速內部時鐘源,RC振蕩器,頻率為40KHz。LSE:低速外部時鐘源,接頻率為32.768KHz的石英晶體。PLL:鎖相環倍頻輸出,

2021-08-23 08:24:05

時鐘,由外接晶振產生,穩定性高HSEOSC2~26MHz高速外部時鐘。由外接晶振產生(外部晶振一般都是8MHz)HSIRC16MHz告訴內部時鐘,由內部RC振蕩器產生PLL鎖相環倍頻輸出:主鎖相環PLL產生:PLL主時鐘 或者 P

2021-08-02 08:57:53

,內部低速RC 時鐘,40KHZ;LSE外部低速時鐘,32.768KHz;PLL鎖相環倍頻,由圖可知,可以選擇HSE/2、HSI/2、HSE,

2021-08-19 06:28:59

。晶振用的是8MHz,PLL鎖相環倍頻獲取SYSCLK(時鐘頻率),代碼配置如下://外部晶振為8M的時候,推薦值:plln=200,pllm=8,pllp=2,pllq=4.//得到:Fvco=8*(200/8)=200Mhz//SYSCLK=200/2=100Mhz//Fu***

2021-08-10 06:26:55

labview虛擬鎖相環的跟蹤鎖定時間過長,請問有什么辦法可以解決這個問題

2011-05-17 19:03:34

進行調節,還可以對同一PLL生成的多個時鐘的相位進行控制,以保證兩個時鐘域的邏輯工作時有確定的時間差。具體鎖相環是通過何種方式實現對時鐘信號的分頻和倍頻的,這里我們不做講解,有興趣的朋友可以自己查閱相關

2017-01-05 00:00:52

初始化;2,GPIO初始化為輸入和輸出。按鍵初始化為輸入,LED初始化為輸出;3,外部輸入中斷初始化,即按鍵使用中斷讀取狀態;4,輸出結果,按鍵一次,LED狀態反一次。時鐘架構 使用PLL鎖相環倍頻到

2016-05-29 14:40:04

介紹了頻率捕獲、電荷泵鎖相環等熱點應用問題。目錄:第1章 簡介1.1 PLL的性質1.1.1 帶寬1.1.2 線性1.2 本書結構1.3 文獻及注釋1.3.1 推薦書目1.3.2 技術文集1.3.3

2017-08-10 17:44:31

`編輯推薦《鎖相環(PLL)電路設計與應用》內容豐富、實用性強,便于讀者自學與閱讀理解,可供電子、通信等領域技術人員以及大學相關專業的本科生、研究生參考,也可供廣大的電子愛好者學習參考。作者簡介作者

2017-09-18 17:56:02

摘要:鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。本文將參考上述各種應用來介紹PLL

2019-10-02 08:30:00

什么是鎖相環 (PLL)?一個鎖相環PLL電路通常由哪些模塊組成?

2022-01-17 06:01:54

鎖相環(PLL)電路存在于各種高頻應用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網絡分析儀(VNA)中的超快開關頻率合成器。今天斑竹帶來干貨好文,參考上述各種應用來

2019-01-28 16:02:54

本文設計了一種寬頻率范圍的CMOS鎖相環(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關噪聲抵消電路,有效地改善了傳統電路中由于電流失配、電荷共享、時鐘饋通等導致的相位偏差問題。設計了

2019-07-08 07:37:37

采用后向Euler數值積分法實現二階鎖相環的一個仿真模型,對二階鎖相環進行仿真,那位大俠做過?可以參考下原代碼不?

2012-05-28 17:21:05

目標:以10或40MHz的差分時鐘經2~5米長的電纜傳輸到至少兩塊線路板上,倍頻為200MHz的時鐘;要求此兩板上的200MHz時鐘保持同步,或者說在每次上電的情況下保持恒定的相位關系。 鎖相環

2018-09-18 11:14:35

說明。所提供的組成部分是,沒有負債。它可以自由使用和修改。YouTube視頻顯示組件在行動:自定義鎖相環(PLL)演示使用PSOC5微控制器-YouTube當做,奧迪賽1拉鏈3.4兆字節郵編2.1兆

2018-11-07 17:06:05

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。鎖相環通常由鑒相器(PD)、環路濾波器(LF

2019-03-17 06:00:00

小弟需要對正弦信號進行鎖相,就是鎖相環的輸入輸出都是正弦信號,有合適的芯片嗎?最好給點資料,小弟急需!!還有芯片要可以外接倍頻單元。在此謝過了!!!

2011-03-13 09:46:00

設計并調試鎖相環(PLL)電路可能會很復雜,除非工程師深入了解PLL 理論以及邏輯開發過程。本文介紹PLL設計的簡易方法,并提供有效、符合邏輯的方法調試PLL 問題。

2021-04-07 06:28:03

鎖相環倍頻輸出,最高能夠為設備提供 144MHz 的系統主頻。 L SE 主要 為實時時鐘( R TC )和其他低速外設提供一個低功耗且精確的時鐘源。產生準確、穩定的時鐘是系統正常工作的前提。本文檔 主要

2022-06-30 15:35:57

如果沒有深入了解 PLL 理論以及邏輯開發過程,可能你在設計并調試鎖相環(PLL)電路時會感到非常棘手。那有沒有比較容易理解或學習妙招呢?小A今日就為大家送上一份妙計錦囊,并提供有效、符合邏輯的方法助你調試PLL問題。請往下看~

2021-01-27 06:52:20

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

控制用微處理器的主要性能有哪些?處理器在調頻(FM)調諧器中的應用是什么?數字調諧系統有哪些性質?怎樣去設計一種基于PLL(鎖相環)合成器的數字調諧系統?

2021-08-17 07:03:36

的PLL鎖相環的倍頻,獲得所希望的工作頻率。同時通過在DSP內部對時鐘進行編程控制,也能較好地滿足不同應用的要求。例如對于自動化儀表、便攜式儀器以及家電等應用場合,往往希望有較低能耗,這時可通過編程,使

2013-04-18 15:58:58

堆疊著鑒相、同相積分、中相積分、濾波等專用名詞。這些概念距離硬件設計實現數字鎖相環較遠。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

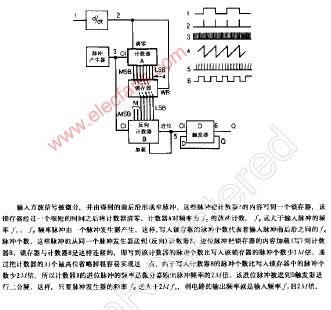

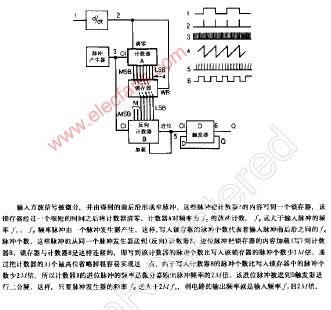

數字鎖相環設計源程序PLL是數字鎖相環設計源程序, 其中, Fi是輸入頻率(接收數據), Fo(Q5)是本地輸出頻率.目的是從輸入數據中提取時鐘信號(Q5), 其頻率與數據速率一致, 時鐘上升沿鎖定在數據的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

最全面最權威的鎖相環PLL原理與應用資料非常經典的資料

2022-12-02 22:39:56

定時器,當然,為了運行100MHz,還應該加上 pll鎖相環倍頻。對于應用程序,應該完成圓周率的計算,并將結果

2021-11-08 08:08:50

模擬鎖相環與數字鎖相環的主要區別在哪里?

2023-04-24 10:48:52

低速外部晶體 )。 其中 H SE 可為系統提供精確的主時鐘源,支持的晶振頻率范圍為 4MHz~32MHz ,通過 PLL 鎖相環倍頻輸出,最高能夠為設備提供 144MHz 的系統主頻。 L SE 主要

2022-07-01 10:17:40

有沒有人用過頻率能達到300M以上的集成鎖相環PLL,急求推薦!!

2015-07-30 17:09:19

求助PLL 鎖相環器件選型指導:1) output: Single End clock2) Work Clock: 1Ghz

2018-09-03 11:49:29

求助:鎖相環(PLL)電路設計與應用; 日本人寫的. [此貼子已經被作者于2010-1-15 18:23:54編輯過]

2009-11-19 15:47:54

信噪比下降,誤碼率增加。低相噪Hittite鎖相環產品分為集成VCO和沒有集成VCO兩種。集成VCO的PLL芯片包括了HMC820,HMC821,HMC826等。下面是與市場上同類產品的對比,以工作頻段1720~2080MHz為例:

2019-06-25 06:22:21

本文介紹了電荷泵鎖相環電路鎖定檢測的基本原理,通過分析影響鎖相環數字鎖定電路的關鍵因子,推導出相位誤差的計算公式。并以CDCE72010 為例子,通過實驗驗證了不合理的電路設計或外圍電路參數是如何影響電荷泵鎖相環芯片數字鎖定指示的準確性。

2021-04-20 06:00:37

請教一下大神鎖相環是如何實現倍頻的?

2023-04-24 10:15:39

您好,我們目前在做一個調頻連續波的雷達,DDS輸出50~60MHz,使用ADI的鎖相環ADF4108 96倍頻至4.8GHz~5.8GHz,掃頻周期4ms,點頻測試時鎖相環的相位噪聲還可

2018-08-16 07:18:19

如題,S3C2440是不是默認不開啟鎖相環PLL的。另外S3C2440與S3C2440A是同一款芯片嗎?為什么這兩款芯片我看到的關于時鐘分頻器設置的參數有些是不一樣的

2019-05-09 04:05:32

這個72MHz也應該是由STM32的PLL鎖相環倍頻出來的啊。。。但是我找了別人移植的工程,就是沒有提到關于stm32的系統時鐘配置啊,我裸跑的時候也會有這個函數初始化系統時鐘

2019-07-29 20:36:41

我剛接觸鎖相環沒多長時間,最近想使用ADF4106搭建一個雙環鎖相環,我閱讀的資料都沒有說主環路環路濾波器參數計算問題,我想咨詢專家ADIsimPLL是否可以仿真計算雙環鎖相環,如果可以具體怎么考慮,如果可以告訴我一些主環路環路帶寬的知識就更好了.

2019-03-07 10:34:03

音頻鎖相環相關資料集很多好資料哦! [hide]音頻鎖相環相關資料等.rar[/hide]

2009-12-04 11:43:03

本文針對一款應用于大規模集成電路的CMOS高頻鎖相環時鐘發生器,提出了一種可行的測試方案,重點講述了鎖相環的輸出頻率和鎖定時間參數的測試,給出了具體的測試電路和測試方法。對于應用在大規模電路系統中的鎖相環模塊,該測試方案既可用于鎖相環的性能評測,也可用于鎖相環的生產測試。

2021-04-21 06:28:15

Skyworks Solutions 的 SKY72302-21 是一款鎖相環,頻率為 400-6100 MHz,相位噪聲 -80

2023-06-12 17:22:25

Skyworks Solutions 的 SKY74038-21 是一款鎖相環,頻率為 100-2600 MHz

2023-06-12 17:24:47

Skyworks Solutions 的 SKY72300-362 是一款鎖相環,頻率為 100-2100 MHz,相位噪聲 -91

2023-06-12 17:30:57

不帶鎖相環的倍頻器

2009-09-17 16:11:00 857

857

鎖相環(PLL),鎖相環(PLL)是什么意思

PLL的概念

我們所說的PLL。其

2010-03-23 10:47:48 6005

6005 本書是圖解電子工程師實用技術叢書之一,本書主要介紹鎖相環(PLL)電路的設計與應用,內容包括PLL工作原理與電路構成、PLL電路的傳輸特性、PLL電路中環路濾波器的設計方法、PLL電路

2011-09-14 17:55:24 0

0 鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

如何設計并調試鎖相環(PLL)電路 pdf

2016-01-07 16:20:08 0

0 本文檔的主要內容詳細介紹的是鎖相環PLL的原理與應用的詳細資料說明包括了:第一部分:鎖相環基本原理,一、鎖相環基本組成,二、鑒相器(PD)phase discriminator ,三、壓控振蕩器

2020-04-29 08:00:00 13

13 定時器,當然,為了運行100MHz,還應該加上 pll鎖相環倍頻。對于應用程序,應該完成圓周率的計算,并將結果

2021-11-03 16:51:05 9

9 背景因項目國產化需要,使用國產化MCU(雅特力)ATF32F413CBT6替代STM32F103C8T6。該項目使用8M外部晶振作為系統時鐘來源,經PLL鎖相環倍頻至72M作為系統時鐘,在使用過程中

2021-12-08 11:06:04 10

10 鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2022-03-29 09:54:55 11472

11472 鎖相環 (PLL) 電路存在于各種高頻應用中,從簡單的時鐘清理電路到用于高性能無線電通信鏈路的本振 (LO),再到矢量網絡分析儀 (VNA) 中的超快速開關頻率合成器。本文解釋了鎖相環電路的一些構建模塊,并參考了每種應用,以幫助指導新手和鎖相環專家導航器件選擇以及每種不同應用固有的權衡取舍。

2022-12-23 14:03:54 3612

3612

PLL鎖相環版圖設計時應注意以下幾點:1)確定PLL的頻率范圍;2)確定PLL的控制電路;3)確定PLL的調節電路;4)確定PLL的輸出電路;5)確定PLL的濾波電路;6)確定PLL的控制參數;7)確定PLL的輸出參數。

2023-02-14 15:42:59 2085

2085 pll鎖相環倍頻的原理? PLL鎖相環倍頻是一種重要的時鐘信號處理技術,廣泛應用于數字系統、通信系統、計算機等領域,具有高可靠性、高精度、快速跟蹤等優點。PLL鎖相環倍頻的原理涉及到鎖相環,倍頻

2023-09-02 14:59:24 1508

1508 PLL倍頻的實現方法、工作原理以及最大倍數的計算方法,幫助讀者更好地了解和應用PLL倍頻電路。 一、PLL倍頻的實現方法 PLL倍頻主要通過三個電路模塊來實現:相位比較器、鎖相環和除頻器。其中,相位比較器主要用于比較輸入信號和反饋信號的相

2023-09-02 14:59:30 811

811 鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 1594

1594 鎖相環倍頻器鎖在基頻怎么辦?? 鎖相環倍頻器是一種基于相位鎖定原理的電子設備,它能夠將輸入信號的頻率倍增。然而,有時候鎖相環倍頻器會鎖在基頻上,導致無法達到所要求的倍頻效果。這時候,我們需要采取一些

2023-09-02 15:12:31 369

369 pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 1102

1102 siumlink中三相鎖相環PLL的輸入怎么實現? siumlink中三相鎖相環PLL的輸入是通過輸入三相交流電壓來實現的。在交流電力系統中,多數情況下使用的是三相電壓,因此三相鎖相環(PLL

2023-10-13 17:39:56 482

482 了解鎖相環(PLL)瞬態響應 如何優化鎖相環(PLL)的瞬態響應? 鎖相環(PLL)是一種廣泛應用于數字通信、計算機網絡、無線傳輸等領域的重要電路。PLL主要用于時鐘恢復、頻率合成、時鐘同步等領域

2023-10-23 10:10:20 869

869

電子發燒友App

電子發燒友App

評論