外延工藝是指在襯底上生長完全排列有序的單晶體層的工藝。一般來講,外延工藝是在單晶襯底上生長一層與原襯底相同晶格取向的晶體層。外延工藝廣泛用于半導體制造,如集成電路工業的外延硅片。MOS 晶體管

2023-02-13 14:35:47 10449

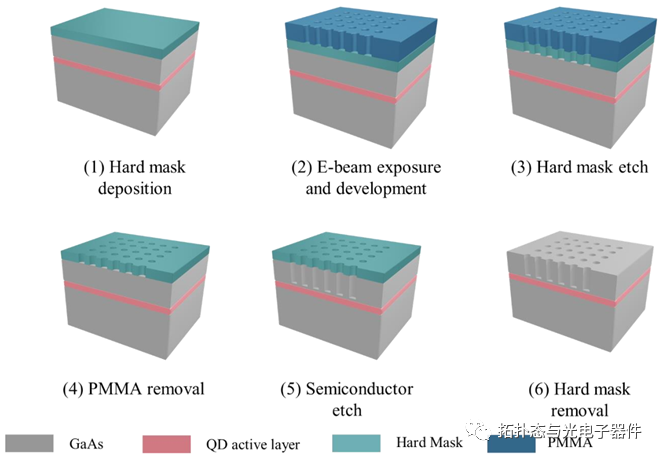

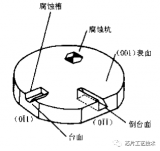

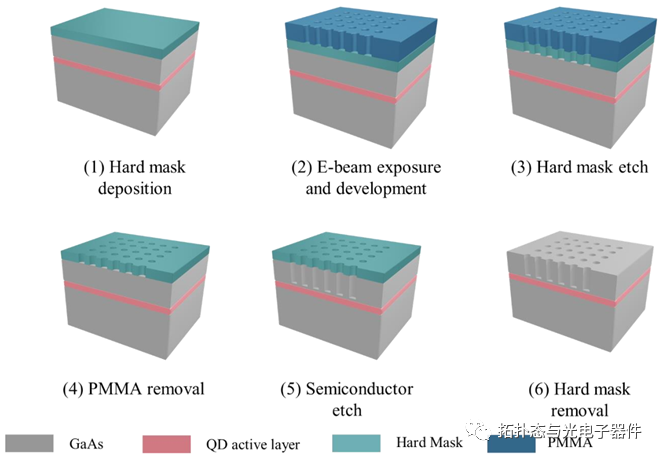

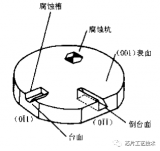

10449 設計外延片參數,第一次外延,制備光子晶體,第二次外延,制備臺面和電極。

2023-05-22 11:43:35 1467

1467

一些后處理步驟,例如研磨、化學機械研磨(CMP)、SiC外延、注入、檢測、化學氣相沉積(CVD)和物理氣相沉積(PVD)。SiC晶圓因其半透明性質和材料硬度而面臨許多挑戰,這需要對關鍵工藝步驟設備進行

2019-05-12 23:04:07

我國科學家成功在8英寸硅片上制備出了高質量的氧化鎵外延片。我國氧化鎵領域研究連續取得突破日前,西安郵電大學新型半導體器件與材料重點實驗室的陳海峰教授團隊成功在8英寸硅片上制備出了高質量的氧化鎵外延片

2023-03-15 11:09:59

`各位大神,小弟初學LV,想編一個工藝流程仿真計算的軟件,類似這樣一個東西如圖所示:先設置每一個單體設備的具體參數,然后運行,得出工藝流程仿真計算的結果,計算模型有很多公式,可以直接編程。但要想達到

2015-11-17 17:18:22

有沒有能否切割晶圓/硅材質濾光片的代工廠介紹下呀

2022-09-09 15:56:04

架上,放入充滿氮氣的密封小盒內以免在運輸過程中被氧化或沾污十、發往封測Die(裸片)經過封測,就成了我們電子數碼產品上的芯片。晶圓的制造在半導體領域,科技含量相當的高,技術工藝要求非常高。而我國半導體

2019-09-17 09:05:06

`晶圓制造總的工藝流程芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構裝工序(Packaging)、測試工序(Initial

2011-12-01 15:43:10

有人又將其稱為圓片級-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對象,在晶圓上封裝芯片。晶圓封裝中最關鍵的工藝為晶圓鍵合,即是通過化學或物理的方法將兩片晶圓結合在一起,以達到密封效果。如下

2021-02-23 16:35:18

細間距的晶圓級CSP時,將其當做倒裝晶片并采用助焊劑浸蘸的方法進行組裝,以取代傳統的焊膏印刷組裝,如圖2所示,首先將晶圓級CSP浸蘸在設定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關于錫膏裝配和助焊劑裝配的優缺點。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

時間。

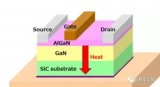

更加環保:由于裸片尺寸小、制造工藝步驟少和功能集成,氮化鎵功率芯片制造時的二氧化碳排放量,比硅器件的充電器解決方案低10倍。在較高的裝配水平上,基于氮化鎵的充電器,從制造和運輸環節產生的碳足跡,只有硅器件充電器的一半。

2023-06-15 15:32:41

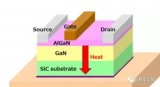

晶圓低得多的成本。更重要的是,行業發展已為硅基氮化鎵在商業化規模量產、庫存維護、適應需求激增等方面打下了堅實的基礎,緩解了供應短缺的擔憂。只要碳化硅基氮化鎵繼續依賴耗時、高成本的制造工藝,這種擔擾就將

2017-08-15 17:47:34

光電子應用正在推動砷化鎵(GaAs)晶圓和外延片市場進入一個新時代!在GaAs射頻市場獲得成功之后,GaAs光電子正成為一顆冉冉升起的新星

2019-09-03 06:05:38

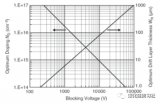

車、工業電機等領域具有巨大的發展潛力。本分會的主題涵蓋大尺寸襯底上橫向或縱向氮化鎵器件外延結構與生長、氮化鎵電力電子器件的新結構與新工藝開發、高效高速氮化鎵功率模塊設計與制造,氮化鎵功率應用與可靠性等。本屆

2018-11-05 09:51:35

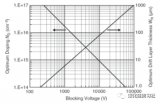

尺寸相同的LDMOS的4到6倍。盡管MACOM氮化鎵的材料成本因氮化鎵外延淀積而略高于 LDMOS,但MACOM的晶片加工流程相較LDMOS可以節省50%的制造步驟,從而單片晶圓的加工成本差異幾乎可以

2017-08-30 10:51:37

不同,MACOM氮化鎵工藝的襯底采用硅基。硅基氮化鎵器件既具備了氮化鎵工藝能量密度高、可靠性高等優點,又比碳化硅基氮化鎵器件在成本上更具有優勢,采用硅來做氮化鎵襯底,與碳化硅基氮化鎵相比,硅基氮化鎵晶元尺寸

2017-09-04 15:02:41

PCB工藝流程詳解PCB工藝流程詳解

2013-05-22 14:46:02

; b. FR-4是環氧樹脂的一種,主要用于線路板行業; c.環氧樹脂的反應: 二、工藝流程圖: 三、排板: 1.將黑化板、P片按要求進行排列。 2. 過程:選P片→切P片→排P片→排棕化板→排P

2018-09-19 16:28:07

PCB制造工藝流程是怎樣的?

2021-11-04 06:44:39

誰能闡述一下PCB四層板的制作工藝流程?

2020-02-24 16:48:14

介紹(二)32.表面處理介紹(三)33.成型工序介紹(一)34.成型工序介紹(二)35.測試FQC包裝36.IPC標準及其它標準介紹PCB工程設計,工藝流程基礎知識下載鏈接`

2021-07-14 23:25:50

本文主要介紹:單面電路板、雙面板噴錫板、雙面板鍍鎳金、多層板噴錫板、多層板鍍鎳金、多層板沉鎳金板;這幾種電路板不同的工藝流程做詳細的介紹。 1、單面板工藝流程 下料磨邊→鉆孔→外層圖形→(全板

2018-09-17 17:41:04

Memory、PLL 鎖相環電路、起振電路與溫補電路。上面六幅圖揭示了整個SITIME晶振生產工藝流程,SITIME MEMS 電子發燒友振采用上下兩個晶圓疊加的方式,外部用 IC 通用的塑料做為封裝。不僅大大減少的石英晶振的工序,而且更全面提升了產品性能。

2017-04-06 14:22:11

, 以及在回流焊接機之后加上PCA下板機(PCA Un-loader ),另外,成品PCA可能需要進行清洗和進行老 化測試,下面的流程圖(圖1)描述了典型的貼裝生產基本工藝流程。 上面簡單介紹了SMT貼

2018-08-31 14:55:23

Verilog設計內外延時

2012-08-15 16:31:14

GaN 襯底上獲得高性能的薄膜器件,必須使 GaN 襯底的表面沒有劃痕和損壞。因此,晶圓工藝的最后一步 CMP 對后續同質外延 GaN 薄膜和相關器件的質量起著極其重要的作用。CMP 和干蝕刻似乎

2021-07-07 10:26:01

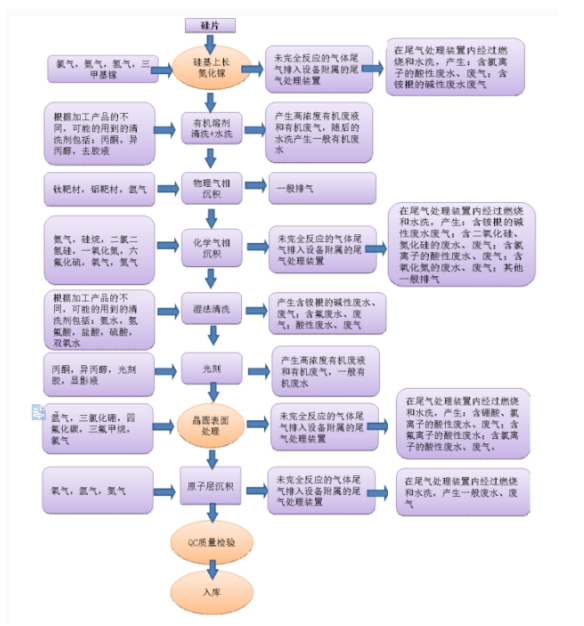

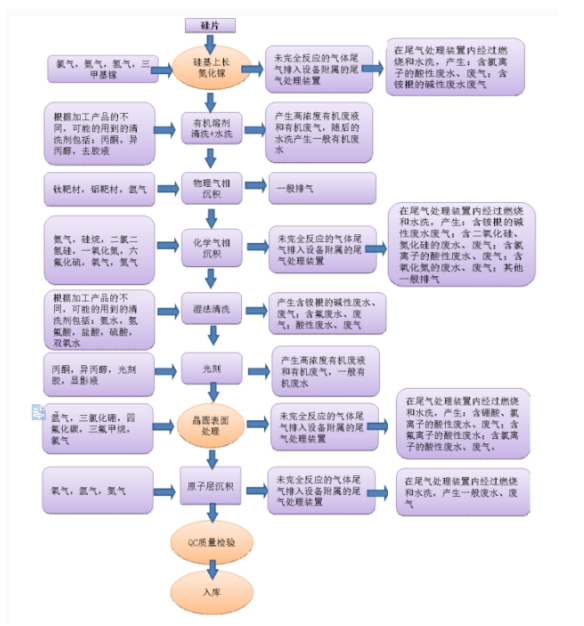

:LED芯片的制造工藝流程 LED芯片的制造工藝流程圖外延片→清洗→鍍透明電極層→透明電極圖形光刻→腐蝕→去膠→平臺圖形光刻→干法刻蝕→去膠→退火→SiO2沉積→窗口圖形光刻→SiO2腐蝕→去膠→N極圖形

2015-03-11 17:08:06

% 的能源浪費,相當于節省了 100 兆瓦時太陽能和1.25 億噸二氧化碳排放量。

氮化鎵的吸引力不僅僅在于性能和系統層面的能源利用率的提高。當我們發現,制造一顆片氮化鎵功率芯片,可以在生產制造環節減少80

2023-06-15 15:47:44

鎵晶圓的制作成為可能。Na Flux (Na Flux)工藝是將 Na/GaN溶液置于壓力30-40的氮氣中,在該溶液中溶解氮并使其飽和,由此導致氮化鎵晶體沉淀。此項技術由山根久典教授于日本東北大學

2023-02-23 15:46:22

eMode硅基氮化鎵技術,創造了專有的AllGaN?工藝設計套件(PDK),以實現集成氮化鎵 FET、氮化鎵驅動器,邏輯和保護功能于單芯片中。該芯片被封裝到行業標準的、低寄生電感、低成本的 5×6mm 或

2023-06-15 14:17:56

氮化鎵南征北戰縱橫半導體市場多年,無論是吊打碳化硅,還是PK砷化鎵。氮化鎵憑借其禁帶寬度大、擊穿電壓高、熱導率大、電子飽和漂移速度高、抗輻射能力強和良好的化學穩定性等優越性質,確立了其在制備寬波譜

2019-07-31 06:53:03

2.倒裝晶片的裝配工藝流程介紹 相對于其他的IC元件,如BGA和CSP等,倒裝晶片裝配工藝有其特殊性,該工藝引入了助焊劑工藝和底部填充工 藝。因為助焊劑殘留物(對可靠性的影響)及橋連的危險,將倒裝

2018-11-23 16:00:22

芯片焊接的工藝流程 倒裝芯片焊接的一般工藝流程為 (1)芯片上凸點制作; (2)拾取芯片; (3)印刷焊膏或導電膠; (4)倒裝焊接(貼放芯片); (5)再流焊或熱固化(或紫外固化

2020-07-06 17:53:32

我想了解關于LED關于外延片生長的結構,謝謝

2013-12-11 12:50:27

關于黑孔化工藝流程和工藝說明,看完你就懂了

2021-04-23 06:42:18

) - 平整和拋光晶圓片的工藝,采用化學移除和機械拋光兩種方式。此工藝在前道工藝中使用。Chuck Mark - A mark found on either surface of a wafer

2011-12-01 14:20:47

哪些 MCU 產品以裸片或晶圓的形式提供?

2023-01-30 08:59:17

TEL:***回收拋光片、光刻片、晶圓片碎片、小方片、牙簽料、藍膜片回收晶圓片硅片回收/廢硅片回收/單晶硅片回收/多晶硅片回收/回收太陽能電池片/半導休硅片回收

2011-04-15 18:24:29

不同的工藝流程做詳細的介紹。 1、單面板工藝流程下料磨邊→鉆孔→外層圖形→(全板鍍金)→蝕刻→檢驗→絲印阻焊→(熱風整平)→絲印字符→外形加工→測試→檢驗。 2、雙面板噴錫板工藝流程下料磨邊→鉆孔→沉銅

2017-12-19 09:52:32

` 有誰用過SEMILAB的SRP-2000外延片厚度測試儀,關于測試儀的機構和控制部分,尤其是精度部分希望交流,資料可發g-optics@163.com,多謝!`

2018-11-20 20:25:37

晶體管管芯的工藝流程?光刻的工藝流程?pcb制版工藝流程?薄膜制備工藝流程?求大佬解答

2019-05-26 21:16:27

在硅頂部生長氮化鎵外延層,可以使用現有的硅制造供應鏈而免于使用昂貴的特定生產地點。供應鏈利用現成的大直徑硅晶圓以低成本進行量產,并與具備豐富經驗的合作伙伴進行大批量后端生產。由于氮化鎵器件比硅器件

2023-06-25 14:17:47

有沒有人了解晶圓片輻照后的退火過程?我公司有輻照設備,但苦于不了解退火的過程

2012-09-12 13:35:04

樣板貼片的工藝流程是什么

2021-04-26 06:43:58

本科畢業設計需要閃存的工藝流程,但是在知網和webofscience我都沒找到,希望有大佬可以幫幫忙。謝謝了

2022-04-18 21:51:10

繼續發展。我們預言激光工藝將在單位晶圓裸片數量和縮短投資回收期方面有進一步的發展。

2010-01-13 17:01:57

`什么是硅晶圓呢,硅晶圓就是指硅半導體積體電路制作所用的硅晶片。晶圓是制造IC的基本原料。硅晶圓和晶圓有區別嗎?其實二者是一個概念。集成電路(IC)是指在一半導體基板上,利用氧化、蝕刻、擴散等方法

2011-12-02 14:30:44

日前,在廣州舉行的2013年LED外延芯片技術及設備材料最新趨勢專場中,晶能光電硅襯底LED研發副總裁孫錢博士向與會者做了題為“硅襯底氮化鎵大功率LED的研發及產業化”的報告,與同行一道分享了硅襯底

2014-01-24 16:08:55

芯片制作工藝流程 工藝流程1) 表面清洗 晶圓表面附著一層大約2um的Al2O3和甘油混合液保護之,在制作前必須進行化學刻蝕和表面清洗。2) 初次氧化 有熱氧化法生成SiO2 緩沖層,用來減小后續

2019-08-16 11:09:49

芯片制造全工藝流程詳情

2020-12-28 06:20:25

芯片生產工藝流程是怎樣的?

2021-06-08 06:49:47

本文主要介紹:單面線路板、雙面板噴錫板、雙面板鍍鎳金、多層線路板噴錫板、多層線路板鍍鎳金、多層板沉鎳金板;這幾種線路板不同的工藝流程做詳細的介紹。1.單面板工藝流程下料磨邊→鉆孔→外層圖形→(全板

2017-06-21 15:28:52

請詳細敘述腐蝕工藝工段的工藝流程以及整個前道的工藝技術

2011-04-13 18:34:13

氮化鎵GaN是什么?

2021-06-16 08:03:56

12英寸晶圓片的外觀檢測方案?那類探針臺可以全自動解決12英寸晶圓片的外觀缺陷測試? 本人郵箱chenjuhua@sidea.com.cn,謝謝

2019-08-27 05:56:09

貼片電阻的生產工藝流程如何

2021-03-11 07:27:02

、通訊等許多行業上的最終產品,它可以包括CPU、內存單元和其它各種專業應用芯片。本文有關超大規模集成電路的一些基本概念、主要生產工藝流程及其產業特點等做一個簡要介紹。

2019-07-29 06:05:53

各位大神,目前國內賣銦鎵砷紅外探測器的有不少,知道銦鎵砷等III-V族化合物外延片都是哪些公司生產的嗎,坐等答案

2013-06-04 17:22:07

長期收購藍膜片.藍膜晶圓.光刻片.silicon pattern wafer. 藍膜片.白膜片.晶圓.ink die.downgrade wafer.Flash內存.晶片.good die.廢膜硅片

2016-01-10 17:50:39

` 集成電路按生產過程分類可歸納為前道測試和后到測試;集成電路測試技術員必須了解并熟悉測試對象—硅晶圓。測試技術員應該了解硅片的幾何尺寸形狀、加工工藝流程、主要質量指標和基本檢測方法;集成電路晶圓測試基礎教程ppt[hide][/hide]`

2011-12-02 10:20:54

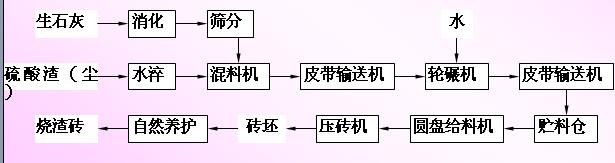

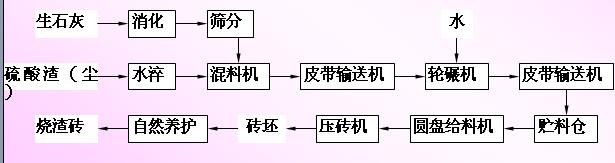

硫酸渣制磚工藝流程

含鐵量較低,

2009-03-30 20:10:20 1174

1174

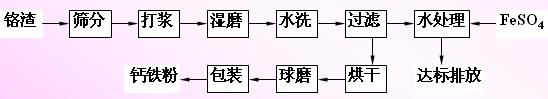

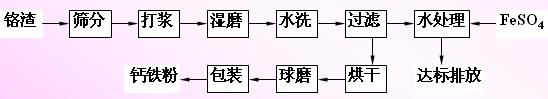

利用鉻渣制鈣鐵粉工藝流程

圖 利用鉻渣制鈣鐵粉工藝流程鉻渣制成的鈣鐵粉

2009-03-30 20:13:30 702

702

啟用PowerFill外延硅工藝的電源設備

ASM International推出了其PowerFill的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。 PoweRFill是一個精

2010-01-23 08:35:54 539

539 采用PowerFill外延硅工藝的電源器件

ASM International推出了其PowerFill的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。 PoweRFill是一個精

2010-01-25 09:17:05 525

525 ASM啟用新的PowerFill外延技術的電源設備

ASM International近日推出了其PowerFillTM的外延硅(Epi Si)溝槽填充工藝。新工藝可使帶有摻雜物的外延硅深溝無縫隙填充。owerFill是

2010-01-27 08:39:29 1820

1820 本內容介紹了LED外延片基礎知識,LED外延片--襯底材料,評價襯底材料必須綜合考慮的因素

2012-01-06 15:29:54 2743

2743 工藝流程

2016-02-24 11:02:19 0

0 一般來說,GaN 的成長須要很高的溫度來打斷NH3 之N-H 的鍵解,另外一方面由動力學仿真也得知NH3 和MO Gas 會進行反應產生沒有揮發性的副產物。 LED 外延片工藝流程如下: 襯底

2017-10-19 09:42:38 11

11 本文開始介紹了mlcc的定義與特性其次詳細的闡述了mlcc的工藝流程,最后介紹了mlcc的應用領域及MLCC在IC電源中的應用詳情。

2018-03-15 14:53:04 25239

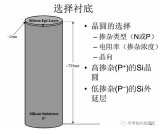

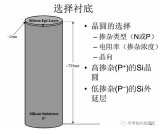

25239 CMOS工藝流程介紹1.襯底選擇:選擇合適的襯底,或者外延片,本流程是帶外延的襯底;2. 開始:Pad ox

2018-03-16 10:40:16 108618

108618

的硅基氮化鎵外延片產品技術。兩家公司最近合作的宗旨是,在為全球范圍內多家杰出的消費類電子產品公司生產外延片的同時,展示ALLOS 200 mm硅基氮化鎵外延片產品技術在Veeco Propel? MOCVD反應器上的可復制性。

2018-11-10 10:18:18 1381

1381 近日,北京耐威科技股份有限公司(以下簡稱“耐威科技”)發布公告稱,其控股子公司聚能晶源(青島)半導體材料有限公司(以下簡稱“聚能晶源”)成功研制“8英寸硅基氮化鎵(GaN-on-Si)外延

2018-12-20 14:45:20 6608

6608 涂覆工藝流程無論是手工浸、刷、噴、還是選擇性涂覆工藝,其工藝流程都是相同的。工藝流程如下:

2020-01-06 11:18:47 18974

18974 CMOS 工藝流程介紹

1.襯底選擇:選擇合適的襯底,或者外延片,本流程是帶外延的襯底;

2. 開始:Pad oxide 氧化,如果直接淀積氮化硅,氮化硅對襯底應力過大,容易出問題;

2020-06-02 08:00:00 0

0 近日,為了解決晶片尺寸不匹配的問題并應對 microLED 生產產量方面的挑戰,ALLOS 應用其獨特的應變工程技術,展示了 200 mm 硅基氮化鎵 (GaN-on-Si) 外延片的出色一致性和可重復性

2020-12-24 10:20:30 1340

1340 最近做芯片和外延的研究,發現同樣的外延工藝和芯片工藝做出來的芯片性能差別很大,大到改變試驗設計的“世界觀”。基板襯底的質量好壞很關鍵。

2021-08-12 10:55:58 4302

4302

從晶圓到芯片,有哪些工藝流程?晶圓制造工藝流程步驟如下: 1.表面清洗 2.初次氧化 3.CVD 4.涂敷光刻膠 5.用干法氧化法將氮化硅去除 6.去除光刻膠 7.用熱磷酸去除氮化硅層 8.退火處理

2021-12-30 11:11:16 17302

17302 CMOS工藝流程介紹,帶圖片。

n阱的形成 1. 外延生長

2022-07-01 11:23:20 27

27 通過圖形化硅氧化或氮化硅掩蔽薄膜生長,可以在掩蔽膜和硅暴露的位置生長外延層。這個過程稱為選擇性外延生長(SEG)。

2022-09-30 15:00:38 5893

5893 固相外延,是指固體源在襯底上生長一層單晶層,如離子注入后的熱退火實際上就是一種固相外延過程。離于注入加工時,硅片的硅原子受到高能注入離子的轟擊

2022-11-09 09:33:52 10252

10252 氮化鎵外延片生長工藝較為復雜,多采用兩步生長法,需經過高溫烘烤、緩沖層生長、重結晶、退火處理等流程。兩步生長法通過控制溫度,以防止氮化鎵外延片因晶格失配或應力而產生翹曲,為目前全球氮化鎵外延片主流制備方法。

2023-02-05 14:50:00 4345

4345 氮化鎵外延片指采用外延方法,使單晶襯底上生長一層或多層氮化鎵薄膜而制成的產品。近年來,在國家政策支持下,我國氮化鎵外延片行業規模不斷擴大。

2023-02-06 17:14:35 3012

3012 硅基氮化鎵外延生長是在硅片上經過各種氣體反應在硅片上層積幾層氮化鎵外延層,為中間產物。氮化鎵功率器件是把特定電路所需的各種電子組件及線路,縮小并制作在極小面積上的一種電子產品。氮化鎵功率器件制造主要

2023-02-11 11:31:42 6163

6163

通常是指的在藍寶石襯底上用外延的方法(MOCVD)生長的GaN。外延片上面一般都已經做有u-GaN,n-GaN,量子阱,p-GaN。

2023-02-12 14:31:25 2103

2103 氮化鎵外延片是一種由氮化鎵制成的薄片,它可以用于制造電子元件、電子器件和電子零件。氮化鎵外延片具有良好的熱穩定性和電磁屏蔽性,可以用于制造高精度的零件和組件,如電路板、電子控制器、電子模塊、電子接口、電子連接器等。

2023-02-14 14:05:41 3722

3722 硅基氮化鎵技術是一種新型的氮化鎵外延片技術,它可以提高外延片的熱穩定性和抗拉強度,從而提高外延片的性能。

2023-02-14 14:19:01 1046

1046 功率半導體分立器件的主要工藝流程包括:在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),進行芯片封裝,對加工完畢的芯片進行技術性能指標測試,其中主要生產工藝有外延工藝、光刻工藝、刻蝕工藝、離子注入工藝和擴散工藝等。

2023-02-24 15:34:13 3185

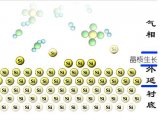

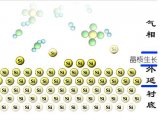

3185 在半導體科學技術的發展中,氣相外延發揮了重要作用,該技術已廣泛用于Si半導體器件和集成電路的工業化生產。

2023-05-19 09:06:46 2467

2467

外延層是在晶圓的基礎上,經過外延工藝生長出特定單晶薄膜,襯底晶圓和外延薄膜合稱外延片。其中在導電型碳化硅襯底上生長碳化硅外延層制得碳化硅同質外延片,可進一步制成肖特基二極管、MOSFET、 IGBT 等功率器件,其中應用最多的是4H-SiC 型襯底。

2023-05-31 09:27:09 2828

2828

無壓燒結銀工藝和有壓燒結銀工藝流程區別如何降低納米燒結銀的燒結溫度、減少燒結裂紋、降低燒結空洞率、提高燒結體的致密性和熱導率成為目前研究的重要內容。燒結銀的燒結工藝流程就顯得尤為重要

2022-04-08 10:11:34 778

778

電子發燒友網站提供《LED外延芯片工藝流程及晶片分類.doc》資料免費下載

2023-11-03 09:42:54 0

0 外延工藝的介紹,單晶和多晶以及外延生長的方法介紹。

2023-11-30 18:18:16 878

878

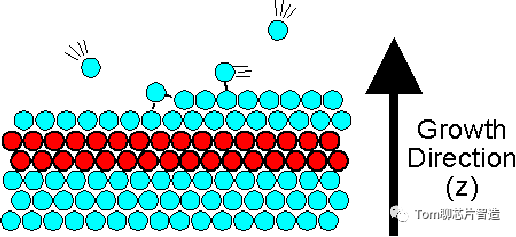

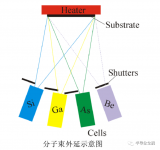

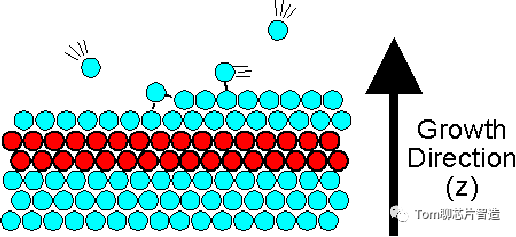

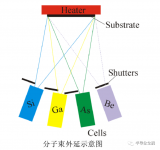

分子束外延(Molecular beam epitaxy,MBE)是一種在超高真空狀態下,進行材料外延技術,下圖為分子束外延的核心組成,包括受熱的襯底和釋放到襯底上的多種元素的分子束。

2024-01-15 18:12:10 968

968

襯底(substrate)是由半導體單晶材料制造而成的晶圓片,襯底可以直接進入晶圓制造環節生產半導體器件,也可以進行外延工藝加工生產外延片。

2024-03-08 11:07:41 161

161

正在加载...

電子發燒友App

電子發燒友App

評論