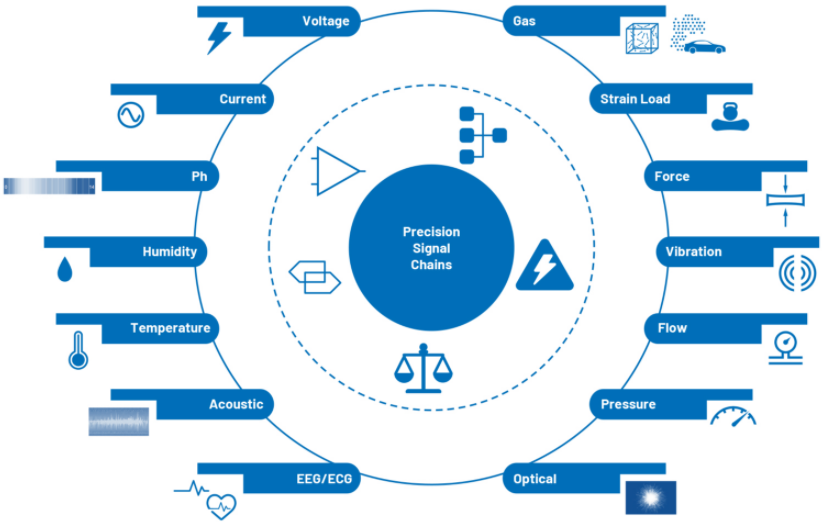

今天我們將討論時鐘如何影響精密 ADC,涉及時鐘抖動、時鐘互調和時鐘的最佳 PCB 布局實踐。

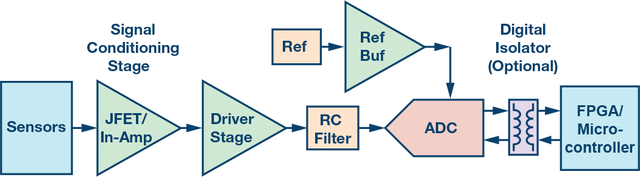

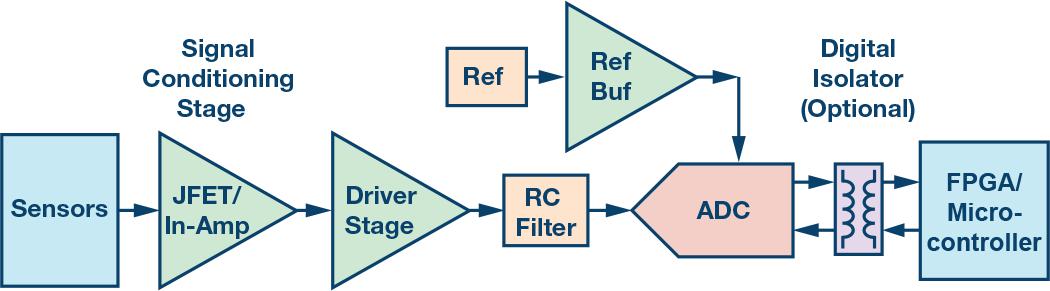

如本系列第 9 部分所述,所有數據采集 (DAQ) 系統都需要一個參考點。在那篇文章中,參考點是一個電壓電平,它與模擬輸入信號進行比較以生成輸出代碼。然而,DAQ 系統還需要另一種類型的參考點,盡管不一定與電壓相關。

在 DAQ 系統中,時鐘作為時間參考,以便所有組件可以同步運行。對于模數轉換器 (ADC),準確且穩定的時鐘可確保主機向 ADC 發送命令,并且 ADC 以正確的順序從主機接收命令且不會損壞。更重要的是,系統時鐘信號使用戶能夠在需要時對輸入進行采樣并發送數據,從而使整個系統按預期運行。

盡管您可能將時鐘視為數字輸入信號,但這些組件會影響精密 DAQ 系統的模擬性能。為了進一步了解時鐘如何影響精密 ADC,我們將討論這些與時鐘信號相關的主題:

時鐘抖動;

時鐘互調;和

時鐘的最佳印刷電路板 (PCB) 布局實踐。

時鐘抖動

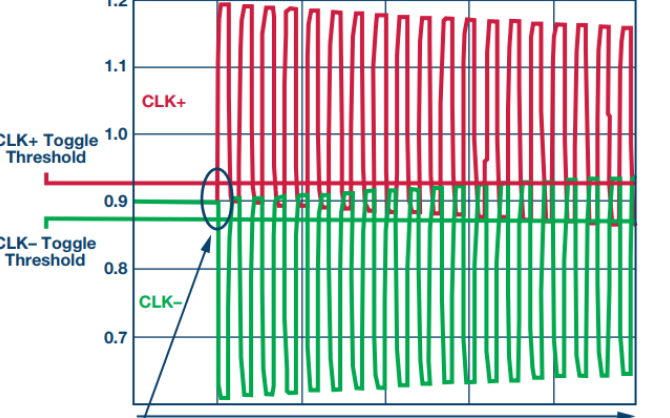

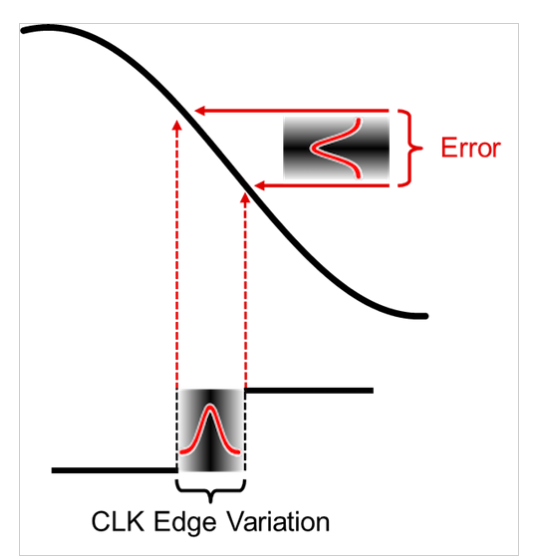

雖然您可能期望 ADC 的采樣周期完全恒定,但始終與理想情況存在一些偏差。“時鐘抖動”是指時鐘波形邊沿從一個周期到下一個周期的變化。由于所有 ADC 都使用時鐘邊沿來控制采樣點,因此時鐘邊沿變化會導致采樣實例出現偏差。這種偏差會導致出現在轉換結果中的非恒定采樣頻率,作為另一個噪聲源。

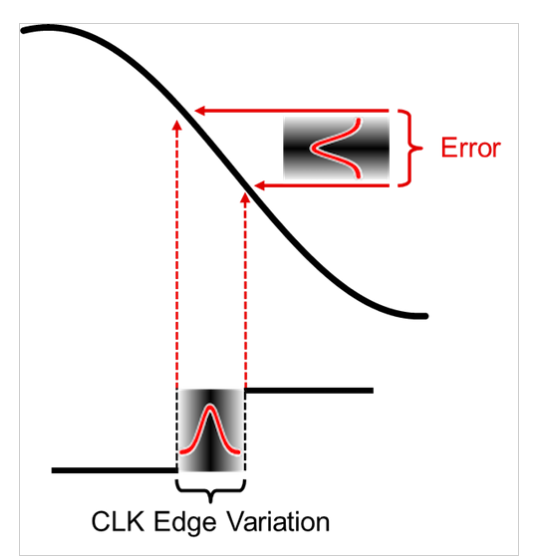

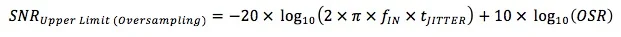

與本系列迄今為止討論的大多數噪聲源類似,時鐘抖動是隨機的,并遵循高斯分布。因此,采樣不確定性誤差也是高斯的,就像熱噪聲一樣。最終,時鐘抖動對 ADC 性能的影響主要是 ADC 的本底噪聲增加,隨后是信號鏈的總熱噪聲。圖 1 顯示了由正弦輸入信號上的時鐘抖動引起的采樣邊沿變化。

圖 1.?時鐘信號顯示由抖動引起的采樣邊沿變化

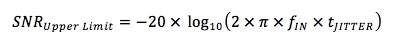

熱噪聲增加的量取決于輸入信號的壓擺率和時鐘源中的時鐘抖動量。您可以使用公式 1 計算 ADC 信噪比 (SNR) 的理論上限:

其中 fIN 是輸入信號頻率,tJITTER 是時鐘源的抖動規范。對于具有較高頻率成分的信號,您可以預期輸入信號壓擺率會更高,而時鐘抖動導致的 SNR 降級會更糟。

過采樣轉換器(如 delta-sigma ADC)的一個主要好處是,理想的 SNR 在使用更高的過采樣率 (OSR) 時會得到改善。過采樣在定義的時間段內平均多次轉換,這反過來又平均了一些由時鐘抖動引起的采樣變化。等式 2 量化了由于過采樣而導致的 SNR 改進,它只是等式 1 的擴展,增加了一個與 Δ-Σ ADC 的 OSR 相關的項:

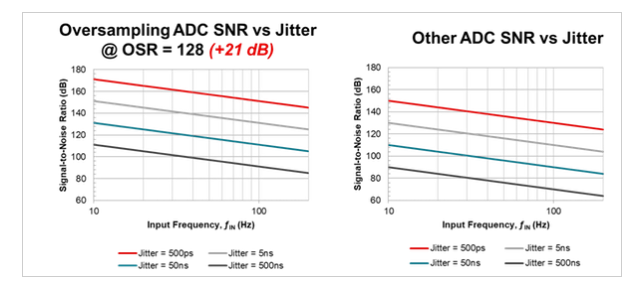

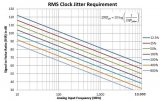

為了直觀顯示具有過采樣和沒有過采樣的 ADC 之間的性能差異,圖 2 繪制了方程 1 和 2 作為輸入信號頻率和抖動的函數。每個圖都包括四種不同時鐘抖動規格(0.5 ns、5 ns、50 ns 和 500 ns)的曲線。圖 2a 表示過采樣 ADC 的 SNR,而圖 2b 表示沒有過采樣架構的 ADC 的 SNR。

圖 2.?過采樣 ADC 的 SNR 圖 (a);和其他 ADC (b)

考慮到過采樣的好處,與圖 2b 中的等效抖動規格曲線相比,圖 2a 中的四個圖提供了 21dB 的 SNR 改進。但是,兩個圖都說明了相同的效果:隨著輸入信號頻率或時鐘抖動量的增加,產生的 SNR 會降低。因此,具有更高 SNR 目標的應用可能需要更昂貴、更高功率的時鐘解決方案來最小化抖動。

例如,德州儀器 (TI)?ADS127L01的評估模塊(EVM)?,一個512kSPS、24 位 delta-sigma ADC,使用 Abracon ASEMB-16.000MHZ-XY-T 低抖動振蕩器。該振蕩器提供 5 ps 的典型周期抖動規格,遠低于圖 2 中繪制的任何抖動規格。但是,如果您考慮低抖動振蕩器的成本與性能權衡,您可能想知道這種選擇是必要的或只是矯枉過正。

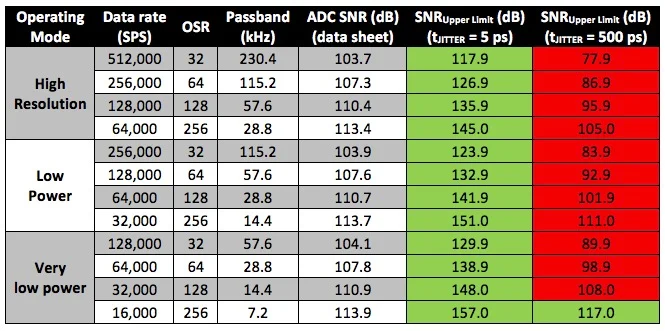

為了幫助回答這個問題,表 1 比較了 ADS127L01 使用“寬帶 1”數字濾波器設置的數據手冊噪聲規范,SNR 上限是針對 5 ps 和 500 ps 時鐘抖動計算得出的。SNR 上限計算使用數字濾波器通帶頻率作為“fIN”來表示最大輸入信號頻率,這是時鐘抖動影響最明顯的地方。

當 tJITTER = 5 ps 時,所有計算出的 SNR 值(以綠色突出顯示)都大于 ADC 的數據手冊 SNR 規格。使用該時鐘源,您可以安全地假設時鐘抖動產生的噪聲不會成為您系統的主要噪聲源。將其與以紅色突出顯示的條目進行比較,表示 SNR 值低于 ADC 的 SNR 規范,所有這些值均針對 tJITTER = 500 ps。在這種情況下,當使用全信號帶寬時,來自時鐘抖動的噪聲實際上會限制 ADC 可實現的 SNR。

表 1. TI 的 ADS127L01“寬帶 1”濾波器 SNR 與 5 ps 和 500 ps 時鐘抖動的 SNRUpper 限制

表 1 和圖 2 的另一個關鍵要點是增加 OSR(相當于降低 ADC 的輸出數據速率)可以進一步提高 SNR 性能。通常,可以支持較慢輸出數據速率的系統正在測量移動較慢的輸入信號。由于時鐘邊沿的輕微變化實際上被“忽視”了,這些系統會因抖動而受到更少的噪聲。

最后,降低時鐘抖動引起的噪聲的另一種方法是選擇使用集成時鐘分頻器產生調制器采樣時鐘的 ADC,例如 ADS131A04。時鐘分頻器僅作用于兩個輸入時鐘邊沿之一(通常是上升沿),以產生不超過原始輸入時鐘頻率一半的輸出時鐘頻率。由于您可以合理地假設兩個輸入時鐘邊沿都存在一些抖動,因此將時鐘一分為二可以有效地降低輸出時鐘上的抖動。如果您繼續多次分頻輸入時鐘,則可以進一步減輕輸入時鐘抖動對 ADC 的影響。

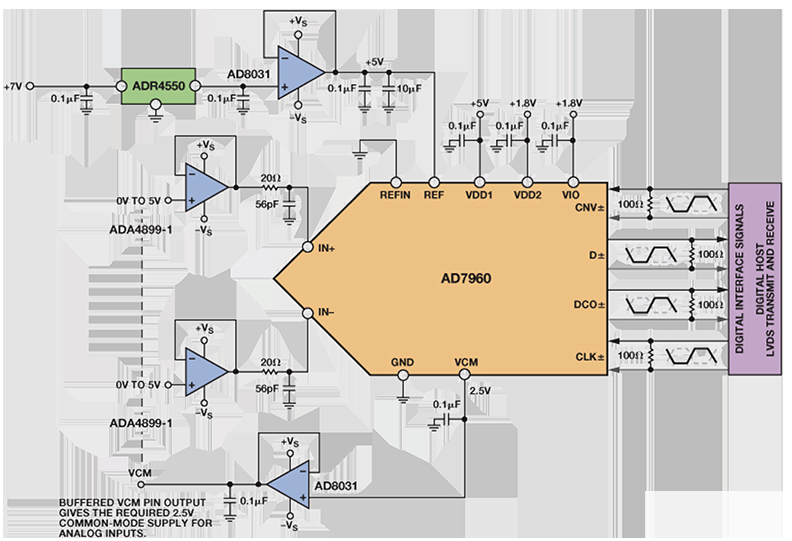

時鐘互調

時鐘源影響 ADC 噪聲性能和增加系統噪聲的另一種方式是通過時鐘互調。幾乎所有 DAQ 系統都有多個需要時鐘輸入的開關組件。在某些情況下,這些時鐘輸入可能需要來自不同時鐘源的不同輸入頻率。

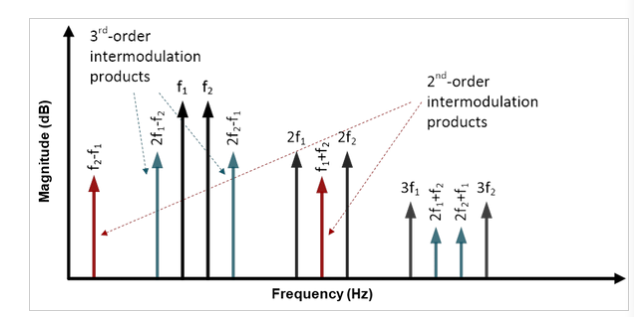

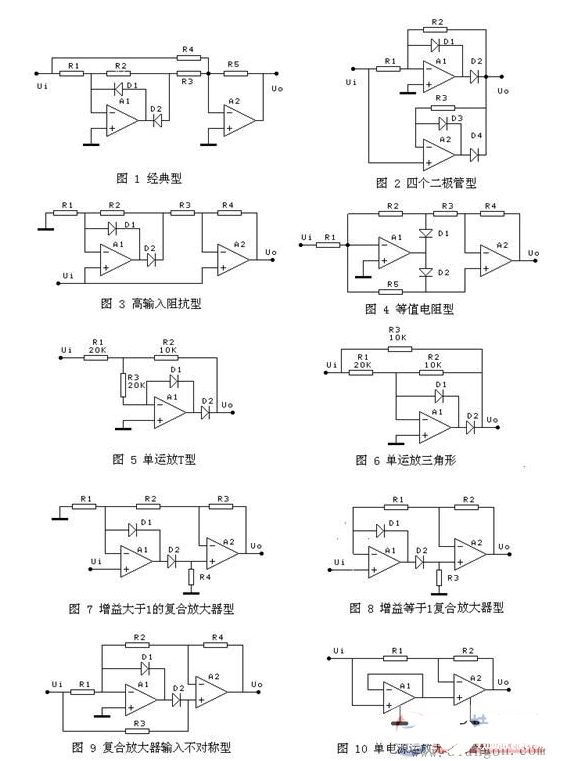

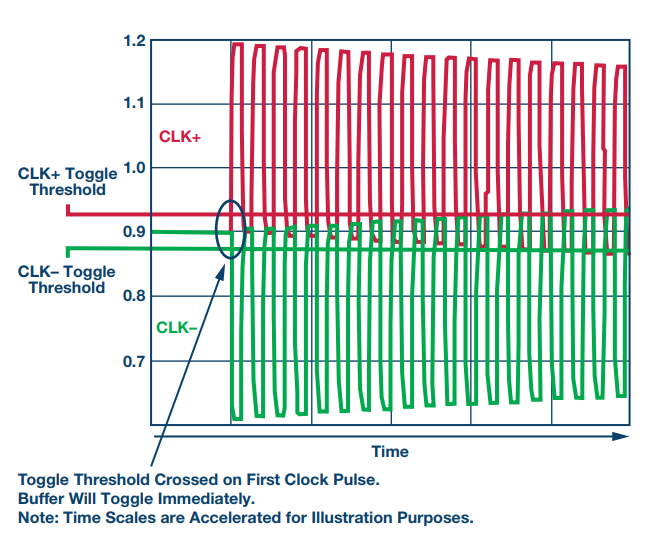

如果這些時鐘源是離散的和異步的,它們可能會相互耦合并在頻譜中產生音調。給定頻率為 F1 和 F2 的兩個時鐘源,它們基頻的差值或總和會產生互調音調。這些被稱為二階互調產物,如圖 3 所示。

圖 3.?異步時鐘源引起的互調產物

此外,基頻與其他互調產物(包括它們的諧波)之間的和或差會產生額外的高階音調。雖然這些音調可能存在于您感興趣的信號帶寬之外,但它們仍然可以混疊到 ADC 通帶中并降低 SNR 和總諧波失真等 AC 規格。

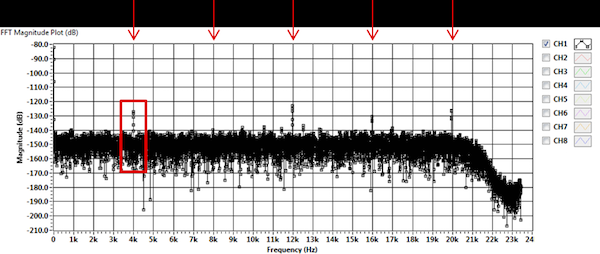

圖 4 中的快速傅立葉變換 (FFT) 說明了這些互調效應。使用具有短路輸入(0-V 差分輸入)的 ADC,處理器時鐘設置為 12 MHz,而 ADC 調制器時鐘降低到 11.996 MHz,產生 4 kHz 的差異。

圖 4.??FFT 顯示了 4 kHz 倍數的互調音

由于處理器和 ADC 時鐘的差異,2 階互調音出現在 4 kHz 的頻譜中,并在 4 kHz 的倍數處產生額外的諧波。這說明了互調產物如何直接落入 ADC 的通帶并產生噪聲。

為了緩解這個問題,寬帶應用通常使用一個時鐘源來生成系統中使用的所有其他頻率,以確保它們都是同步的。另一種有用的緩解技術是選擇在感興趣的信號帶寬內最不可能產生音調的時鐘頻率和采樣率。

時鐘的最佳 PCB 布局實踐

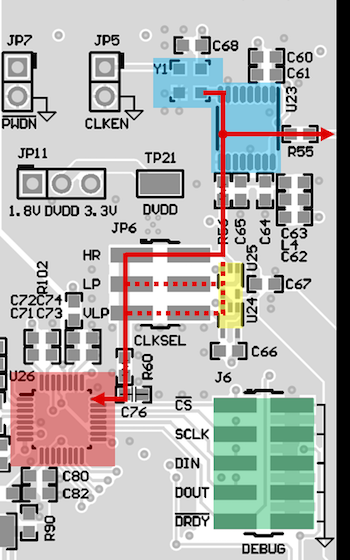

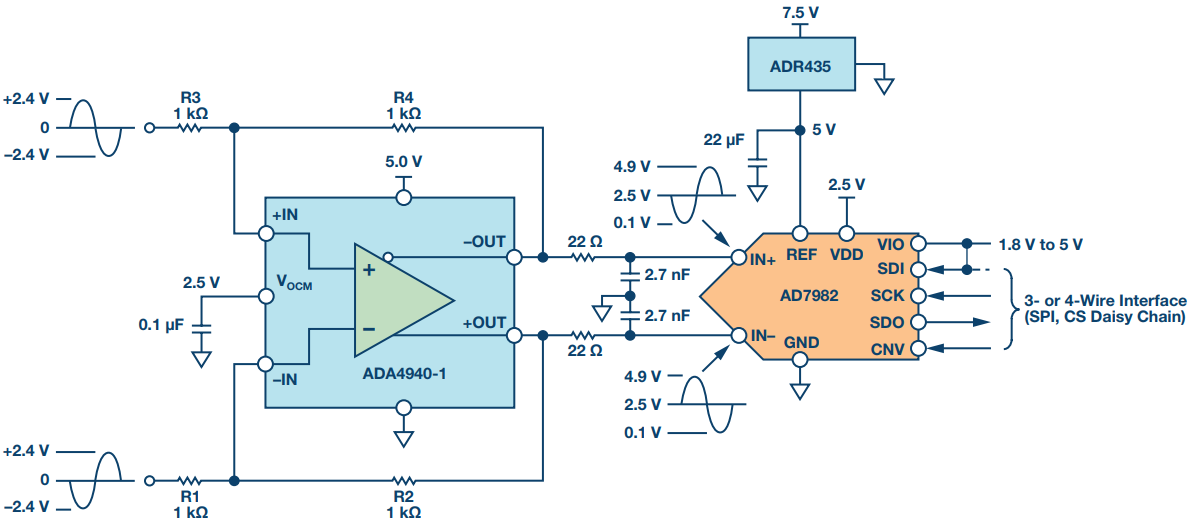

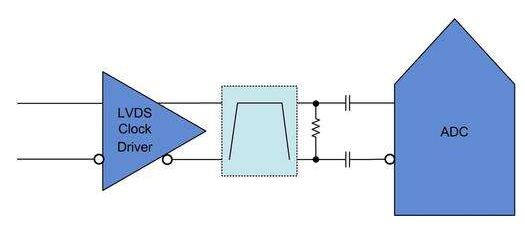

在為您的時鐘源設計 PCB 布局時,請注意保持時鐘信號盡可能干凈。盡管它被視為數字輸入,但將時鐘信號視為另一個重要的模擬信號。最小化走線阻抗,將走線遠離串行外設接口 (SPI) 信號和其他噪聲電路,并考慮包括用于串聯電阻器和并聯電容器的 PCB 封裝,以幫助處理反射或過沖。圖 5 顯示了來自ADS127L01EVM的示例時鐘布局。

圖 5.?示例時鐘布局

圖 5 中的紅線跟蹤從源到 ADC(U26,以紅色突出顯示)的時鐘路徑。時鐘路徑從時鐘源 (Y1) 開始,然后被送入時鐘扇出緩沖器 (U23)。這兩個組件在圖 5 的右上角以藍色突出顯示。時鐘扇出緩沖器生成原始輸入時鐘頻率的兩個相同副本:一個用于驅動 ADC,另一個用于驅動微控制器(通過 R55)。

為了進入 ADC,時鐘信號繼續通過一個與時鐘緩沖器輸出串聯的 43 Ω 小電阻器 (R56),以幫助抑制反射。然后時鐘信號連接到跳線 (JP6),該跳線選擇三個不同的 ADC 時鐘頻率之一。另外兩個時鐘頻率由兩個 D 觸發器(U24 和 U25,在圖 5 中以黃色突出顯示)產生。這些組件對時鐘緩沖器輸出進行分頻以產生用于其他兩種模式的時鐘:“低功耗”(LP) 模式和“極低功耗”(VLP) 模式。所有三種模式選擇也與原始時鐘源同步。在圖 5 中,紅色實線穿過“高分辨率”(HR) 模式選擇。

在跳線之后,選定的時鐘信號在到達 ADC 時鐘引腳之前通過另一個電阻器 (R60) 和一個并聯電容器 (C76)。路徑盡可能短且直接。SPI 接口信號(以綠色突出顯示)也遠離時鐘輸入,直到它們到達 ADC。

獲得最佳性能的其他時鐘提示

如果您遵循此處提供的時鐘布局指南,但仍懷疑您的時鐘正在降低 ADC 性能,則需要測試一些其他與時鐘相關的問題。

ADC 輸入端的時鐘信號質量?

如果 ADC 時鐘輸入引腳上的時鐘信號顯示過度的過沖和振鈴,您可能需要通過添加或增加小型串聯電阻器和并聯電容器(分別為圖 5 中的 R60 和 C76)的大小來進一步壓擺時鐘邊沿。添加這些組件可以有效地將低通濾波器應用于時鐘輸入,同時保留基本時鐘頻率。

您可能還會注意到時鐘邊沿中的“擱架”或“階梯”。這是由時鐘信號沿走線傳輸并進入高阻抗輸入時的反射引起的。串聯電阻器將有助于抑制這些時鐘反射。

ADC 上的電源引腳

因為 ADC 的 DVDD 輸入和時鐘源或時鐘緩沖器可能共享同一個數字電源,所以檢查這些引腳是否有大的瞬變。瞬態由電流的突然需求引起,可能需要額外的去耦電容器來抑制。但是在選擇去耦電容器的尺寸時要小心:較小的去耦電容器具有較小的電感并且可以更快地提供必要的電流,而較大的去耦電容器有助于存儲大部分必要的電荷并過濾電源軌上的任何噪聲。可能需要結合使用兩種尺寸的去耦電容器來保持數字電源的安靜和穩定。

另一種有助于減少耦合到 ADC 輸出的瞬變的技術是在 ADC 數字電源引腳和時鐘源或時鐘緩沖器電源引腳之間放置一個小鐵氧體磁珠。

分割地平面

如果您的 PCB 尺寸不允許將時鐘電路放置在遠離敏感模擬電路的地方,則可能有助于部分分離接地以隔離時鐘電流的返回路徑。但是,應始終將接地層的兩側盡可能靠近器件,以避免 ADC 的模擬部分和數字部分之間出現顯著的接地電位差。

消除時鐘源噪聲的信號鏈

最終,遵循本文中推薦的做法和程序應該有助于避免最常見的時鐘相關問題,并確保您的時鐘源不是信號鏈噪聲的最大貢獻者。

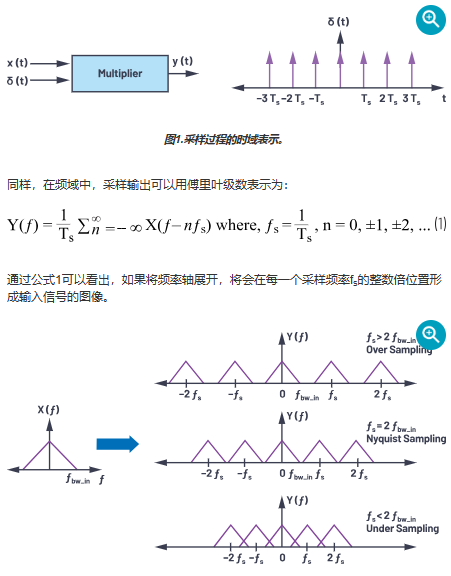

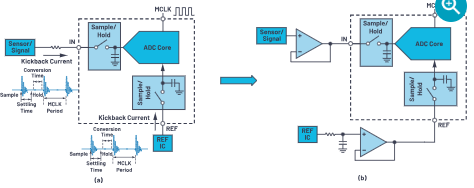

從基礎到高級的ADC講座,將涵蓋高速ADC設計的原理、傳統架構和最先進的設計。第一部分首先回顧了ADC的基本知識,包括采樣、開關電容和量化理論。接下來,介紹了經典ADC架構的基礎和設計實例,如閃存、SAR和流水線ADC。然后,本教程將對混合型ADC架構進行總體概述,這就結束了第一部分。在第二部分,首先描述了ADC的度量。然后,介紹混合或非混合架構的各種先進設計。該教程最后將以數字輔助解決技術結束。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論