本文的目的是介紹高速ADC相關(guān)的理論和知識(shí),詳細(xì)介紹了采樣理論、數(shù)據(jù)手冊(cè)指標(biāo)、ADC選型準(zhǔn)則和評(píng)估方法、時(shí)鐘抖動(dòng)和其它一些通用的系統(tǒng)級(jí)考慮。 另外,一些用戶希望通過交織、平均或抖動(dòng)(dithering)技術(shù)進(jìn)一步提升ADC的性能。

引言

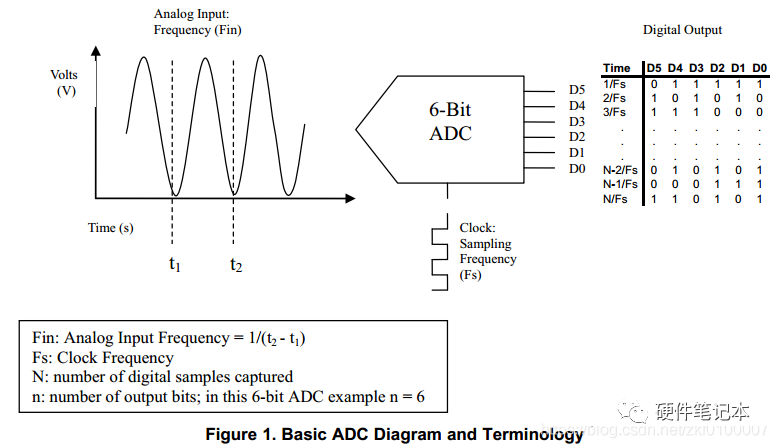

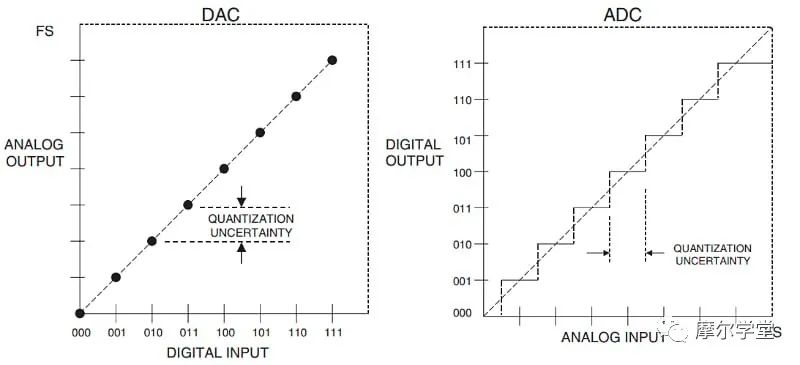

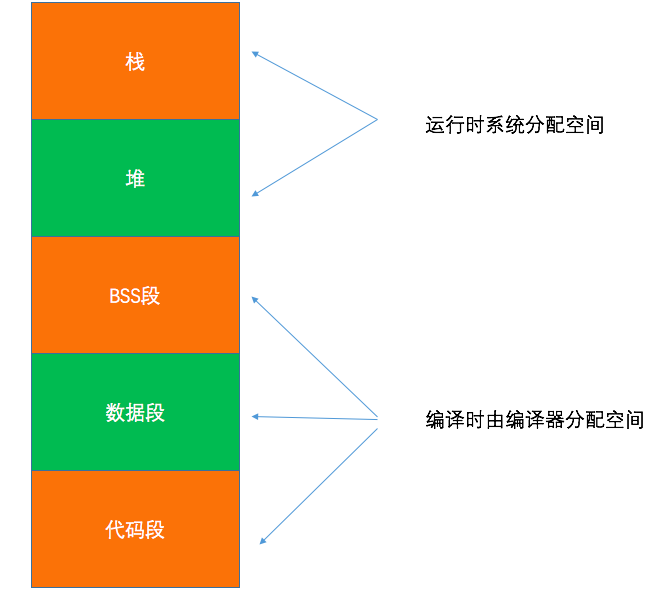

基本的ADC框圖和術(shù)語如下圖所示:

隨著數(shù)字信號(hào)處理技術(shù)和數(shù)字電路工作速度的提高,以及對(duì)于系統(tǒng)靈敏度等要求的不斷提高,對(duì)于高速、高精度的 ADC(Analog to Digital Converter)、DAC(Digital to Analog Converter)的指標(biāo)都提出了很高的要求。 比如在雷達(dá)和衛(wèi)星通信中,所需要的信號(hào)帶寬已經(jīng)達(dá)到了 2 GHz 以上,而下一代的 5G 移動(dòng)通信技術(shù)在使用毫米波頻段時(shí)也可能會(huì)用到 2 GHz 以上的信號(hào)帶寬。 雖然有些場合(比如線性調(diào)頻雷達(dá))可能采用頻段拼接的方式去實(shí)現(xiàn)高的帶寬,但是畢竟拼接的方式比較復(fù)雜,而且對(duì)于通信或其它復(fù)雜調(diào)制信號(hào)的傳輸也有很多限制。

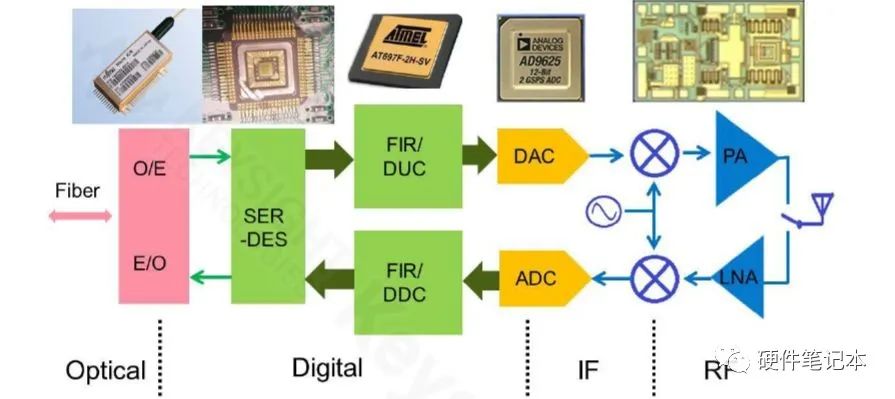

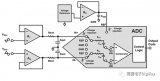

根據(jù) Nyquist 采樣定律,采樣率至少要是信號(hào)帶寬的 2 倍以上。 同時(shí)為了支持靈活的制式、相控陣或大規(guī)模 MIMO 的波束賦形,現(xiàn)代的收發(fā)機(jī)模塊越來越普遍采用數(shù)字中頻直接采樣,這其實(shí)進(jìn)一步提高了對(duì)于高速 ADC/DAC 芯片的性能要求。 下圖是一個(gè)典型的全數(shù)字雷達(dá)收發(fā)信機(jī)模塊的結(jié)構(gòu)。 高速數(shù)字化儀和多通道數(shù)據(jù)采集解決方案 | Keysight根據(jù) Nyquist 采樣定律,采樣率至少要是信號(hào)帶寬的 2 倍以上。 同時(shí)為了支持靈活的制式、相控陣或大規(guī)模 MIMO 的波束賦形,現(xiàn)代的收發(fā)機(jī)模塊越來越普遍采用數(shù)字中頻直接采樣,這其實(shí)進(jìn)一步提高了對(duì)于高速 ADC/DAC 芯片的性能要求。 下圖是一個(gè)典型的全數(shù)字雷達(dá)收發(fā)信機(jī)模塊的結(jié)構(gòu)。

高速 ADC/DAC 在現(xiàn)代全數(shù)字雷達(dá)中的應(yīng)用

可以看到,ADC/DAC 芯片是模擬域和數(shù)字域的邊界。 一旦信號(hào)轉(zhuǎn)換到數(shù)字域,所有的信號(hào)都可以通過軟件算法進(jìn)行處理和補(bǔ)償,而且這個(gè)處理過程通常不會(huì)引起額外的噪聲和信號(hào)失真,因此把 ADC/DAC 芯片前移、實(shí)現(xiàn)全數(shù)字化處理是現(xiàn)代通信、雷達(dá)技術(shù)的發(fā)展趨勢。

在全數(shù)字化的發(fā)展過程中,ADC/DAC 芯片需要采樣或者輸出越來越高的頻率、越來越高帶寬的信號(hào)。 而在模擬到數(shù)字或者數(shù)字到模擬的轉(zhuǎn)換過程中造成的噪聲和信號(hào)失真通常是很難補(bǔ)償?shù)模⑶視?huì)對(duì)系統(tǒng)性能造成重大影響。 所以,高速 ADC/DAC 芯片在采樣或者產(chǎn)生高頻信號(hào)時(shí)的性能對(duì)于系統(tǒng)指標(biāo)至關(guān)重要。

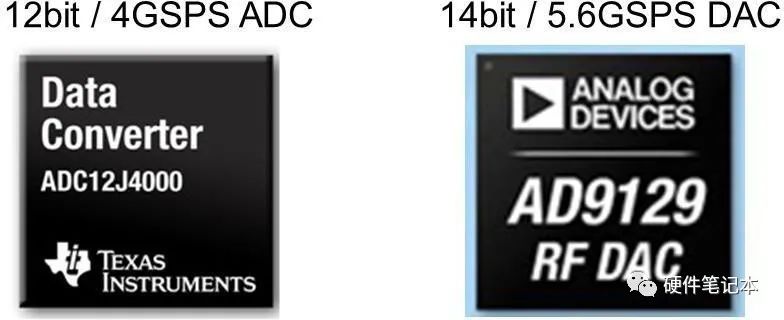

目前在很多專用領(lǐng)域,使用的 ADC/DAC 的采樣率可以達(dá)到非常高的程度。 比如 Fujitsu 公司可以提供 110G~130GHz 的 IP 核,Keysight 公司在高精度示波器里用到了單片 40GHz 采樣率、10bit 的 ADC 芯片,以及 Keysight 公司在高帶寬任意波發(fā)生器里用到了 92GHz 采樣率、8bit 的 DAC 芯片等。 這些專用的芯片通常用于特殊應(yīng)用,比如光通信或者高端儀表等,比較難以單獨(dú)獲得。

在商用領(lǐng)域,很多 ADC/DAC 芯片的采樣率也都已經(jīng)達(dá)到了 GHz 以上,比如 TI 公司的 ADC 12J4000 是 4 GHz 采樣率、12bit 分辨率的高速 ADC 芯片; 而 ADI 公司的 AD9129 是 5.6 GHz 采樣率、14 bit 分辨率的高速 DAC 芯片。 這一方面要求 ADC 有比較高的采樣率以采集高帶寬的輸入信號(hào),另一方面又要有比較高的位數(shù)以分辨細(xì)微的變化。

隨著 ADC/DAC 的采樣率的提高,高速 ADC/DAC 的數(shù)字側(cè)的接口技術(shù)也在發(fā)生著比較大的變化。

低速串行接口:很多低速的 ADC/DAC 芯片采用 I2C 或 SPI 等低速串行總線把多路并行的數(shù)字信號(hào)復(fù)用到幾根串行線上進(jìn)行傳輸。 由于 I2C 或 SPI 總線的傳輸速度大部分在10Mbps 以下,所以這種接口主要適用于MHz 以下采樣率的ADC/DAC 芯片。

并行 LVCMOS 或 LVDS 接口:對(duì)于幾 MHz 甚至幾百 MHz 采樣率的芯片來說,由于信號(hào)復(fù)用后數(shù)據(jù)速率太高,所以基本上采用并行的數(shù)據(jù)傳輸方式,即每位分辨率對(duì)應(yīng) 1 根數(shù)據(jù)線(比如 14 位的 ADC 芯片就采用 14 根數(shù)據(jù)線),然后這些數(shù)據(jù)線共用 1 根時(shí)鐘線進(jìn)行信號(hào)傳輸。 這種方法的好處是接口時(shí)序比較簡單, 但是由于每 1 位分辨率就要占用 1 根數(shù)據(jù)線,所以占用芯片管腳較多。

JESD204B 串行接口:對(duì)于更高速率的 ADC/DAC 芯片來說,由于采樣時(shí)鐘頻率更高,時(shí)序裕量更小,采用并行 LVCMOS 或 LVDS 接口的布線難度很大,而且占用的布線空間較大。 為了解決這個(gè)問題,目前更高速和小型化的ADC/DAC 芯片都開始采用串行的JESD204B 接口。 JESD204B 接口是把多位要傳輸?shù)臄?shù)據(jù)合并到一對(duì)或幾對(duì)差分線上,同時(shí)采用現(xiàn)在成熟的 Serdes(串行-解串行)技術(shù)用數(shù)據(jù)幀的方式進(jìn)行信號(hào)傳輸,每對(duì)差分線都有獨(dú)立的 8b/10b 編碼和時(shí)鐘恢復(fù)電路。 采用這種方法有幾個(gè)好處:首先數(shù)據(jù)傳輸速率更高,每對(duì)差分線按現(xiàn)在的標(biāo)準(zhǔn)最高可以實(shí)現(xiàn) 12.5 Gbps 的信號(hào)傳輸,可以用更少的線對(duì)實(shí)現(xiàn)高速數(shù)據(jù)傳輸; 其次各對(duì)線不再共用采樣時(shí)鐘,這樣對(duì)于各對(duì)差分線間等長的要求大大放寬; 借用現(xiàn)代 Serdes 芯片的預(yù)加重和均衡技術(shù)可以實(shí)現(xiàn)更遠(yuǎn)距離的信號(hào)傳輸,甚至可以直接把數(shù)據(jù)直接調(diào)制到光上進(jìn)行遠(yuǎn)距離傳輸; 可以靈活更換芯片,通過調(diào)整JESD204B 接口里的幀格式,同一組數(shù)字接口可以支持不同采樣率或分辨率的ADC 芯片,方便了系統(tǒng)更新升級(jí)。

ADC 的主要性能指標(biāo)分為靜態(tài)和動(dòng)態(tài)兩部分:

主要靜態(tài)指標(biāo):

微分非線性 (DNL)

積分非線性 (INL)

失調(diào)誤差

主要?jiǎng)討B(tài)指標(biāo):

總諧波失真 (THD)

信噪比加失真 (SINAD)

有效位數(shù) (ENOB)

信噪比 (SNR)

無雜散動(dòng)態(tài)范圍 (SFDR)

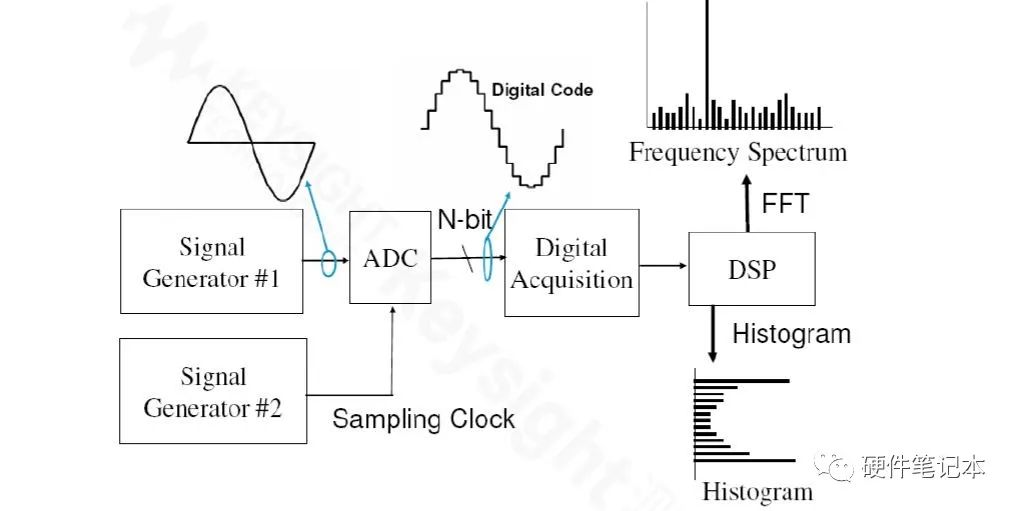

要進(jìn)行 ADC 這些眾多指標(biāo)的驗(yàn)證,可用的方法很多。 最常用的方法是給 ADC 的輸入端提供一個(gè)理想的正弦波信號(hào),然后對(duì) ADC 對(duì)這個(gè)信號(hào)采樣后的數(shù)據(jù)進(jìn)行采集和分析。 因此,ADC 的性能測試需要多臺(tái)儀器的配合并用軟件對(duì)測試結(jié)果進(jìn)行分析。 下圖是最常用的進(jìn)行ADC 性能測試的方法。

在測試過程中,第 1 個(gè)信號(hào)發(fā)生器用于產(chǎn)生正弦波被測信號(hào),第 2 個(gè)信號(hào)發(fā)生器用于產(chǎn)生采樣時(shí)鐘,采樣后的數(shù)字信號(hào)經(jīng) FFT 處理進(jìn)行頻譜分析和計(jì)算得到動(dòng)態(tài)指標(biāo),經(jīng)過直方圖統(tǒng)計(jì)得到靜態(tài)指標(biāo)。

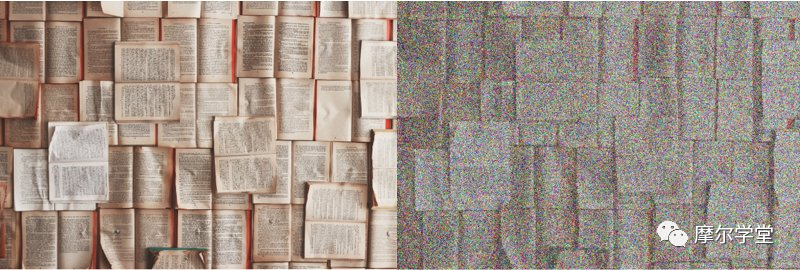

靜態(tài)指標(biāo)是對(duì)正弦波的采樣數(shù)據(jù)進(jìn)行幅度分布的直方圖統(tǒng)計(jì),然后間接計(jì)算得到。 如下圖所示,理想正想波的幅度分布應(yīng)該是左面的形狀,由于非線性等的影響,分布可能會(huì)變成右邊的形狀,通過對(duì)實(shí)際直方圖和理想直方圖的對(duì)比計(jì), 可以得出靜態(tài)參數(shù)的指標(biāo)。

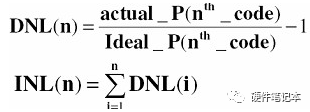

以下是 DNL 和 INL 的計(jì)算公式:

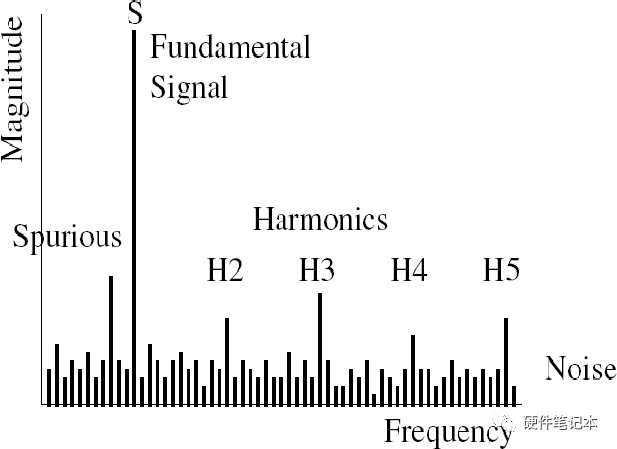

動(dòng)態(tài)指標(biāo)是對(duì)正弦波的采樣數(shù)據(jù)進(jìn)行 FFT 頻譜分析,然后計(jì)算頻域的失真間接得到。 一個(gè)理想的正弦波經(jīng) A/D 采樣,再做后頻譜分析可能會(huì)變成如下圖的形狀。 除了主信號(hào)以外,由于ADC 芯片的噪聲和失真,在頻譜上還額外產(chǎn)生了很多噪聲、諧波和雜散,通過對(duì)這些分量的運(yùn)算,可以得到ADC 的動(dòng)態(tài)參數(shù)。

通過 FFT 頻譜分析測試動(dòng)態(tài)參數(shù)

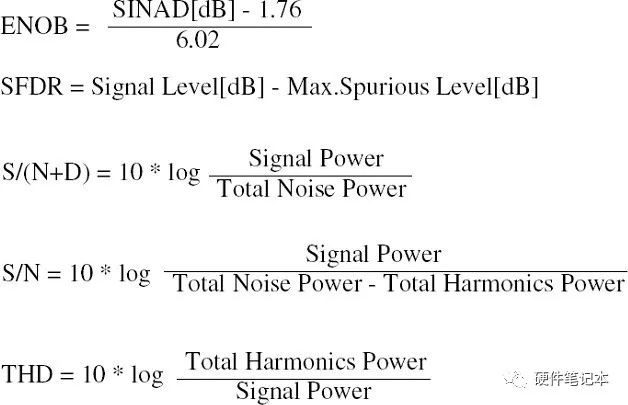

下面是動(dòng)態(tài)參數(shù)的計(jì)算公式:

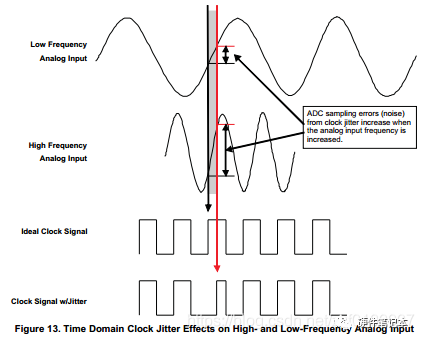

對(duì)于產(chǎn)生被測信號(hào)和采樣時(shí)鐘的信號(hào)發(fā)生器來說,為了得到比較理想的測試效果, 要求其時(shí)間抖動(dòng)(或者相位噪聲)性能要足夠小,因?yàn)椴蓸訒r(shí)鐘的抖動(dòng)會(huì)造成采樣 位置的偏差,而采樣位置的偏差會(huì)帶來采樣幅度的偏差,從而帶來額外的噪聲,從 而制約信噪比的測量結(jié)果。 下圖是時(shí)鐘或者信號(hào)抖動(dòng)引起信噪比惡化的示意圖,以 及根據(jù)信噪比要求及輸入信號(hào)頻率計(jì)算信號(hào)抖動(dòng)要求的公式。

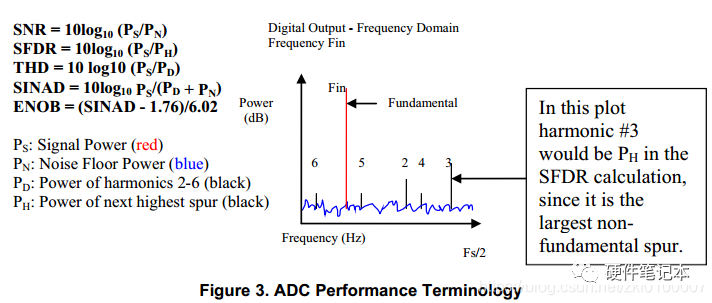

頻譜性能術(shù)語

SNR:信噪比,是指基頻功率與除去直流及前5次諧波的噪底功率之比,有些數(shù)據(jù)手冊(cè)可能是要除掉前9次諧波。 基頻也叫信號(hào)或者載波。 SNR的單位是dBc(當(dāng)用基頻的絕對(duì)作參考時(shí)); 或者dBFS。

SFDR:無雜散動(dòng)態(tài)范圍。 SFDR是基頻功率與最高的雜散功率之比。

THD:總諧波失真。 THD是基頻功率與前5次諧波功率之比。 THD在單位通常是dBc。 與SNR類似,有的數(shù)據(jù)手冊(cè)可能取前9次諧波來計(jì)算THD。

SINAD:信號(hào)噪聲與失真。 SINAD的單位可能是dBc或者dBFS。

ENOB:有效位數(shù)。

理想SNR=6.02*n+1.76,當(dāng)n=ENOB時(shí),理想SNR=SNR。 對(duì)于理想ADC而言,由于沒有諧波,其SINAD=SNR。

例如,設(shè)計(jì)師需要一個(gè)SINAD為75dB的ADC,則ENOB=(75-1.76)/6.02=12.2bits,那么至少要選14位甚至16位的ADC才能滿足要求。

奈奎斯特、混疊、欠采樣、過采樣和帶寬

根據(jù)奈奎斯特采樣定理,采樣時(shí)鐘頻率至少是輸入模擬信號(hào)頻率的2倍。

過采樣:采樣頻率大于信號(hào)頻率的2倍,即FIN

欠采樣:信號(hào)頻率大于奈奎斯特頻率。 此時(shí),會(huì)導(dǎo)致混疊。

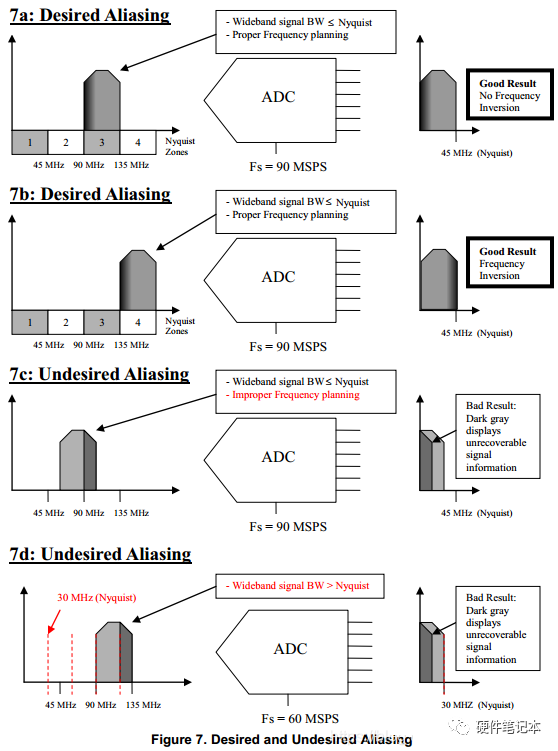

混疊并非一無是處,它可以將高頻信號(hào)混頻到低頻信號(hào),可以省去額外的混頻器,以減少系統(tǒng)功耗和成本,但前提是必須慎重考慮頻率規(guī)劃和ADC選型。

從上圖可知,在ADC選型時(shí),需要考慮如下兩點(diǎn):

A:ADC滿足期望的頻率規(guī)劃

B:輸入模擬信號(hào)的帶寬小于ADC的奈奎斯特頻率

另外,ADC的帶寬還要滿足輸入模擬信號(hào)的頻率需求。

4.ADC管腳接口

一般來說,ADC包括以下6種接口:

模擬輸入

參考/共模模式

時(shí)鐘輸入

數(shù)字輸出

GND

4.1模擬輸入

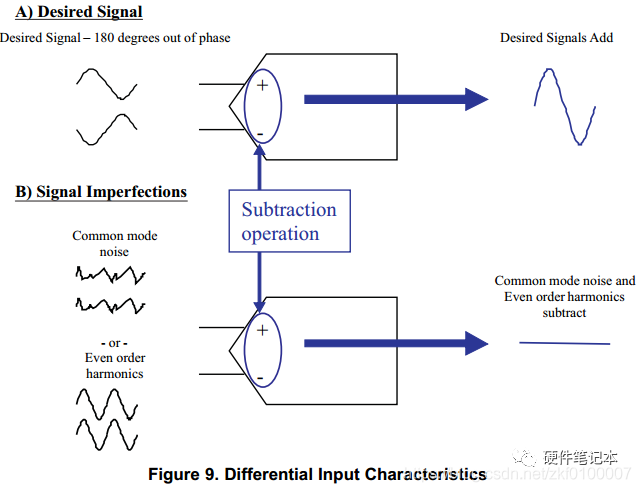

高速ADC通常采用差分輸入,輸入信號(hào)是180度反相的,使得信號(hào)是疊加的。 與單端輸入相比,由于消除了共模噪聲,差分信號(hào)改善了ADC的噪聲特性。 此外,差分信號(hào)還降低了偶次諧波,這是由于信號(hào)被偏移了180度,對(duì)于偶次諧波,導(dǎo)致2x180,4X180,6X180度的相移,如下圖所示

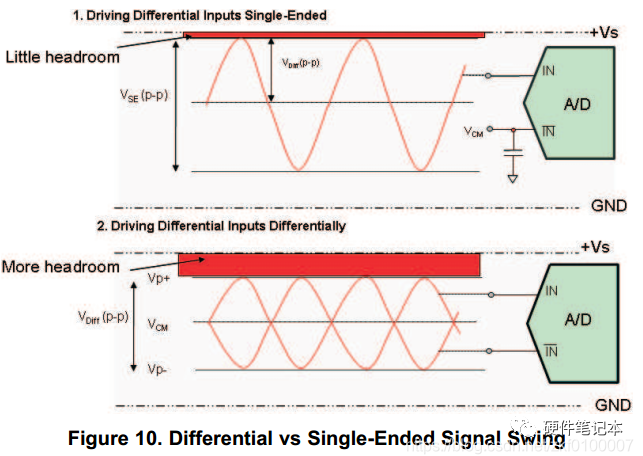

與單端信號(hào)相比,差分信號(hào)的幅度僅于等效單端信號(hào)的一半,從而差分信號(hào)具有更優(yōu)的諧波性能。 小信號(hào)使得ADC具有更寬的裕量。 一般而言,更多的裕量可以使ADC工作在線性區(qū)域,減少產(chǎn)生諧波的非線性影響。 如下圖所示:

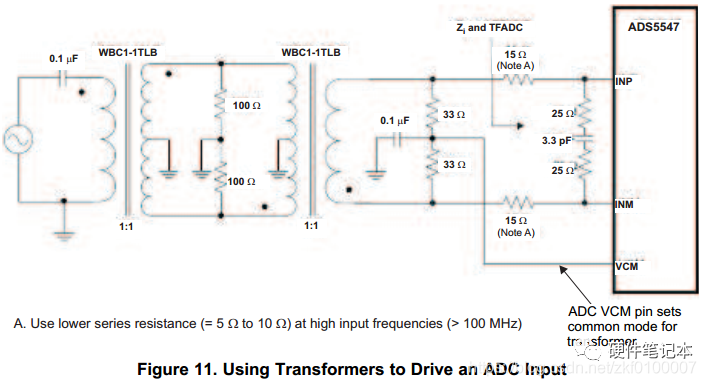

下圖所示為雙變壓器ADC輸入接口,變壓器用于將單端信號(hào)轉(zhuǎn)換成差分信號(hào)。

單變壓器會(huì)有少量的不匹配,會(huì)產(chǎn)生偶次諧波。 第二級(jí)變壓器用于校正這種不匹配,以降低偶次諧波。 在高頻信號(hào)時(shí),采用變壓器可以獲得較高的性能。 但是,對(duì)于基帶信號(hào)或者低頻信號(hào),通常采用運(yùn)放驅(qū)動(dòng)ADC輸入。

4.2參考/共模模式

參考電壓和共模電壓在ADC中具有不同功能。 在許多ADC中,參考電壓和共模電壓具有相同的電平,或者有時(shí)ADC管腳會(huì)復(fù)用參考電壓和共模電壓功能。 因此,這些信號(hào)術(shù)語有時(shí)會(huì)導(dǎo)致誤解。

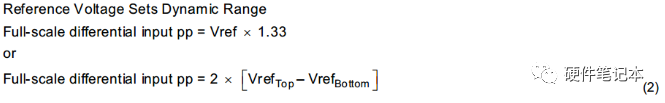

參考電壓決定的ADC的動(dòng)態(tài)范圍。 數(shù)據(jù)手冊(cè)通常會(huì)提供參考電壓和動(dòng)態(tài)范圍的關(guān)系。

參考電壓可以由ADC內(nèi)部生成,或者外部提供。 為了獲得數(shù)據(jù)手冊(cè)標(biāo)注的性能,需要提供正確的參考電壓。 對(duì)于外部參考,應(yīng)盡量降低外部參考電壓的直流噪聲。 參考電壓上的噪聲會(huì)直接影響ADC的SNR。

圖11中,共模電壓VCM是指輸入到差分模擬輸入信號(hào)的直流電平。 VCM用于將將差分輸入信號(hào)偏置在電源和GND的中間。

VCM有以下幾種應(yīng)用方式:

有些ADC有VCM管腳,輸出內(nèi)部產(chǎn)生的VCM

有些ADC將VREF設(shè)置成與VCM相同的電平,因此,VREF可用于生成VCM

設(shè)計(jì)師可選擇外部提供VCM

對(duì)于外部產(chǎn)生的VCM,必須保證其電平與數(shù)據(jù)手冊(cè)要求一致,錯(cuò)誤的VCM電平會(huì)降低ADC的SNR。

4.3時(shí)鐘輸入/抖動(dòng)

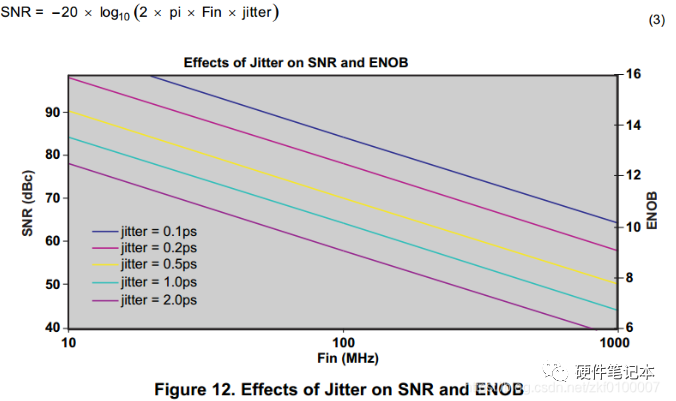

高速ADC通常采用差分時(shí)鐘輸入。 時(shí)鐘抖動(dòng)及斜率是影響ADC的SNR的重要因素。 時(shí)鐘抖動(dòng)對(duì)SNR的影響如下所示:

由上可知,對(duì)于理想ADC,時(shí)鐘頻率并不會(huì)影響SNR。 若不考慮時(shí)鐘抖動(dòng),時(shí)鐘頻率達(dá)到ADC設(shè)計(jì)極限(諸如建立、保持或模擬建立時(shí)間),從而最終導(dǎo)致SNR下降。

抖動(dòng)不變時(shí),SNR隨輸入信號(hào)頻率增加而降低。

由上圖所示,指定時(shí)鐘抖動(dòng)時(shí),SNR隨信號(hào)頻率增加而降低。 高頻模擬輸入信號(hào)對(duì)于時(shí)鐘抖動(dòng)有較大的誤差。 如果時(shí)鐘信號(hào)上有隨機(jī)噪聲,會(huì)表現(xiàn)在頻譜圖上。 如果時(shí)鐘信號(hào)上有確定的誤差信號(hào),這個(gè)信號(hào)會(huì)與ADC的輸入信號(hào)混合在一起,在頻譜圖上表現(xiàn)為雜散。

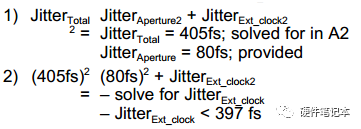

設(shè)計(jì)師必須考慮時(shí)鐘抖動(dòng)的兩個(gè)重要因素。 其一是ADC的孔徑延遲,其二是外部輸入時(shí)鐘的抖動(dòng)。 這兩個(gè)因素共同產(chǎn)生的抖動(dòng)影響ADC的采樣誤差。

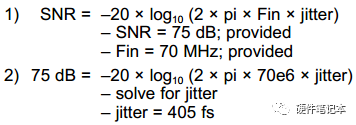

設(shè)計(jì)實(shí)例:

設(shè)計(jì)需求如下:

SNR=75dB

FIN=75MHz

客戶選定的ADC其孔徑抖動(dòng)=80fs

為了滿足客戶的SNR需求,客戶應(yīng)用所能容忍的最大抖動(dòng)是多少?

A:用公式3求解抖動(dòng)

B:用公式4求解外部時(shí)鐘抖動(dòng)

因此,外部輸入時(shí)鐘抖動(dòng)必須小于397fs。

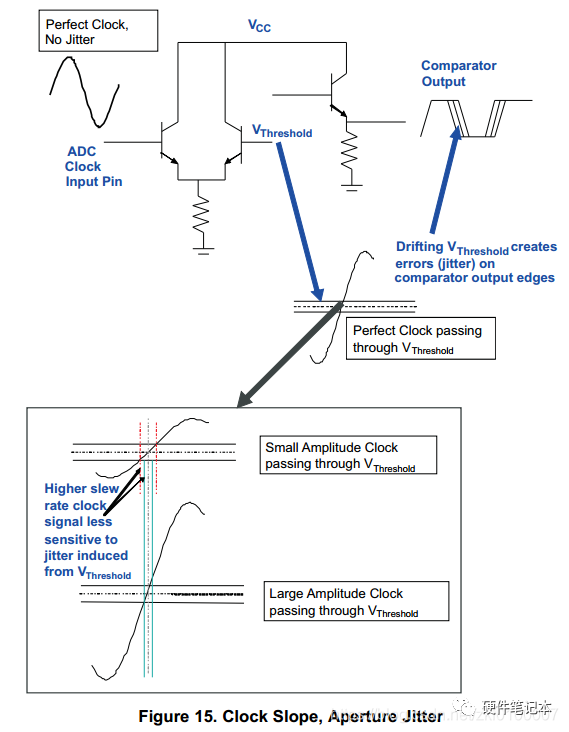

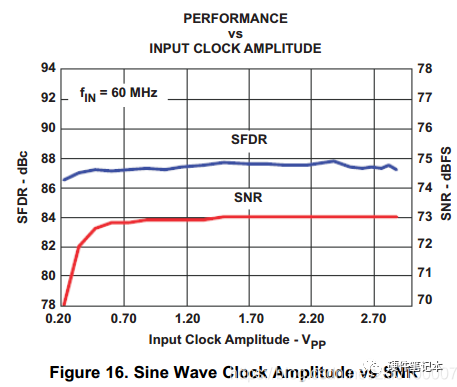

下圖展示了慢時(shí)鐘沿導(dǎo)致較大的孔徑抖動(dòng)的情形。 對(duì)于正弦時(shí)鐘,增大時(shí)鐘幅度可以改善孔徑抖動(dòng)進(jìn)而提高ADC的SNR。

正弦波幅度與SNR的關(guān)系如下圖所示:

那么問題來了,如果關(guān)注時(shí)鐘上升斜坡,那為什么不直接給ADC提供方波時(shí)鐘信號(hào)? 答案是:方波時(shí)鐘確實(shí)是一個(gè)可行的ADC時(shí)鐘選擇。 但是,設(shè)計(jì)者必須在正弦和方波之間做出一系列的折衷。

其一是低抖動(dòng)方波時(shí)鐘與時(shí)鐘頻率范圍間的折衷。 對(duì)于大多數(shù)應(yīng)用,通過窄帶SAW或晶體濾波器以改進(jìn)ADC時(shí)鐘的close-in相位噪聲(抖動(dòng))。 濾波后,時(shí)鐘變成低抖動(dòng)正弦時(shí)鐘,可以直接提供給ADC。 這種方法的局限在于時(shí)鐘頻率范圍受限于濾波器帶寬。 一些公司有時(shí)鐘抖動(dòng)清除及時(shí)鐘分配芯片,這些芯片具有較好的相噪性能、方波輸出和較寬的頻率范圍,其相噪特性足以滿足系統(tǒng)需求,而不需要額外濾波器。

其二是方波時(shí)鐘與正弦時(shí)鐘在信號(hào)完整性方面的折衷。 與正弦信號(hào)相比,方波信號(hào)具有豐富的諧波,具有高頻分量。 由于信號(hào)反射及對(duì)其它信號(hào)的干擾,高頻分量會(huì)對(duì)電路設(shè)計(jì)帶來較大困難。 不管采用哪種時(shí)鐘信號(hào),必須對(duì)電路設(shè)計(jì)著重考慮,以滿足ADC的抖動(dòng)需求。

4.4實(shí)驗(yàn)評(píng)估

ADC的實(shí)驗(yàn)評(píng)估主要包括軟件和硬件兩個(gè)方面。

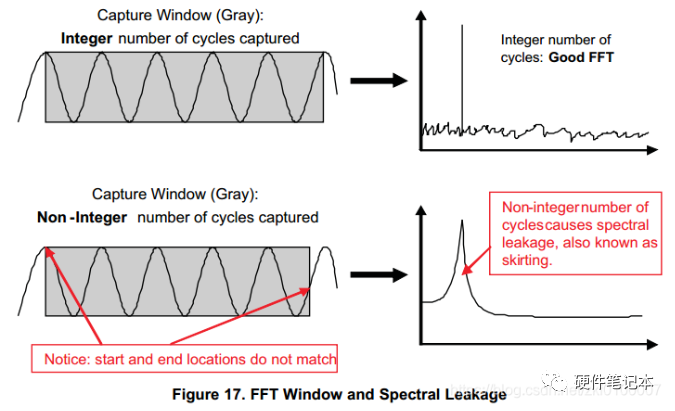

ADC實(shí)驗(yàn)評(píng)估的軟件手段主要是FFT。 由于其高速及準(zhǔn)確性,F(xiàn)FT是時(shí)域到頻域變換的卓越評(píng)估工具。

要實(shí)現(xiàn)FFT,必須理解一致性、加窗和頻譜泄漏等概念。

下圖顯示了加窗和頻譜泄漏。 窗口選擇不當(dāng)會(huì)導(dǎo)致頻譜泄漏。

某些設(shè)計(jì)者需要非整數(shù)個(gè)周期。 在這些特殊情況下,由于頻譜泄漏,不能使用FFT,可以使用布萊克曼窗或者傅利葉分析。 這種方法允許采集非整數(shù)個(gè)周期信號(hào),但是需要更多計(jì)算時(shí)間并且會(huì)對(duì)噪底計(jì)算和頻率響應(yīng)引入少量誤差。

FFT一致性定義如下:

上式中的參數(shù)需遵循以下規(guī)則:

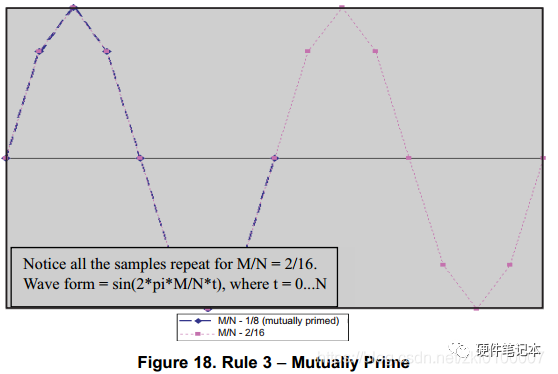

規(guī)則1:M是奇整數(shù)。 M為整數(shù)是為了避免頻譜泄漏,奇數(shù)的要求是由于規(guī)則3。

規(guī)則2:N是2的冪。 FFT的點(diǎn)數(shù)必須是2的冪,通常是4096,8192,16384,32768或65536。 選擇N時(shí),需要在計(jì)算時(shí)間、測量重復(fù)性等因素之間做權(quán)衡。

規(guī)則3:M和N是互質(zhì)數(shù)。 M和N互質(zhì)是為了保證采集到非重復(fù)數(shù)的樣本。 由于FFT的特性,重復(fù)樣本除了帶來額外的計(jì)算量外,并不能提供更多的有用信息。 由于N是2的冪,若限定M是奇整數(shù),則可保證M和N互質(zhì)。

規(guī)則4:FIN與FS的分辨率須大于輸入源的最小分辨率要求。 例如,模擬輸入和時(shí)鐘源的最小分辨率為10Hz,則它們不能被設(shè)置為小于10Hz的分辨率。 在做FFT時(shí),如果頻率分辨率小于輸入源的分辨率,會(huì)采集到非整數(shù)個(gè)周期,進(jìn)而引起頻譜泄漏。

設(shè)計(jì)實(shí)例:

需求如下:

Fin=70MHz

Fs=125Msps

分辨率為1Hz

求解M,N,F(xiàn)in,F(xiàn)s。

(1)取N=8192,M=N*Fin/Fs=4587.52,取M=4587.

(2)根據(jù)N重新計(jì)算Fs(保證分辨率為1Hz)

X=Fs/N=125M/8192=15258.789

X取整為Xnew=15258.

新的Fs=Xnew*N=15258*8192=124.993536Msps

(3)計(jì)算新的Fin

Fin=Fs*M/N=124.993536Msps*4587/8192=69.9988446MHz

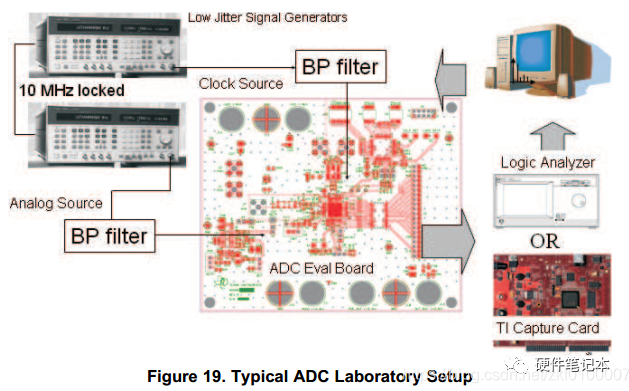

ADC實(shí)驗(yàn)評(píng)估的硬件包括:

(1)時(shí)鐘源:為達(dá)到所需的抖動(dòng)要求,需通過BPF濾除close-in和寬帶噪聲

(2)模擬輸入源:為達(dá)到所需的噪聲和諧波要求,需通過BPF濾除噪聲和諧波

(3)數(shù)據(jù)采集儀:保證采集儀具有足夠的速度和存儲(chǔ)容量用于FFT處理

典型的ADC實(shí)驗(yàn)設(shè)置如下圖所示:

5.交織采樣

高端用戶通常推動(dòng)ADC SNR和采樣速度的極限。 如果當(dāng)前最高端的ADC的SNR或者采樣速度仍不能滿足用戶要求,那么交織采樣是一個(gè)可行的解決方案。

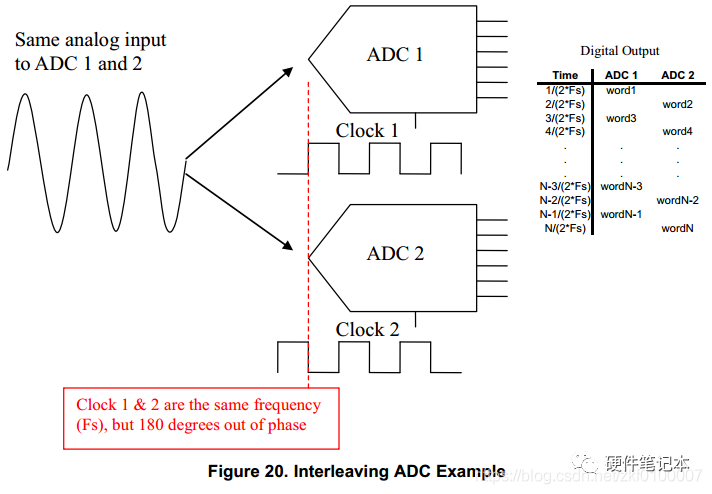

下圖所示為ADC交織采樣:

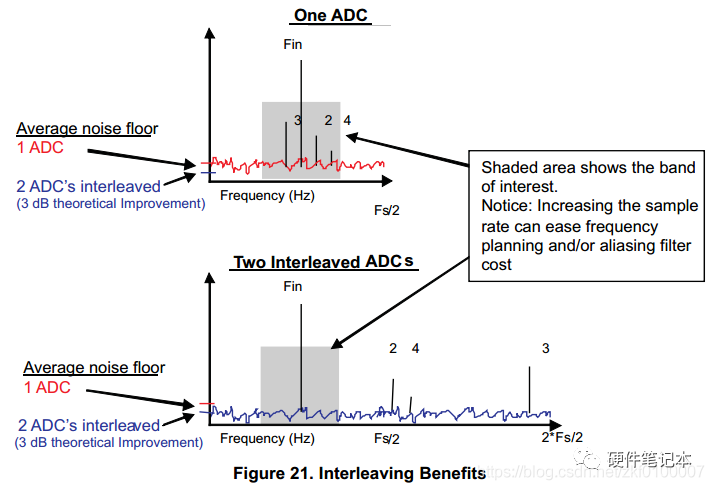

兩個(gè)ADC的模擬輸入并聯(lián)連接,采樣時(shí)鐘相差180度,從而實(shí)現(xiàn)采樣速度翻倍。 采樣速度翻倍有兩個(gè)好處,其一是提高的采樣信號(hào)帶寬,其二是交織采樣將噪底在更寬的帶寬上進(jìn)行擴(kuò)展,可將噪底降低3dB,如下圖所示:

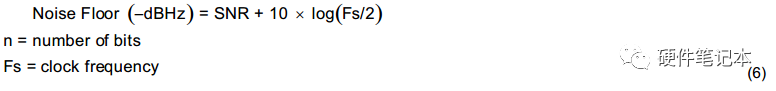

單片ADC噪底計(jì)算公式如下:

當(dāng)多片ADC交織時(shí),噪底計(jì)算公式如下:

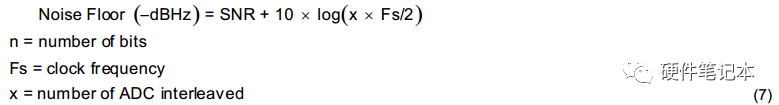

兩片或多片ADC交織也帶來了另外的設(shè)計(jì)挑戰(zhàn)。 ADC之間的DC偏移的差異會(huì)在特定位置產(chǎn)生頻譜分量。 ADC之間的增益差異、INL差異和時(shí)鐘相位誤差會(huì)在時(shí)鐘和模擬輸入混頻的位置產(chǎn)生頻譜分量。

幸運(yùn)的是,這些頻譜分量的位置是已知的。 但是,但是這些誤差及誤差幅度隨溫度漂移,導(dǎo)致頻率規(guī)劃非常困難。

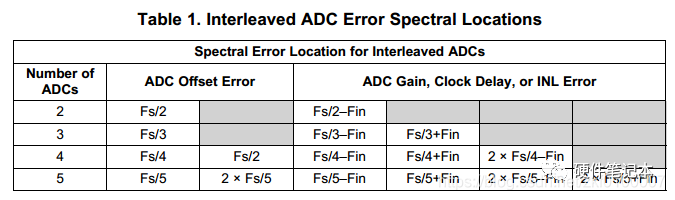

下圖所示為2片、3片、4片和5片ADC交織的頻譜圖,假定選用的ADC為理想14bit ADC,且偏移誤差<15LSB,增益誤差<0.3%。

由上圖可知,盡管ADC的誤差較小,但仍會(huì)造成較大的雜散響應(yīng)。

設(shè)計(jì)者需要設(shè)計(jì)相應(yīng)的經(jīng)溫度補(bǔ)償校正的模擬或數(shù)字濾波器,濾除這些雜散。

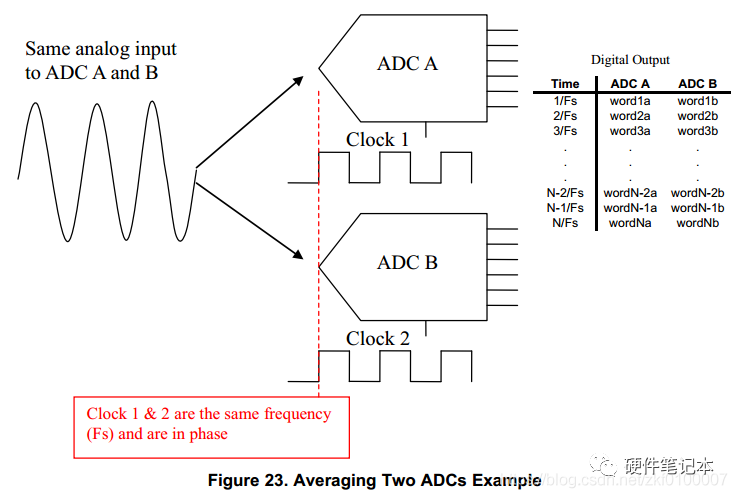

6.ADC取平均

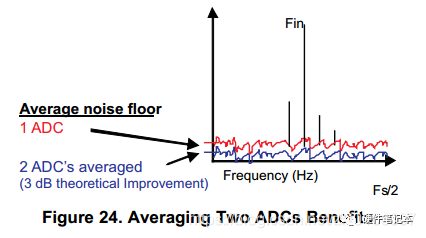

提高單片ADC SNR性能的另一方法是對(duì)兩片或多片ADC取平均。 對(duì)兩片ADC取平均,可以將SNR提高3dB。

這種取平均技術(shù)降低了ADC之間的非相關(guān)噪聲,包括熱噪聲、內(nèi)部ADC參考噪聲或非確定孔徑時(shí)鐘抖動(dòng)。 相反地,取平均技術(shù)并不會(huì)降低了ADC之間的相關(guān)噪聲,包括ADC設(shè)計(jì)固有的失真、ADC外部時(shí)鐘和模擬輸入的通用誤差(common error)。

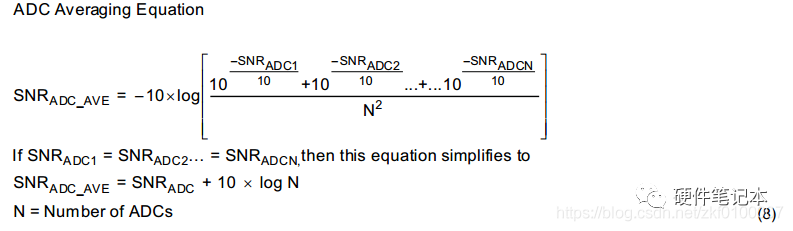

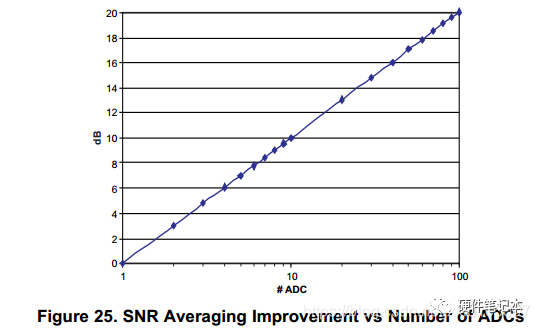

假定各片ADC的SNR相同,則4片取平均可將系統(tǒng)SNR提高6dB,而提高20dB需要100片ADC取平均,計(jì)算公式如下:

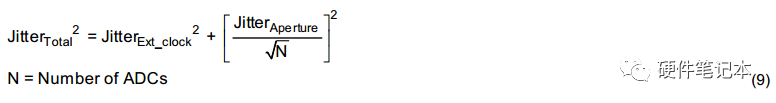

如前所述,孔徑時(shí)鐘抖動(dòng)是非相關(guān)噪聲源。 假定所有ADC具有相同且隨機(jī)的孔徑時(shí)鐘抖動(dòng),下式可用于計(jì)算系統(tǒng)所能容忍的最大外部時(shí)鐘抖動(dòng):

7.抖動(dòng)(Dithering)

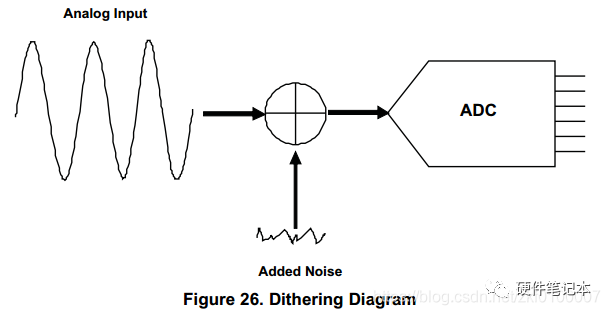

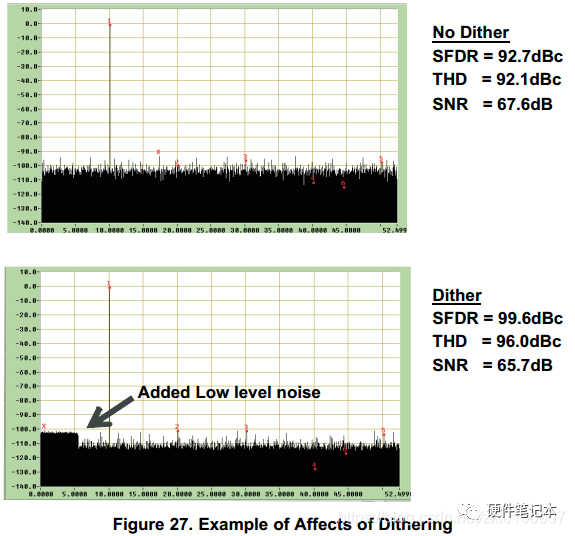

ADC具有確定性和系統(tǒng)性的錯(cuò)誤,且具有重復(fù)性。 理論上, 可以通過添加一個(gè)低量級(jí)的隨機(jī)噪聲來最大限度地減少這些錯(cuò)誤。 添加低量級(jí)隨機(jī)噪聲,以改善 ADC 失真的過程稱為抖動(dòng)(Dithering)。

Dithering的要點(diǎn)如下:

Dithering可以降低諧波的水平,但是可能會(huì)有增加噪底的負(fù)面影響

諧波性能改善與信號(hào)的類型和幅度有關(guān),在某些情況下,甚至不會(huì)有改善

為了將SNR惡化降到最低,某些Dithering技術(shù)在電路中需要隨機(jī)化的部分添加噪聲,后續(xù)又要消除這些噪聲

Dithering可以ADC外部添加,某些ADC內(nèi)置了Dithering選項(xiàng)

某些情況下,真實(shí)世界中已經(jīng)包括了足夠的表現(xiàn)為抖動(dòng)的噪聲

設(shè)計(jì)師要決定是否有必要采用Dithering。 Dithering是一項(xiàng)復(fù)雜的技術(shù),在決定采用前必須深刻理解其內(nèi)涵。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論