了解模數轉換器 (ADC) 中的兩個非線性源、無雜散動態范圍 (SFDR) 和 SNR(信噪比)。

無雜散動態范圍 (SFDR)是?表征電路線性性能的常用方法。該規范在處理通信系統時特別有用。通過檢查 AD 轉換器 (ADC) 的一般功能,本文試圖解釋限制 ADC SFDR 性能的兩個主要非線性源,即采樣保持 (S/H) 電路和 ADC 的編碼器部分。

我們還將了解 ADC 中 SFDR 和SNR(信噪比)之間的一般權衡,并為以后有關應用抖動技術改善 ADC SFDR 的有趣討論奠定基礎。抖動是一種故意向 ADC 輸入添加適當的噪聲分量以改善 AD 轉換系統的某些性能方面的技術。認為添加噪聲可以改善 SFDR 這聽起來很神奇。

然而,在深入探討之前,讓我們快速回顧一下什么是 SFDR 及其重要性。

什么是無雜散動態范圍 (SFDR)?為什么 SFDR 很重要?

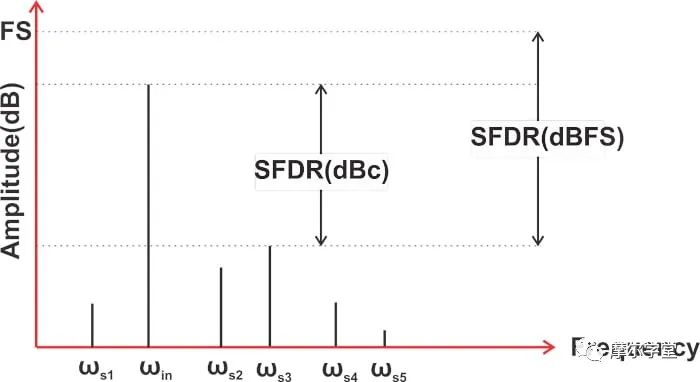

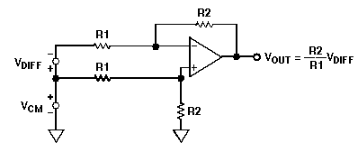

有幾種不同的規范可用于表征電路線性度。一種常用的規范是 SFDR 指標。該指標定義為所需信號幅度與感興趣帶寬內最大雜散的比率(圖 1)。

圖 1.?顯示 SFDR 指標的圖表。

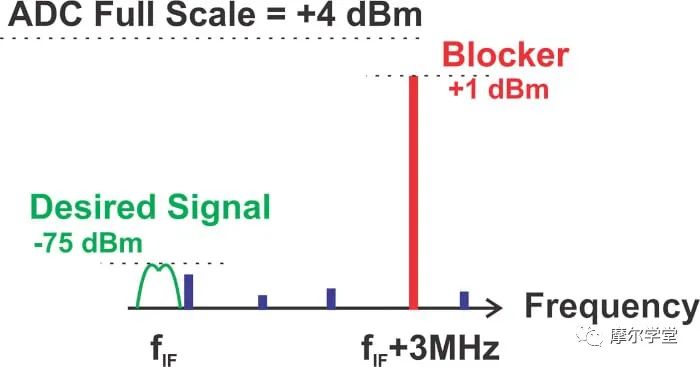

對于 ADC,SFDR 展示了 ADC 如何在存在大信號的情況下同時處理小信號。例如,考慮一個接收器應用程序。假設 ADC 輸入包含一個 +1 dBm 阻塞信號和一個 -75 dBm 所需信號。在這種情況下,由于ADC 非線性,大阻斷器會在 ADC 輸出端產生不需要的雜散。這些不需要的雜散在圖 2 中以紫色組件顯示。

圖 2.?以紫色顯示不需要的雜散的圖表。

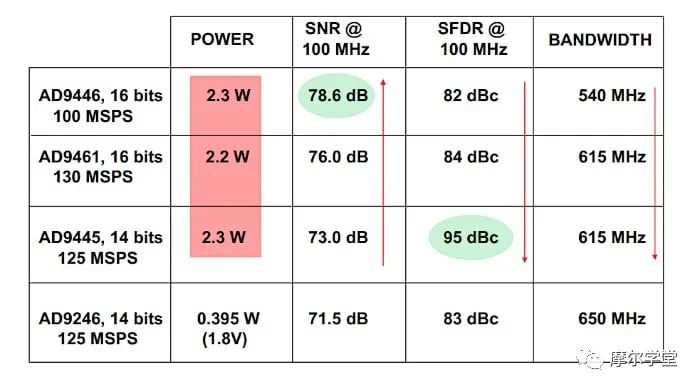

如果雜散距離所需信號足夠近并且足夠大,它可能會將 SNR 降低到不可接受的水平。當今通信系統的嚴格要求可能需要 95 dB 范圍內的高 SFDR 值。然而,普通的 ADC 無法提供這種級別的線性度。下面的表 1 比較了 Analog Devices 的四種高性能 ADC 的一些關鍵參數,應該可以幫助您了解高性能 ADC 中的 SFDR 范圍。

表 1.?四種高性能 ADC 的關鍵參數。數據由Analog Devices提供

此外,該表強調了 SNR 和 SFDR 指標之間的權衡。對于此表中的前三個 ADC,它們使用相同的 IC 技術并具有相同的功耗,SFDR 和 SNR 之間存在反比關系。我們稍后會在本文中探討這種權衡的起源。在此之前,讓我們回答一個重要問題:在高速 ADC 中增加 SFDR 的主要限制是什么??

ADC 中的靜態和動態線性度

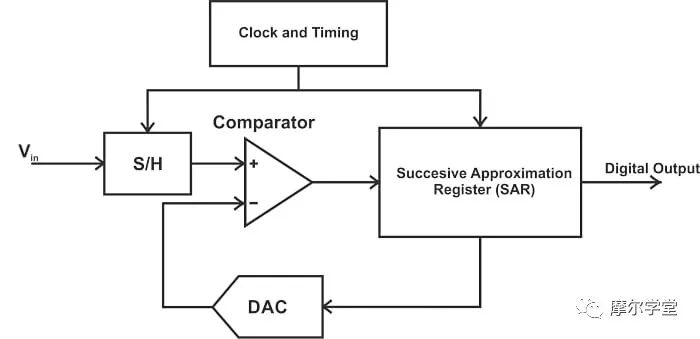

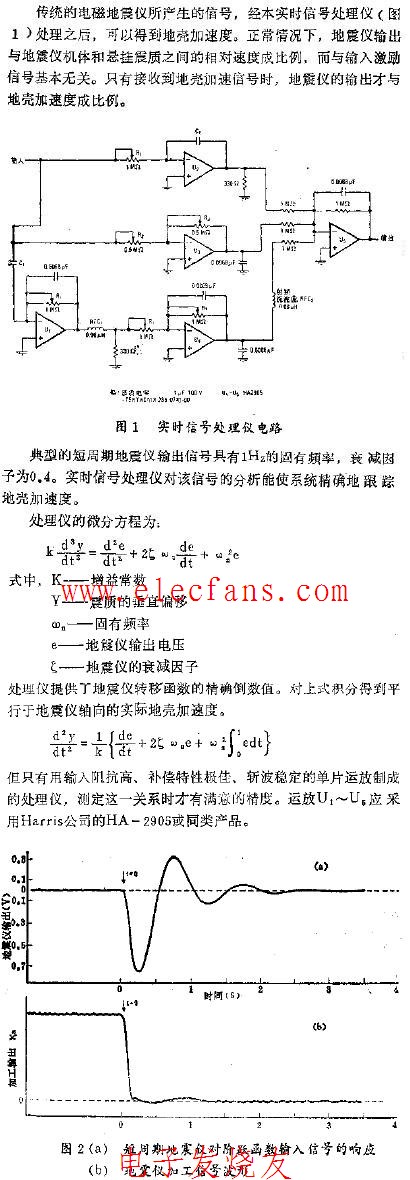

ADC 是基于許多不同電路架構設計的復雜系統,例如閃存、SAR、delta-sigma (ΔΣ)和流水線結構。根據架構和特定的電路實現,不同的電路組件可能是非線性的主要來源。盡管有許多設計,但我們仍然可以認識到在高速 ADC 中增加 SFDR 的兩個主要限制,即 S/H 電路和 ADC 的編碼器部分。為了更好地理解這一點,請考慮圖 3 中描繪的 SAR ADC 的框圖。

圖 3.??SAR ADC 的框圖。

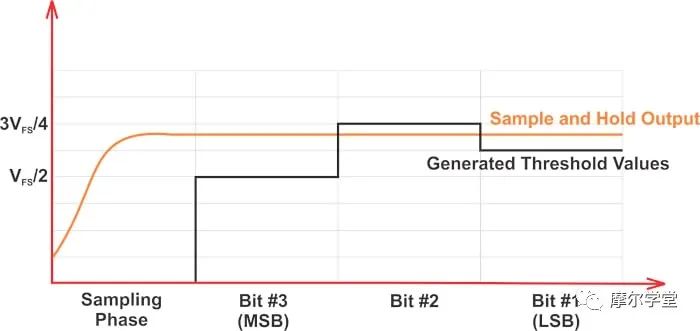

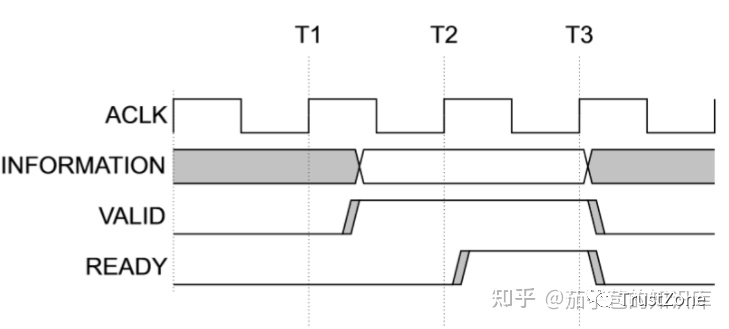

SAR 數字化算法的第一步是采樣階段,在此期間 S/H 獲取輸入值。該樣本將在整個轉換階段保留。在轉換階段,將采集的樣本連續與適當的閾值水平進行比較,以找到輸入的數字等效值。要確定輸出的每一位,需要一個時鐘周期。假設采樣階段也需要一個時鐘周期,對于一個 N 位 SAR ADC,我們需要 N + 1 個時鐘周期。圖 4 顯示了 3 位 SAR ADC 的 S/H 輸出和閾值波形。

圖 4.??3 位 SAR ADC 的 S/H 輸出和閾值波形。

這里的要點是,對于給定的轉換階段,無論輸入頻率是多少,S/H 之后的電路元件都理想地處理直流信號。因此,SAR ADC 的比較器或內部DAC(數模轉換器)內的任何非線性?都不會隨輸入頻率而變化。我們可以說 ADC 編碼器部分的非線性會導致系統的靜態(或 DC)非線性。靜態非線性的特征在于 ADC 傳遞函數中的DNL(微分非線性)和INL(積分非線性)誤差。

S/H 非線性如何?與有效處理直流信號的編碼器部分不同,S/H“看到”交流信號。我們將在下一節中討論 S/H 非線性的重要部分如何隨輸入頻率變化。因此,S/H 決定了 ADC 的動態(或 AC)線性度。

S/H 電路非線性

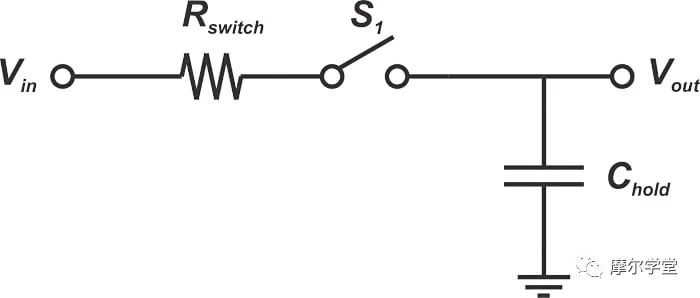

要了解 S/H 非線性,請考慮圖 5 中所示的簡單 S/H 電路。?

圖 5.??S/H 電路示例。

這個基本的 S/H 由一個采樣開關 S1 和一個保持電容(C?hold?) 組成,后者用于存儲采集的樣本。

電路操作包括兩種模式:采樣(或采集模式)和保持模式。在采樣模式下,開關導通,電容電壓跟蹤輸入。在采樣瞬間,開關關閉并斷開 C?hold?與輸入的連接。這將啟動保持模式,其中電容器保持采集的樣本。

實際上,我們不可能有零電阻的理想開關。為了強調這一點,上圖明確顯示了開關電阻 R?switch。開關電阻的熱噪聲是高分辨率奈奎斯特速率 ADC 中的主要噪聲來源。為了解決這個問題,保持電容的值通常選擇得足夠大以限制帶寬?,從而限制系統的噪聲。然而,有限的帶寬意味著 S/H 的輸出無法立即達到其最終值。這是由于 RC 網絡的時間常數,由下式給出

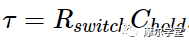

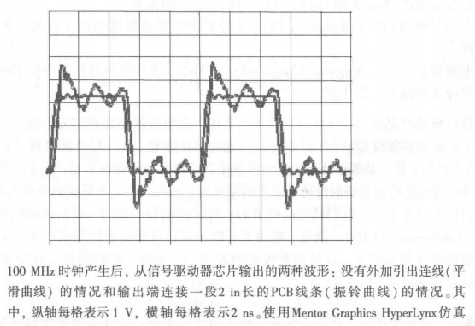

圖 6 顯示了 S/H 操作的一個周期的示例波形。

圖 6.??S/H 電路操作一個周期的示例波形。

S/H 需要一些時間(如圖中的“采集時間”所示)才能穩定在最終值附近的指定誤差范圍內。在采集時間之后,S/H 能夠以較小的誤差跟蹤輸入。采集時間取決于 R?switch、 C?hold?和最大允許誤差的值。此外,采集時間對 ADC 的最大采樣率設置了上限。

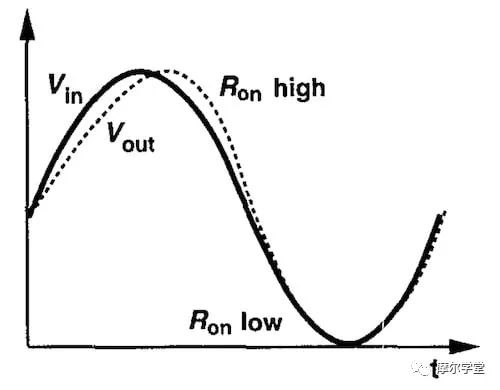

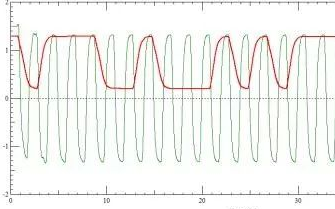

實際上,開關電阻不是恒定的,會隨著輸入電平的變化而變化。R switch 對輸入的依賴性會導致輸入相關的相移,從而導致諧波失真。圖 7 顯示了 R開關隨輸入電平增加的情況的示例波形?。

圖 7. R開關?隨輸入電平增加時的示例波形。圖片由B. Razavi提供

請注意,此相移(或非線性)隨頻率變化。例如,在比 RC 網絡的極點小得多的頻率下,相移為零,R開關的微小變化?對線性度的影響可以忽略不計。然而,隨著我們增加頻率,相移變得越來越顯著。

值得一提的是,R開關?隨輸入的變化只是 S/H 非線性的一個來源。開關的輸入相關電荷注入以及輸入相關采樣瞬間等機制是導致 S/H 非線性的其他現象。后一種機制是指開關關閉的瞬間可以隨輸入電平的變化而變化。

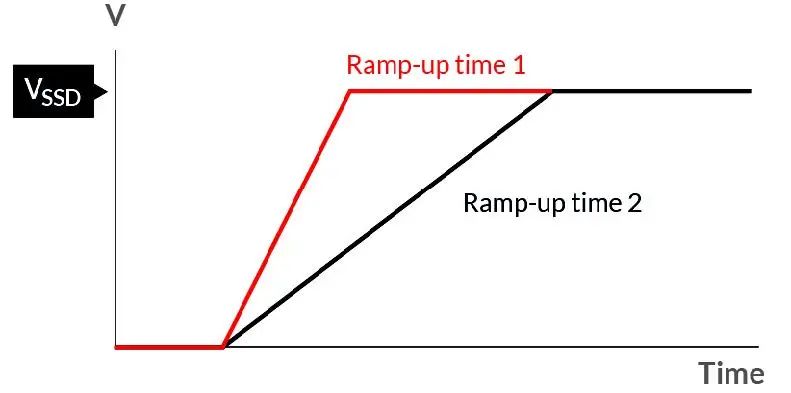

轉換率限制問題

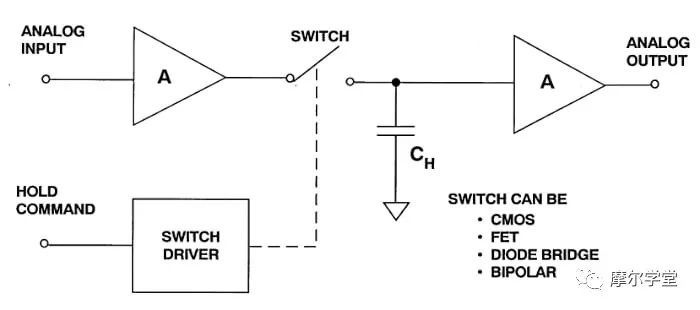

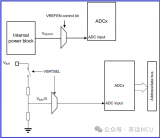

S/H 電路的頻率相關非線性也可以通過注意到驅動保持電容器的電路具有有限的轉換速率來解釋。圖 8 更詳細地顯示了典型 S/H 電路的框圖。

圖 8.?更詳細的 S/H 電路框圖。圖片由Analog Devices提供。

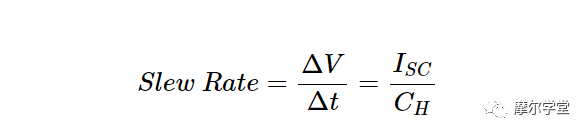

在該電路中,第一個放大器通過向信號源呈現高阻抗來緩沖輸入。它還提供電流增益來為保持電容器充電。右側放大器用作輸出緩沖器,并防止 S/H 輸出電壓在保持模式期間被后續電路的輸入阻抗放電。假設輸入緩沖器的短路輸出電流為I?SC。這是緩沖器可以提供給 C?H的最大電流。因此,壓擺率(或 S/H 輸出的最大變化率)由公式 1 給出。

等式 1。

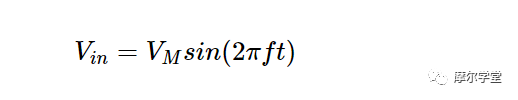

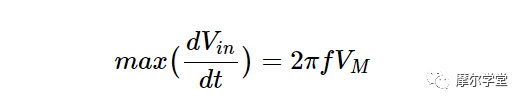

對于正弦波輸入:

信號的最大變化率由下式給出:

對于給定的大信號輸入,增加頻率可以使信號的變化率大于 S/H 的壓擺率。在這種情況下,S/H 輸出無法足夠快地跟隨輸入,從而導致信號失真問題。缺乏顯示足夠轉換率以跟上快速變化的模擬輸入的 S/H 是許多 ADC 無法在超過幾兆赫信號帶寬的情況下表現良好的一個關鍵原因。

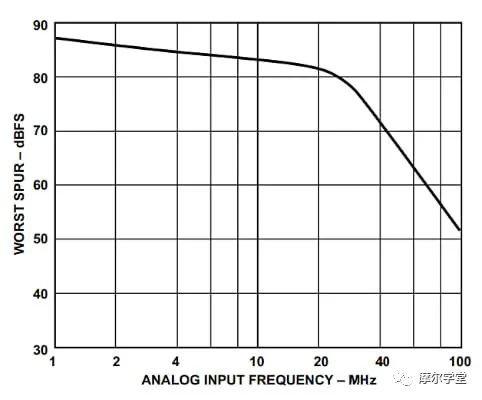

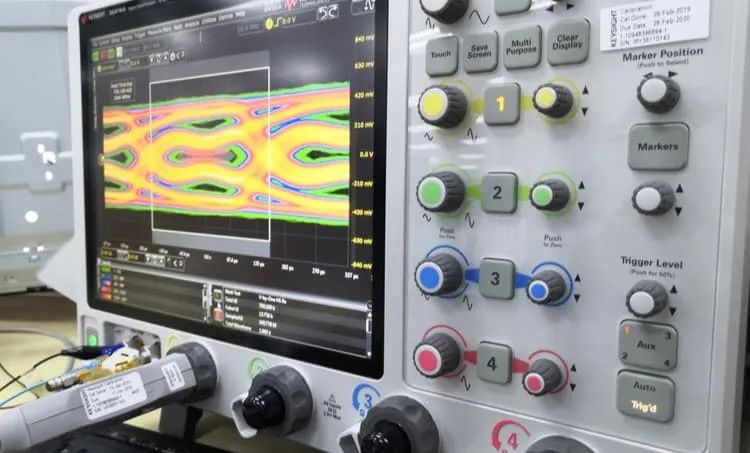

例如,考慮Analog Devices 的AD9042??。盡管 AD9042 是專門設計有寬帶、高 SFDR 前端的轉換器,但其 SFDR 仍會隨著輸入頻率而降低,如圖 9 所示。

圖 9.?顯示 AD9042 的 SFDR 如何隨輸入頻率降低的圖表。圖片由Analog Devices提供。

SNR-SFDR 權衡

上述討論還解釋了我們在本文前面提到的 SNR-SFDR 權衡。請注意,較大的保持電容器會導致較低的轉換率(公式 1)和較高的失真(或較低的 SFDR)。另一方面,較大的電容器會降低系統帶寬并改善噪聲性能(更高的 SNR)。??

應用抖動改善 SFDR

如上所述,改進 SFDR 有兩個主要限制:S/H 電路產生的非線性和 ADC 編碼器部分產生的非線性。沒有任何外部措施可以減少 S/H 電路產生的失真。然而,抖動技術可以降低 ADC 編碼器部分的非線性。這將在本系列的下一篇文章中討論。? ?

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論