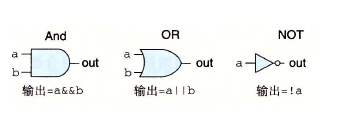

在《數(shù)字電路之如雷貫耳的“邏輯電路”》、《數(shù)字電路之?dāng)?shù)字集成電路IC》之后,本文是數(shù)字電路入門3,將帶來「時(shí)序電路」的講解,及其核心部件觸發(fā)器的工作原理。什么是時(shí)序電路?

2016-08-01 10:58:48 18171

18171

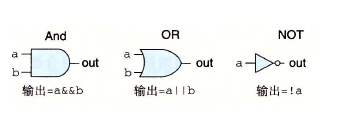

時(shí)序電路 首先來看兩個(gè)問題: 1.為什么CPU要用時(shí)序電路,時(shí)序電路與普通邏輯電路有什么區(qū)別。 2.觸發(fā)器、鎖存器以及時(shí)鐘脈沖對時(shí)序電路的作用是什么,它們是如何工作的。 帶著這兩個(gè)問題,我們從頭了解

2020-11-20 14:27:09 3998

3998

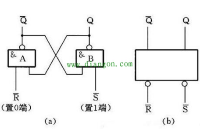

觸發(fā)器是由各種基礎(chǔ)門電路單元組成,廣泛應(yīng)用于數(shù)字電路和計(jì)算機(jī)中。它具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。 觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài)

2023-01-11 17:17:07 9167

9167

觸發(fā)器是一種特殊的電路元件或信號,它可以根據(jù)預(yù)先設(shè)定的條件或事件來產(chǎn)生相應(yīng)的輸出信號或動(dòng)作。觸發(fā)器是數(shù)字電路中的基本元件,用于控制信號的時(shí)序、邏輯運(yùn)算和狀態(tài)轉(zhuǎn)換。

2024-01-15 16:33:15 659

659

用Qn(t)表示現(xiàn)態(tài)函數(shù),用Qn+1(t)表示次態(tài)函數(shù)。它們統(tǒng)稱為狀態(tài)函數(shù),一個(gè)時(shí)序電路的主要特征是由狀態(tài)函數(shù)給出的。三:時(shí)序電路的特征時(shí)序電路中記憶功能是靠觸發(fā)器來實(shí)現(xiàn)的,我們設(shè)計(jì)和分析時(shí)序電路

2018-08-23 10:36:20

時(shí)序電路測試及應(yīng)用一、實(shí)驗(yàn)?zāi)康?.掌握常用時(shí)序電路分析,設(shè)計(jì)及測試方法。2.訓(xùn)練獨(dú)立進(jìn)行實(shí)驗(yàn)的技能.二、實(shí)驗(yàn)儀器及材料1.雙蹤示波器 2.

2009-08-20 18:55:27

邏輯功能,若電路存在問題,并提出改進(jìn)方法。在分析同步時(shí)序電路時(shí)分為以下幾個(gè)步驟:分清時(shí)序電路的組成.列出方程. 根據(jù)時(shí)序電路的組合部分,寫出該時(shí)電路的輸出函數(shù)表達(dá)式.并確定觸發(fā)器輸入信號的邏輯表達(dá)式

2018-08-23 10:28:59

觸發(fā)器PPT電子教案:觸發(fā)器是構(gòu)成時(shí)序邏輯電路的基本邏輯部件。? 它有兩個(gè)穩(wěn)定的狀態(tài):0狀態(tài)和1狀態(tài);? 在不同的輸入情況下,它可以被置成0狀態(tài)或1狀態(tài);? 當(dāng)輸入信號消失后,所置成的狀態(tài)能夠保持

2009-09-16 16:06:45

觸發(fā)器輸入電路二極管D的作用是只把負(fù)的尖脈沖輸入觸發(fā)器,還可用來組成加速電路。

2009-09-22 08:28:30

ARM與單片機(jī)對比分析哪個(gè)好?

2021-11-05 07:16:04

CPLD與FPGA對比分析哪個(gè)好?

2021-06-21 06:10:12

CPLD與FPGA的對比分析哪個(gè)好?

2021-11-05 08:20:40

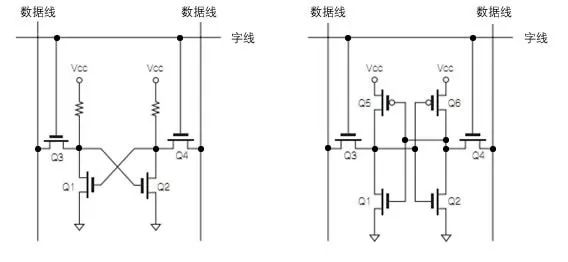

RAM有哪些分類?特點(diǎn)是什么?DRAM和SRAM對比分析哪個(gè)好?

2022-01-20 07:16:10

的,因此可以設(shè)計(jì)成儲存電路用來保存信息。常用的存儲電路有兩類:一類采用電平觸發(fā),我們稱為鎖存器(Latch);另一類通過邊沿信號觸發(fā),也就是觸發(fā)器(Flip-flop)。中文譯法經(jīng)常有一種不明覺厲的感覺

2021-07-04 08:00:00

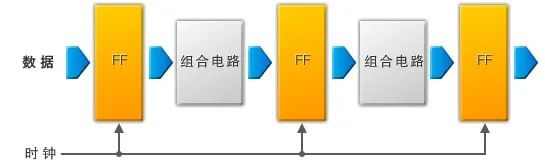

,顯然內(nèi)部結(jié)構(gòu)不是單純的組合邏輯。內(nèi)部的功能有一定的記憶性功能,能夠清楚的記得之前我們投入的硬幣的數(shù)量。 時(shí)序邏輯電路 = 組合邏輯電路 + 時(shí)序邏輯器件(觸發(fā)器)。 根據(jù)輸出信號的特點(diǎn)將時(shí)序電路劃分

2023-02-22 17:00:37

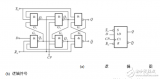

主從觸發(fā)器(邊沿觸發(fā))。主從JK觸發(fā)器主從觸發(fā)器通過使用兩個(gè)串聯(lián)配置的SR觸發(fā)器消除了所有時(shí)序問題。一個(gè)觸發(fā)器充當(dāng)“主”電路,在時(shí)鐘脈沖的上升沿觸發(fā),而另一個(gè)觸發(fā)器充當(dāng)“從屬”電路,在時(shí)鐘脈沖的下降沿觸發(fā)。這

2021-02-01 09:15:31

LTE與WiMAX對比分析哪個(gè)好?

2021-05-31 06:22:29

Arduino和STM32各自的特點(diǎn)是什么?STM32和Arduino對比分析哪個(gè)好?

2021-11-04 06:34:07

什么是時(shí)序電路?時(shí)序電路核心部件觸發(fā)器的工作原理

2021-03-04 06:32:49

什么是時(shí)序電路?SRAM是觸發(fā)器構(gòu)成的嗎?

2021-03-17 06:11:32

根據(jù)輸入信號改變輸出狀態(tài)。把這種在時(shí)鐘信號觸發(fā)時(shí)才能動(dòng)作的存儲單元電路稱為觸發(fā)器,以區(qū)別沒有時(shí)鐘信號控制的鎖存器。觸發(fā)器是一種能夠保存1位二進(jìn)制數(shù)的單元電路,是計(jì)算機(jī)中記憶裝置的基本單元,由它可以組成

2019-12-25 17:09:20

`如圖所示,圖中第一個(gè)觸發(fā)器D接第二個(gè)觸發(fā)器的非Q端,這個(gè)時(shí)序圖,整不明白啊,我的看法是:當(dāng)?shù)谝粋€(gè)時(shí)鐘信號高電平來的時(shí)候,第一個(gè)觸發(fā)器的輸出狀態(tài)Q是不能判斷的啊,因?yàn)镈接在第二個(gè)觸發(fā)器的非Q端。求大佬指點(diǎn)一下 這個(gè)圖,是如何工作的?`

2019-01-16 11:50:35

邏輯可構(gòu)成時(shí)序邏輯電路,簡稱時(shí)序電路。現(xiàn)在討論實(shí)現(xiàn)存儲功能的兩種邏輯單元電路,即鎖存器和觸發(fā)器。雙穩(wěn)態(tài):電子電路中。其雙穩(wěn)態(tài)電路的特點(diǎn)是:在沒有外來觸發(fā)信號的作用下,電路始終處于原來的穩(wěn)定狀態(tài)。在外

2016-05-21 06:50:08

印制電路板設(shè)計(jì)中手工設(shè)計(jì)和自動(dòng)設(shè)計(jì)對比分析哪個(gè)好?

2021-04-25 07:32:18

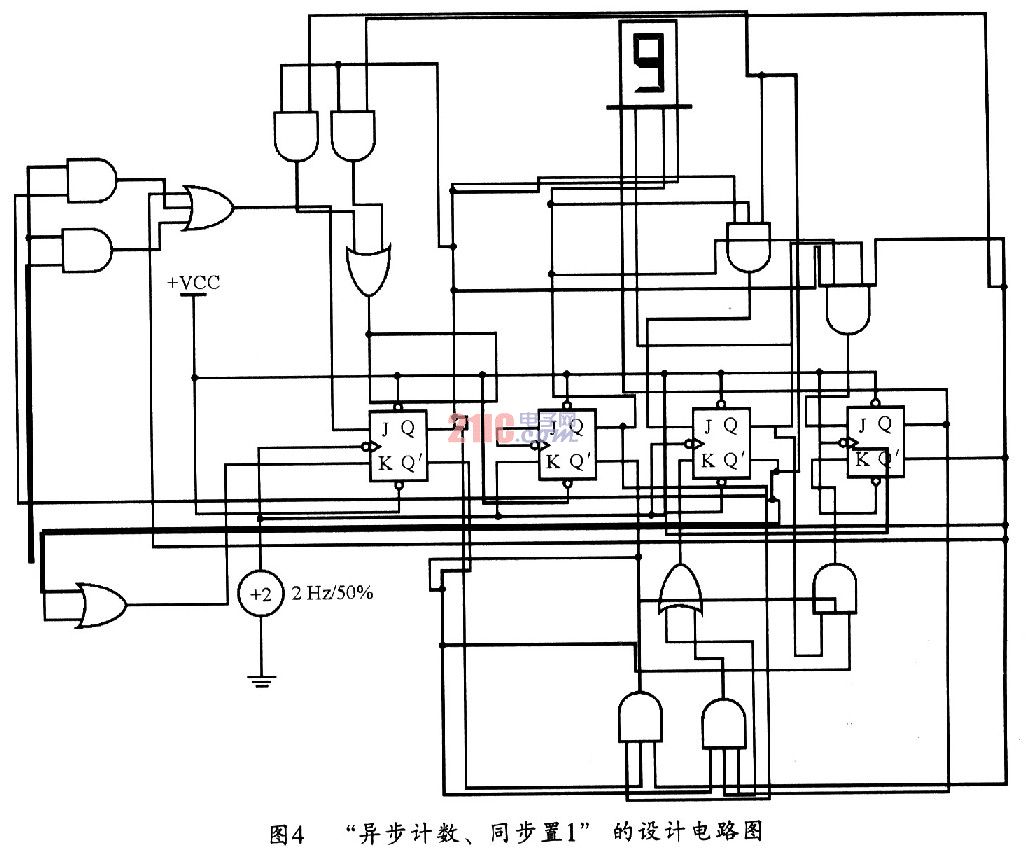

同步時(shí)序邏輯電路的設(shè)計(jì)(仿真實(shí)驗(yàn) 2學(xué)時(shí))一、 實(shí)驗(yàn)?zāi)康模?. 掌握時(shí)序電路的設(shè)計(jì)和測試方法。2. 驗(yàn)證二進(jìn)制計(jì)數(shù)器的工作原理:學(xué)會用集成觸發(fā)器

2009-10-11 09:09:51

觸發(fā)器沒有使用相同的時(shí)鐘信號,需要分析哪些觸發(fā)器時(shí)鐘有效哪些無效分析步驟和同步時(shí)序電路一樣,不過要加上時(shí)鐘信號有關(guān)D觸發(fā)器的例題抄自慕課上的一個(gè)題目,注意第二個(gè)觸發(fā)器反相輸出端同時(shí)連接到復(fù)位端JK

2021-09-06 08:20:26

狀態(tài),因此,與標(biāo)準(zhǔn)環(huán)形計(jì)數(shù)器相比,約翰遜計(jì)數(shù)器僅需要一半數(shù)量的觸發(fā)器便可實(shí)現(xiàn)同樣的MOD。 典型時(shí)序電路的缺陷 如圖1所示,這種電路最大的缺點(diǎn)是不可配置,因此,不能改變時(shí)鐘分頻因子。一個(gè)N觸發(fā)器

2018-09-30 16:00:50

實(shí)驗(yàn)二 基本時(shí)序電路設(shè)計(jì)(1)實(shí)驗(yàn)?zāi)康模菏煜uartusⅡ的VHDL文本設(shè)計(jì)過程,學(xué)習(xí)簡單時(shí)序電路的設(shè)計(jì)、仿真和硬件測試。(2)實(shí)驗(yàn)內(nèi)容:Ⅰ.用VHDL設(shè)計(jì)一個(gè)帶異步復(fù)位的D觸發(fā)器,并利用

2009-10-11 09:21:16

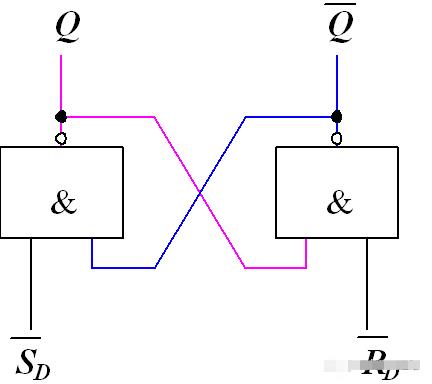

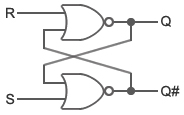

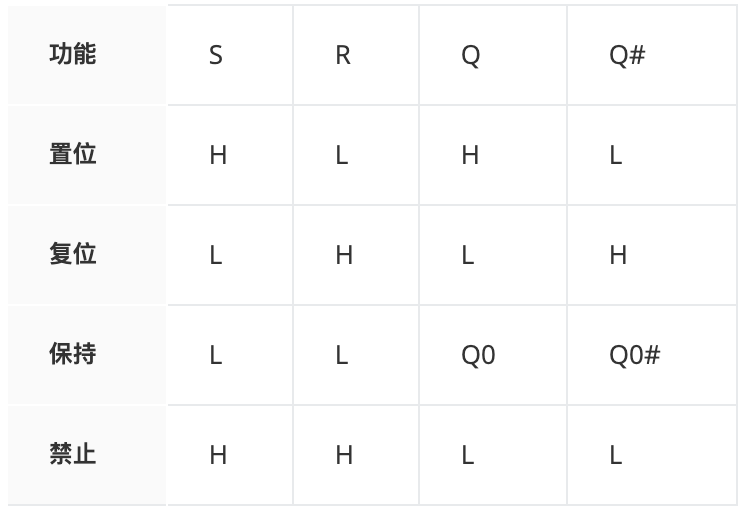

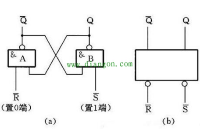

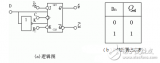

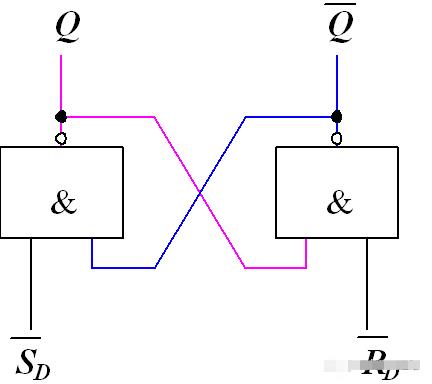

新課第五章 觸發(fā)器5.1 概述1、觸發(fā)器具有“記憶”功能,它是構(gòu)成時(shí)序邏輯電路的基本單元。本章首先介紹基本RS觸發(fā)器的組成原理、特點(diǎn)和邏輯功能。然后引出能夠防止“空翻”現(xiàn)象的主從觸發(fā)器和邊沿觸發(fā)器。同時(shí),較詳細(xì)地討論RS觸發(fā)器、JK觸發(fā)器、D觸發(fā)器、T觸發(fā)器、T'觸發(fā)器的邏輯功能及其描述方法。

2009-04-02 11:58:41

常見單片機(jī)對比分析哪個(gè)好?

2021-10-29 07:39:21

干簧管傳感器與霍爾效應(yīng)傳感器的比較對比分析哪個(gè)好?

2021-06-08 07:03:59

根據(jù)波形圖設(shè)計(jì)異步時(shí)序電路 急 求大神

2017-12-08 23:07:44

《計(jì)算機(jī)系統(tǒng)基礎(chǔ)》30’一、處理器的時(shí)序電路1、CPU中的時(shí)序電路答:CPU中的時(shí)序電路:通過RS觸發(fā)器控制CPU的時(shí)序。2、單周期處理器的設(shè)計(jì)答:CPU在處理指令時(shí),一般需要經(jīng)過以下幾個(gè)步驟:1

2021-07-22 09:46:12

步進(jìn)電機(jī)與伺服電機(jī)對比分析采用閉環(huán)技術(shù)的步進(jìn)電機(jī)

2021-02-05 06:05:47

視頻標(biāo)準(zhǔn)核心技術(shù)對比分析哪個(gè)好

2021-06-07 06:12:34

計(jì)數(shù)器及時(shí)序電路一、實(shí)驗(yàn)?zāi)康?、了解時(shí)序電路的經(jīng)典設(shè)計(jì)方法(D觸發(fā)器、JK觸發(fā)器和一般邏輯門組成的時(shí)序邏輯電路)。 2、了解同步計(jì)數(shù)器,異步計(jì)數(shù)器的使用方法。 3

2009-10-11 09:13:20

計(jì)數(shù)器及時(shí)序電路原理及實(shí)驗(yàn) 一、實(shí)驗(yàn)?zāi)康?、了解時(shí)序電路的經(jīng)典設(shè)計(jì)方法(D觸發(fā)器、JK觸發(fā)器和一般邏輯門組成的時(shí)序邏輯電路)。 &

2009-10-10 11:47:02

多輸入時(shí)序電路的基本原理是什么?基于數(shù)據(jù)選擇器和D觸發(fā)器的多輸入時(shí)序邏輯電路設(shè)計(jì)

2021-04-29 07:04:38

鉛酸電池和鋰電池對比分析哪個(gè)好?

2021-06-10 06:59:19

中,除了組合電路以外,還有一種時(shí)序電路,它的輸出不僅與當(dāng)前時(shí)刻的輸入狀態(tài)有關(guān),而且與電路原來狀態(tài)有關(guān)。而觸發(fā)器是組成時(shí)序電路中存儲部分的基本單元,具有保持、記憶、存儲功能。它有兩個(gè)輸出端Q和Q,當(dāng)Q

2008-12-11 23:38:01

PLD練習(xí)2(時(shí)序電路)

2006-05-26 00:14:19 20

20 摘要:針對同步時(shí)序電路的初始化問題,提出了一種新的實(shí)現(xiàn)方法。當(dāng)時(shí)序電路中有未確定狀態(tài)的觸發(fā)器時(shí),就不能順利完成該電路的測試生成,因此初始化是時(shí)序電路測試生成中

2010-05-13 09:36:52 6

6 本文介紹將量子進(jìn)化算法應(yīng)用在時(shí)序電路測試生成的研究結(jié)果。結(jié)合時(shí)序電路的特點(diǎn),本文將量子計(jì)算中的量子位和疊加態(tài)的概念引入傳統(tǒng)的測試生成算法中,建立了時(shí)序電路的量

2010-08-03 15:29:01 0

0 5.1 基本RS觸發(fā)器5.2 時(shí)鐘控制的觸發(fā)器5.3 集成觸發(fā)器5.4 觸發(fā)器的邏輯符號及時(shí)序圖

2010-08-10 11:53:23 0

0 觸發(fā)器是時(shí)序邏輯電路中完成記憶功能的電路,是最基本的時(shí)序邏輯電路。

2010-08-12 16:20:24 0

0 在討論時(shí)序邏輯電路的分析與設(shè)計(jì)之前,讓我們先回顧一下在第四章中介紹過的時(shí)序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時(shí)序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 一、基本要求1、理解R-S觸發(fā)器、J-K觸發(fā)器和D觸發(fā)器的邏輯功能;2、掌握觸發(fā)器構(gòu)成的時(shí)序電路的分析,并了解其設(shè)計(jì)方法;3、理解計(jì)數(shù)器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 組合電路和時(shí)序電路是數(shù)字電路的兩大類。門電路是組合電路的基本單元;觸發(fā)器是時(shí)序電路的基本單元。

2010-08-29 11:29:04 67

67

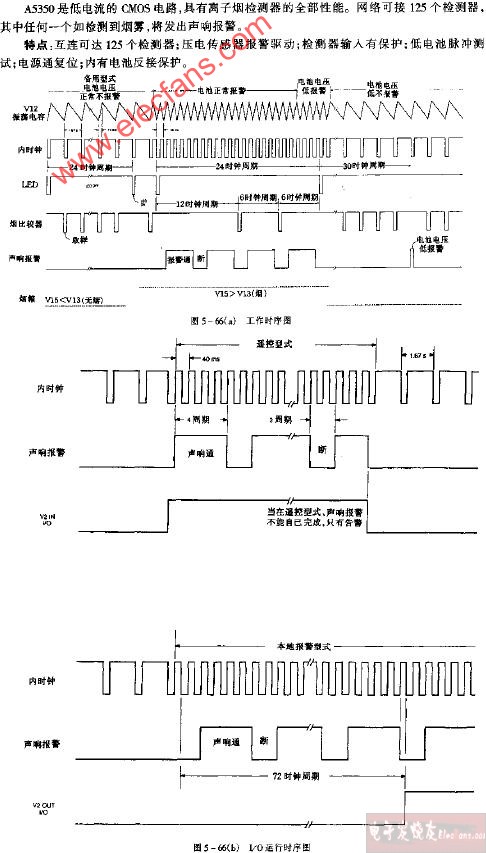

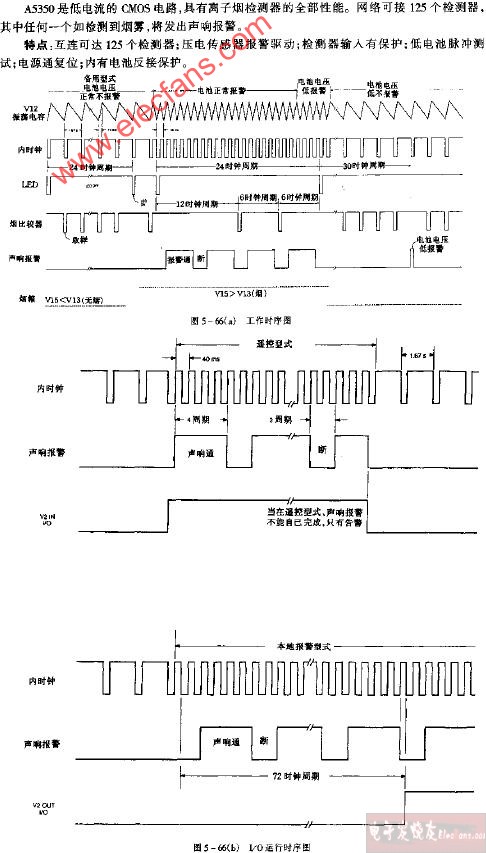

A5350工作時(shí)序電路圖

2009-07-03 12:22:16 652

652

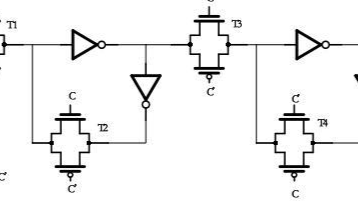

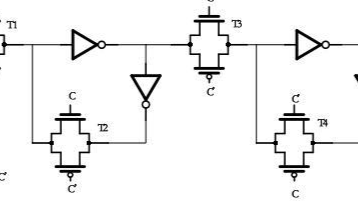

CMOS觸發(fā)器的結(jié)構(gòu)與工作原理

CMOS D觸發(fā)器足主-從結(jié)構(gòu)形式的一種邊沿觸發(fā)器,CMOS T型觸發(fā)器、JK觸發(fā)器、計(jì)數(shù)單元、移位單元和各種時(shí)序電路都由其組成,因此儀

2009-10-17 08:52:27 7151

7151

同步時(shí)序電路

4.2.1 同步時(shí)序電路的結(jié)構(gòu)和代數(shù)法描述

2010-01-12 13:31:55 4672

4672

觸發(fā)器的分類, 觸發(fā)器的電路

雙穩(wěn)態(tài)器件有兩類:一類是觸發(fā)器,一類是鎖存器。鎖存器是觸發(fā)器的原始形式。基本

2010-03-09 09:59:59 1554

1554 什么是時(shí)序電路

任意時(shí)刻的穩(wěn)定輸出,不僅與該時(shí)刻的輸入有關(guān),而且還

2010-01-12 13:23:14 8109

8109

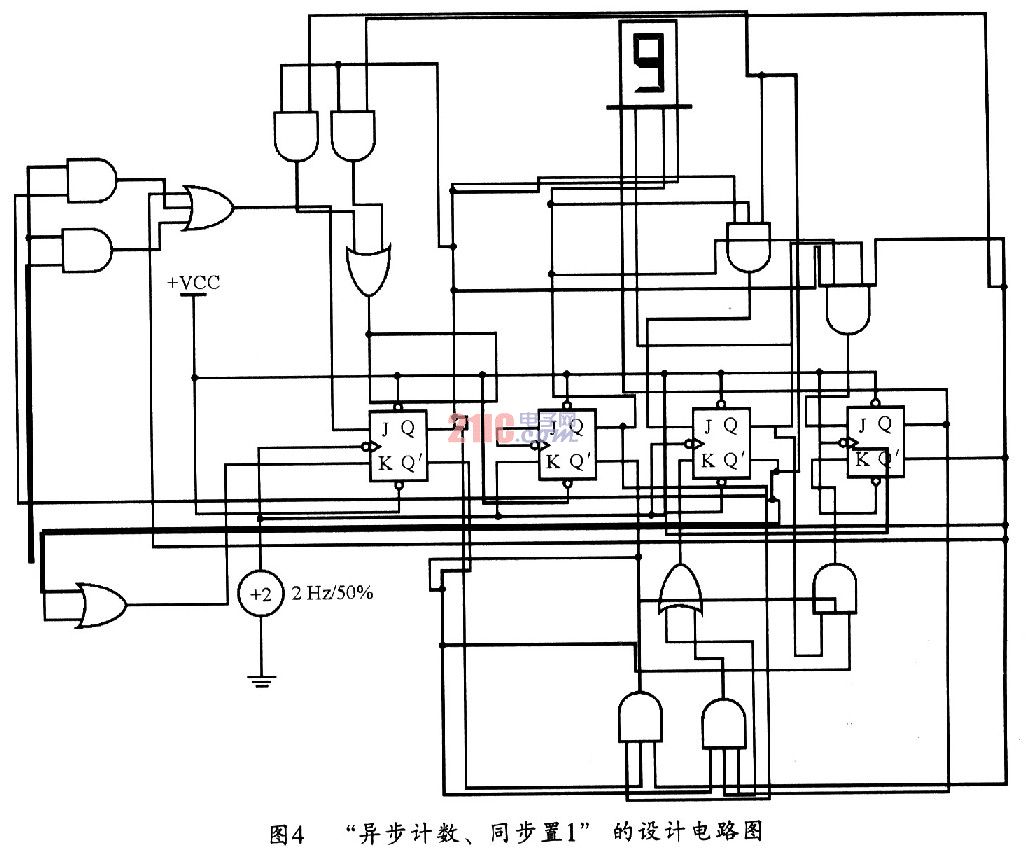

觸發(fā)器是數(shù)字電路的基本邏輯單元之一,也是構(gòu)成各種時(shí)序電路的最基本邏輯單元。

文中給出了基于JK觸發(fā)器來設(shè)計(jì)十二歸一計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)方法,并通過EWB軟件進(jìn)行了

2010-06-30 15:58:29 15211

15211

圖中所示是用CMOS電路D觸發(fā)器組成T型觸發(fā)器和J-K觸發(fā)器線路。圖示線路將D觸發(fā)器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 17220

17220

圖中所示是用J-K觸發(fā)器組成的D觸發(fā)器電路。

從J-K觸發(fā)器的邏輯圖已知在D觸發(fā)器端增

2010-09-24 00:21:27 6900

6900

為了實(shí)現(xiàn)時(shí)序電路狀態(tài)驗(yàn)證和故障檢測,需要事先設(shè)計(jì)一個(gè)輸入測試序列。基于二叉樹節(jié)點(diǎn)和樹枝的特性,建立時(shí)序電路狀態(tài)二叉樹,按照電路二叉樹節(jié)點(diǎn)(狀態(tài))與樹枝(輸入)的層次邏輯

2012-07-12 13:57:40 0

0 1、了解時(shí)序電路的經(jīng)典設(shè)計(jì)方法(D觸發(fā)器、JK觸發(fā)器和一般邏輯門組成的時(shí)序邏輯電路)。

2、了解同步計(jì)數(shù)器,異步計(jì)數(shù)器的使用方法。

3、了解同步計(jì)數(shù)器通過清零阻塞法和預(yù)顯數(shù)法得到循環(huán)任意進(jìn)制

2022-07-10 14:37:37 15

15 觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計(jì)算機(jī)中有著廣泛的應(yīng)用。觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài),即“0”和“1”,在一定的外界信號作用下,可以從一個(gè)穩(wěn)定狀態(tài)翻轉(zhuǎn)到另一個(gè)穩(wěn)定狀態(tài)。

2017-08-19 09:21:00 11043

11043

在傳統(tǒng)設(shè)計(jì)中,所有計(jì)算機(jī)運(yùn)算(算法邏輯和存儲進(jìn)程) 都參考時(shí)鐘同步執(zhí)行,時(shí)鐘增加了設(shè)計(jì)中的時(shí)序電路數(shù)量。在這個(gè)電池供電設(shè)備大行其道的移動(dòng)時(shí)代,為了節(jié)省每一毫瓦(mW) 的功耗,廠商間展開了殘酷的競爭

2017-10-25 15:41:59 25

25 觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計(jì)算機(jī)中有著廣泛的應(yīng)用。觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài).

2017-11-02 08:53:42 58361

58361 觸發(fā)器是一個(gè)具有記憶功能的二進(jìn)制信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計(jì)算機(jī)中有著廣泛的應(yīng)用。觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài),即“0”和“1”,,在一定的外界信號作用下,可以從一個(gè)穩(wěn)定狀態(tài)翻轉(zhuǎn)到另一個(gè)穩(wěn)定狀態(tài)。

2017-11-02 10:20:40 96979

96979

觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計(jì)算機(jī)中有著廣泛的應(yīng)用。觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài),即“0”和“1”。

2017-12-12 16:47:56 7411

7411

觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。在數(shù)字系統(tǒng)和計(jì)算機(jī)中有著廣泛的應(yīng)用。觸發(fā)器具有兩個(gè)穩(wěn)定狀態(tài)

2017-12-12 17:20:40 80618

80618

“時(shí)鐘是時(shí)序電路的控制者” 這句話太經(jīng)典了,可以說是FPGA設(shè)計(jì)的圣言。FPGA的設(shè)計(jì)主要是以時(shí)序電路為主,因?yàn)榻M合邏輯電路再怎么復(fù)雜也變不出太多花樣,理解起來也不沒太多困難。但是時(shí)序電路就不

2018-07-21 10:55:37 4504

4504 組合電路和時(shí)序電路是計(jì)算機(jī)原理的基礎(chǔ)課,組合電路描述的是單一的函數(shù)功能,函數(shù)輸出只與當(dāng)前的函數(shù)輸入相關(guān);時(shí)序電路則引入了時(shí)間維度,時(shí)序電路在通電的情況下,能夠保持狀態(tài),電路的輸出不僅與當(dāng)前的輸入有關(guān),而且與前一時(shí)刻的電路狀態(tài)相關(guān),如我們個(gè)人PC中的內(nèi)存和CPU中的寄存器,均為時(shí)序電路。

2018-09-25 09:50:00 24779

24779 ,得到原始狀態(tài)圖. 2.化簡原始狀態(tài). 在制作原始狀態(tài)圖時(shí),難免會出現(xiàn)多余狀態(tài)(觸發(fā)器的個(gè)數(shù)增多激勵(lì)電路過于復(fù)雜等),因此要進(jìn)行狀態(tài)化簡,化簡時(shí)應(yīng)根據(jù)具體情況來考慮. 3.分配化簡后的狀態(tài). 把化簡后的狀態(tài)用二進(jìn)制代碼來表示稱為狀態(tài)編碼.時(shí)序電路中,電路

2018-10-31 18:14:01 1097

1097 將驅(qū)動(dòng)方程代入相應(yīng)觸發(fā)器的特性方程中,便得到該觸發(fā)器的次態(tài)方程。時(shí)序邏輯電路的狀態(tài)方程由各觸發(fā)器次態(tài)的邏輯表達(dá)式組成。

2019-02-28 14:06:14 23502

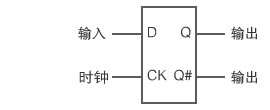

23502 D觸發(fā)器是一個(gè)具有記憶功能的,具有兩個(gè)穩(wěn)定狀態(tài)的信息存儲器件,是構(gòu)成多種時(shí)序電路的最基本邏輯單元,也是數(shù)字邏輯電路中一種重要的單元電路。

2019-12-02 07:06:00 6425

6425

時(shí)序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質(zhì)的區(qū)別在于時(shí)序電路具有記憶功能。

2019-09-27 07:10:00 2169

2169

異步時(shí)序電路是指電路中除以使用帶時(shí)鐘的觸發(fā)器外,還可以使用不帶時(shí)鐘的觸發(fā)器和延遲元件作為存儲元件;電路中沒有統(tǒng)一的時(shí)鐘;電路狀態(tài)的改變由外部輸入的變化直接引起.

2019-11-27 07:04:00 1624

1624 數(shù)字時(shí)序電路中通常用到的觸發(fā)器有三種:電平觸發(fā)器、脈沖觸發(fā)器和邊沿觸發(fā)器。

2019-07-05 14:38:54 13424

13424

本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)碼管與分析儀的時(shí)序電路原理圖免費(fèi)下載。

2019-12-13 15:17:11 8

8 時(shí)間的重要性不言而喻,加上時(shí)間這個(gè)維度就如同X-Y的平面加上了一個(gè)Z軸,如同打開了一個(gè)新的世界。所以今天我們就要來聊聊時(shí)序電路。 在時(shí)序電路中,電路任何時(shí)刻的穩(wěn)定狀態(tài)輸出不僅取決于當(dāng)前的輸入,還與

2021-01-06 17:07:22 4371

4371 電子發(fā)燒友網(wǎng)為你提供什么是時(shí)序電路?觸發(fā)器又是怎么回事資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-02 08:41:19 5

5 電子發(fā)燒友網(wǎng)為你提供“時(shí)序電路”及其核心部件觸發(fā)器的工作原理資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:51:02 13

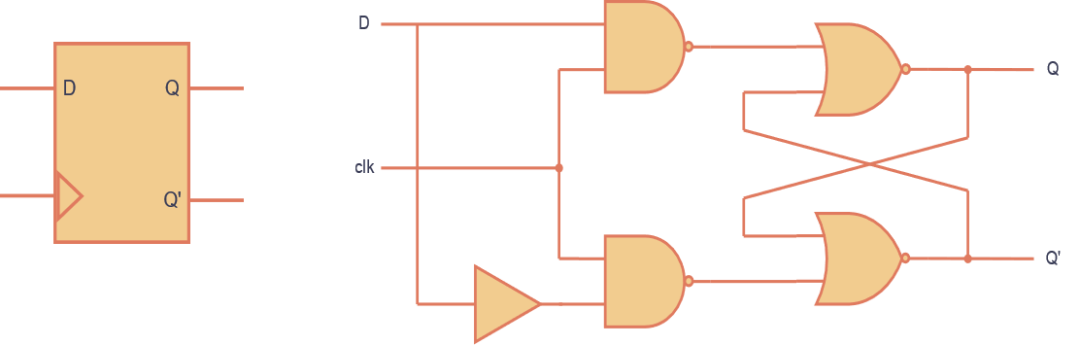

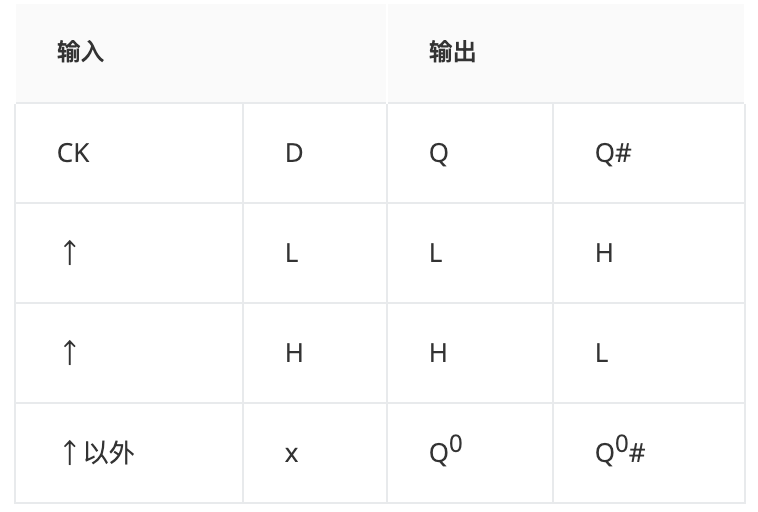

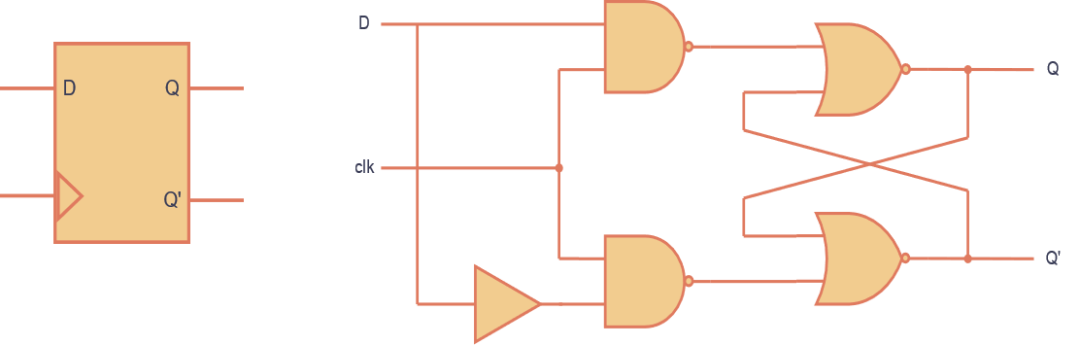

13 明德?lián)P有完整的時(shí)序約束課程與理論,接下來我們會一章一章以圖文結(jié)合的形式與大家分享時(shí)序約束的知識。要掌握FPGA時(shí)序約束,了解D觸發(fā)器以及FPGA運(yùn)行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開始講起。

2022-07-11 11:33:10 2922

2922

組合邏輯和時(shí)序邏輯電路是數(shù)字系統(tǒng)設(shè)計(jì)的奠基石,其中組合電路包括多路復(fù)用器、解復(fù)用器、編碼器、解碼器等,而時(shí)序電路包括鎖存器、觸發(fā)器、計(jì)數(shù)器、寄存器等。 在本文中,小編簡單介紹關(guān)于時(shí)序電路的類型和特點(diǎn)等相關(guān)內(nèi)容。

2022-09-12 16:44:00 7234

7234

1:鎖存器、觸發(fā)器、寄存器的關(guān)聯(lián)與區(qū)別 首先應(yīng)該明確鎖存器和觸發(fā)器是由與非門之類的東西構(gòu)成。尤其是鎖存器,雖說數(shù)字電路定義含有鎖存器或觸發(fā)器的電路叫時(shí)序電路,但鎖存器有很多組合邏輯電路的特性

2022-12-19 12:25:01 8207

8207 D 觸發(fā)器或數(shù)據(jù)觸發(fā)器是一種觸發(fā)器,它只有一個(gè)數(shù)據(jù)輸入“D”和一個(gè)時(shí)鐘脈沖輸入, 這種觸發(fā)器也稱為延遲觸發(fā)器,經(jīng)常用于許多時(shí)序電路,如寄存器、計(jì)數(shù)器等。下面一起來了解一下D觸發(fā)器不同應(yīng)用下的電路圖。

2023-01-06 14:19:46 4144

4144 觸發(fā)器是構(gòu)成時(shí)序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進(jìn)制信息的邏輯電路。在之前的文章中已經(jīng)介紹過觸發(fā)器了,這里再介紹一下其他類型的觸發(fā)器。

2023-03-23 15:13:26 9263

9263

那么,如何才能將過去的輸入狀態(tài)反映到現(xiàn)在的輸出上呢?「時(shí)序電路」到底需要些什么呢?人類總是根據(jù)過去的經(jīng)驗(yàn),決定現(xiàn)在的行動(dòng),這時(shí)我們需要的就是—記憶。同樣,「時(shí)序電路」也需要這樣的功能。這種能夠?qū)崿F(xiàn)人類記憶功能的元器件就是觸發(fā)器。

2023-03-24 10:48:58 818

818

同步和異步時(shí)序電路都是使用反饋來產(chǎn)生下一代輸出的時(shí)序電路。根據(jù)這種反饋的類型,可以區(qū)分這兩種電路。時(shí)序電路的輸出取決于當(dāng)前和過去的輸入。時(shí)序電路分為同步時(shí)序電路和異步時(shí)序電路是根據(jù)它們的觸發(fā)器來完成的。

2023-03-25 17:29:52 17511

17511

本文旨在總結(jié)近期復(fù)習(xí)的數(shù)字電路D觸發(fā)器(邊沿觸發(fā))的內(nèi)容。

2023-05-22 16:54:29 9071

9071

時(shí)序邏輯電路分析和設(shè)計(jì)的基礎(chǔ)是組合邏輯電路與觸發(fā)器,所以想要分析和設(shè)計(jì),前提就是必須熟練掌握各種常見的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎(chǔ)顯得尤為重要。 本文主要介紹時(shí)序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

時(shí)間的重要性不言而喻,加上時(shí)間這個(gè)維度就如同X-Y的平面加上了一個(gè)Z軸,如同打開了一個(gè)新的世界。所以今天我們就要來聊聊時(shí)序電路。

2023-06-20 16:59:50 252

252

,在很多應(yīng)用場景中都可以用來構(gòu)建序列發(fā)生器。本文將介紹使用D觸發(fā)器設(shè)計(jì)序列發(fā)生器的方法和步驟。 首先,我們需要了解D觸發(fā)器的基本原理和性質(zhì)。D觸發(fā)器是一種時(shí)序電路,它可以存儲和延遲一個(gè)輸入信號,并在時(shí)鐘信號到來時(shí)輸出

2023-08-24 15:50:17 2733

2733 D觸發(fā)器,是時(shí)序邏輯電路中必備的一個(gè)基本單元,學(xué)好 D 觸發(fā)器,是學(xué)好時(shí)序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構(gòu)成數(shù)字電路組合、時(shí)序邏輯的基礎(chǔ)。

2023-10-09 17:26:57 1230

1230

RS觸發(fā)器是一種經(jīng)典的數(shù)字邏輯電路元件,用于存儲和控制信息流。它是由兩個(gè)反饋?zhàn)饔玫倪壿嬮T組成,常用于時(shí)序電路和數(shù)據(jù)存儲。 RS觸發(fā)器由兩個(gè)互補(bǔ)的輸出Q和~Q組成,其中Q表示觸發(fā)器的狀態(tài)

2023-11-17 16:14:28 898

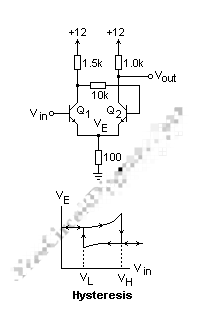

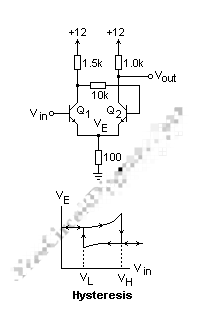

898 施密特觸發(fā)器是一種常見的數(shù)字電路元件,主要用于時(shí)序電路和數(shù)字邏輯電路中。它是由兩個(gè)雙穩(wěn)態(tài)門電路(或稱為非門電路)構(gòu)成的。在施密特觸發(fā)器中,輸出是由輸入信號的變化而變化的,而不是根據(jù)門電路的輸入和輸出

2024-01-12 16:50:30 321

321 jk觸發(fā)器是一種常見的時(shí)序電路元件,常用于計(jì)數(shù)器、寄存器以及存儲器等電子電路中。本文將介紹jk觸發(fā)器的特征方程以及推導(dǎo)過程。 jk觸發(fā)器的基本結(jié)構(gòu)及原理 jk觸發(fā)器由兩個(gè)交叉耦合的反饋環(huán)組成,它具有

2024-01-17 10:00:22 314

314 RS觸發(fā)器與SR觸發(fā)器都是基本的數(shù)字邏輯電路元件,常用于存儲、控制和時(shí)序電路中。

2024-01-29 14:15:08 459

459 時(shí)序電路是由觸發(fā)器等時(shí)序元件組成的數(shù)字電路,用于處理時(shí)序信號,實(shí)現(xiàn)時(shí)序邏輯功能。根據(jù)時(shí)序元件的類型和組合方式的不同,時(shí)序電路可以分為同步時(shí)序電路和異步時(shí)序電路。本文將從這兩個(gè)方面詳細(xì)介紹時(shí)序電路

2024-02-06 11:22:30 291

291 ,時(shí)序電路可以分為同步時(shí)序電路和異步時(shí)序電路。接下來,我們將詳細(xì)討論時(shí)序電路的分類以及其基本單元電路。 一、同步時(shí)序電路 同步時(shí)序電路是指所有的時(shí)鐘信號在整個(gè)電路中具有相同的時(shí)鐘頻率和相位。它包括鎖存器、觸發(fā)器

2024-02-06 11:25:21 399

399 時(shí)序電路基本原理是指電路中的輸出信號與輸入信號的時(shí)間相關(guān)性。簡單來說,就是電路的輸出信號要依賴于其輸入信號的順序和時(shí)間間隔。 時(shí)序電路由時(shí)鐘信號、觸發(fā)器和組合邏輯電路組成。時(shí)鐘信號是時(shí)序電路的重要

2024-02-06 11:30:00 344

344

電子發(fā)燒友App

電子發(fā)燒友App

評論