摘 要

針對SiC MOSFET模塊應用過程中出現的串擾問題,文章首先對3種測量差分探頭的參數和測 量波形進行對比,有效減小測量誤差;然后詳細分析串擾引起模塊柵源極出現電壓正向抬升和負向峰值過大 的原因,并提出3種有效應用對策:減小柵極阻抗、采用有源米勒箝位和三級關斷串擾抑制電路。其中,減小柵極阻抗可減小感應壓降,抑制柵源極過壓;有源米勒箝位技術使柵源極電壓串擾波形幅值限制在箝位電 壓范圍;利用三級關斷串擾抑制電路技術,顯著抑制了柵源極電壓的正向抬升和負向峰值,最后通過試驗仿 真驗證了3種方法的有效性。

0? 引言

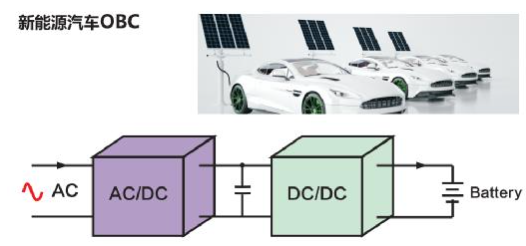

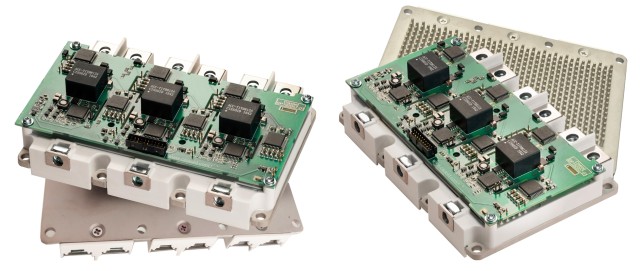

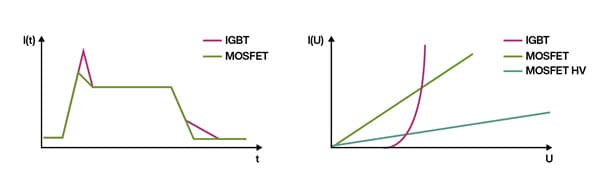

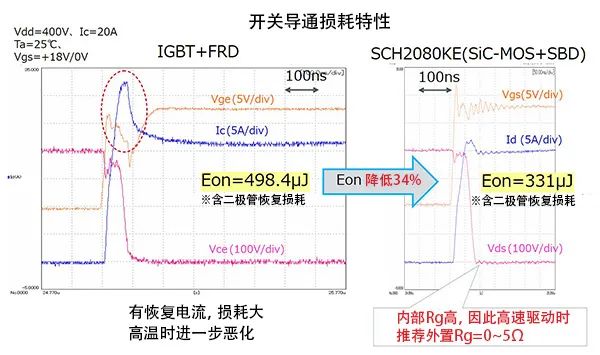

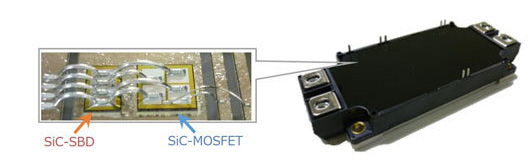

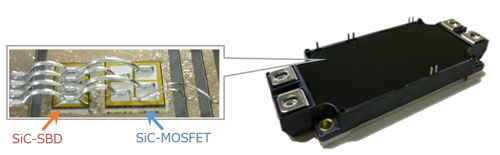

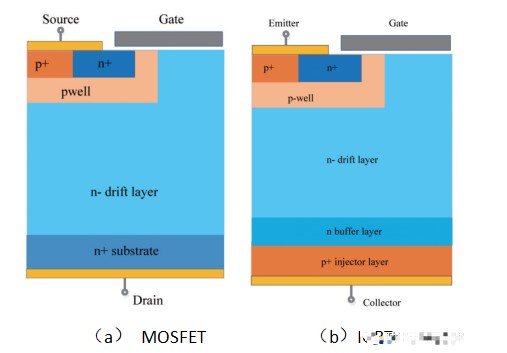

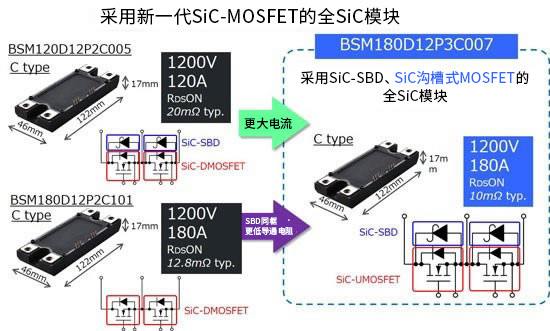

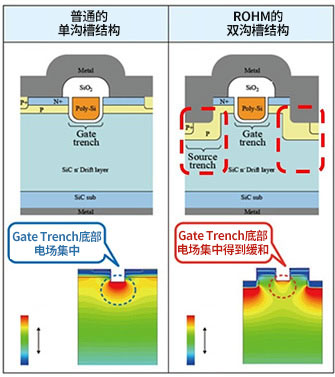

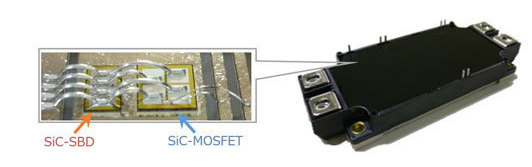

Si(Silicon)基IGBT(Insulated Gate Bipolar Tran‐ sistor)是由雙極型三極管(Bipolar Junction Transistor, BJT和絕緣柵型場效應管(Metal Oxide Semiconduc‐ tor,MOS)組成的復合全控型器件,綜合了兩種器件 的優點,并采用電壓控制器件開關,驅動功率小且飽和壓降低,適用于軌道交通、電網、汽車和新能源等 變流領域。相比較于Si材料,SiC(Silicon Carbide)具 有更大的禁帶寬度、更高的臨界擊穿場強和電子飽和 漂移速度等諸多優點,應用在單極型模塊SiC MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)中可使其開關損耗更低,在高溫、大功率和高頻率的嚴 苛條件下也能正常工作?。?

SiC MOSFET模塊目前廣泛運用于新能源汽車逆變器、車載充電、光伏、風電、智能電網等領域,展示了新技術的優良特性。但 SiC MOSFET 模塊的高頻化和高開關速度,引發了新的應用問題,即串擾問題, 對SiC MOSFET模塊應用造成影響,嚴重時會導致SiC ?MOSFET模塊無法正常工作。?

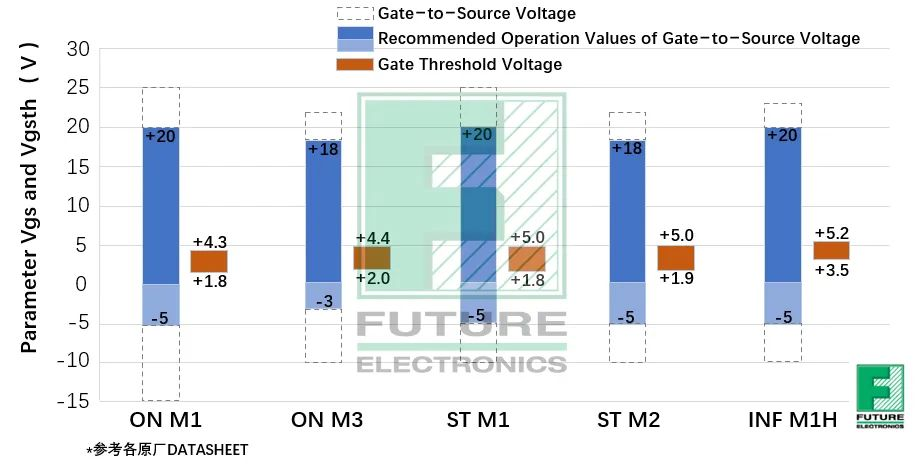

串擾問題是指在半橋電路中,SiC MOSFET模塊開關動作引起另一個 SiC MOSFET 模塊開關的柵源極電壓波動的問題,分為正向串擾和負向串擾。以1200 V/ 600 A SiC MOSFET為例,柵極開通控制電壓為+15 V, 柵極關斷電壓為-5 V。當半橋電路發生正向串擾時, 上橋臂SiC MOSFET(以下簡稱“上管”)的柵極電壓 由-5 V升高至+15 V,上管開通過程會引起下橋臂SiC ?MOSFET (以下簡稱“下管”) 的柵極電壓從-5 V向 0 V方向升高,即正向抬升,若正向抬升超過下管柵極閾值將導致誤開通,造成上下管短路。當發生負向串擾時,上管柵極由+15 V降低為-5 V,上管關斷過程則 引起下管柵極電壓從-5 V向更低負壓方向變化,即負向增大,若負向增大超過下管柵極負壓耐受極限將會 導致柵極擊穿,從而造成器件失效。?

現有學者對 SiC MOSFET 模塊的串擾 問題已做了大量研究。串擾的發生與應用電路、驅動 技術和 SiC MOSFET 型號等都有關聯,對應不同的應用場景和SiC MOSFET型號,會出現不同程度的串擾。本文選取1200 V/600 A SiC MOSFET 為研究對象,針對串擾問題提出3種應對策略:串擾影響程度較輕時, 通過減少柵極阻抗的方式抑制串擾,該方法簡單且成 本低;當串擾影響程度較嚴重時,如減少柵極阻抗未 能有效抑制串擾問題,可采用有源米勒箝位(AMC)技術,限制柵源極電壓串擾波形幅值;在串擾特別嚴重工況下,上述兩種方法有可能失效,則可增加柵源 電壓模擬檢測電路,結合三級關斷驅動技術應對串擾問題。

1 原理分析

1.1 測量探頭對比分析?

串擾現象客觀存在,而測量誤差會對串擾問題研 究造成嚴重的干擾影響。為保證測量電路參數波形的 準確性,本文對測量使用的差分探頭進行分析,通過 對比實測數據,有效減小測量誤差。?

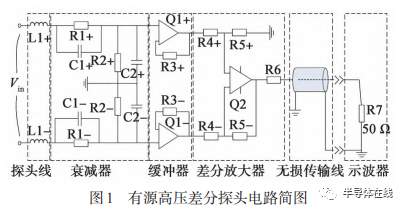

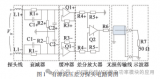

半橋電路中SiC MOSFET模塊的漏源極電壓Vds和 柵源極電壓Vgs均采用高壓差分探頭測量,被測信號 經過差分信號端電感、衰減器、緩沖器、差分放大器 和無損傳輸線等環節,連接到示波器,如圖 1 所示。SiC MOSFET模塊在高頻高壓下工作時,測試電壓探頭 需考慮帶寬、共模抑制比等參數。探頭帶寬是指探頭 測量輸出波形幅值下降到被測波形正弦波幅值 70.7% (-3 dB=20 lg 0.707) 的頻率,即當被測正弦波的頻率 等于示波器帶寬時,幅值測量誤差大約為 30%。對于 漏源極電壓Vds和柵源極電壓Vgs,30%測量誤差過大無 法準確分析串擾問題。因此,探頭帶寬需遠大于被測 波形的頻率,帶寬越大,則能測到更寬的高頻諧波, 越接近真實波形。同時差分探頭線選擇較短的雙絞線、 使線路等效電感L1+和L1-盡量小。

共模抑制比Kcmrr是指差分探頭在測量中抑制兩個 測試點共模信號的能力。共模信號即對地干擾信號, 因此探頭的差分放大電路抑制共模信號的能力越強, 測量波形越接近真實值,其公式為 Kcmrr?= | Ad?Ac?|,其 中Ad為差分信號的電壓增益,Ac為共模信號的電壓增 益。Ad值越大說明差分信號增益越大,共模信號相對 越小,測量值越接近真實波形。?

數字示波器組成如圖 2 所示,進入示波器的信 號,經過信號調理電路、采集控制電路和信號處理等 環節,最后顯示為波形。測試高頻高壓下的信號,需 考慮示波器的帶寬、采樣率、存儲深度等參數影響。與差分探頭一樣,示波器帶寬不夠,也無法捕獲準確 的電壓波形。示波器將采集到的波形存儲到內存區進行計算和處理,內存區容量即存儲深度為固定值。示 波器每幀波形的時間長度是人為調節設定的,當時間 長度設定后,采樣率為存儲深度與時間長度的比值。測量 SiC MOSFET 模塊瞬態高頻高壓信號時,采樣率 盡可能高才能確保測試準確,因此,每幀波形的時間 長度不能設定太大,存儲深度過小都會導致采樣率降低,引起較大測量誤差。

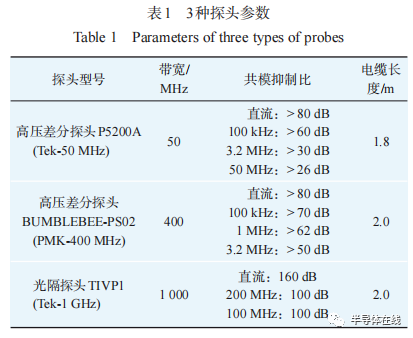

常用的3種探頭有:高壓差分探頭P5200A,高壓 差分探頭BUMBLEBEE-PS02和光隔探頭,對3種探頭 的參數進行對比分析,如表1所示。由表1可知,光隔 探頭 TIVP1 的帶寬和共模抑制比參數性能遠大于高壓 差分探頭P5200A和BUMBLEBEE-PS02。

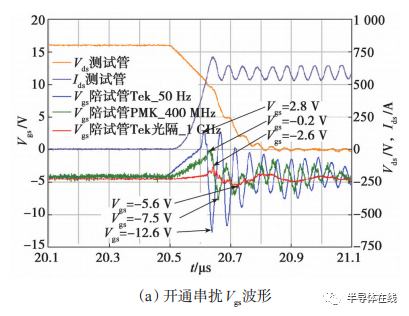

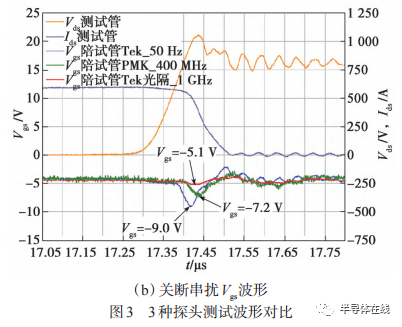

為了對比 3 種探頭的測試效果,搭配 Tek MSO58 示波器測試 SiC MOSFET 模塊串擾波形。Tek MSO58 示波器的帶寬為2 GHz,存儲深度為125 M,采樣率為 6.25 GS/s,每幀波形的時間長度為20 ms。3種探頭測 量 SiC MOSFET 模塊的柵源極電壓 Vgs波形對比如圖 3所示。圖3(a)為串擾開通過程,模塊內測試管的漏源極 電壓 Vds 從 800 V 下降至 0 V,測試管漏源極電流 Ids 從 0 A逐漸上升到最大值;圖3(b)為串擾關斷過程。由圖 3可知,采用光隔探頭TIVP1測量的柵源極電壓Vgs波 形抗干擾性強,采樣精度高,遠優于其他兩種探頭。因此精準測量 SiC MOSFET 模塊串擾波形推薦光隔探 頭TIVP1。?

1.2 串擾產生機制?

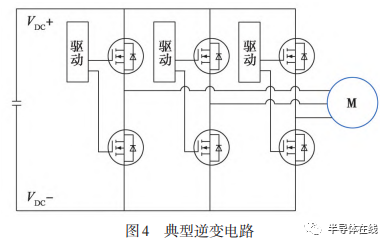

典型逆變電路如圖4所示,它有3組半橋電路,每 個半橋電路由上橋臂和下橋臂組成。上、下橋臂的SiC ?MOSFET模塊不能同時開通,必須為互補的高速開關 切換狀態,每秒鐘將完成上萬次或更高次開關動作, 這會造成模塊的漏極和源極之間產生較大 dVds?/dt,將 導致模塊柵極和源極間的電壓具有較大的尖峰。

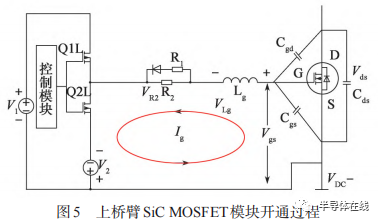

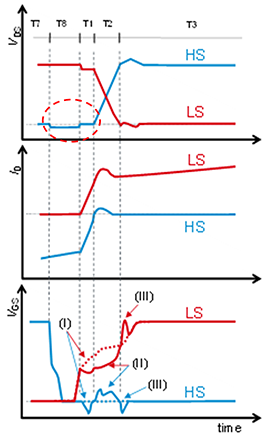

SiC MOSFET模塊的開通過程如圖5所示,對其柵 源極電壓的正向抬升進行分析。當上橋臂模塊開通時, 推挽開關Q1L斷開,推挽開關Q2L閉合,下橋臂模塊 的二極管進行反向恢復動作,漏源間電壓Vds逐步開始 增加,dVds?dt大于0。反向傳輸電容 (也稱米勒電容) Cgd上的位移電流Ig從漏極經柵極注入到門極電路。Lg 為柵極引線雜感,位移電流Ig流過Lg后,由楞次定律可知,產生左負右正的感應電動勢VLg,此時柵源間電 壓為

式中:VR2為電阻R2上的電壓;-V2是驅動負電源。因此,當上橋臂模塊開通時,會導致下橋臂模塊 柵源極電壓Vgs在-V2的基礎上正向抬升VLg?+ VR2。

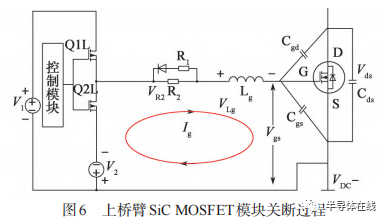

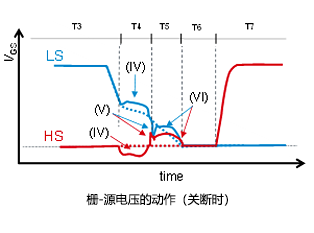

SiC MOSFET模塊的關斷過程如圖6所示,同樣對 其柵源極電壓的負向增大現象進行分析。當上橋臂模 塊關斷時,Q1L 斷開,Q2L 閉合,下橋臂模塊的二極 管進行正向續流動作,漏源間電壓 Vds 開始下降, dVds dt小于0。反向傳輸電容Cgd上的位移電流則從柵 極到漏極。位移電流 Ig 流過 Lg后,由楞次定律可知, 產生左正右負的感應電動勢VLg,此時柵源間電壓Vgs = -V2 -(VLg + VR2 )。因此,當上橋臂模塊關斷時,下橋臂 模塊的柵源極電壓會在 -V2 的基礎上負向疊加增大 VLg?+ VR2。

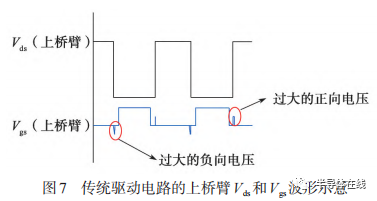

傳統驅動電路的上橋臂Vds和Vgs波形如圖7所示。

由于 SiC MOSFET 模塊柵源極之間的正向閾值電 壓較低,正向電壓抬升易造成功率模塊誤導通,從而 使得上下橋臂直通,而直通電流將造成模塊短路損壞。另外,過大的電壓負向峰值使 SiC MOSFET 功率模塊 的門極柵氧層承受較大的電壓應力,加速其退化,甚至損壞。?

2 應對策略?

2.1 減小柵極阻抗?

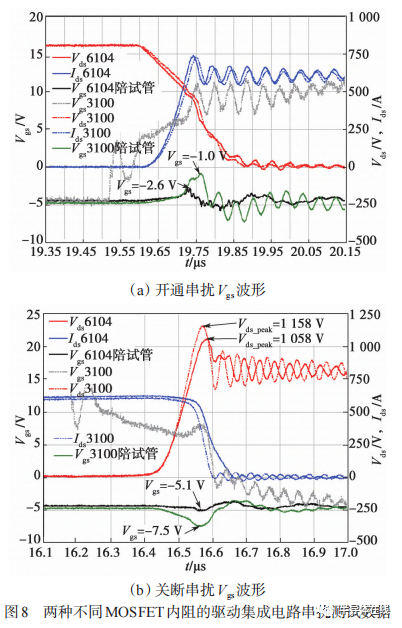

從串擾產生機制可知,柵極引線阻抗和位移電流 是造成柵源極電壓正向抬升和負向增大的直接因素, 減小柵極引線阻抗和位移電流,則能抑制串擾引起的 柵源極電壓變化幅值。柵極引線阻抗包含驅動輸出電 路阻抗和 SiC MOSFET 模塊內部柵極引線端子阻抗。由于減小 SiC MOSFET 模塊內的柵極阻抗可能會引起 模塊開關速度變化,對模塊器件的開關動態損耗和過 電壓值有一定影響,通過調整柵極電容,可有效折中 電參數。因此重點在驅動電路的設計中考慮減小輸出 電路阻抗。本文對比分析了兩種MOSFET內阻的驅動 集成電路 (Integrated Circuit,IC ) 串擾測試數據,如 圖8所示。第一種MOSFET內阻為500 mΩ,對應的驅動集成電路型號是NXP GD3100,圖中 Vgs 3100表示其 柵源極電壓;第二種 MOSFET 內阻為 15 mΩ,對應的 驅動集成電路型號是ROHM BM6104FV,圖中Vgs 6104 表示其柵源極電壓。由圖 8 可知,驅動集成電路 ROHM BM6104FV對應的內阻更小,相較于驅動電路 NXP GD3100受到的串擾影響也降低。?

2.2 采用有源米勒箝位AMC(active miller clamp)?

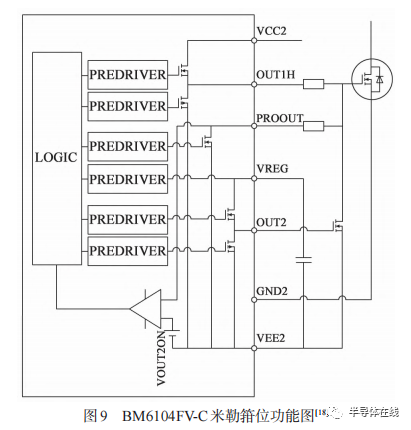

在逆變半橋電路中,由于米勒電容 Cgd?的存在, 串擾會引起柵源極電壓 Vgs?波動,而有源米勒箝位 AMC 技術可抑制柵源極電壓 Vgs?波動,有效防止 SiC MOSFET模塊橋臂直通。圖9為BM6104FV-C米勒 箝位功能示意圖,引腳VCC2為正電源,引腳OUT1H 為 驅 動 電 源 , 引 腳 PROOUT 為 Vgs?檢 測 腳 , 引 腳 VREG 為米勒箝位電源,引腳 VEE2 為負電源,引腳 OUT2 控制外部 MOS 開關。在 SiC MOSFET 模塊關斷 期間,此時驅動電源 OUT1H 為低電平,通過 PRO‐ OUT 端實時監測柵源極電壓 Vgs,如 Vgs?小于保護閾值 2 V,則OUT2端輸出高電平,外部MOS開關將導通, 柵極電位箝位至 VEE2,柵源極形成低阻抗回路,米 勒電流通過 VEE2 被完全吸收,不會流經柵極電阻形 成米勒電流泄放回路。在SiC MOSFET模塊導通期間, 此時驅動電源 OUT1H 為高電平,監測到 Vgs?大于保護 閾值時,則外部MOS開關將斷開,避免電源短路。引 腳 VREG 和 VEE2 之間連接電容,能有效抑制柵源極電壓波動。

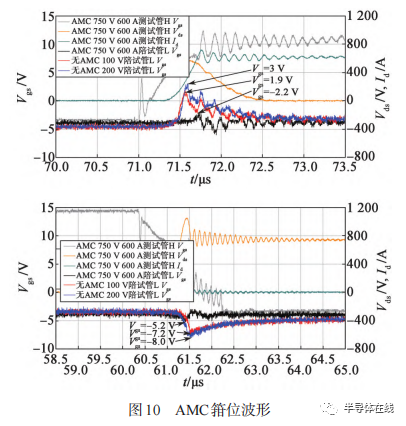

有源米勒AMC箝位波形如圖10所示,下管開通期 間串擾引起的上管柵源極電壓峰值 Vgs_peak=-2.2 V,遠 遠小于0 V;下管關斷期間串擾引起的上管柵源極電壓 峰值 Vgs_peak=-5.2 V,此時未出現大的負向峰值電壓。因此在開通和關斷情況下都起到了較好箝位效果。

2.3 采用三級關斷串擾抑制電路?

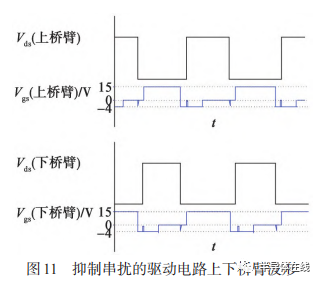

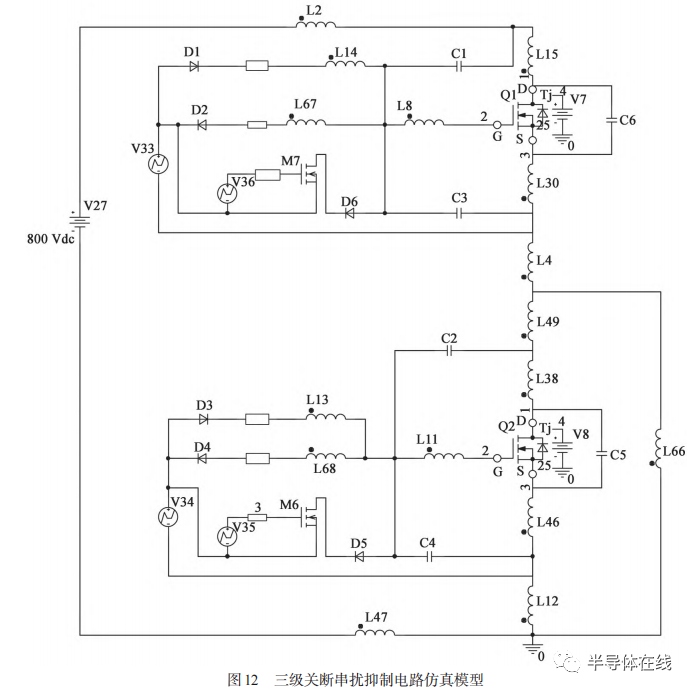

模塊門極關斷期間柵源極電壓Vgs為-4 V,串擾發 生時會引起Vgs抬升,若采用三級關斷串擾抑制電路檢 測柵源極電壓,當Vgs超過設定閾值,抑制電路可將Vgs?直接拉低到-4 V,抑制其正向抬升;當串擾引起過大 的電壓負向峰值時,三級關斷串擾抑制電路可將Vgs拉 升到0 V,抑制柵源極出現較大的電壓負向峰值,從而 保護柵極。圖11為抑制串擾驅動電路的上下橋臂Vds和Vgs工 作波形。Vgs?(上橋臂) 包含3種電平,+15 V,0 V和 -4 V。當Vgs(上橋臂)為+15 V時,SiC MOSFET模塊 為開通狀態;當 Vgs (上橋臂) 為 0 V 和-4 V 時,SiC ?MOSFET模塊為關斷狀態。為驗證上述方法的有效性, 搭建了三級關斷串擾抑制電路的PSPICE半橋斬波電路 模型,如圖12所示。

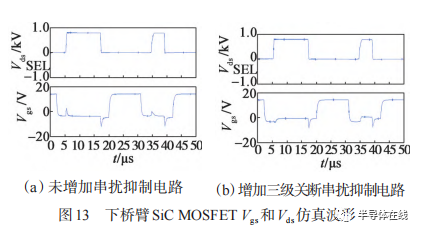

圖13為下橋臂SiC MOSFET Vgs和Vds的仿真波形。圖 13(a)為未增加串擾抑制電路時的相關波形,此時 SiC MOSFET柵源極電壓Vgs在關斷期間抬升約為+2 V, 可能會誤觸發 SiC MOSFET 開通造成短路,而最大電 壓負向峰值約為-12 V,易損傷SiC MOSFET柵源極造 成器件失效。圖13(b)為模塊驅動電路增加了串擾抑制 措施時的相關波形,此時SiC MOSFET柵源極電壓Vgs?在關斷期間抬升電壓最大約為-4 V,基本沒有抬升,電壓最大負向峰值約為-8 V。可見,增加串擾抑制電 路后,柵源極電壓的負向電壓和正向抬升都明顯改善。?

3 結語?

針對 SiC MOSFET 模塊應用中出現的串擾問題, 本文對測量使用的差分探頭進行了詳細對比,由結果 可知采用高帶寬和高采樣率的示波器和差分探頭可測 量得到準確的信號波形。同時分析了串擾問題的產生 機制,正dVds dt在反向傳輸電容上產生流向驅動側的 位移電流,在柵極阻抗引起正向感應電壓,疊加在柵 源極上會引起柵源極電壓抬升;而負dVds dt在反向傳 輸電容上產生流向模塊側的位移電流,在柵極阻抗引 起負向感應電壓,造成柵源極出現過大的電壓負向峰 值。為解決串擾問題,本文提出了3種有效應用對策:①減小柵極引線阻抗,從而減小阻抗上的感應壓降, 抑制柵源極過壓;②采用有源米勒箝位技術,泄放位 移電流,有效保護 SiC MOSFET 模塊;③通過三級關 斷串擾抑制技術改善柵極驅動波形,有效抑制過大的電壓正向抬升和負向電壓。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論