引言:從本文開始,我們介紹下項目中設計的并行LVDS高速DAC接口設計,包括DAC與FPGA硬件接口設計、軟件設計等。項目設計高速DAC采用了ADI公司的AD9129,該芯片最大更新速率5.7Gsps,該芯片在寬帶通信應用、LTE、雷達信號產生、干擾機等領域有廣泛應用。

1. AD9129概述

AD9129是高性能14位RF數模轉換器(DAC),支持最高達2.85GSPS的數據速率。DAC內核基于一個四通道開關結構,使雙邊沿時鐘能夠有效運行,配置為混頻模式(Mix-Mode)或2倍插值時,能將DAC更新速率提高至5.7GSPS。在混頻模式中,AD9129可在二階和三階奈奎斯特區內重構RF載波,同時仍保持高達4.2GHz的出色動態范圍。其高性NMOS DAC內核具有四通道開關結構,能以最小輸出功耗實現業界領先的直接RF頻率合成性能。輸出電流可以在9.5mA至34.4mA范圍內進行編程。

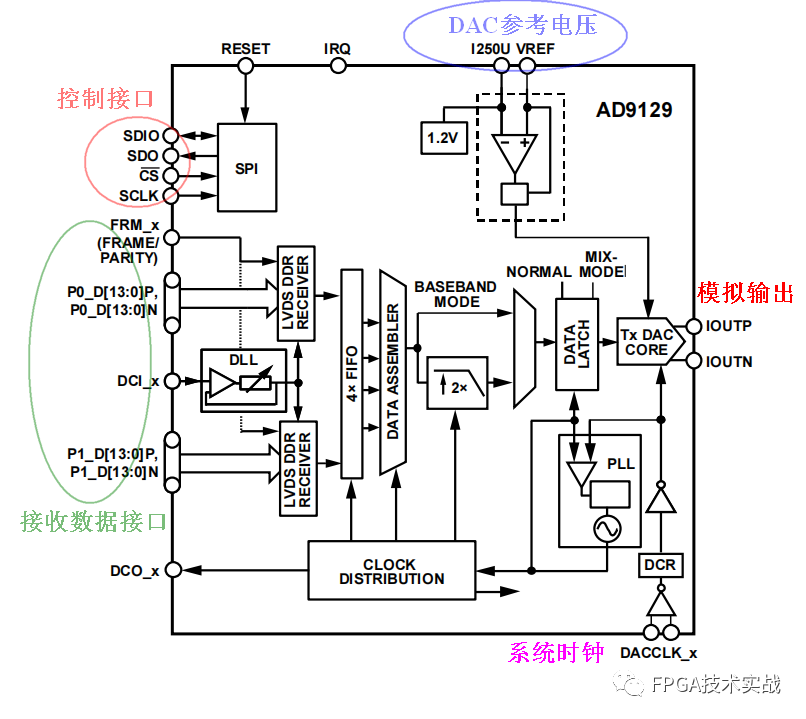

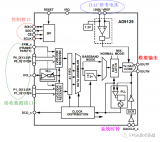

圖1:AD9129系統框圖

2.AD9129接口描述

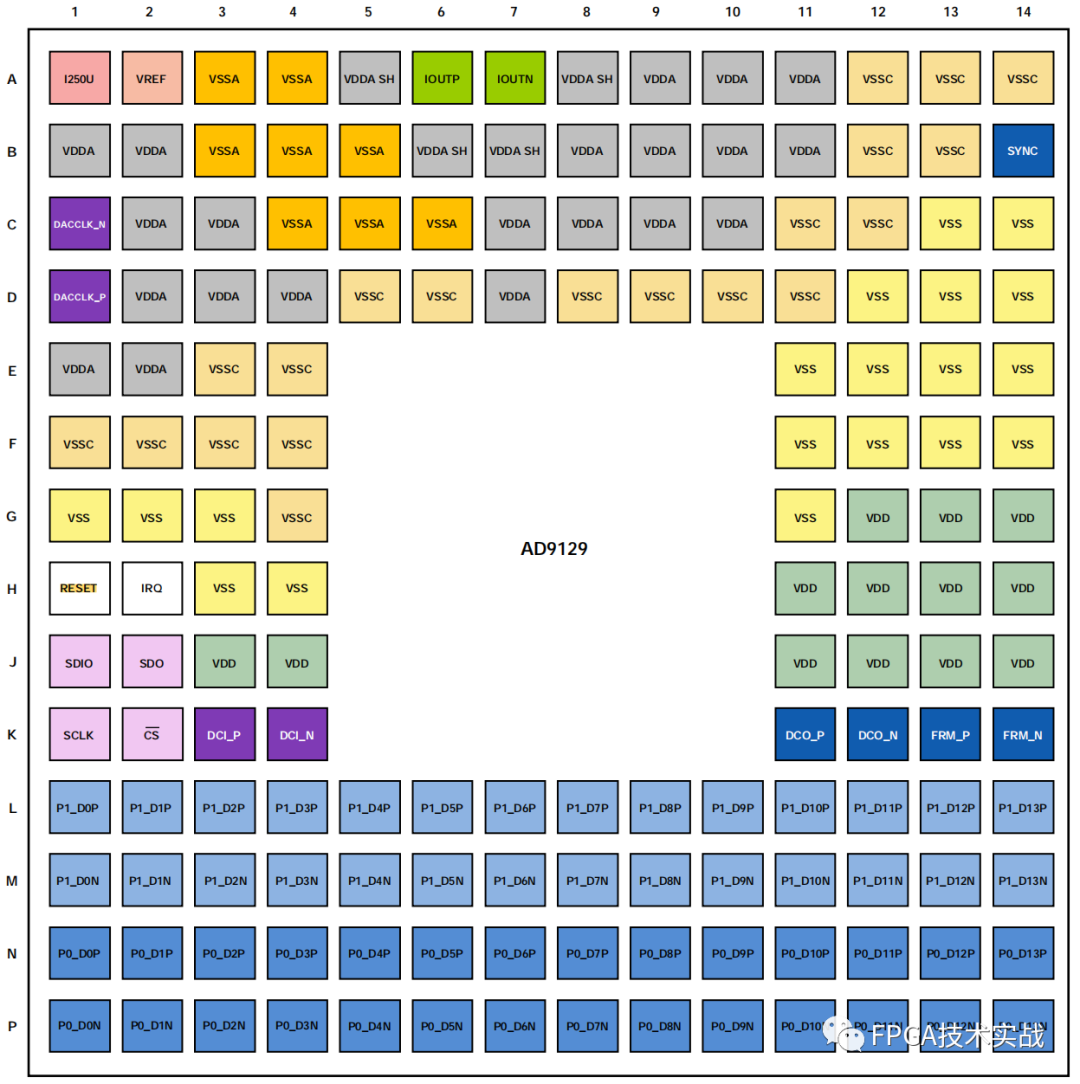

圖2:AD9129管腳分布

如圖1所示,AD9129接口主要分為與主機FPGA互聯的控制接口(包括SPI接口、復位等)和LVDS源同步數據接口,參考電壓接口,DAC時鐘接口(包括DCO_x、DACCLK_x)以,DAC模擬輸出接口以及供電接口(圖1中未標出)。

2.1控制接口

AD9129控制接口包括SPI接口、復位接口。SPI接口包括四個信號:SCLK、CSn、SDO、SDIO,通過該接口可以實現DAC內部寄存器的配置。SPI接口支持MSB(最高有效位)優先和LSB(最低有效位)優先傳輸格式。AD9129串行接口端口可以配置為單I/O引腳(SDIO),或者配置為兩個單向輸入/輸出引腳(SDIO和SDO)。SCLK最大工作時鐘為20MHz。

復位信號RESET為高電平復位,如果未使用此管腳,需接地處理。SPI及RESET接口電平為1.8V IO。

2.2 LVDS源同步數據接口

AD9129數據輸入接口為LVDS源同步數據接口,包含源同步時鐘DCI、兩組數據接口P0_D和P1_D,分辨率為14bits。LVDS接口電平為1.8V,典型輸入阻抗為100Ω。

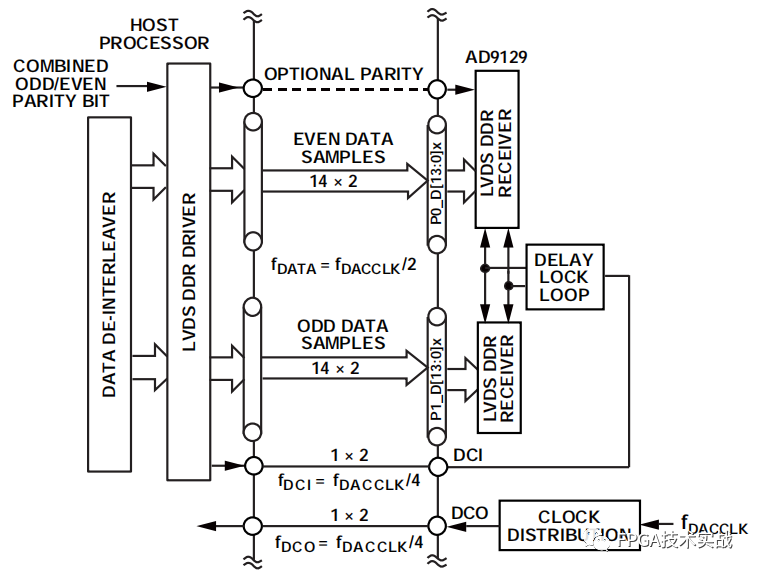

AD9129與FPGA之間的接口關系如下圖所示。

圖3:AD9129與FPGA之間的接口關系

2.3參考電壓VREF接口

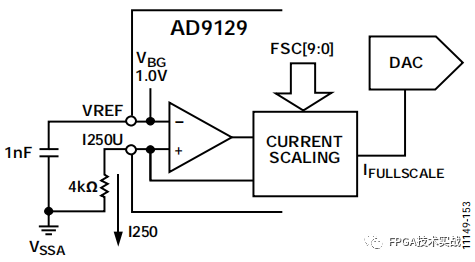

AD9129輸出電流由數字控制位和I250U基準電流共同設置,如圖下圖所示。

圖4:基準電壓源電路

將VREF施加于I250U(引腳A1)與VSSA之間的4.0 kΩ外部電阻,便可獲得基準電流。1.0 V標稱參考電壓(VREF)在4.0 kΩ電阻中產生250 μA基準電流。配置基準電壓電路應注意以下幾點限制:

? 為使器件正常工作,4.0 kΩ電阻和1 nF旁路電容均是必需的。

? 將DAC輸出滿量程電流IOUTFS調整為默認設置20 mA以外的值時,應以數字方式執行。

? AD9129不是乘法DAC,不支持用交流信號對基準電流I250U進行調制。

? VREF引腳上的帶隙電壓必須緩沖才能用于外部電路,因為其輸出阻抗約為7.5 kΩ。

? 可以將一個外部基準源連接到VREF引腳,以過載內部基準源。

2.4時鐘接口

DAC時鐘接口包括DAC工作時鐘DACCLK_x和DCO_x時鐘。DACCLK_x時鐘用于設置DAC的更新速率,還路由至時鐘分配模塊以產生所有關鍵的內部和外部時鐘DCO_x。DCO_x=1/4*DACCLK_x。DCO時鐘與DCI時鐘頻率相同,以建立同步操作,如圖3所示。

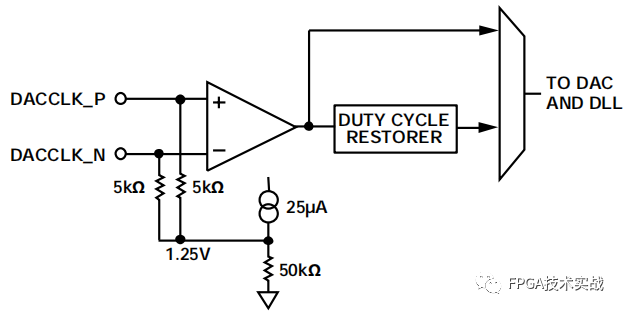

圖5:DACCLK_x時鐘輸入

DACCLK_x輸入連接到一個高頻PLL以確保DAC采樣時鐘可靠地鎖定輸入時鐘。PLL默認使能,上電后即鎖定。

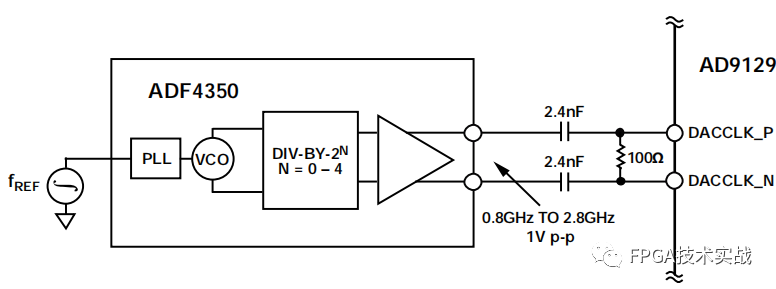

圖6:DACCLK_x輸入的可能信號鏈

DACCLK_x輸入的峰峰值電壓為0.25~2V,典型值為1V,共模電壓為1.25V。DACCLK_x輸入時鐘頻率范圍為1.4G~2.85GHz。

DCO_x時鐘輸出時鐘阻抗100Ω,最大時鐘712.5MHz,輸出電壓為1.025~1.375V,共模電壓為1.25V。

DACCLK_x差分時鐘可以接受正弦信號;如果輸入信號電平保持在0dBm以上,則NSD(噪聲譜密度)性能降低可忽略不計。?5dBm輸入時,性能降低+1dB;當信號接近?10dBm時,性能進一步降低,達到+2dB。時鐘接收器之后有一個占空比恢復器(DCR),用于確保后續電路的占空比接近50%。DCR的輸出用作主時鐘,直接路由至DAC。此外時鐘源的質量是保持最佳交流性能的重要考慮因素,可從三方面來定義:相位噪聲特性、抖動和驅動能力。

2.5模擬輸出接口

AD9129提供互補電流輸出IOUTP和IOUTN,吸收外部負載的電流,外部負載由1.8 V VDDA電源供電。

2.5.1峰值DAC輸出功率能力

差分電流輸出DAC的最大峰值功率能力取決于峰值差分交流電流IPEAK和等效負載電阻。對于具有50 Ω源端接電阻的1:1巴倫,DAC交流電流源的等效負載為25 Ω。如果AD9129設置IOUTFS = 20 mA,則其峰值交流電流為9.375 mA,提供給等效負載的峰值功率為2.2 mW(即P = I2R)。由于1:1巴倫的源電阻和負載電阻相等,因而此功率由二者均分。所以,輸出負載獲得1.1 mW或0.4 dBm的峰值功率。

要計算提供給負載的均方根功率,需考慮以下事項:

? 數字波形的峰值與均方根之比

? 相對于數字滿量程的任何數字倒退

? DAC sinc響應和外部網絡中的非理想損耗

2.5.2輸出級配置

AD9129設計用于需要寬信號重構帶寬或高IF/RF信號產生的高動態范圍系統。最佳交流性能只有在以下情況下才能實現:DAC輸出配置為差分(即平衡)工作模式,輸出共模電壓偏置到穩定的低噪聲1.8 V標稱模擬電源(VDDA)。用于與DAC接口的輸出網絡應提供接近0 Ω的直流偏置路徑以連接到VDDA。

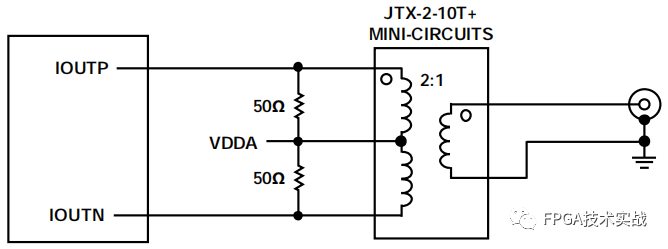

在整個頻率范圍內,IOUTP和IOUTN引腳之間的任何輸出阻抗不平衡都會降低失真性能(主要是偶數階失真)和噪聲性能。元件選擇和布局對于實現AD9129的潛在性能至關重要。大多數要求平衡到不平衡轉換且工作頻率為10 MHz到1 GHz的應用,都可以利用Mini-Circuits JTX系列變壓器,它可提供2:1和1:1的阻抗比。

圖7:寬帶應用的推薦變壓器,帶寬上限高達2.2 GHz

圖7顯示AD9129與JTX-2-10T變壓器接口。此變壓器可提供出色的幅度/相位平衡(<1 dB/1°,最高1 GHz),通過提供0 Ω直流偏置路徑以連接VDDA。如果需要濾除DAC鏡像和時鐘成分,可在單端側應用一個模擬LC濾波器,其好處是可以保持變壓器的平衡。

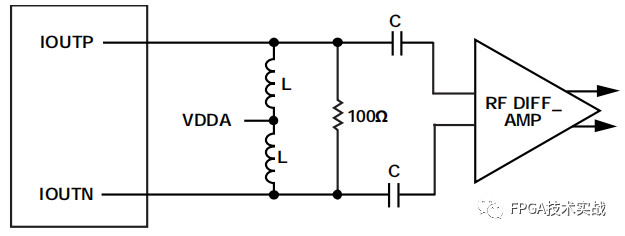

圖8:DAC輸出與自偏置差分增益級接

圖8顯示了將DAC輸出與自偏置差分增益模塊接口時可以考慮的接口。電感(L)用作RF扼流圈,提供直流偏置路徑以連接到VDDA。其值與隔直電容一起決定復合通帶響應的截止頻率下限。(隔直電容與RF差分增益級的輸入電阻一起形成高通響應。)

許多RF差分放大器由兩個增益匹配的單端放大器組成,因而無法提供共模抑制,而且由于匹配不佳,還可能降低平衡。此外,由于元件容差,差分LC濾波器可能會進一步降低差分信號路徑的平衡。兩種情況下,使用巴倫均非常有利,可在濾波或進一步放大之前,抑制RF DAC的共模失真和噪聲成分。

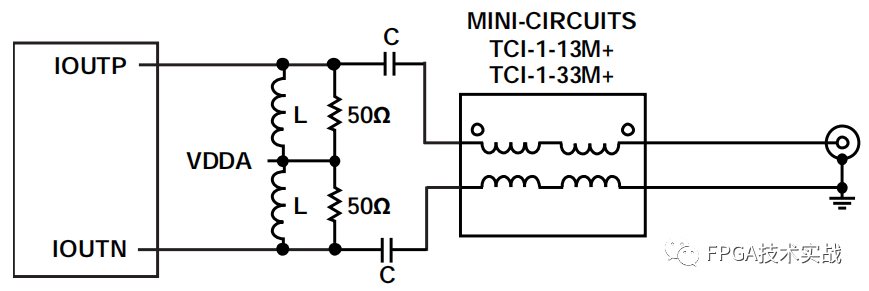

圖9:建議混頻模式配置,提供擴展的RF帶寬,采用TC1-1-13M+巴倫

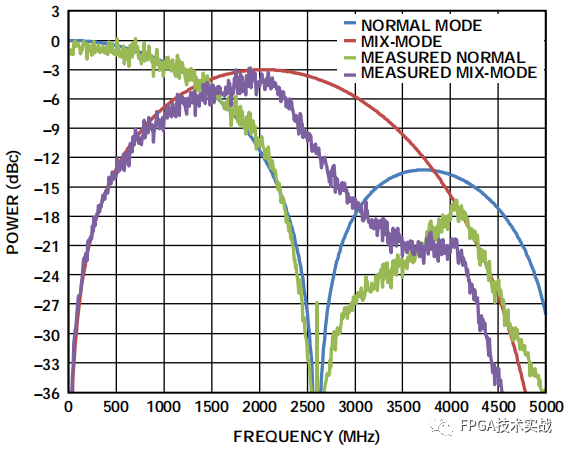

對于在混頻模式下使用AD9129且輸出頻率超過2.2 GHz的應用,用戶可以考慮圖9所示的電路。此電路采用寬帶巴倫(例如4.0 GHz時為?3 dB)來為DAC輸出提供直流偏置路徑,其配置與圖7所示范例相似。此電路是在評估板上實現,結果如圖10所示。

圖10:實測與理想DAC輸出響應,fDAC = 2.6 GSPS

2.6電源接口

AD9129電源分為模擬電源和數字電源,整個芯片最大功耗在1.1W左右。

模擬電源VSSA=-1.5V,Imax=54mA;

模擬電源VDDA=1.8V,Imax=230mA;

數字電源VDD=1.8V,Imax=336mA。

3.小結

本文簡單介紹了AD9129的基礎知識,包括芯片的重要特性,外部接口相關的信號特性等。下一篇我們重點介紹下項目中FPGA與AD9129互聯的原理圖設計,包括LVDS IO接口設計、時鐘電路以及供電設計。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論