為了在USB 3.0中實現數據的8 b/10 b編解碼,把8b/10b編解碼分解成5 b/6 b編解碼和3 b/4 b編解碼,然后在FPGA上實現了具體的硬件電路。

2011-11-30 11:38:18 2803

2803

語音編解碼器技術的發展一定程度上處于靜止狀態,但音頻編解碼器技術一直在向前演進。音頻編解碼器朝更多的環繞聲通道發展就是一個趨勢。

2012-02-03 16:17:11 4774

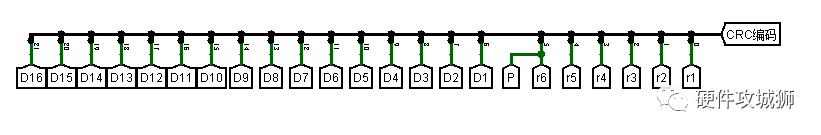

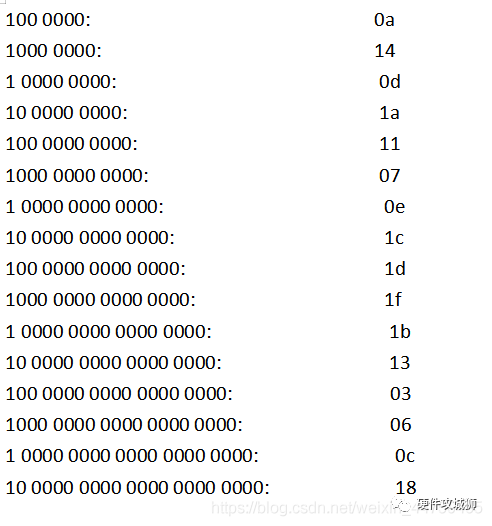

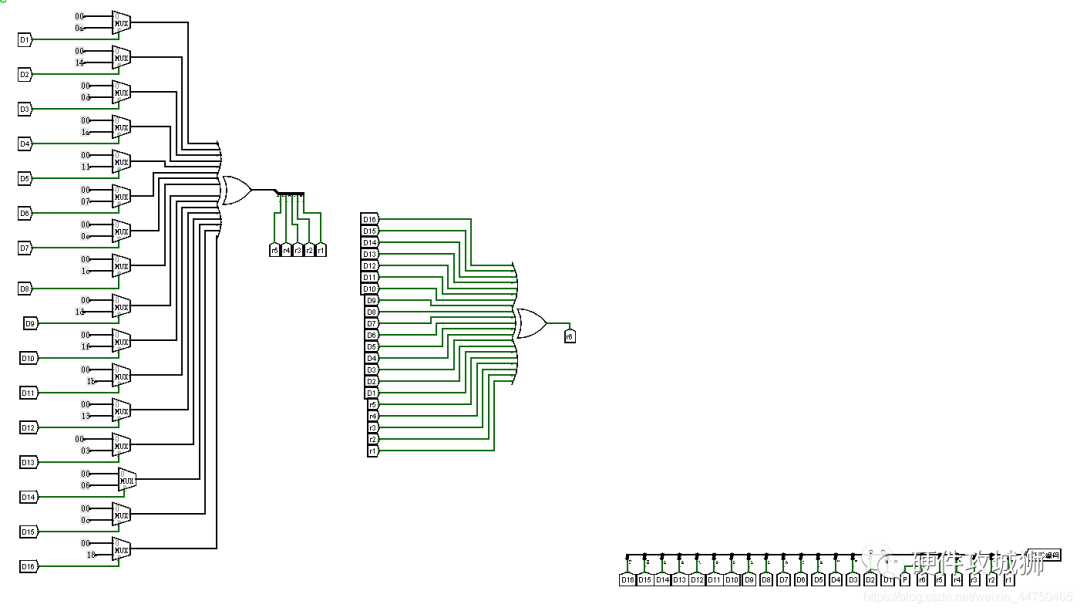

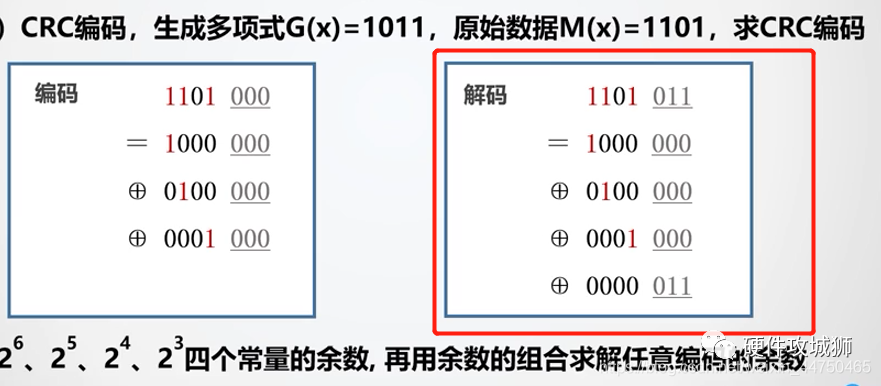

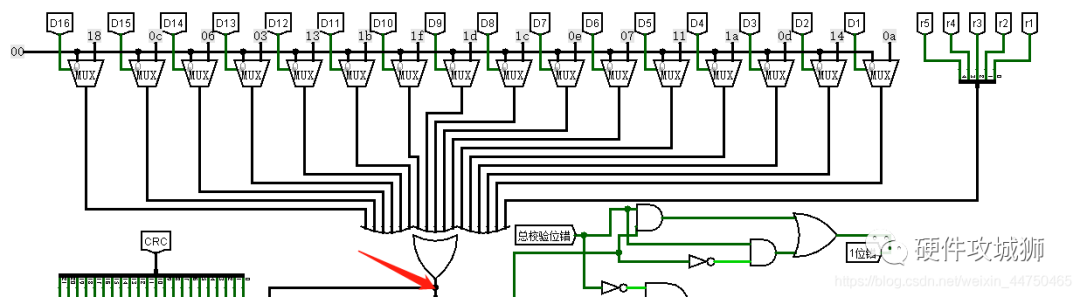

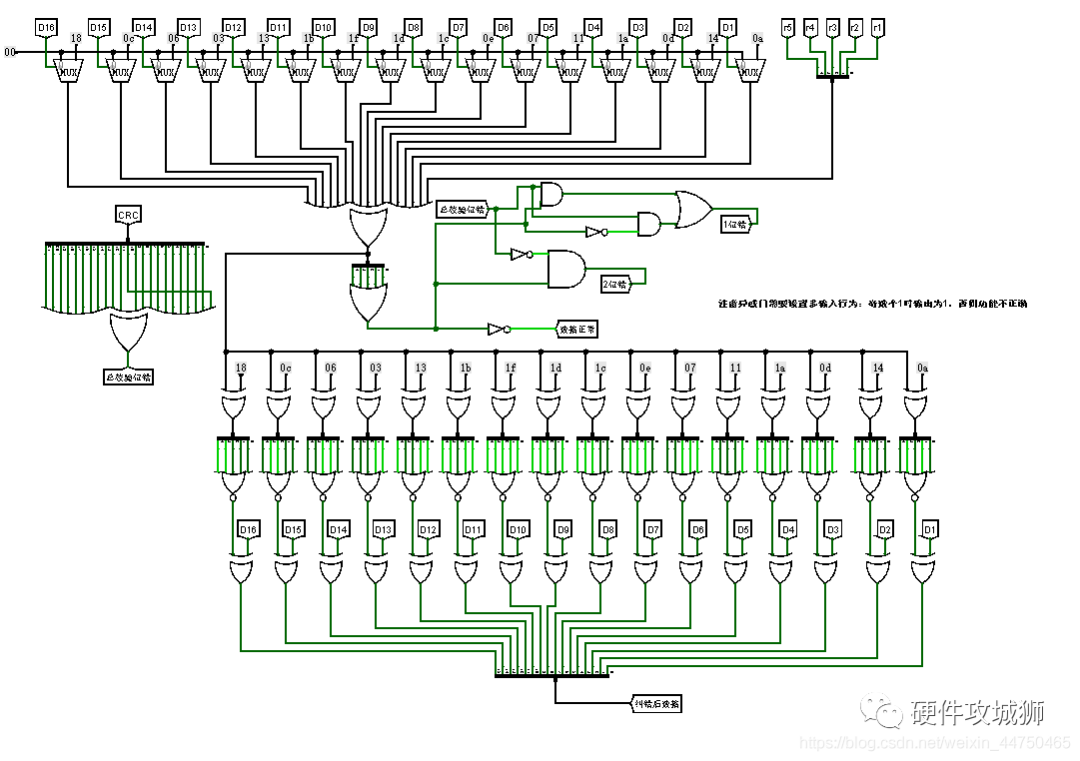

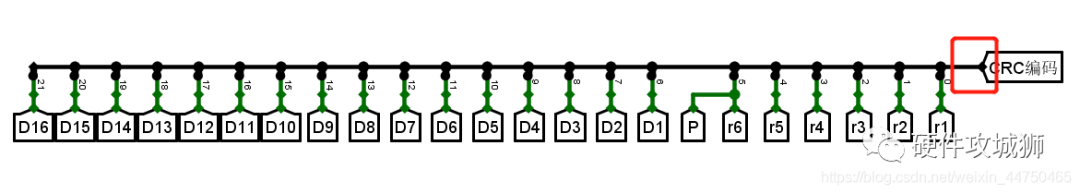

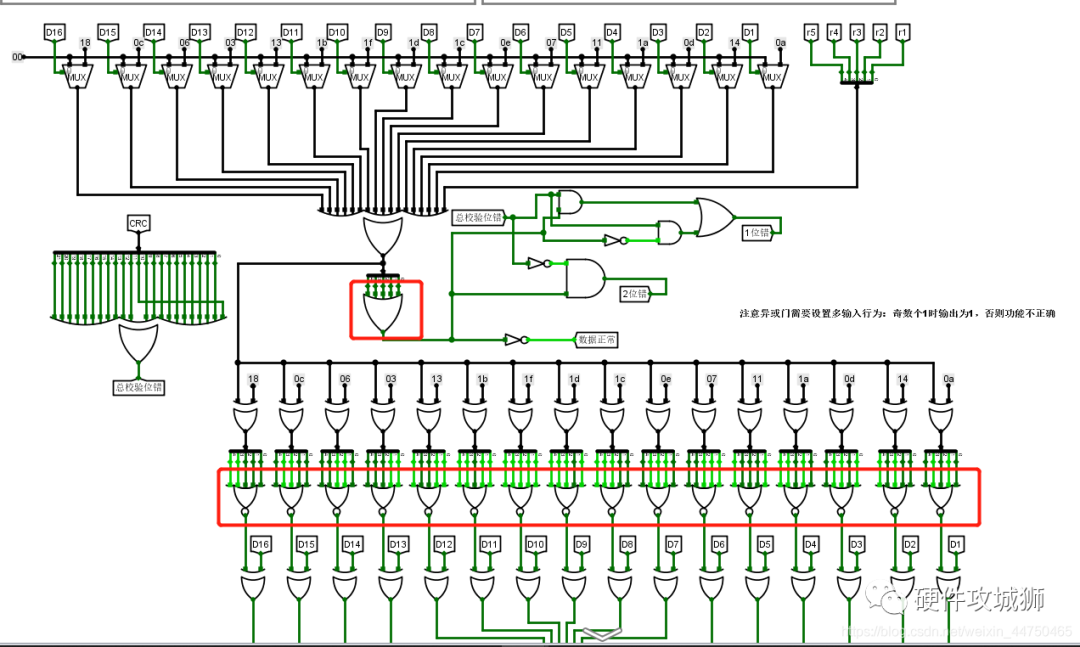

4774 10G以太網系統中的并行CRC編解碼器的設計

2012-08-10 17:59:00

53小波的EZW壓縮編解碼FPGA實現,有了解的麻煩指點下,謝謝!

2014-06-22 11:25:36

16位音頻編解碼芯片[ES689]開發手冊

2012-08-20 13:22:31

16B 20B編解碼 Xilinx提供1

2012-08-10 18:01:22

鎖定,12位數據一起輸入到電腦的并行口(打印口)。經電腦翻譯用中文顯示發生報警的地址和報警的類型,并同時發出“嘟嘟”的報警聲,以引起注意,如圖4和圖5所示。圖4 接收解調和解碼模塊原理方框圖圖5 解碼

2008-09-02 10:55:21

編解碼器是用于對數字媒體文件(如歌曲或視頻)進行壓縮或解壓縮的軟件。Windows Media Player 和其他程序使用編解碼器來播放并創建數字媒體文件。

2020-04-06 09:00:42

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:57:27

AD7655并行模式工作,為何我采集的數據無論何時候16bit中都是第3~0位一直為F,變化的是第4~11位,在原理圖設計中我將byteswap引腳接地了,在sigtap中采集的波形圖如下,急求指點呀

2023-12-22 07:22:36

AKD4641EN-A,AK4641評估板,16位立體聲編解碼器,內置麥克風放大器和16位單聲道CODEC,用于藍牙接口。除環回模式(A / D至D / A)外,AKD4641還可單獨評估A / D

2020-06-18 08:44:41

Android硬編解碼主要用MediaCodec實現。以下是Android官方的使用說明:我就用MediaCodec做一個demo,實現硬編解碼攝像的的preview數據。demo界面如圖:程序界面

2022-04-11 14:39:36

我正在使用 I91260 語音芯片,我在SDS 看到有不同的編解碼格式(AudioPlayback MD4 NuOneEx ...) 我想知道這些格式有什么區別,我如何更好的選擇使用那個格式?

我的另一個問題是,在那個文檔 展示了關于 音頻編解碼的 介紹,比如 采樣率,通道選擇 等描述

2023-06-13 06:16:22

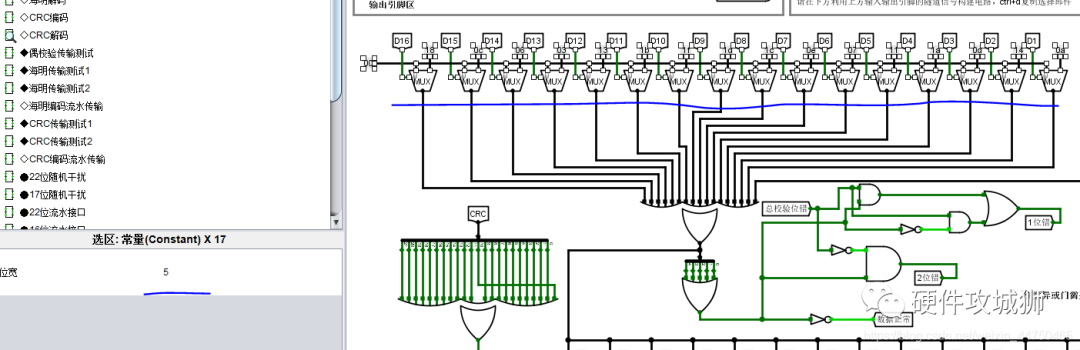

Verilog并行CRC校驗

2012-08-20 21:52:15

)====================================================================版權歸作者所有,未經允許,請勿轉載。====================================================================一、opus編解碼簡介Opus是一個完全開放,免版稅,高度通用的音頻編解碼器。在互聯網上Opus是交互式語音和音樂傳輸,也

2021-12-24 06:56:37

小弟最近在做2013年國賽題目紅外通信裝置,其實核心就是對音頻信號進行PCM編解碼,其中我們用到了MC14LC5480這款PCM編解碼芯片,其中有幾個疑問1.看全英文的文檔介紹說有四種工作模式,但我

2016-03-15 11:30:37

下面的代碼是為8位CRC編寫的。有人建議如何轉換下面的代碼為16位CRCCode修改 以上來自于百度翻譯 以下為原文 The below code written for 8 bit CRC

2018-10-16 11:00:35

初識紅外編解碼

2021-08-16 06:35:47

數字通信過程中,基帶信道對傳輸信號的碼型有嚴格的限制。針對數字光纖通信傳輸信號碼型的要求,介紹了CMI碼的編解碼原理,提出了一種基于可編程邏輯器件EPM240T100C5實現CMI編解碼的方法,給出

2010-05-06 09:06:05

語音通信、聯網音頻甚至高性能音頻處理應用。較之 ARM 等通用處理器,此設計還通過在 DSP 上實現 Opus 編解碼器來提升性能。根據通用處理器上所運行代碼的優化級別,通過在 C66x TI DSP

2018-08-20 06:02:22

ADPCM算法及其編解碼器原理是什么?如何去設計ADPCM語音編解碼電路?

2021-05-06 06:37:15

WM873l是什么?WM8731芯片接口時序有哪幾種?如何對音頻編解碼芯片WM8731進行接口電路的設計?

2021-06-07 06:20:50

怎樣運用CPLD去控制曼徹斯特編解碼器?

2021-05-07 07:09:08

)PARALLEL-TO-SERIAL位模式與帖子頭部的圖片相同,我必須發送到編解碼器,串行,首先是MSB,16位數據,其余32-16將是16.所以我必須發送一個LRframe總共32位,因為32是同步串行輸入的時鐘脈沖。并行到

2019-06-11 09:48:00

CODE WORD, 支持CD(載波偵測),FEC前項糾錯,16位CRC校驗,data whitening ,曼徹斯特編解碼,3/4線SPI接口, 獨立的64字節RX 和TX FIFO.專業無線總匯

2011-04-11 10:20:37

沒有遇到過。我所知道的每個編解碼器都使用一個 256 位幀和 8 個 32 位槽,盡管它們通常每個樣本使用少于 32 位。有誰知道可以使用 16 位插槽的 8 通道輸出音頻編解碼器或 DAC?

2023-04-12 06:12:20

目前在做視頻編解碼,功能只是實現對640*480 25fps做H.264編碼和解碼,請教專家:1、基于這種應用DM368是否就可以了?2、DM368能否支持編碼和解碼的并行執行?即兩路同時輸入,一路

2019-02-20 09:16:35

音視頻編解碼標準簡介

2021-01-21 06:53:21

本人完全未接觸過音頻編解碼,最近因為需要了解了一下音頻編解碼的芯片,其中均集成了ADC和DAC,想請教一下,音頻編解碼與ADC和DAC是什么關系?(我理解是:ADC是編碼的基礎,DAC是解碼的基礎,解碼其實就是將數字量經DAC后生成了模擬量在經運放等恢復音頻,不知對否?)

2014-08-07 15:22:30

;amp;amp;D),威聲(VLSI)針對新技術的集成電路開發了近20年,其產品涵蓋了許多低功率產品應用程序。公司的研究重點是低功耗應用的數模混合信號與射頻信號。威聲(VLSI)專注開發的音頻編解碼

2012-11-06 09:44:06

頂層為原理圖的能顯示16進制減法計數器設計1.用VHDL設計一個二選一電路,并用ModelSim Simulator 仿真驗證。 要求該二選一電路能實現16進制數的兩位數據串行輸出(或稱動態輸出

2009-10-11 08:51:38

RS編解碼原理是什么如何實現RS編解碼器?

2021-04-29 06:11:40

TLC320AD535編解碼器電路圖,原理圖

2007-06-05 17:49:23 40

40 Jupiter 1.0是一款符合中國國情的原理圖設計軟件,聚焦核心功能,覆蓋原理圖設計全流程,功能設計更智能化,界面操作更人性化,讓硬件工程師使用得更愉悅、順暢。為昕科技旨在通過新技術提高硬件工程師

2022-04-11 13:47:20

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:54:41 25

25 AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-15 15:13:14 27

27 HDB3碼是基帶傳輸系統中經常采用的傳輸碼型。本文闡述了HDB3碼編解碼電路的基本原理,在MAX+PLUSⅡ軟件平臺上,給出了利用復雜可編程邏輯器件設計的HDB3碼編解碼電路,并進行了編譯和

2010-02-24 15:59:48 51

51 基于AMI/HDB3編解碼原理,設計了一種用CD22103集成芯片實~AMI/HDB3編解碼的硬件電路.詳細分析了編解碼的實現過程、單雙極性變換及位同步,最后給出實驗結果并分析了編解碼時延

2010-04-13 08:56:28 145

145 主題內容與適用范圍

本標準規定了PCM編解碼系統信號的格式和其他有關條件。

本標準適用于錄像系統錄放音頻信號用的PCM編解碼器。

系統說明

PCM編解碼

2010-08-31 18:26:25 35

35 采用多路復用流水線的思想,設計基于FPGA仿真測試的RS編解碼的改進IBM算法,使用Verilog硬件編程語言實現,進一步提高RS編解碼器的運行速度及糾錯能力,擴大應用范圍。系統設計

2010-12-22 17:02:40 25

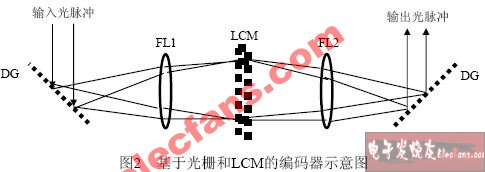

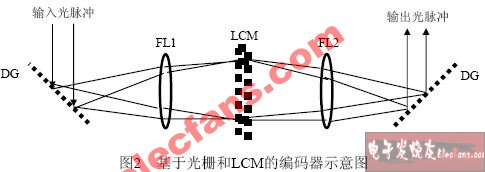

25 頻域相位編解碼OCDMA系統

基于頻域相位編解碼OCDMA通信系統如圖1所示[3]。頻域相位編解碼OCDMA通信系統,無論是在實驗還是理論方面,相對

2009-02-28 11:32:43 1009

1009

什么是音頻編解碼器?

編解碼器(編碼器/解碼器)轉換成模擬信號的數字碼流,另一個相同的編解碼器轉換為數字流回到成模擬信

2009-05-03 23:48:59 3870

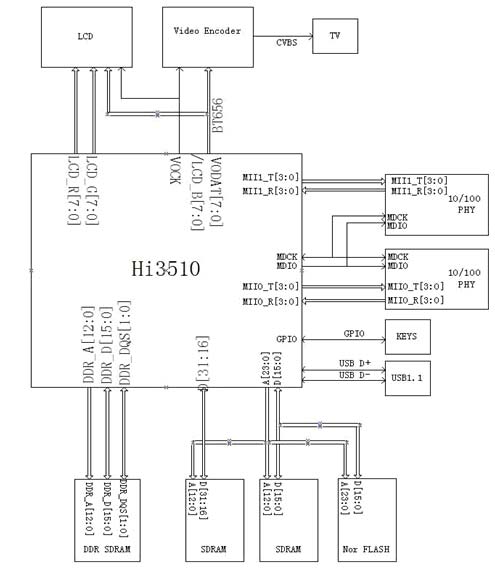

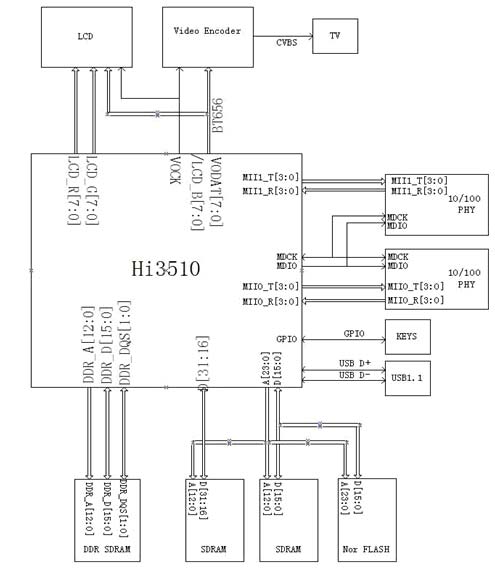

3870 i3510編解碼的應用 Hi3510自帶的Linux操作系統(同時支持Vxworks、WinCE等開放式操作系統)和ARM處理器,使得芯片除了編解碼功能外,還可以實現許多豐富的應用功能開發。如圖2

2009-05-13 11:13:28 1360

1360

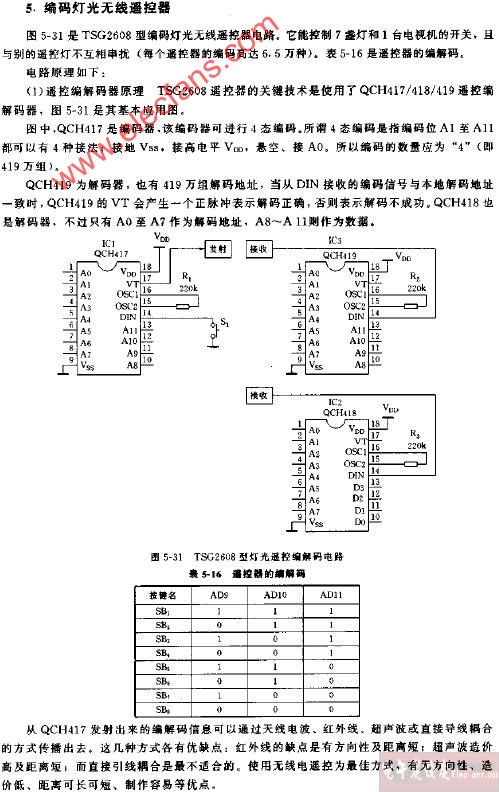

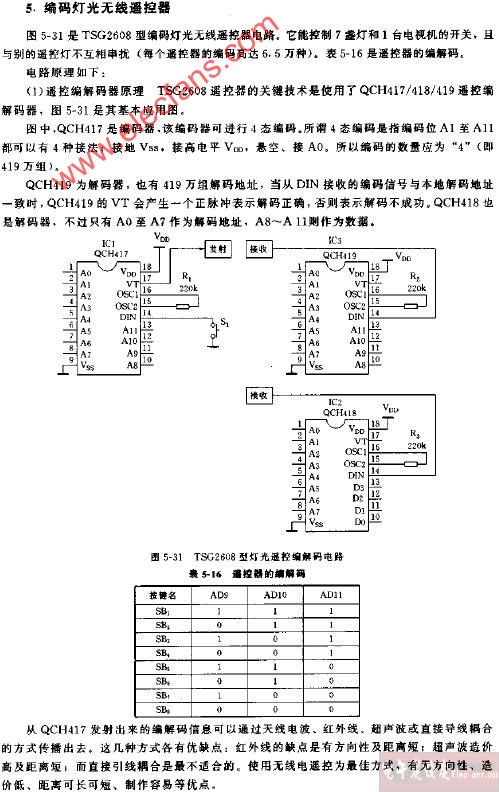

TSG2608型燈光遙控編解碼電路圖

2009-06-13 16:58:01 838

838

討論如何使用CPLD實現單片機與曼徹斯特編解碼器的接口。設計時采用自頂向下的流程,具體電路可靈活地添加到各種曼徹斯特碼接口系統中。

關鍵詞 曼徹斯特編解碼器 T2模

2009-06-16 07:40:18 1251

1251

摘要:介紹了HDB3編解碼的原理和方法,給出了用CPLD(Complex Programmable Logic Device)實現E1信號HDB3編解碼的方法,同時給出了它的實現原理圖,最后給出了XI

2009-06-20 13:44:03 1049

1049

摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統設計方案。與現有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現8B/lOB編解碼的模塊方

2011-05-26 11:08:20 3364

3364

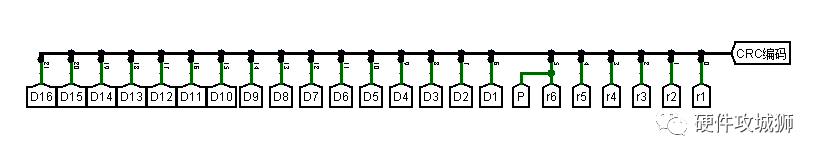

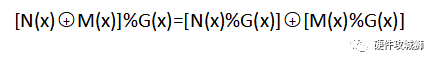

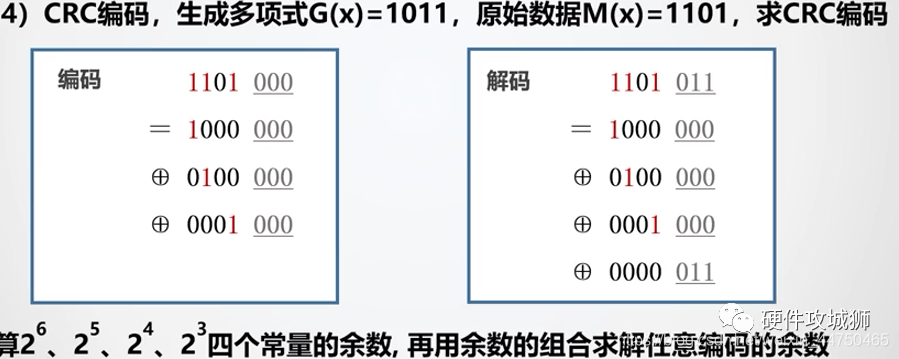

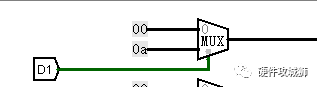

循環冗余碼校驗 CRC (Cyclic Redundancy Check) 廣泛用于通訊領域和數據存儲的數據檢錯。基于FPGA在通訊領域和數據存儲的應用越來越廣泛,CRC的編碼解碼模塊已經是FPGA上的常用模塊了。采

2011-08-15 11:19:57 40

40 結合RS碼的基本特性,講述了RS碼的編解碼過程,給出了經過實際驗證的RS編解碼在超短波跳頻電臺開發中的軟件應用實例。

2012-02-13 10:07:26 26

26 在介紹CRC校驗原理和傳統CRC32串行比特算法的基礎上,由串行比特型算法推導出一種CRC32并行算法。并結合SATAⅡ協議的要求,完成了SATAⅡ主控制器設計中CRC生成與校驗模塊的設計。最后

2012-11-07 16:19:37 54

54 E文JPEG編解碼介紹,很好的資料,快來學習吧

2016-02-18 14:14:31 0

0 RS編解碼的FPGA實現-說明RS編解碼的FPGA實現-說明。

2016-05-04 15:59:44 21

21 六路編解碼電路原理圖都是值得參考的設計。

2016-05-11 17:00:47 33

33 四路編解碼電路原理圖都是值得參考的設計。

2016-05-11 17:33:19 27

27 循環碼編解碼電路的EDA設計。

2016-05-20 11:47:38 11

11 基于FPGA的JPEG實時圖像編解碼系統

2016-08-29 16:05:01 15

15 通信接口——編解碼

2017-09-04 09:39:45 9

9 基于Cortex_A8多媒體編解碼優化

2017-09-25 13:20:56 7

7 串行編碼原理得到8 位并行數據的CRC 校驗矩陣,之后對矩陣進行迭代簡化,得到32 位并行數據的參數矩陣,此參數矩陣作為該CRC 算法的核心實現了對數據進行預處理。最后對該算法進行了硬件實現,仿真及綜合結果表明,該算法可在單周期內完成對128 位并行數據的CRC 編碼和解碼校驗,

2017-10-30 16:39:25 3

3 。CRC的實現方式分為串行方式和并行方式,由于并行方式一個時鐘周期內可以處理8個bit,與千兆以太網的C;MIl接口協議相符合,故千兆以太網的CRC校驗碼的生成和校驗中常使用并行算法實現。本文研究了CRC校驗碼的串行實現算法和并行實現算法,并且

2017-11-13 14:20:47 12

12 基于串行異步收發器(UART)的通信中經常用到循環冗余校驗(CRC),常見的CRC校驗電路多為串行校驗,校驗所需時鐘周期較多,基于查找表或輸入矩陣轉換的并行算法,需要存儲余數表,占用大量的硬件資源

2017-11-18 11:24:54 1789

1789

對L9320編解碼器的工作原理和使用方法 進行了分析,給出了L9320在便攜式語音系統中的典型應用電路.

2019-12-20 17:27:09 24

24 本文檔的主要內容詳細介紹的是PCM語音編解碼的PCB原理圖免費下載。

2020-10-14 14:52:00 20

20 的LFSR 電路為基礎,推導出產生32位并行數據的CRC - 16編碼表達式,用EDA 工具設計出CRC - 16編碼模塊,并對其進行綜合仿真,驗證其可行性。

2021-03-10 15:50:00 14

14 CRC校驗的實現基于串行位移寄存器,如果要處理并行數據,需要對電路進行改進。本文介紹了一種并行CRC電路HDL代碼的快速生成鐘算法,只需要帶入不同的參數,可自動生成不同長度以及并行度的并行CRC電路的HDL代碼。

2021-03-28 09:29:50 15

15 文章介紹了用于 USB 總線數據傳輸的CRC 校驗的原理和算法,并且采用并行電路實現 USB2.0 中的 CRC產生和CRC校驗,與傳統的串行電路實現相比,并行電路實現方法雖然在芯片面積上大于串行電路實現, 但由于降低了時鐘頻率,電路更容易綜合實現,并且大大降低了功耗,有利于低功耗電路設計。

2021-03-28 09:32:27 11

11 用軟件實現 CRC 校驗碼計算很難滿足高速數據通信的要求 ,基于硬件的實現方法中 ,有串行經典算法 LFSR 電路 以及由軟件算法推導出來的其它各種并行計算方法。以經典的LFSR 電路為基礎 ,研究

2021-03-28 09:34:24 30

30 、并行總線共用和丌AG菊花鏈技術。通過國內外技術對比和網絡性能測試,DSP實現語音編解碼技術最終在多個項目中得以廣泛應用,為今后語音編解碼技術的發展提供了借鑒經驗。

2021-04-11 11:39:38 17

17 AD1846:低成本并行端口16位SoundPort立體聲編解碼器過時數據表

2021-05-14 15:12:53 6

6 PCM語音編解碼及原理圖下載

2021-07-14 09:56:33 12

12 NANDFLASH快速BCH編解碼算法及便件實現(嵌入式開發自學網)-NANDFLASH快速BCH編解碼算法及便件實現? ? ? ??

2021-07-30 14:14:40 5

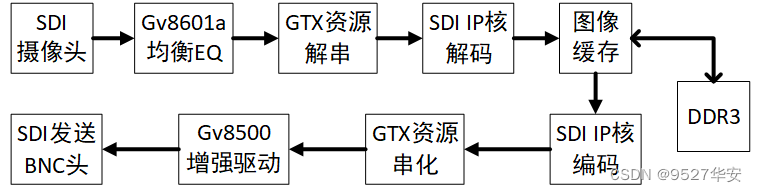

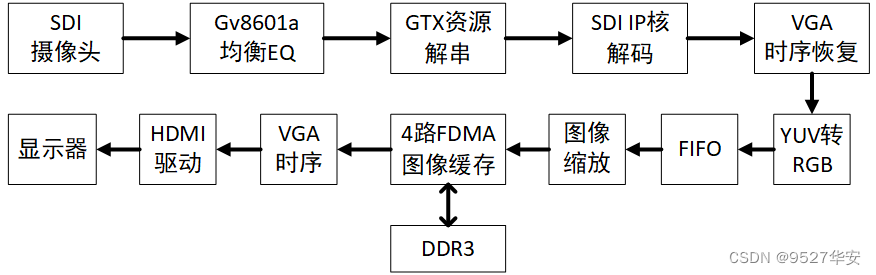

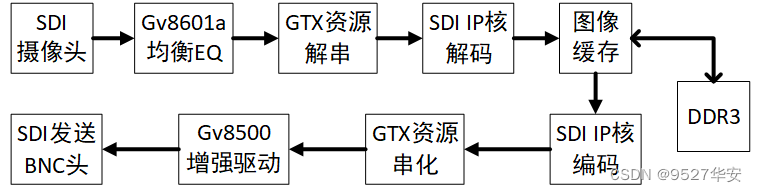

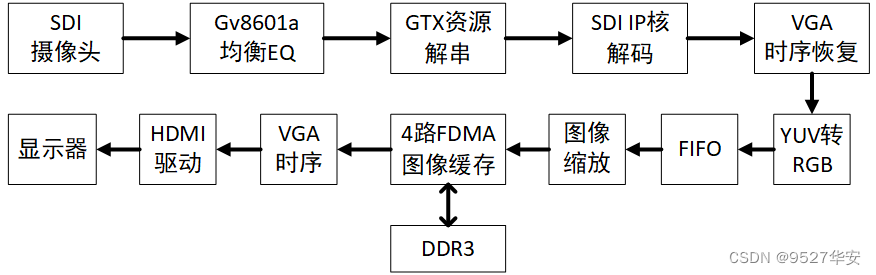

5 一是使用專用編解碼芯片,比如典型的接收器GS2971,發送器GS2972,優點是簡單,比如GS2971接收器直接將SDI解碼為并行的YCRCB,

2023-06-14 14:48:28 679

679

大家好,今天我分享的是走向實用的AI圖像編解碼。本次將著重從 “走向”兩個字出發,闡述AI編解碼研發的關鍵內容和進展。

2023-06-15 09:19:10 465

465

一是使用專用編解碼芯片,比如典型的接收器GS2971,發送器GS2972,優點是簡單,比如GS2971接收器直接將SDI解碼為并行的YCRCB,GS2972發送器直接將并行的YCRCB編碼為SDI視頻,缺點是成本較高,可以百度一下GS2971和GS2972的價格

2023-06-19 16:55:52 809

809

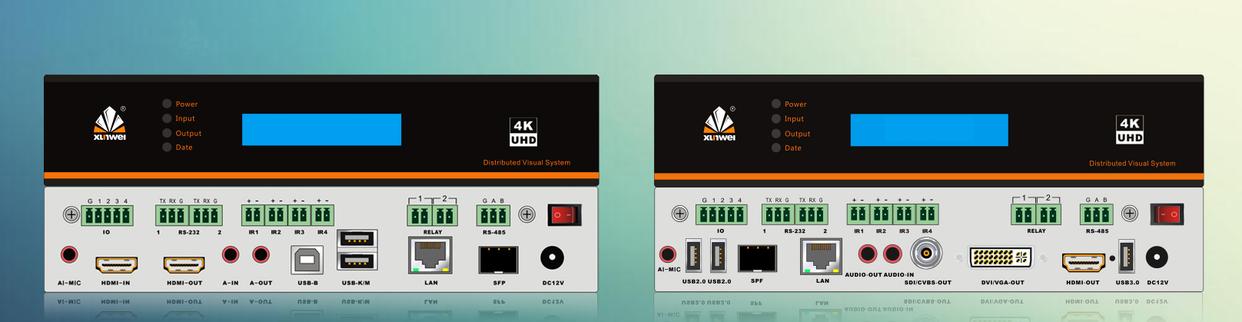

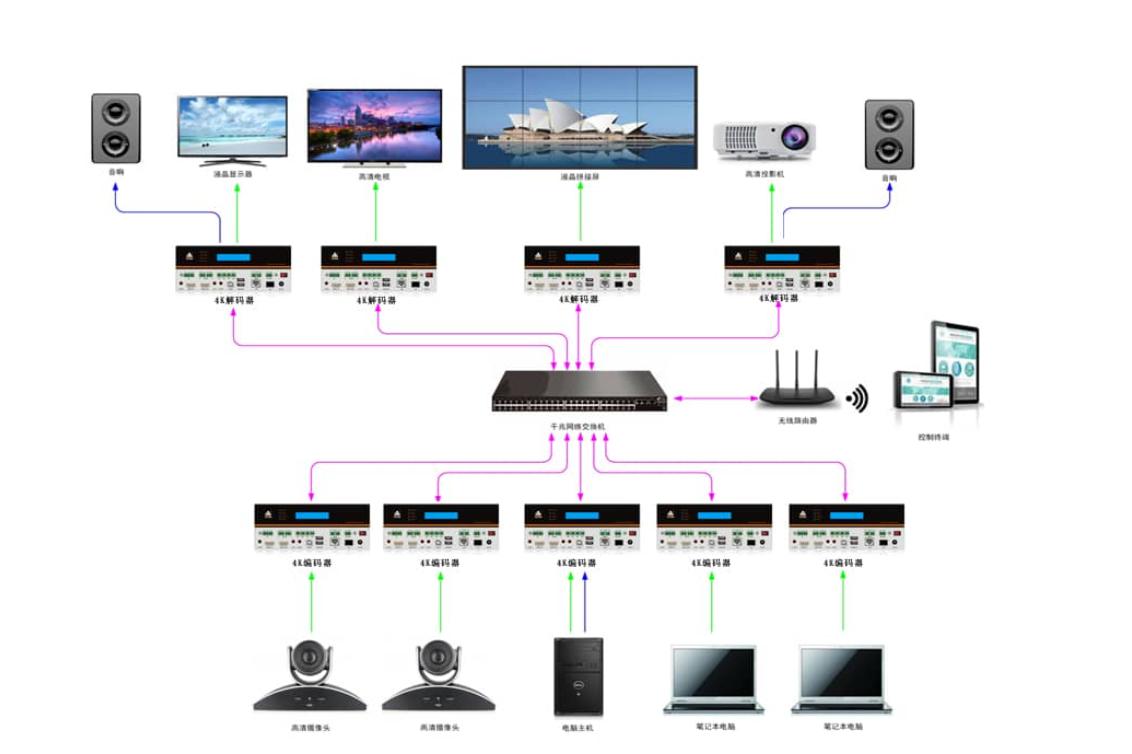

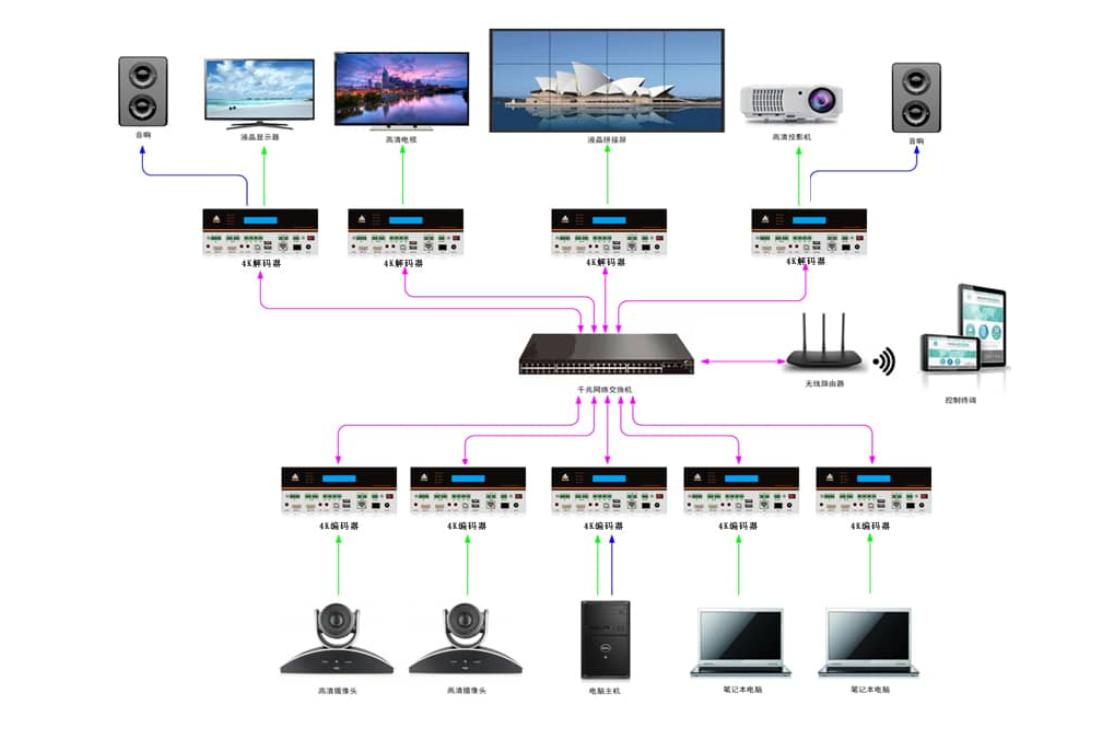

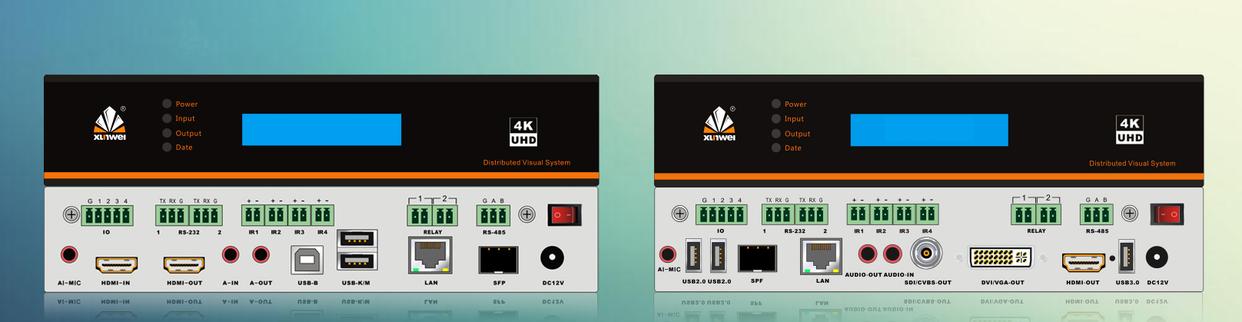

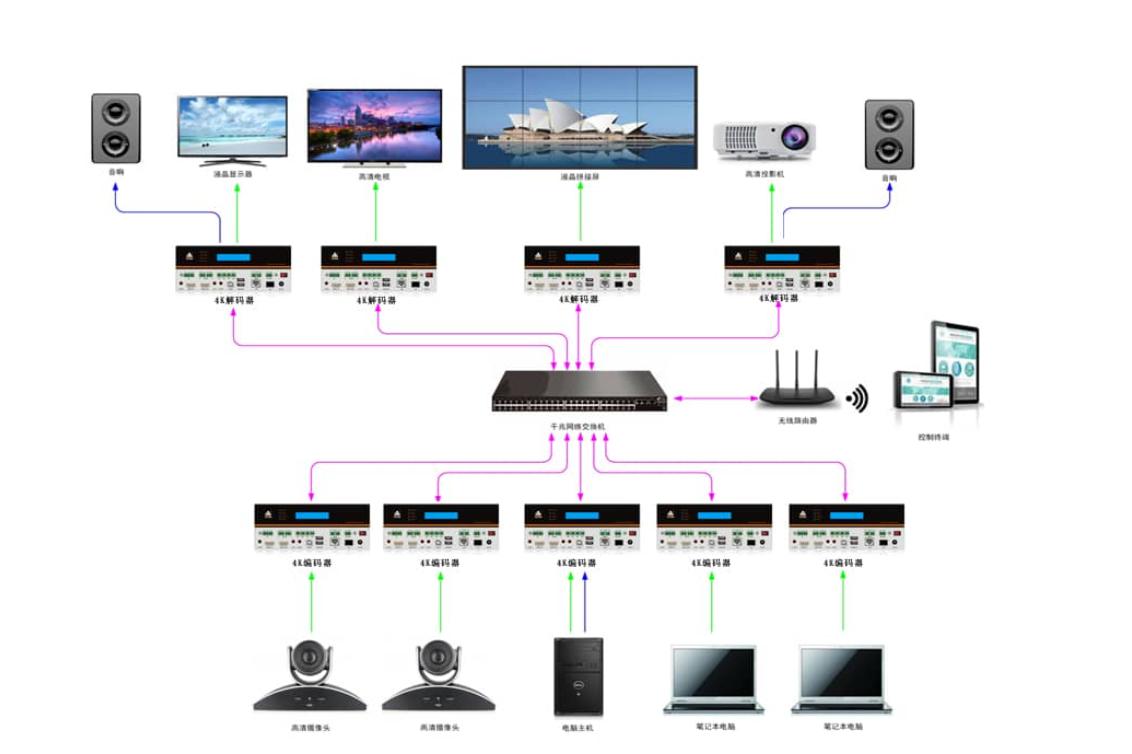

編解碼一體機是一種集視頻編解碼、音頻編碼以及數據傳輸功能于一體的多媒體設備。這種設備通常基于云計算技術和先進的編解碼算法,能夠高效地處理視頻流,提供低延遲、高穩定性的音視頻傳輸服務。此外,編解碼

2024-01-31 14:19:36 168

168

編解碼一體機作為音頻處理的新選擇,以其高效、靈活的解決方案,引領著音頻處理技術的新篇章。這種設備集成了音頻編解碼和數據傳輸功能,將復雜的音頻處理流程簡化在一臺設備中,提高了音頻處理的效率和靈活性

2024-01-31 14:46:16 134

134

編解碼一體機是一種集視頻編解碼、音頻編碼以及數據傳輸功能于一體的多媒體設備。它基于云計算技術,具有高效、實時的視頻處理能力,廣泛應用于安防監控、視頻會議、教育錄播等領域。 首先,編解碼一體機采用

2024-01-31 14:48:04 148

148

編解碼一體機相對于傳統的編解碼設備具有多個優勢。以下是編解碼一體機的幾個主要優勢: 高效實時的視頻處理能力:編解碼一體機采用先進的編解碼算法和云計算技術,能夠實現高效、實時的視頻處理,滿足各種應用場

2024-01-31 14:56:04 291

291

編解碼一體機是一種集視頻編解碼、音頻編碼以及數據傳輸功能于一體的多媒體設備,廣泛應用于各個領域。以下是編解碼一體機的幾個主要應用場景: 來百度APP暢享高清圖片 視頻會議:編解碼一體機可以為視頻會議

2024-01-31 14:57:21 146

146

電子發燒友App

電子發燒友App

評論