模擬電路是指用來(lái)對(duì)模擬信號(hào)進(jìn)行傳輸、變換、處理、放大、測(cè)量和顯示等工作的電路。模擬電路是電子電路的基礎(chǔ),它主要包括放大電路、信號(hào)運(yùn)算和處理電路、振蕩電路、調(diào)制和解調(diào)電路及電源等。

模擬電路設(shè)計(jì)的基本流程

1.系統(tǒng)定義

系統(tǒng)定義是模擬電路設(shè)計(jì)的基本前提。根據(jù)設(shè)計(jì)要求,模擬電路設(shè)計(jì)工程師需要對(duì)電路系統(tǒng)及子系統(tǒng)做出相應(yīng)的功能定義,并確定面積、功耗等相關(guān)性能的參數(shù)范圍。

電路結(jié)構(gòu)的選擇是電路設(shè)計(jì)的重要環(huán)節(jié)。模擬電路設(shè)計(jì)工程師需要根據(jù)模擬電路需要實(shí)現(xiàn)的功能要求、設(shè)計(jì)規(guī)范及相應(yīng)的參數(shù)指標(biāo)選擇合適的電路結(jié)構(gòu),并在此基礎(chǔ)上確定元器件的組合方式等。

針對(duì)模擬電子電路的設(shè)計(jì),目前暫時(shí)沒有可以利用的比較成熟的設(shè)計(jì)軟件,因此,只能是有工程師根據(jù)自己的經(jīng)驗(yàn)手工完成。這在一定程度上增加了模擬電路設(shè)計(jì)的難度,限制了模擬電路的發(fā)展速度。

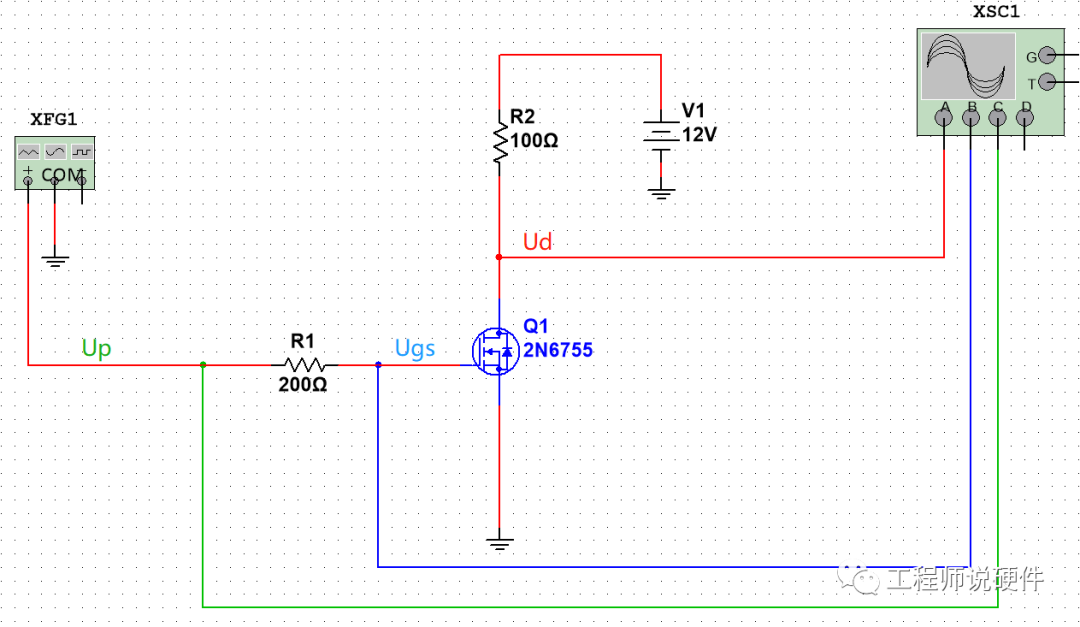

3、電路仿真

電路仿真是模擬電路的設(shè)計(jì)過(guò)程中必不可少的一個(gè)環(huán)節(jié),是模擬工程師判斷模擬電路是否可以達(dá)到設(shè)計(jì)要求的一個(gè)重要依據(jù)。

工程師根據(jù)仿真結(jié)果,不斷對(duì)電路進(jìn)行修改和調(diào)整,直到模擬電路的仿真結(jié)果可以達(dá)到設(shè)定的指標(biāo)及相應(yīng)的功能要求。常用方法主要有參數(shù)掃描法,直流和交流分析法、蒙特卡羅分析等。

4、版圖實(shí)現(xiàn)

版圖將電路設(shè)計(jì)轉(zhuǎn)化生產(chǎn)的重要橋梁。在由前面的設(shè)計(jì)及仿真結(jié)果確定了模擬電路的結(jié)構(gòu)及相關(guān)參數(shù)后,設(shè)計(jì)工程師對(duì)設(shè)計(jì)的模擬電路進(jìn)行物理幾何性的描述,將其轉(zhuǎn)換成圖形格式,以便于模擬電路后續(xù)的加工與制作。

5、物理驗(yàn)證

在物理驗(yàn)證階段,需要對(duì)設(shè)計(jì)的模擬電路進(jìn)行設(shè)計(jì)規(guī)則檢查(DRC)。設(shè)計(jì)規(guī)則檢查是在給定的設(shè)計(jì)規(guī)則的基礎(chǔ)上對(duì)其最小線寬、孔尺寸、最小圖形間距等限制工藝進(jìn)行檢查,衡量版圖工藝實(shí)現(xiàn)上的可行性。此外,還要對(duì)版圖與電路圖的一致性進(jìn)行檢查(LVS)。可以利用LVS工具提取版圖的參數(shù),將得到的電路圖與原電路設(shè)計(jì)圖進(jìn)行比較,保證版圖與原電路設(shè)計(jì)的一致性。

6、寄生參數(shù)提取后仿真

在版圖之前進(jìn)行的電路設(shè)計(jì)的仿真稱之為“前仿真”,“前仿真”都是比較理想的仿真,沒有考慮到連線的電阻、電容等寄生參數(shù)。將寄生參數(shù)加入版圖后進(jìn)行的電路仿真稱之為“后仿真”,只有當(dāng)后仿真的仿真結(jié)果達(dá)到設(shè)計(jì)指標(biāo)及系統(tǒng)功能要求,電路的設(shè)計(jì)工作才算完成。

寄生參數(shù)對(duì)模擬電路的影響較大,前仿真的仿真結(jié)果滿足的情況下,后仿真結(jié)果卻無(wú)法滿足要求。因此,設(shè)計(jì)工程師需要根據(jù)后仿真結(jié)果不斷進(jìn)行晶體管參數(shù)的修改,有時(shí)甚至要進(jìn)行電路結(jié)構(gòu)的調(diào)整,直至后仿真結(jié)果達(dá)到系統(tǒng)設(shè)計(jì)要求。

目前,模擬電路設(shè)計(jì)難度高且比較復(fù)雜,使用的EDA工具的功能和系統(tǒng)配套性又相對(duì)落后,且在設(shè)計(jì)過(guò)程中需要進(jìn)行頻繁的人工干預(yù),對(duì)寄生參數(shù)等比較敏感等,這些都在一定程度上限制了模擬電路的發(fā)展,導(dǎo)致模擬電路發(fā)展速度相對(duì)緩慢。

模擬電路設(shè)計(jì)中應(yīng)該注意的細(xì)節(jié)

(1)為了獲得具有良好穩(wěn)定性的反饋電路,通常要求在反饋環(huán)外面使用一個(gè)小電阻或扼流圈給容性負(fù)載提供一個(gè)緩沖。

(2)積分反饋電路通常需要一個(gè)小電阻(約560歐)與每個(gè)大于10pF的積分電容串聯(lián)。

(3)在反饋環(huán)外不要使用主動(dòng)電路進(jìn)行濾波或控制EMC 的RF帶寬,而只能使用被動(dòng)元件(最好為RC電路)。僅僅在運(yùn)放的開環(huán)增益比閉環(huán)增益大的頻率下,積分反饋方法才有效。在更高的頻率下,積分電路不能控制頻率響應(yīng)。

(4)為了獲得一個(gè)穩(wěn)定的線性電路,所有連接必須使用被動(dòng)濾波器或其他抑制方法(如光電隔離)進(jìn)行保護(hù)。

(5)使用EMC濾波器,并且與IC相關(guān)的濾波器都應(yīng)該和本地的0V參考平面連接。

(6)在外部電纜的連接處應(yīng)該放置輸入輸出濾波器,任何在沒有屏蔽系統(tǒng)內(nèi)部的導(dǎo)線連接處都需要濾波,因?yàn)榇嬖?a target="_blank">天線效應(yīng)。另外,在具有數(shù)字信號(hào)處理或開關(guān)模式的變換器的屏蔽系統(tǒng)內(nèi)部的導(dǎo)線連接處也需要濾波。

(7)在模擬IC的電源和地參考引腳需要高質(zhì)量的RF去耦,這一點(diǎn)與數(shù)字IC一樣。但是模擬IC通常需要低頻的電源去耦,因?yàn)槟M元件的電源噪聲抑制比(PSRR)在高于1KHz后增加很少。在每個(gè)運(yùn)放、比較器和數(shù)據(jù)轉(zhuǎn)換器的模擬電源走線上都應(yīng)該使用RC 或LC濾波。電源濾波器的拐角頻率應(yīng)該對(duì)器件的PSRR拐角頻率和斜率進(jìn)行補(bǔ)償,從而在整個(gè)工作頻率范圍內(nèi)獲得所期望的PSRR 。

(8)對(duì)于高速模擬信號(hào),根據(jù)其連接長(zhǎng)度和通信的最高頻率,傳輸線技術(shù)是必需的。即使是低頻信號(hào),使用傳輸線技術(shù)也可以改善其抗干擾性,但是沒有正確匹配的傳輸線將會(huì)產(chǎn)生天線效應(yīng)。

(9)避免使用高阻抗的輸入或輸出,它們對(duì)于電場(chǎng)是非常敏感的。

(10)由于大部分的輻射是由共模電壓和電流產(chǎn)生的,并且因?yàn)榇蟛糠汁h(huán)境的電磁干擾都是共模問(wèn)題產(chǎn)生的,因此在模擬電路中使用平衡的發(fā)送和接收(差分模式)技術(shù)將具有很好的EMC效果,而且可以減少串?dāng)_。平衡電路(差分電路)驅(qū)動(dòng)不會(huì)使用0V參考系統(tǒng)作為返回電流回路,因此可以避免大的電流環(huán)路,從而減少RF 輻射。

(11)比較器必須具有滯后(正反饋),以防止因?yàn)樵肼暫透蓴_而產(chǎn)生的錯(cuò)誤的輸出變換,也可以防止在斷路點(diǎn)產(chǎn)生振蕩。不要使用比需要速度更快的比較器(將dV/dt保持在滿足要求的范圍內(nèi),盡可能低)。

(12)有些模擬IC本身對(duì)射頻場(chǎng)特別敏感,因此常常需要使用一個(gè)安裝在PCB上,并且與PCB的地平面相連接的小金屬屏蔽盒,對(duì)這樣的模擬元件進(jìn)行屏蔽。注意,要保證其散熱條。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論