?摘? 要?

金剛石因具有極高熱導率、5.5eV寬帶隙、極高擊穿電場、高固有載流子遷移率和低介電常數等優異性能,在高功率、高頻、高溫及低功率損耗電子器件領域中成為有力的競爭者。然而,研究人員對金剛石半導體摻雜技術進行了幾十年的探索和優化,卻仍然無法滿足當前電子器件的應用需求。最近,隨著H終端金剛石表面二維空穴氣的發現,研究重心逐漸轉向優化H終端金剛石的導電特性及制備場效應晶體管(FET)。綜述了H終端金剛石研究的發展歷程,從柵層材料選擇、表面終端處理、金剛石摻雜和FET結構優化出發,歸納了提升表面終端金剛石FET器件性能的方法,并對表面終端金剛石FET的發展前景進行了總結和展望。

研究背景?

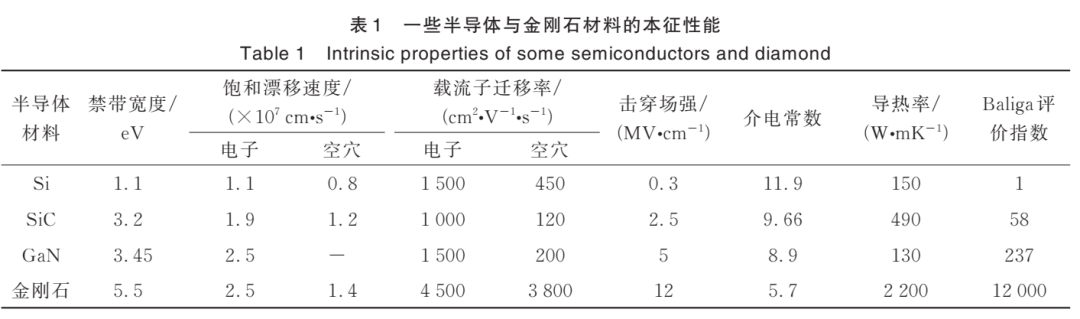

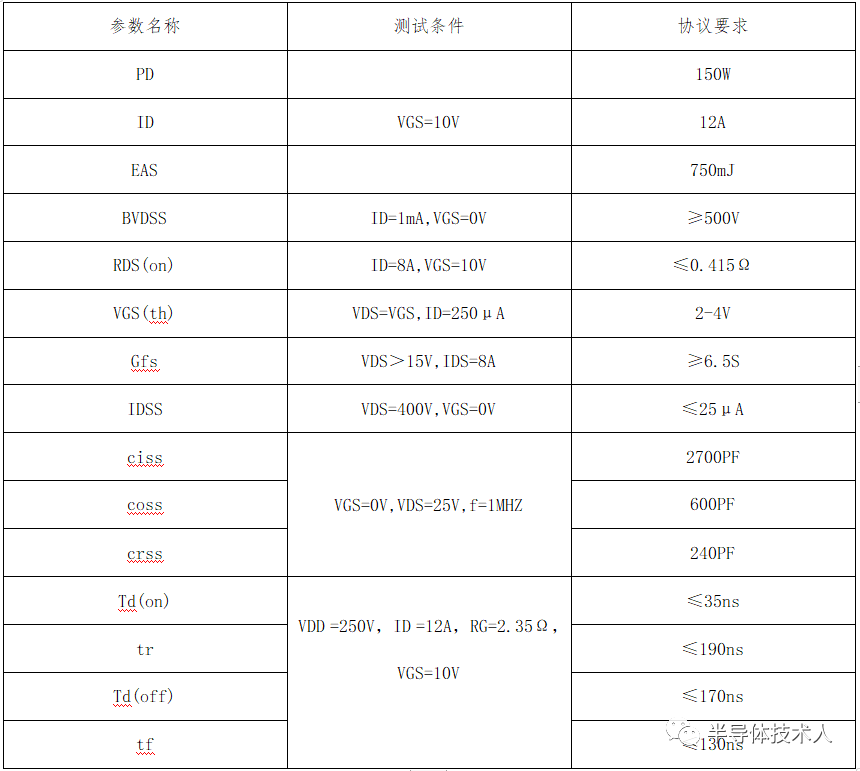

金剛石不僅具有包括最高的硬度、極高的熱導率、達5.5eV的寬帶隙、極高的擊穿電場和高固有載流子遷移率等多種卓越性質[1-2],同時還具有耐化學腐蝕、耐高溫、抗輻照能力強和表面穩定性高等優點,因此它在大功率器件、精密加工、熱管理、量子傳感、污水處理、生物傳感等領域得到了廣泛應用[3-5]。Si、第三代寬禁帶半導體SiC、GaN和金剛石材料[1-2]的基本參數和Baliga高頻評價指數[6]列于表1。由表1可知:金剛石在下一代高功率、高頻、高溫及低功率損耗電子器件中具有極為顯著的優勢,故其被業界譽為“終極半導體”。

? 幾十年來,研究人員一直試圖在各種電子設備應用中實現金剛石的理想性能。與大多數半導體材料一樣,金剛石材料必須進行雜質摻雜,以獲得穩定的高載流子濃度,但對金剛石進行n型摻雜的研究結果一直不太理想[7]。摻S的金剛石晶格畸變較多,降低了S的電活性[8],且低溫時會呈現p型導電[9];而N和Li摻雜后均為深雜質能級,通常為絕緣體[10-11];P摻雜會在金剛石中形成導帶底下0.58eV的雜質能級[12],且摻雜后的載流子遷移率很低。目前,雖然有一些研究表明[7,13-15],復雜摻雜物可以實現金剛石的n型摻雜,但都難以重復和應用。

在p型摻雜方面,使用B作為摻雜元素是最常見的方法。然而,B摻雜金剛石后的電離能約為0.36eV,這意味著即使在室溫下仍然難以電離,導致載流子濃度較低[16]。而高濃度B摻雜會導致空間電荷效應,從而降低載流子遷移率[17],影響導電性能,并降低金剛石的晶體質量。因此,盡管B摻雜金剛石的工藝相對成熟,且已在污水處理、傳感器等行業中得到了廣泛應用[18],但其在電子器件領域中的應用仍然受到限制。

近年研究發現,將H終端金剛石表面與氣體分子、氧化物、電荷等接觸,進行轉移摻雜后,可以形成良好導電特性的二維空穴氣(Two?Dimensional?Hole?Gas,2DHG),這提供了1種金剛石半導體應用的新途徑,同時避免了傳統摻雜帶來的嚴格限制[6]。H終端金剛石非常適合平面器件的制備,效應晶體管(Field?EffectTransistor,FET)是其應用最廣的領域。本文首先綜述了近年來H終端金剛石FET器件的研究和發展情況,包括H終端金剛石的發現歷程及二維空穴氣的產生機理。然后,從柵層材料的選擇、表面終端處理、金剛石摻雜和FET結構優化等方面入手,總結了目前研究中對H終端金剛石的優化方向和進展。最后,展望了表面終端金剛石FET器件未來的發展前景。

1 H終端FET的歷史發展?

1.1 氣體分子

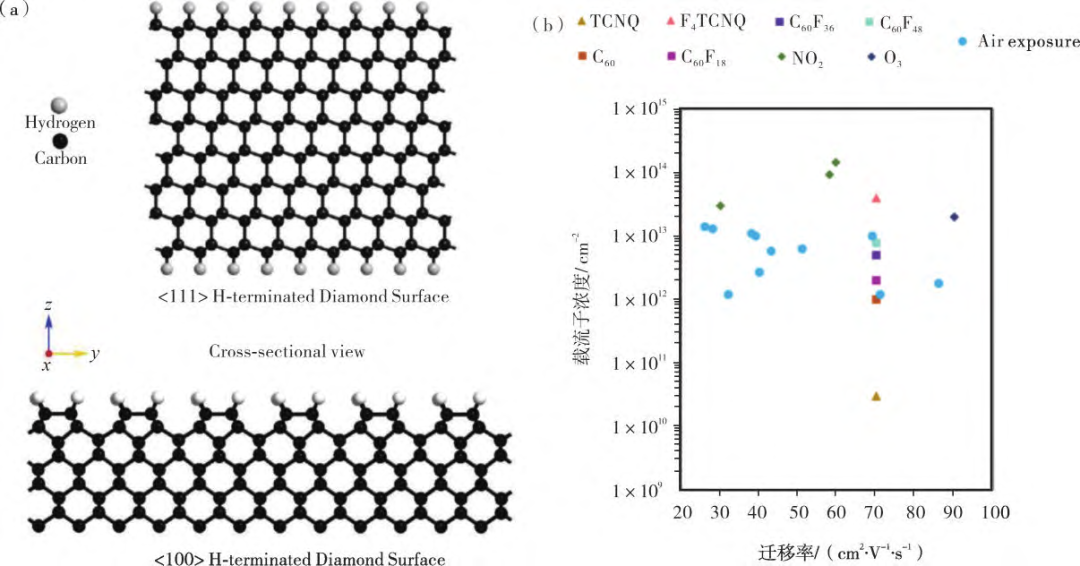

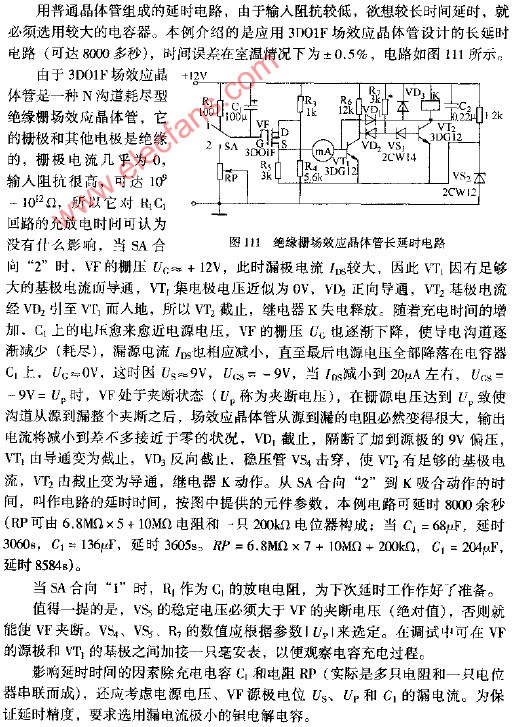

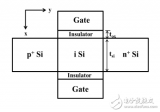

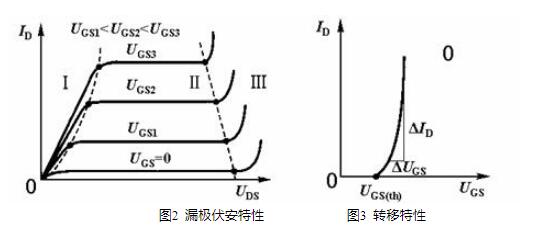

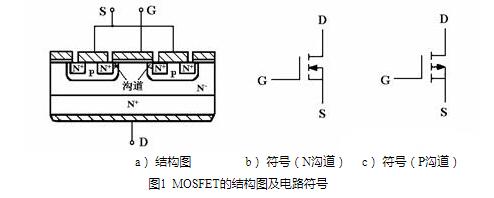

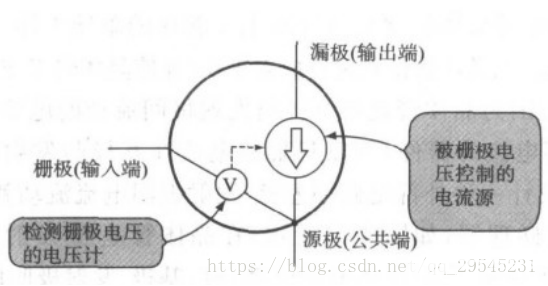

雖然金剛石半導體的B摻雜研究較為成熟,但B的激活能較高,常溫下難以電離,限制了其在電子器件領域的發展[16]。最近的研究發現,H終端金剛石(見圖1)具有p型導電,這引起了研究人員的廣泛關注。

1989年,Landstrass?等[19]研究發現,未使用任何雜質摻雜技術制備的H?終端金剛石表面電導率為1×10-6?Ω-1?cm-1。Gi 等[20-21]通過實驗證明了電子轉移依賴于 H 終端金剛石的環境氣氛,并有實驗表明?H?終端金剛石表面存在負電子親和勢[22],其導電表面下存在空穴積累層[23]。Maier 等[24]進一步證實了由于表面存在的空氣分子能夠作為電子受體,H終端和環境空氣暴露能夠增強金剛石表面的電導率。 經過長時間的理論發展和實驗探索,金剛石氫終端表面的轉移摻雜導電機理得到了廣泛認可。

當H 終端與水蒸氣接觸時會形成水合氫潤濕層,潤濕層會吸附一些低非占據電子能態的氣體(氧氣、甲酸、二氧化碳等),價帶電子向低非占據能態吸附層的躍遷,使亞表面層積累足夠多的空穴,最終形成導電的二維空穴氣(2DHG),從而實現金剛石表面導電[6,25]。 選用不同的氣體分子作為摻雜物會明顯影響?H終端金剛石的電導率,H?終端金剛石的導電特性波動十分巨大,其遷移率和典型載流子濃度的變化范圍分別為?20—100cm2??V-1??s-1?和?1×1012—1×1013cm-2[26-27]。這可能是由于存在太多難以控制的變量,如金剛石表面形態、H 終端密度、表面污染、自然發生的大氣吸附物、襯底組成和金剛石晶體質量等。空氣摻雜 H 終端金剛石的電學特性差異大,但2DHG 的載流子密度很少超過 1×1013?cm-2。

相比于空氣吸附轉移摻雜,直接選用特定氣體分子作為轉移摻雜物可顯著提高 H 終端金剛石的導電特性(見圖 1)。富勒烯分子 C60?及其氟化變體具有較高的電子親和勢,是首批 H 終端金剛石上的電子受體分子之一。C60?作為轉移摻雜物時,H 終端金剛石的空穴載流子濃度與空氣暴露產生的相當[28-29]。此外,Riedel 等[30]研究發現,在臭氧環境下進行退火可增強 H 終端金剛石表面導電性,這是因為臭氧可能產生部分 O 終端,導致局部鍵合,消除或降低了電子交換的勢壘,提高了表面導電性[30]。 雖然選用特定的氣體分子可以提高 H 終端金剛石的電導率,但分子吸附層本身穩定性和均一性很低的問題依舊沒有解決,難以應用于電子器件。

1.2 金屬氧化物

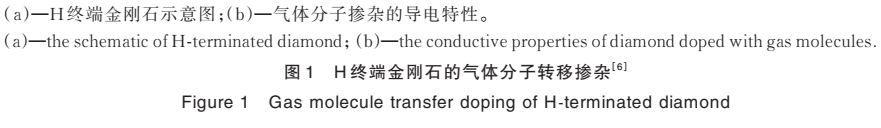

為了綜合提高?H?終端金剛石材料作為電子器件的穩定性和導電性,人們將研究重心逐漸轉向許多固體包封材料,其中金屬氧化物最為普遍。高電子親和勢(ElectronAffinity,EA)和功函數的過渡金屬氧化物(TransitionMetalOxides,TMOs)已被證明是有效的 H 終端金剛石表面摻雜物。 當轉移摻雜物的電子親和勢較高時,表面電子受體導帶位于 H 終端金剛石價帶下方,費米能級對齊會導致能帶向上彎曲從而在金剛石表面形成2DHG,這一發現引起了眾多學者的廣泛關注。2013 年,Russell 等[31]研究發現,三氧化鉬(MoO3)可以誘導轉移 H 終端金剛石表面電子,使 2DHG 載流子濃度提升了一個數量級,且在金剛石/MoO3 界面中發現了清晰的電荷分離。

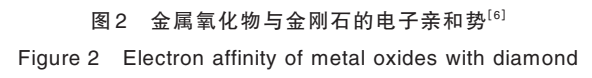

之后,五氧化釩(V2O5)[32-33]?,三氧化鎢(WO3)[32,34],三氧化錸(ReO3)[23,34],五氧化鈮(Nb2O5)[32]和三氧化鉻(CrO3)[35]等相繼被用作摻雜物。其中 MoO3、V2O5 和 WO3 的載流子密度超過1×1014?cm-2[32,34],V2O5 和 MoO3 可在 300℃?下實現高溫穩定性[26,36],而 ReO3 可達 400℃[34]。相比于氣體分子,TMOs 是 1 種更有吸引力的電子轉移摻雜物,它們可在更大的溫度范圍內具有更強的穩定性,并且在由具有可控性能的固體材料驅動下,可產生穩定可靠的高載流子濃度。圖 2 為與金剛石帶隙有關的 TMOs 材料導帶的比較[6]。?

后續實驗發現,在不引入其他氣體分子或表面終端時,具有較低EA 的 Al2O3 依然能夠作為 H 終端金剛石的轉移摻雜物,產生 2DHG[37]。這一現象引起了學者們的討?論,可能的解釋有兩種:其一為ALD 技術制備 Al2O3?層會產生間隙氧和 Al 空位[38];其二為 Al2O3?與 H 終端金剛石存在相互作用鍵合[39]。這兩種解釋都能與實驗較好符合,同時表明了電荷摻雜和鍵合也可以在 H 終端金剛石表面產生 2DHG。 這些金屬氧化物大多就是?FET?器件中較為常用的柵層材料,制備工藝較為成熟,且穩定性良好,這一發現極大地促進?了?H?終端金剛石在電子器件領域的發展。

1.3 金屬電極接觸

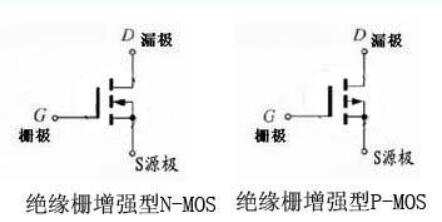

盡管 H 終端金剛石半導體材料已經具有良好的導電性、環境穩定性和熱穩定性,但使其應用于電子器件領域,還需要研究其與金屬等電極材料的接觸特性。 1994 年,Aoki 等[40]研究了 CVD 制備的 H 終端金剛石表面與各種金屬的接觸特性,結果表明,界面肖特基勢壘高度(schottkybarrierheight,SBH)與 H終端金剛石表面沉積金屬的功函數有很強的相關性。這是由于 H 終端金剛石表面可降低費米釘扎,使得其表面狀態受到金屬功函數的影響,高功函數金屬在 H 終端金剛石上表現出線性歐姆響應,而低功函數金屬被用于產生與大肖特基勢壘的接觸[41-42]。

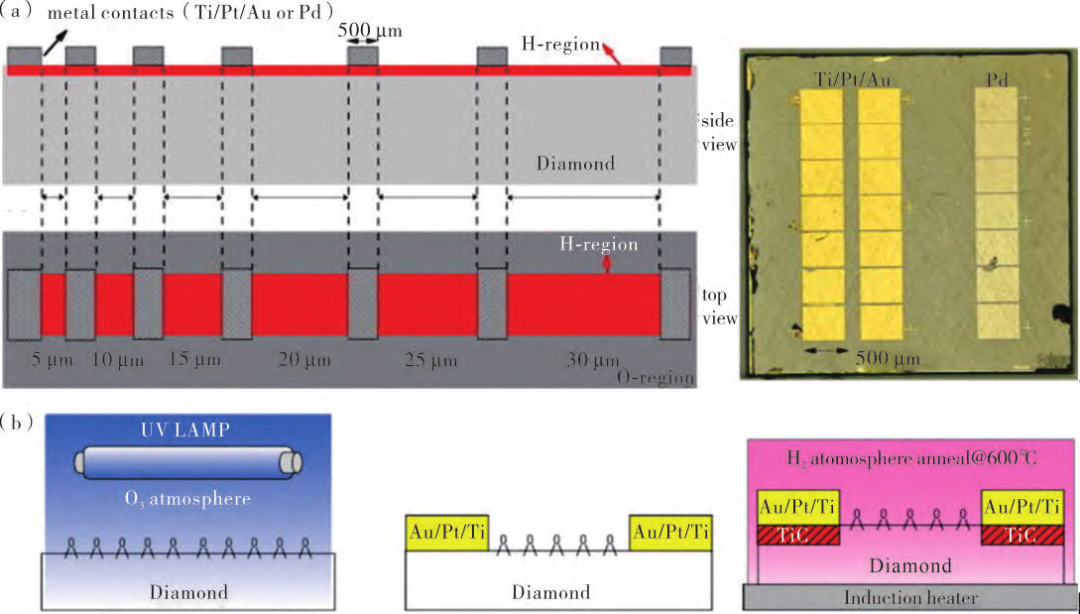

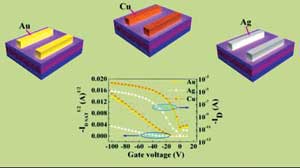

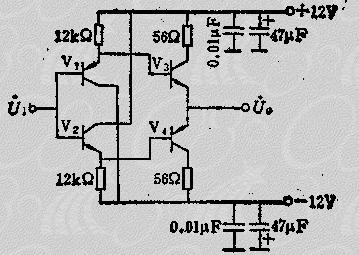

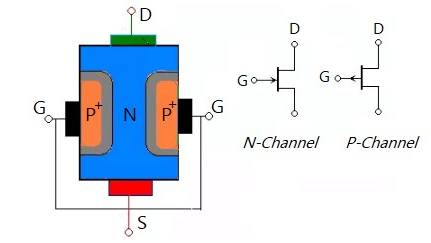

在 MOSFET 器件中,源漏級的金屬電極需要與 H 終端金剛石具有較好的歐姆接觸。具有較高功函數的 Au、Ag、Cu、Ir、Pt 和 Pd 被證明可以在 H終端金剛石表面產生歐姆接觸(見圖 3(a)),是備選的 H 終端金剛石 FET 的金屬電極[43-48]。這些金屬中,由于 Au 用于電子器件領域的沉積工藝較為成熟,它成為了 H 終端金剛石上最常用的歐姆接觸電極[47-49]。

此外,一些研究表明部分碳化物同樣可以與?H終端金剛石實現歐姆接觸[50-51]。Jingu 等[50]首先將Ti 制備在 O 終端金剛石上,然后用氫等離子體金剛石進行處理以獲得 H 終端,最后測得 TiC 與金剛石的最終接觸電阻約為9Ω?mm,TiC 與 H 終端金剛石接觸的制備流程如圖 3(b)所示。Vardi 等[51]研究了由鎢形成的碳化物接點,其接觸電阻為 2.6Ω?mm,且具有良好的機械穩定性。這些研究還表明,碳化物接觸電極可以在氫等離子體暴露下穩定存在。 因此,高功函數金屬和碳化物可以與?H?終端金剛石實現歐姆接觸,且工藝較為簡單集成,可以作為FET 器件的源漏電極。?

1.4 H終端MOSFET實現

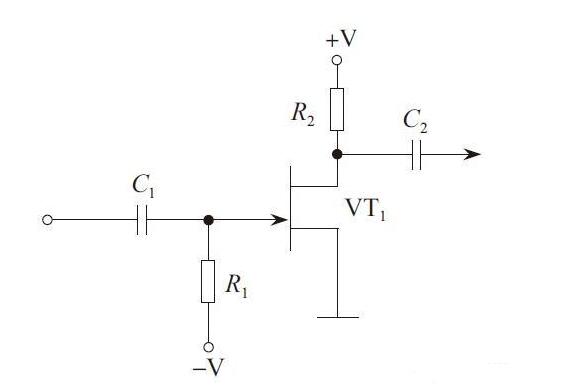

隨著H終端金剛石材料的研究日益深入,其電子器件的設計開發呼之欲出,其中FET是最被關注的領域。 在1994年,Kawarada等[52]使用CVD生長的H終端金剛石襯底(100),通過空氣暴露轉移摻雜實現導電性,結合Al柵極的肖特基柵、Au源漏極的歐姆接觸,首次實現了H終端金剛石三端增強型FET?的制備。該器件的柵極長度為?10μm,其最大漏極電流為1.6mA?mm-1,非本征跨導高達200μS?mm-1;將柵極長度增加到41μm,由于更大柵極的耗竭區域增加,可以完全關閉器件,進而將非本征跨導降低到20μS?mm-1,最大漏極電流降低到0.14mA?mm-1。這項工作開創性地驗證了將H終端金剛石用于電子領域的潛力,從這項工作開始,利用H終端金剛石轉移摻雜的FET技術得到了長足的發展。

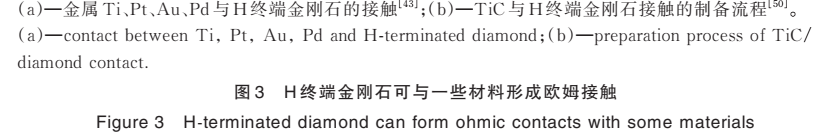

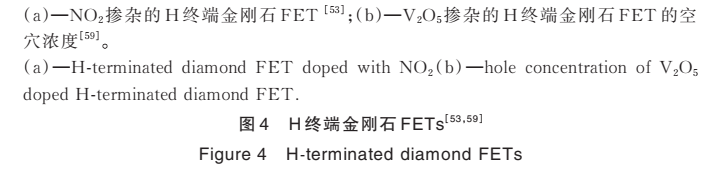

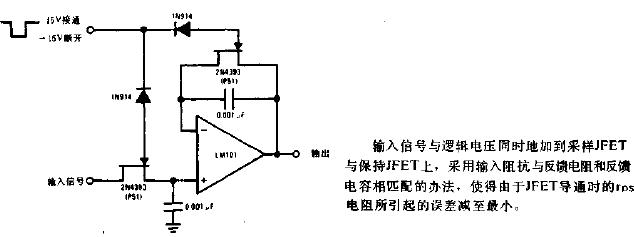

使用氣體分子作為轉移摻雜物可以產生2DHG,有?望借此制備出 H 終端金剛石 FET 器件。但氣體分子的穩定性較差,于是部分研究者利用Al2O3等絕緣層對 H 終端表面進行鈍化封裝,提高了氣體分子轉移摻雜產生 2DHG 的穩定性[53-54]。NO2作為轉移摻雜物時的空穴濃度比空氣摻雜時要高一個數量級[55-56],是較優的氣體分子轉移摻雜物。2022 年,MakotoKasu 等[53]在高質量異質外延金剛石襯底上使用 NO2 作為轉移摻雜物,利用 Al2O3 進行鈍化封裝,制備了 H 終端金剛石 MOSFET(見圖4(a))。該器件具有 7.54mΩ?cm2 的低比導通電阻和0.68A?mm-1的高漏極電流密度,溝道關閉狀態下的擊穿電壓高達-2568V,器件還具有 874.6MW?cm-2的最大可用功率密度,達到了當時金剛石器件的最高報告值。后續,他們進一步優化工藝,將擊穿電壓進一步提高到了-3326V[54]。

鈍化封裝技術一定程度上提高了氣體分子摻雜后器件運行的穩定性,但這不僅增加了制備工藝,也依舊難以保證摻雜后 FET 器件的均一性。而在 H終端金剛石表面直接沉積氧化物實現轉移摻雜,既簡化了制備工藝,又保證了 FET 的穩定性和均一性[57]。Colangeli 等[58-59]利用 V2O5 制備了器件,研究了不同金剛石晶面制備的 FET 的空穴濃度(見圖 4(b)),其高電子親和勢允許 H 終端金剛石產生2DHG。Liu 等[60]利用電子束蒸發技術直接在 H 終端金剛石上生長 Y2O3 氧化物絕緣體,制備了增強型H 終端金剛石 FET,Y2O3 薄膜中的正電荷可能補償了空穴積聚,使得 FET 具有明顯的常關特征,最大漏源電流為 114.6mA?mm-1。

2 表面終端金剛石FET?的研究現狀?

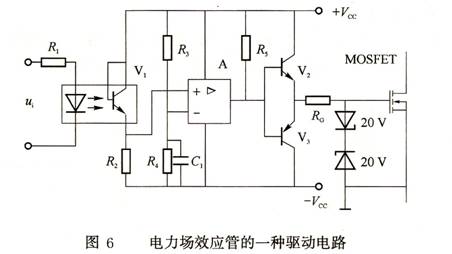

在大多數情況下,H?終端金剛石?FET?表現出常開特性,難以實現安全、節能和邏輯電路的應用,特別是由耗盡模式和增強模式組成的?H?終端金剛石NOT?和?NOR?邏輯電路,因此迫切需要研制增強型H 終端金剛石 FET[61]。此外,為了提升器件性能以?滿足不同的應用需求,研究者們通過對柵層的制備、表面終端、金剛石摻雜、FET 結構等方面研究,優化了金剛石 FET 的閾值電壓、載流子濃度、載流子遷移率、擊穿電壓等。

2.1 柵介電層材料

2.1.1 鐵電柵層材料

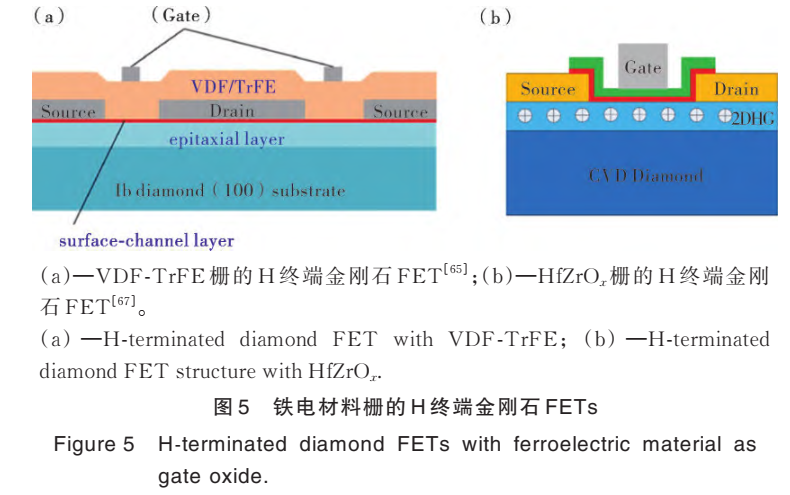

鐵電材料作為?FET?的柵層時,其負電容特性可以大幅降低亞閾值擺幅,使其小于傳統?MOSFET器件的玻爾茲曼極限?60mV?dec-1[62],提高了?FET的開關速率。此外,鐵電材料具有剩余極化,有望同時實現無外加電場時保持 FET 器件的開關狀態。 2009 年,Liao 等[63-64]首先使用 Pb(Zr0.52,Ti0.48)O3(PZT)鐵電材料作柵,Al2O3 作為絕緣層,摻硼單晶金剛石半導體制備了 FET,可應用于非易失性存儲器和微機電加工技術。傳統鐵電材料 PZT 等的復雜制備工藝容易破壞 H 終端金剛石表面[65],要求插入絕緣層以提高鐵電材料質量,而 2DHG 進一步縮小了絕緣層材料的選擇,這嚴重限制了 H 終端金剛石的鐵電 FET 發展。相比于 PZT,有機鐵電材料聚偏氟乙烯(poly(vinylidenefluoride),PVDF)及其共聚物為柔性薄膜,其制備簡單、化學惰性好且受界面問題影響較小[66]。? 2016 年,Kawae 等[65]使用偏氟乙烯(VDF)-三氟乙烯(TrFE)共聚物鐵電材料作為柵極,制備了H 終端金剛石 FET(見圖 5(a))。

當柵極電壓從 20V掃至-20V 時,飽和漏極電流最大值為 50mA?mm-1,最大開關電流比和線性遷移率分別為 108 和398cm2?V-1?s-1;此外,通過 VDF-TrFE 柵極的剩余極化調制?FET 結構的漏極電流,在不施加直流柵極電壓的情況下獲得了 103的開關電流比。 HfZrOx 鐵電材料進一步克服了其他鐵電材料難以集成、需要高溫退火、高工作電壓、大厚度等缺點。Zhang 等[67]首次展示了一種具有鐵電 HfZrOx/Al2O3 堆疊柵極介質的 H 終端金剛石負電容 FET[67](見圖 5(b))。在 7.3—9.2V 寬的記憶窗內,測得的最大開關比為 109,柵電壓從-10.0V 到 10.0V,亞閾值擺幅約為 58mV?dec-1,小于玻爾茲曼極限。這些結果表明,HfZrOx/Al2O3/H 終端金剛石 FET 為金剛石增強型 FET、負電容 FET 和高密度集成非易失性存儲器提供了新的可能性。?

2.1.2 其他柵層材料

一些柵層材料因其優異特性在Si?半導體器件、熱離子電子源等領域有所應用,這些柵層材料的選用可能會簡化 H 終端金剛石器件的制備工藝,制備增強型 FET,優化其導電特性[68]。 金屬?Y?的功函數較低且沉積工藝簡單,不會破壞金剛石的表面終端,是增強型金剛石 FET 的候選柵層材料。Zhang 等[69]首次將 Y 應用于 H 終端金剛石 FET,Y 和金剛石間有 10nm 厚的 Al2O3 介電層。在柵極電壓為 7V、漏極源電壓為 20V 時,柵極長度為8μm 的 FET 的最大漏極源電流為-53.9mA?mm-1,電流開關比超過 109,亞閾值擺幅為 198mV?dec-1。但較厚的介電層導致 FET 仍為常開模式,因此該組進一步優化了介電層厚度,分別采用了 5nmAl2O3介質層[70]和無介電層[71]方案,成功制備了常關 Y 柵金剛石場 FET。

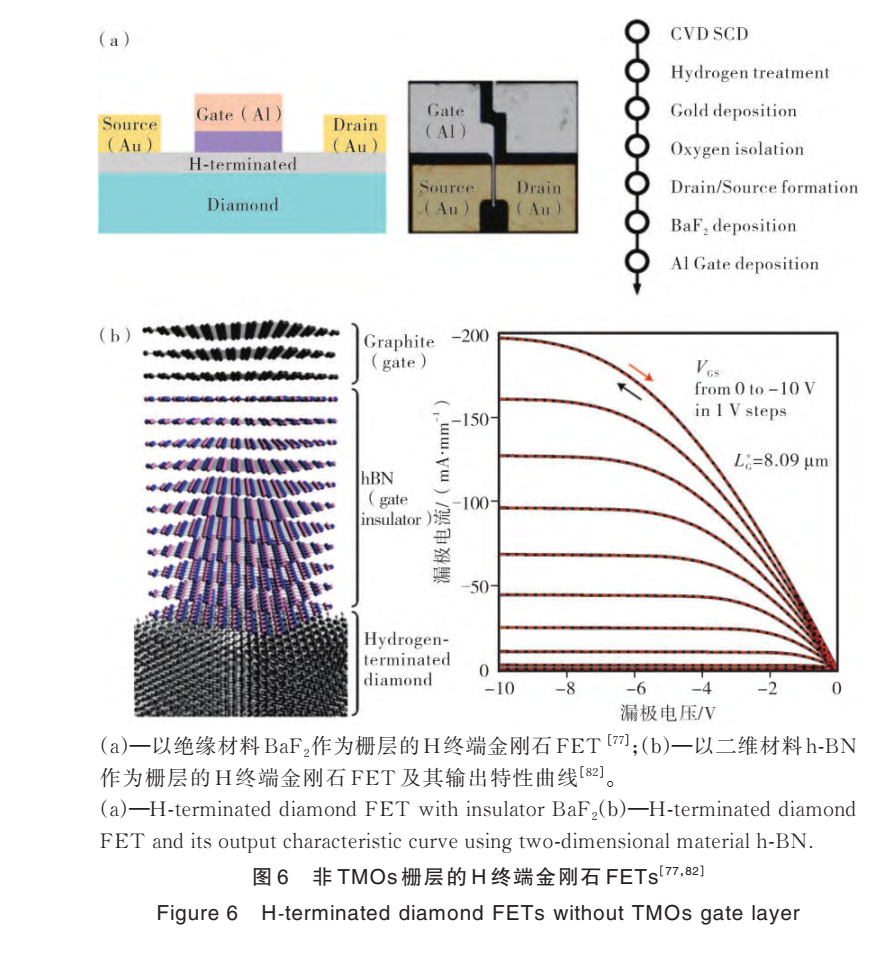

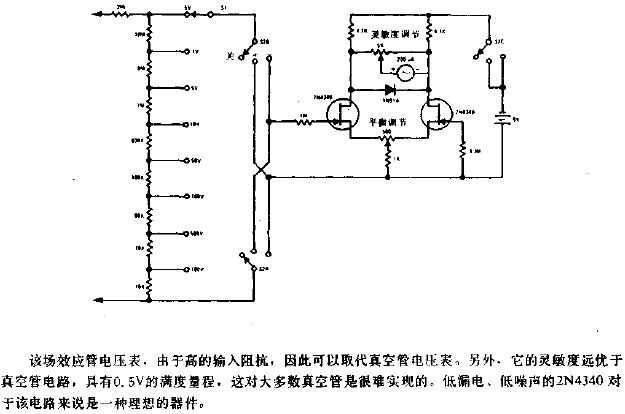

然而,隨著介質層的降低,FET 的閾值電壓提高且在大電壓下柵層易被擊穿,限制了Y 柵 FET 的應用。 直接對金屬進行氧化制備 H 終端金剛石 FET的柵層,可以簡化制備工藝。Wang 等[72]利用 6 nm 厚的 Al 薄膜在室溫空氣中的自氧化制備了 AlOx層,實現了 H 終端金剛石 FET。AlOx介質層能有效降低泄漏電流,VDS =-15V 時,閾值電壓為-0.4V。Zhang 等[73]利用電子束蒸發技術在 H 終端金剛石表面沉積了 5nm 的 Ti 薄膜,然后在 120℃的空氣中熱氧化 10h,形成 Ti/TiOx,成功制備了增強型金剛石 FET。在 VDS 為?-8V 時,FET 的閾值電壓為-0.14V,Ti 和 H 端金剛石之間功差的不同,從而耗盡了 H 終端金剛石的空穴載流子,使得器件表現為常關特性。 六硼化鑭(LaB6)具有低功函數、高熔點、低揮發性、低電阻率和高化學穩定性等特點,是熱離子電子源領域的常用材料[74],Wang 等[75]采用 LaB6 制備了一種增強型 H 終端氫金剛石 FET,其產生增強模式的原因是 LaB6 層的電子流入 2DHG 溝道并對空穴進行補償,導致導電溝道關閉。氟化鋇(BaF2)薄膜是 1 種應用廣泛的寬禁帶能(10.6eV)絕緣材料[76],He 等[77]利用 Al/BaF2 柵極材料制備了高性能增強型金剛石 FET(見圖 6(a))。該增強模式主要是由于柵極金屬對通道的肖特基勢壘損耗效應,其次是 BaF2 層中存在的正固定電荷。器件在 VGS 為-2.1V,有效空穴遷移率約為 225.0cm2?V-1?s-1。

為解決一些柵層材料制備工藝會破壞表面 H終端和柵層材料本身的問題,一些研究者提出了使用 Al2O3 作為過渡柵層[78]。Liu 等[79]研究了高介電常數材料 ZrO2/Al2O3 雙分子層的能帶結構、ZrO2/Al2O3 雙分子層的擊穿場強及柵漏距離對金剛石FET 性能的影響。他們還采用 ALD 制備 Al2O3 薄膜作為 TiO2 和 H 終端金剛石表面之間的緩沖層,抑制了等離子體放電效應,降低了漏電流[80]。但采用兩種柵層材料不可避免地增加了 H 終端金剛石FET 的工藝流程,提高了制備成本。

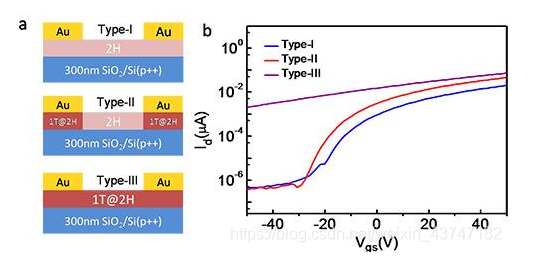

目前使用的各種柵層與表面終端金剛石接觸時,其轉移摻雜形成的電離表面受體會產生空穴散射,降低了空穴遷移率,限制了表面終端金剛石器件的性能。而二維材料無懸掛鍵的特性可以提供更良好的界面狀態,提高器件載流子遷移率。Sasama 等[81-82]以單晶六方氮化硼(h-BN)作為柵極電介質,制備了常態關的 H 終端金剛石 FET,并測試了輸出特性曲線(見圖 6(b))。界面處的表面受體密度降低,但 2DHG 具有較高的室溫霍爾遷移率(680cm2?V-1?s-1),與其他 p 通道寬帶隙 FET 相比,器件具有較低的片電阻(1.4kΩ)和較大的 ON 電流(1600μm?mA?mm-1),開關比為 108。但使用二維材料作為柵層會導致在大電壓情況下,柵極可能首先被擊穿,這會顯著降低 H終端金剛石 FET 的擊穿電壓[82]。

2.2 表面端基

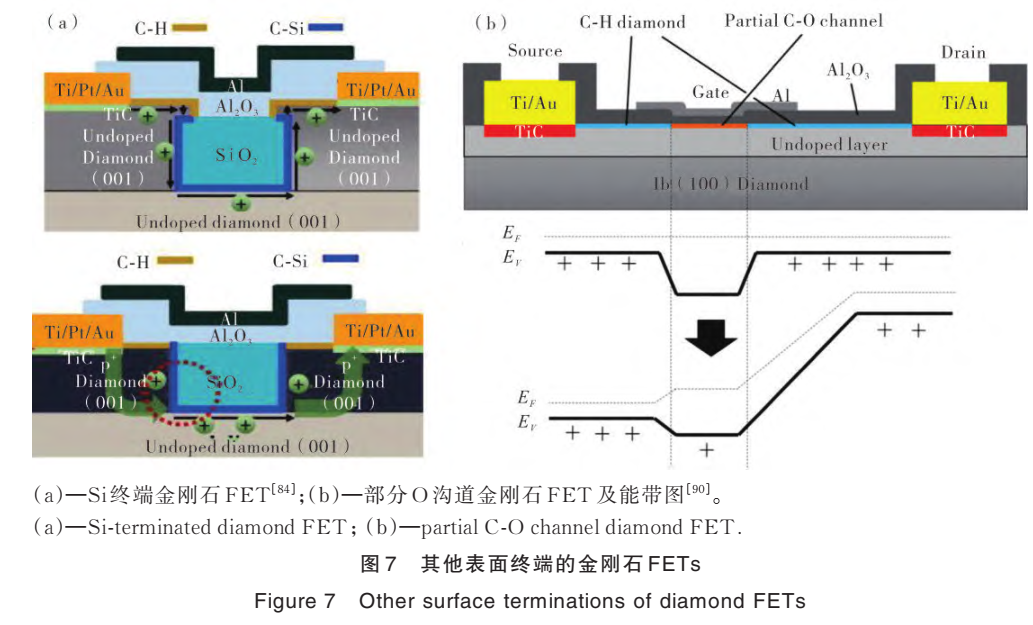

除?H?終端金剛石外,O、F、Si 等終端的金剛石也曾被廣泛研究,他們的電子親和勢差別較大,因此改變金剛石表面終端構成,可以極大地影響 2DHG 的導電特性[83]。 相比于其他氧化物絕緣層,SiO2 具有最寬的帶隙和更簡單的制備流程,更有利于功率器件的制備與應用,因此對 Si 終端金剛石 2DHG 的性質及電場效應對其導電性的影響進行研究十分有必要[84]。2015 年,Schenk 等[85-86]研究了在真空 Si 終端金剛石的形成和表面表征,發現了氧化 Si 終端金剛石上的能帶彎曲。 2020?年,Fei 等[84]在 SiO2 掩膜的選擇性外延生長過程中,利用 Si 終端取代掩膜下金剛石原本的 O終端。研究發現:高溫的選擇性生長及還原氣氛使SiO2 中的 Si 原子與金剛石表面相互作用,從而形成由金剛石表面單層或多層 C-Si 鍵組成的 Si 終端金剛石,利用 Si 終端金剛石制備的 FET 均表現出增強模式特性,且 Si 終端金剛石的導電性同樣受到電場調制。

之后,浮現出了一些新的 Si 終端金剛石導電溝道的制備方法,Zhu 等[87]在還原氣氛中對 SiO2 柵絕緣體進行退火,在(111)金剛石襯底上構建了金剛石/Si 界面,采用 Si 終端金剛石的導電通道制備了相應的 FET(見圖 7(a)),檢測表明 SiO2 薄膜和(111)金剛石之間界面良好,這確保了其較高的溝道空穴遷移率 200cm2?V-1?s-1 和較低的界面態密度3.8×1011 cm-2?eV-1。2022 年,Fu 等[88]利用分子束沉積技術實現原子尺度 Si 沉積,優化了 Si 終端金剛石的制備方法。與 H 終端不同,O 終端金剛石的電子親和勢高達+1.7eV[89],難以實現轉移摻雜產生 2DHG,因此一些研究人員想到以此來制備增強型金剛石表面終端 FET[90-91]。Kitabayashi 等[90]利用氧化部分導電溝道制備了 H 終端金剛石 FET,該器件在室溫下表現出超過 2kV 的高擊穿電壓和常斷特性(見圖 7(b))。Chen 等[91]采用 Al2O3納米粒子掩膜的超強力臭氧工藝制備了部分 O 終端金剛石,與 Al/H 終端金剛石相比,Al/O 終端金剛石結構具有更高的 SBH,可以很好地抑制金剛石 FET 關閉狀態下的漏電流。?

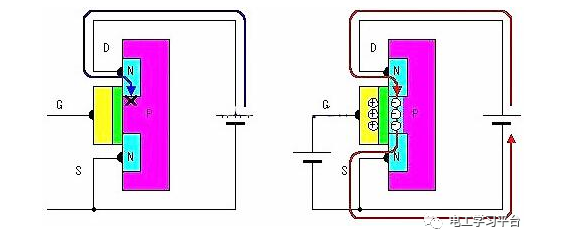

2.3 金剛石摻雜與FET?結構

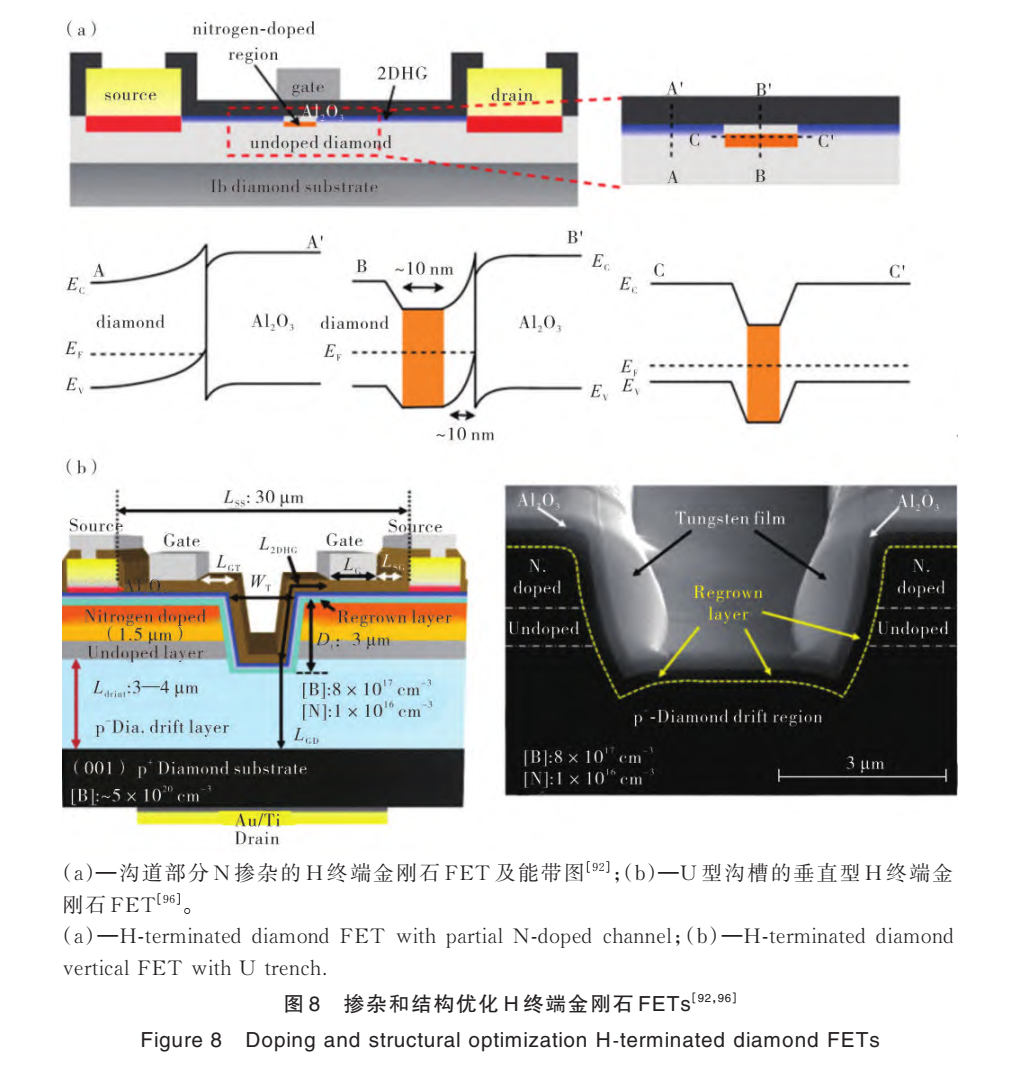

除了對金剛石表面終端和柵層的優化外,一些研究者通過改變金剛石 FET 結構,調控金剛石的摻雜[92-93]和晶體取向[59]等,從而優化表面終端金剛石 FET。對金剛石材料進行摻雜,可以顯著改變其載流子濃度,調控?2DHG 導電特性,增加 FET 的耐擊穿場強。Kawarada 等[92]使用離子注入在 H 終端導電溝道下方形成一層薄的 N 摻雜層,實現了增強型金剛石表面終端 FET(見?圖 8(a))。N 是深層供?體(1.7eV),氮摻雜層抑制了近表面空穴的積聚,FET 的閾值電壓高達-2.5V,室溫擊穿場強為2.7MV?cm-1。在 64 個具有相同柵極長度的設備中,75%?表現為增強型特性。 對源漏區的金剛石材料進行摻雜,可以優化其與金屬電極的接?觸,實?現低歐姆接觸電阻。Zhu等[94]報道了一種高漏極電流密度的增強型 H 終端金剛石 MOSFET,在多晶金剛石襯底上沉積了大量摻硼層作為源漏區,以柵極寬度歸一化計算的最大電流密度為-400mA?mm-1。進一步研究發現,摻雜 B 的源和漏極可以提供高濃度的空穴,提高了由H 終端引起的表面 p 型通道電輸運特性[93]。

此外,部分研究者借鑒傳統 MOSFET 器件的結構,制備出了導通電流更高的 H 終端金剛石器件。Tsunoda 等[95]研究了一種具有溝槽柵結構的低導通電阻的(001)垂直型 H 終端金剛石 FET(見圖 8(b))。研究發現:在引入溝槽柵結構后,器件的有源面積減小,顯著提高了 FET 器件的集成度,并獲得了更大的導通電流。在 VDS=-50V 和 VGS=-20V 時,最大漏極電流密度超過 20kA?cm-2,這是目前(001)晶面垂直型金剛石 MOSFET 的最高值。之后,該組又制備出了 U 型槽的垂直型 H 終端金剛石器件,獲得了垂直型器件的最高擊穿電壓 580V[96]。然而,具有溝槽垂直型 FET 器件會集聚電場,大幅降低了器件的擊穿電壓,限制了 H 終端金剛石垂直型器件的發展。?

?3 總結與展望?

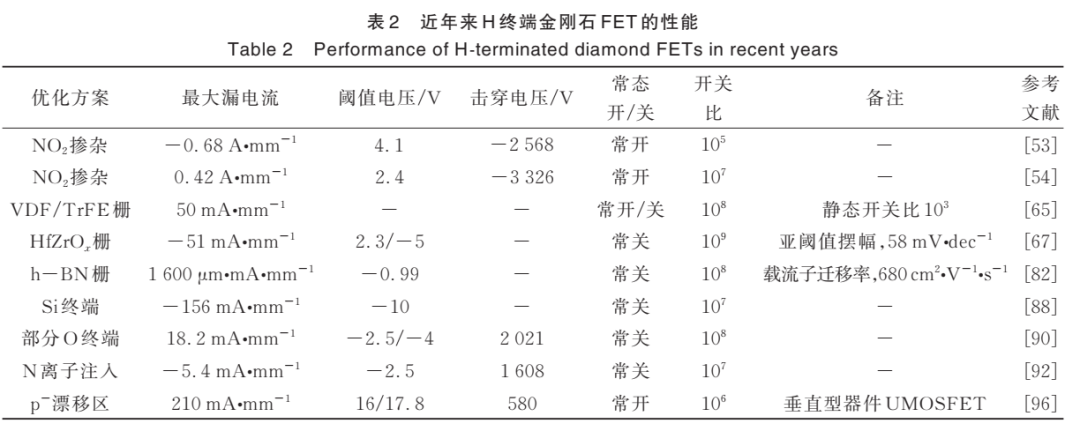

本文介紹了H 終端金剛石轉移摻雜物的發展,綜述了當前 2DHG 的產生機理。為了進一步提高表面終端金剛石 FET 的載流子濃度、遷移率、擊穿電壓,獲得性能優良的增強型 FET,需要從柵層材料選擇、表面終端、結構和摻雜等技術手段著手優?化,總結了近年來不同優化方案下?H?終端?FET?器件的性能(見表 2)。本文總結了當前優化方案的主要出發點和問題。?

柵層材料可以極大地影響2DHG 的導電特性。選擇常規的氧化物絕緣體作為柵層,其載流子散射較為嚴重,且無法獲得增強型特性;選擇非常規柵層時,高擊穿電壓、優良的導電特性和增強型 FET 往往不可兼得。這可能是由于界面處的電荷轉移較容易,往往其載流子散射嚴重或難以承受較高的電壓,而界面處電荷轉移困難,則會導致載流子濃度較低,閾值電壓較高,FET 開關性能差。需要更加深入地了解 H 終端金剛石的 2DHG 導電機制,尋找柵層材料,以獲得更好的界面狀態。 從表面終端處理、結構和摻雜等方式可以特定解決部分問題。通過表面終端處理,有望優化 FET的擊穿電壓并獲得增強型特性。

FET 結構的改變可以大幅優化其導電特性,而摻雜有望優化電極與金剛石的接觸并獲得增強型特性。 當前,H?終端金剛石 FET 已經有了長足的發展,各種優化技術相結合,可以進一步提升其導電特性和擊穿電壓,而金剛石本身具有優良的導熱率,可以一定程度上緩解功耗散熱的問題,這使得其在高溫、高功率和高頻的電子器件領域必有一席之地。H 終端金剛石與鐵電材料等其他功能材料結合,在光學傳感、非易失性存儲等領域也有望得到應用。 然而,金剛石無法 n 型摻雜,極大地限制著金剛石 FET 器件擊穿電壓的提升,無法發揮金剛石本身的優良性能,無法制備常規的 MOSFET、IGBT 等器件,難以與 SiC 等半導體材料競爭。此外,金剛石器件的大規模應用仍受限于大尺寸、高質量的金剛石晶圓制備,有待進一步解決。?

審核編輯:劉清

電子發燒友App

電子發燒友App

評論