?摘? 要?

超寬禁帶氧化鎵(Ga2O3)半導(dǎo)體具有臨界擊穿場強(qiáng)高和可實現(xiàn)大尺寸單晶襯底等優(yōu)勢,?在功率電子和微波射 頻器件方面具有重要的研究價值和廣闊的應(yīng)用前景。?盡管Ga2O3材料與器件研究已取得很大進(jìn)展,?但其極低的熱導(dǎo)?系數(shù)和缺少有效的p 型摻雜方法成為限制其復(fù)雜器件結(jié)構(gòu)制備和器件性能提升的主要瓶頸。??

針對上述兩大關(guān)鍵瓶 頸,???本文綜述了利用異質(zhì)材料集成的方法實現(xiàn)高導(dǎo)熱襯底Ga2O3?異質(zhì)集成晶體管與基于p?型氧化鎳/n型氧化鎵(p-?NiO/n-Ga2O3)異質(zhì)結(jié)的Ga2O3功率二極管和超結(jié)晶體管的研究進(jìn)展。??

采用離子刀智能剝離-鍵合技術(shù)實現(xiàn)的高導(dǎo)熱 襯底Ga2O3異質(zhì)集成方案可有效解決其導(dǎo)熱問題,??碳化硅(SiC)和硅(Si)基Ga2O3異質(zhì)集成晶體管展現(xiàn)出遠(yuǎn)優(yōu)于Ga2O3體材料器件的熱相關(guān)特性。??

采用異質(zhì)外延技術(shù)制備的p-NiO/n-Ga2O3功率二極管和超結(jié)晶體管均展現(xiàn)出良好的電?學(xué)特性,??p-NiO/n-Ga2O3異質(zhì)結(jié)為Ga2O3雙極器件的發(fā)展提供了一種可行途徑。??

異質(zhì)集成和異質(zhì)結(jié)技術(shù)可有效地克 服Ga2O3本身的關(guān)鍵難點問題,?助力高效能、高功率和商業(yè)可擴(kuò)展的Ga2O3微電子系統(tǒng)的實現(xiàn),?推動其實用化進(jìn)程。

?研究背景?

超寬禁帶氧化鎵(Ga2O3)半導(dǎo)體禁帶寬度為4.5~ 5.16 eV, 理論預(yù)測其擊穿電場強(qiáng)度達(dá)到8 MV/cm, 遠(yuǎn)高 于硅(Si) 、碳化硅(SiC)和氮化鎵(GaN)等半導(dǎo)體材料, 在功率和射頻器件方面有著重要的研究價值和巨大的 應(yīng)用前景[1] 。經(jīng)過多年的發(fā)展, Ga2O3單晶研究取得了長 足的進(jìn)步。目前, 可以利用區(qū)熔法、導(dǎo)模法和提拉法等 方法實現(xiàn)大尺寸β相Ga2O3單晶襯底的制備[1,2] 。 早期的β-Ga2O3晶體管由于Ga2O3外延溝道材料質(zhì) 量較差, 因此電學(xué)特性不理想[3~5] 。2016年, 日本國家信 息與情報中心(The National Institute of Information and Communications Technology, NICT)的Wong等人[6]在鐵(Fe)摻雜β-Ga2O3(010)半絕緣襯底上制備了場板結(jié)構(gòu)金 屬-氧化物-半導(dǎo)體場效應(yīng)晶體管(metal-oxide-semicon- ductor field effect transistor, MOSFET), 其擊穿電壓Vbr 超過750 V, 且開關(guān)電流比ION/IOFF高于109, 自此拉開了 高性能Ga2O3 晶體管研究序幕。目前,Ga2O3晶體管方面 的研究已經(jīng)引起了廣泛的關(guān)注, 各國政府和科研機(jī)構(gòu) 都針對Ga2O3材料 、器件的研發(fā)投入大量人力和 物力[2] 。

為提升Ga2O3晶體管器件性能, 研究人員開發(fā)了 凹槽柵結(jié)構(gòu) [7] 、復(fù)合場板結(jié)構(gòu) [8] 、垂直鰭(fin)型溝 道結(jié)構(gòu) [9] 和超高介電常數(shù)BaTiO 3 柵介質(zhì)層結(jié)合β -

(Al0.18Ga0.82)2O3/Ga2O3雙異質(zhì)結(jié)導(dǎo)電溝道[10]等器件技 術(shù)。目前, 水平和垂直結(jié)構(gòu)Ga2O3晶體管器件分別實現(xiàn) 了最高擊穿電壓8[11]和4 kV[2], 最高功率品質(zhì)因子408[10] 和280 MW/cm2[9] 。雖然Ga2O3晶體管在器件性能上已經(jīng) 取得良好進(jìn)展, 但Ga2O3材料極低的熱導(dǎo)率和缺少有效 p型摻雜技術(shù)仍然是限制其進(jìn)一步發(fā)展的主要瓶頸。

Ga2O3材料中更為劇烈的聲子-聲子散射導(dǎo)致其熱 導(dǎo)率相比其他材料更低[12], 解決其極低熱導(dǎo)率問題是Ga2O3器件實用化的必由之路。中國科學(xué)技術(shù)大學(xué)的Yu 等人 [13] 通過襯底減薄技術(shù)進(jìn)行Ga2O3肖特基二極管 (Schottky barrier diode, SBD)的熱管理, 襯底厚度從 650 μm減到250 μm后, 器件散熱效果得到一定的提升, 但襯底機(jī)械減薄較難控制 。

利用異質(zhì)集成的方法將 Ga2O3單晶薄膜轉(zhuǎn)移到高導(dǎo)熱襯底上形成Ga2O3異質(zhì)集 成晶圓是解決Ga2O3低導(dǎo)熱瓶頸的有效方法之一。西安 電子科技大學(xué)和中國科學(xué)院上海微系統(tǒng)與信息研究所 合作團(tuán)隊, 從2017年開始, 經(jīng)過兩年攻關(guān), 成功開發(fā)出 應(yīng)用于Ga2O3晶圓的離子注入-鍵合剝離技術(shù)。2019年, 該合作團(tuán)隊[14]在國際電子器件會議(International Elec- tron Device Meeting, IEDM)上報道了利用該技術(shù)制備 的晶圓級高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓和晶體管。該 工作引起了廣泛關(guān)注, 并被Compoundsemiconductor發(fā) 表題為“Helping gallium oxide keep its cool”的文章進(jìn) 行報道。 p型摻雜技術(shù)是Ga2O3材料與器件研究的關(guān)鍵技術(shù) 難點。

非故意摻雜Ga2O3價帶頂?shù)腅-k色散關(guān)系比較平 坦, 導(dǎo)致其內(nèi)部空穴有效質(zhì)量較大, 空穴強(qiáng)烈局域化于 電負(fù)性較強(qiáng)的O 2p能級上, 同時傳統(tǒng)單一摻雜引入的 深能級受主在室溫下激活效率極低, 難以向價帶貢獻(xiàn) 有效的自由空穴, 因而Ga2O3難以實現(xiàn)p型摻雜[15] 。目前 廣泛使用的Fe摻雜半絕緣Ga2O3襯底隨著溫度升高展 現(xiàn)出明顯的n型導(dǎo)電特性, 直接導(dǎo)致Ga2O3 MOSFETs的 關(guān)態(tài)電流隨著測試溫度升高而急劇增加[16] 。而且, 缺少 p型Ga2O3, 就不能實現(xiàn)pn結(jié)以及與之相關(guān)的雙極型功 率電子器件。雖然已經(jīng)有文獻(xiàn)報道了不同的Ga2O3p型 摻雜技術(shù)和理論研究, 譬如使用氫(H)元素對Ga2O3實 現(xiàn)p型和n型雙極型摻雜[17] 、固態(tài)反應(yīng)摻雜[18]等, 但是 這些技術(shù)都存在受主離化率低與空穴濃度偏低的問 題[19] 。

研究人員也提出利用其他p型氧化物, 比如p型 NiO與n型Ga2O3組合形成pn結(jié), 并開發(fā)了相關(guān)異質(zhì)結(jié) 器件[20~23], 包括結(jié)型場效應(yīng)晶體管(junction field-effect transistor, JFET)[20] 、超結(jié)(superjunction, SJ)晶體管[21] 和pn結(jié)二極管[22]等。JFET使用與溝道構(gòu)成pn結(jié)的半導(dǎo) 體作為柵極, 類似金屬-半導(dǎo)體場效應(yīng)晶體管(metal semiconductor field-effect transistor, MESFET), 而超結(jié) 晶體管基于超結(jié)結(jié)構(gòu), 利用pn結(jié)之間的電荷平衡原理 實現(xiàn)漂移區(qū)電場調(diào)控。2021年, 西安電子科技大學(xué)與南 京大學(xué)合作團(tuán)隊報道了基于p-NiO/n-Ga2O3異質(zhì)結(jié)的Ga2O3超結(jié)MOSFET[24] 。 本文將綜合介紹高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶體 管和基于p-NiO/n-Ga2O3異質(zhì)結(jié)的功率二極管與超結(jié)晶 體管研究進(jìn)展。

1 高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓?

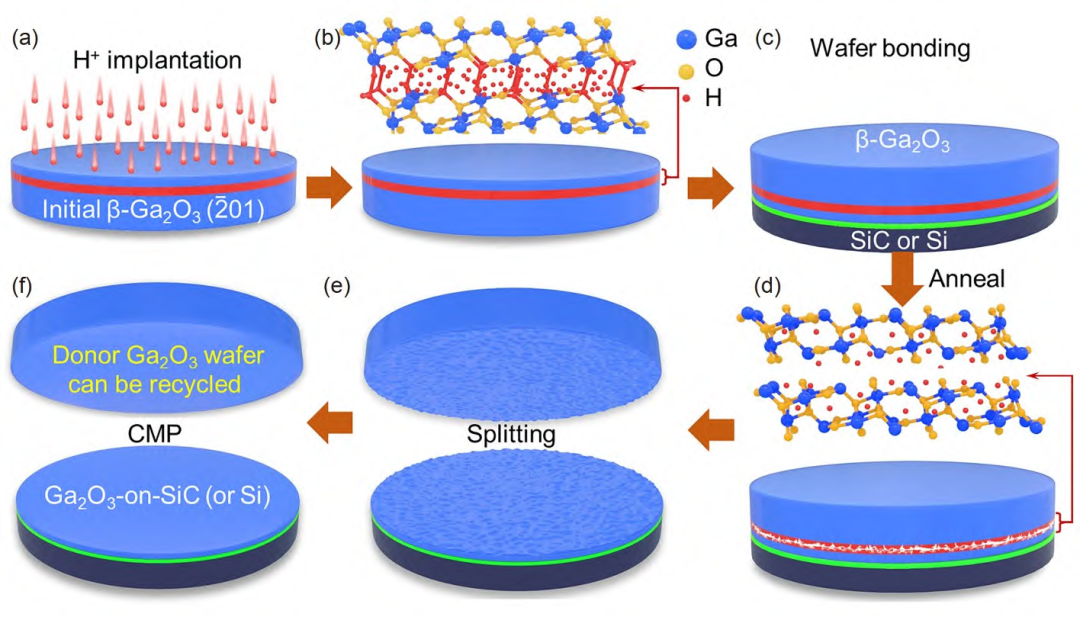

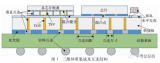

離子注入-鍵合剝離技術(shù)也稱為“ 萬能離子刀 ”技 術(shù), 可以突破不同材料之間晶格失配 、晶型失配等多 物理場失配限制, 實現(xiàn)高質(zhì)量的Ga2O3單晶薄膜與高導(dǎo) 熱襯底的異質(zhì)集成。目前基于該技術(shù)的絕緣體上硅(si- licon on insulator, SOI), 即SOI晶圓制備[25] 已經(jīng)產(chǎn)業(yè)化, 其商業(yè)名稱是Smart CutTM。 高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓制備流程如圖1所 示。首先將氫離子(H+)注入Ga2O3晶圓內(nèi)部產(chǎn)生H+缺陷 層, 之后將注入H+ 的Ga2O3晶圓與高導(dǎo)熱的SiC或Si晶 圓進(jìn)行鍵合。

在退火過程中,Ga2O3薄膜將沿著H+缺陷 層位置從Ga2O3晶圓上剝離下來, 并轉(zhuǎn)移到SiC(Si)襯底 上, 從而實現(xiàn)Ga2O3薄膜與高導(dǎo)熱襯底的異質(zhì)集成[14] 。通過控制注入離子能量和劑量 ,Ga2O3 薄膜厚度在 100 nm~10 μm范圍內(nèi)實現(xiàn)可控變化。 Liao等人[26]將氦(He)離子注入Ga2O3體材料中, 通 過加熱觀察到了Ga2O3表面的起泡行為, 但由于He離子 半徑大, 注入He離子后的Ga2O3晶體質(zhì)量會大幅度惡 化。在晶圓鍵合方面, Xu等人[27]和Lin等人[28]通過表面 激活鍵合工藝實現(xiàn)了Ga2O3與n型單晶SiC和多晶SiC的 鍵合。然而這些工作都是獨立的, 并沒有實現(xiàn)可用于器 件制備的Ga2O3薄膜與SiC襯底的異質(zhì)集成。

2019年, Xu等人[14]通過在Ga2O3晶圓中注入H+, 結(jié) 合表面激活鍵合工藝成功地將2英寸(1 in=2。54 cm)的Ga2O3單晶薄膜異質(zhì)集成到SiC襯底上(圖1)。該技術(shù)的 難點在于, 剝離退火過程中異質(zhì)晶圓之間的熱失配會 導(dǎo)致其解鍵合, 從而剝離失敗, 因此需要對離子注入劑 量 、鍵合方法以及剝離溫度工藝協(xié)同優(yōu)化[29,30] 。目前 通過該技術(shù)已經(jīng)實現(xiàn)了Ga2O3-SiC(GaOSiC) 、Ga2O3- Al2O3-SiC(GaOISiC)和Ga2O3-Al2O3-Si(GaOISi)三種不同結(jié)構(gòu)的高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓。

對于制備的2英寸Ga2O3異質(zhì)集成晶圓, Ga2O3薄膜 的轉(zhuǎn)移面積達(dá)到95%, 剝離之后, 剩余Ga2O3 晶圓完整, 后續(xù)通過化學(xué)機(jī)械拋光(chemical mechanical polishing, CMP)工藝處理, 其可以循環(huán)使用, 以減少Ga2O3異質(zhì)晶 圓的制備成本。

轉(zhuǎn)移后的Ga2O3薄膜有極佳的厚度均勻 性, 其厚度不均勻性小于±2%, 通過CMP可將異質(zhì)集成Ga2O3薄膜的表面粗糙度均方根(root mean square, RMS)減小到0。2 nm[14,30] 。通過高溫退火處理,Ga2O3薄 膜搖擺曲線的半高寬從剛轉(zhuǎn)移的230 arcsec提升到80 arcsec, 其質(zhì)量接近于同質(zhì)外延薄膜的質(zhì)量(22 arc- sec)[31] , 遠(yuǎn)優(yōu)于藍(lán)寶石襯底上異質(zhì)外延的Ga2O3 薄膜 (4248 arcsec)[32] 。

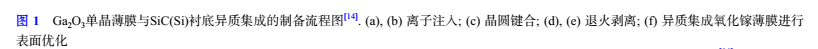

根據(jù)制備的Ga2O3/SiC異質(zhì)集成界面 的透射電子顯微鏡表征結(jié)果, 鍵合界面處存在著幾個 納米的非晶鍵合層[14,33], 鍵合層厚度可以通過鍵合工 藝和器件制備工藝溫度來適當(dāng)調(diào)整。 通過瞬態(tài)熱反射方法對Ga2O3異質(zhì)集成晶圓的熱 輸運能力進(jìn)行研究。

通過有限元模型擬合瞬態(tài)熱反射 曲線[34], 得到Ga2O3異質(zhì)集成晶圓熱導(dǎo)率和界面熱阻等 關(guān)鍵數(shù)據(jù), 相關(guān)結(jié)果如圖2所示[29,30]。高溫退火后, Ga2O3異質(zhì)集成晶圓的熱輸運能力得到大幅度提升, Ga2O3異 質(zhì)集成薄膜的熱導(dǎo)率達(dá)到9。0 W/mK, 相比退火前提升 一倍, 界面熱阻為7.5 m2 K/GW, 下降為原來的1/3, 這是 源于介質(zhì)層的結(jié)晶化。高溫退火后, SiC基Ga2O3異質(zhì)集 成晶圓的熱擴(kuò)散速率接近于SiC體材料, 遠(yuǎn)優(yōu)于Ga2O3體材料。??

?同時,??退火處理的Ga2O3異質(zhì)集成薄膜的熱傳?導(dǎo)機(jī)制由原來聲子-缺陷散射機(jī)制轉(zhuǎn)變?yōu)橐月曌?聲子?散射機(jī)制為主[30]?。?Ga2O3異質(zhì)集成器件展現(xiàn)出優(yōu)異的散?熱能力,?如圖2(d)所示,?在相同的功率偏置下,?Ga2O3體?材料SBD的表面最高溫度是SiC基Ga2O3?SBD的4倍,??同?時SiC基Ga2O3? SBD表面溫度分布非常均勻,??證明了高?導(dǎo)熱襯底優(yōu)異的散熱能力。

綜上所述,??通過萬能離子刀異質(zhì)集成技術(shù)實現(xiàn)的?高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓,??具有優(yōu)異的表面均勻?性、粗糙度和結(jié)晶質(zhì)量。??通過高溫退火處理,?Ga2O3異?質(zhì)集成晶圓的材料熱輸運能力和器件散熱能力得到大?幅度提升?。???高導(dǎo)熱襯底Ga2 O 3 異質(zhì)集成技術(shù)是解決?Ga2O3散熱瓶頸的關(guān)鍵技術(shù)。

2 高導(dǎo)熱Ga2O3異質(zhì)集成功率晶體管?

2.1 ??Ga2O3異質(zhì)集成晶體管

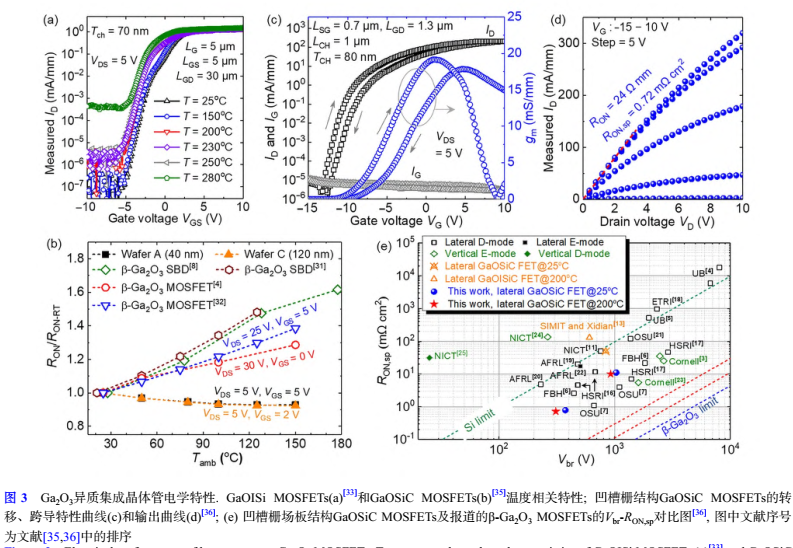

基于材料特性良好的高導(dǎo)熱襯底Ga2O3異質(zhì)集成?晶圓,??西安電子科技大學(xué)和中國科學(xué)院上海微系統(tǒng)與?信息研究所合作團(tuán)隊開發(fā)和制備了高導(dǎo)熱襯底Ga2O3異質(zhì)集成MOSFETs。??相比于報道的Ga2O3襯底上器件,?Si和SiC基Ga2O3異質(zhì)集成晶體管均呈現(xiàn)出更優(yōu)異的?開、關(guān)態(tài)熱穩(wěn)定性。?在工作溫度由室溫上升至250°C時, Si基Ga2O3異質(zhì)集成晶體管的開態(tài)工作電流基本保持?不變,??關(guān)態(tài)泄漏電流上升小于兩個數(shù)量級,???如圖3(a)所示[33] 。

在工作溫度上升過程中, SiC基Ga2O3異質(zhì)集成晶 體管的開、關(guān)態(tài)電流呈現(xiàn)更優(yōu)的相關(guān)性, 圖3(b)中對比 了SiC基Ga2O3異質(zhì)集成晶體管與報道的Ga2O3襯底上 器件的導(dǎo)通電阻隨溫度的變化關(guān)系, 150°C時SiC基 Ga2O3異質(zhì)集成晶體管導(dǎo)通電阻相比于室溫時略有下 降, 而Ga2O3襯底上器件導(dǎo)通電阻均增加12%以上[35] 。

如圖3(c), (d)所示, 采用凹槽柵和場板結(jié)構(gòu)相結(jié)合 制備的SiC基Ga2O3 MOSFETs, 在漏端電壓VDS為5 V的 條件下, 實現(xiàn)了19。15 mS/mm的峰值跨導(dǎo), 開態(tài)電流超 過300 mA/mm, 導(dǎo)通電阻RON僅為24 Ω mm, 對應(yīng)的特 征導(dǎo)通電阻率RON,SP為0。72 mΩ cm2。對比已報道數(shù)據(jù), 制備的凹槽柵場板結(jié)構(gòu)GaOSiC MOSFETs實現(xiàn)了目前 最低特征導(dǎo)通電阻值, 如圖3(e)所示[36]。 通過增加器件 柵漏尺寸, 器件擊穿電壓超過1000 V, 在工作環(huán)境溫度 由25°C增加至200°C時, 其擊穿和輸出特性沒有發(fā)生明 顯的衰退, 如圖3(e)所示[36] 。器件良好的溫度穩(wěn)定性源 于襯底良好的導(dǎo)熱性和絕緣層上薄膜結(jié)構(gòu)有效抑制器件靜態(tài)泄漏電流隨工作環(huán)境溫度的迅速增加。

綜上所述, 高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶體管展現(xiàn) 出遠(yuǎn)優(yōu)于Ga2O3體襯底器件的熱穩(wěn)定性和溫度相關(guān)性, 根據(jù)實驗結(jié)果, 在室溫至250°C的工作溫度范圍內(nèi), 其 呈現(xiàn)出穩(wěn)定的器件電學(xué)特性。

2.2 Ga2O3異質(zhì)集成晶體管遷移率

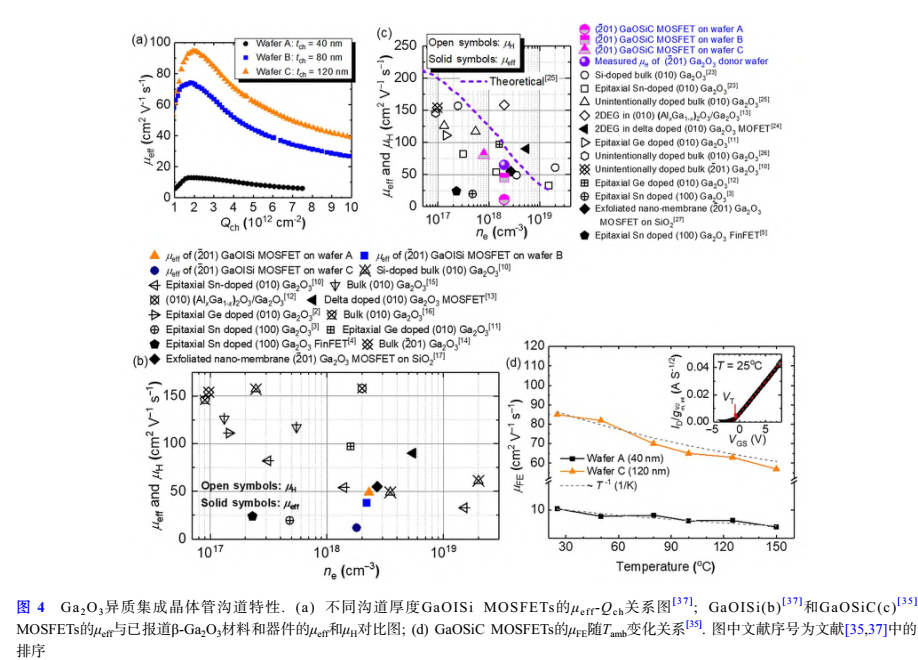

晶體管遷移率反映載流子導(dǎo)電能力的大小, 是晶 體管電學(xué)特性中最為關(guān)鍵的參數(shù)之一。我們對高導(dǎo)熱 襯底Ga2O3異質(zhì)集成晶體管的溝道特性進(jìn)行了深入分 析, 探究了不同溝道厚度和不同激活溫度條件下, Ga2O3異質(zhì)集成溝道有效遷移率μeff的變化規(guī)律以及晶體管場 遷移率的溫度相關(guān)性和作用機(jī)制。

基于Si基Ga2O3 MOSFETs(GaOISi MOSFETs)測試 的柵電容和轉(zhuǎn)移特性曲線, 計算得到不同溝道厚度(tch) 晶體管的μeff隨溝道內(nèi)電荷密度的變化關(guān)系如圖4(a)所 示。隨著溝道厚度減小, 器件的μeff降低, 溝道厚度為 120 nm時(Wafer C), μeff峰值高達(dá)約95 cm2 V- 1 s- 1, 而溝道厚度減少至40 nm時(Wafer A), 其μeff峰值不足 20 cm2 V- 1 s- 1[37] 。

如圖4(b)所示, 對比了Si基Ga2O3MOSFETs的μeff與 報道的同質(zhì)外延β-Ga2O3 、delta摻雜Ga2O3和β-Ga2O3體 材料中的霍爾遷移率μH和(AlGa)2O3/Ga2O3 中二維電子 氣(two dimensional electron gas, 2DEG)遷移率以及同 質(zhì)外延材料制備的β-Ga2O3 MOSFETs中的μeff[37] 。

在相 近的摻雜濃度條件下, 溝道厚度為120 nm的硅基Ga2O3 MOSFETs(Wafer C)的μeff與同質(zhì)外延β-Ga2O3薄膜和體 材料中的μH水平相當(dāng), 證明采用離子注入-鍵合剝離技 術(shù)制備的高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶圓具有與Ga2O3 體材料相當(dāng)?shù)倪w移率特性。基于SiC基Ga2O3 ?MOSFETs (GaOSiC MOSFETs)探究器件μeff與注入激活溫度的關(guān) 系。將提取的器件μeff與報道的遷移率結(jié)果進(jìn)行對比, 如圖4(c)所示, 虛線為考慮各種散射機(jī)制作用的遷移率?隨摻雜濃度變化的理論計算結(jié)果。??

1200°C退火的GaO-SiC ?MOSFET(Wafer ?A)實現(xiàn)μeff約為80。5 cm2 V- 1 ?s- 1,?而1100°C退火(Wafer ?B)器件的μeff與剝離前β-Ga2O3 晶 圓的μH值相近,?表明在1100°C退火后,?剝離和注入產(chǎn)生?的缺陷得到有效恢復(fù),??更高激活溫度將進(jìn)一步提升遷?移率[35]?。

基于SiC基Ga2O3 ?? MOSFETs的變溫轉(zhuǎn)移特性結(jié)合 Y-function,??研究其場遷移率μFE 隨測試溫度Tamb 的變化?關(guān)系,??如圖4(d)所示[35]?。??在Tamb 由25~150°C變化過程中, SiC基Ga2O3 ? MOSFETs的μFE與測試Tamb滿足T 1amb變化?關(guān)系,??隨著Tamb 的升高,??μFE逐漸降低。

??在聲子散射效應(yīng) 起主要影響作用時,??遷移率與溫度遵從T-3/2amb 的規(guī)律?變化,??而當(dāng)雜質(zhì)散射占主導(dǎo)作用時,??變化規(guī)律為T3/2amb,?所以制備的SiC基Ga2O3 晶體管的μFE 隨Tamb 的變化規(guī)律 主要由聲子散射機(jī)制決定,??雜質(zhì)散射對聲子散射起到?一定的補(bǔ)償作用,??在兩者共同作用下,??呈現(xiàn)T- 1amb 的變 化關(guān)系。?結(jié)合相關(guān)特性分析,?上述結(jié)果表明載流子被嚴(yán)格限制在頂層Ga2O3薄膜內(nèi)運動, 呈現(xiàn)電學(xué)上的pn結(jié)限 制效應(yīng), 有利于減小器件泄漏電流。

3 p-NiO/n-Ga2O3異質(zhì)結(jié)超結(jié)晶體管

3.1 異質(zhì)外延集成功率二極管

Ga2O3是一種離子性很強(qiáng)的超寬禁帶半導(dǎo)體材料, 存在p型摻雜困難的關(guān)鍵瓶頸問題[38] 。相比于單極型器 件, 采用p-n結(jié)構(gòu)設(shè)計的雙極型器件具有電導(dǎo)調(diào)制能 力 、雪崩能力和更優(yōu)異的浪涌電流能力, 同時可以通 過降低表面電場(reduced surface electric field, RES- URF)設(shè)計更多的終端結(jié)構(gòu)[2] 。

在p型摻雜難以實現(xiàn)的情況下, 將Ga2O3與其他p型 材料進(jìn)行異質(zhì)集成, 可以為Ga2O3基功率器件設(shè)計提供 新的自由度。目前研究較多的p型材料主要包括SnO 、 CuAlO2家族及NiO等, 其中p-NiO/n-Ga2O3異質(zhì)結(jié)展現(xiàn)出極佳的性能[2]?。??

理想化學(xué)配比的NiO薄膜是一種室溫?絕緣體,?通過增加Ni空位和/或填隙氧原子,?可有效降低 NiO的電阻率,??使之呈現(xiàn)良好的p型導(dǎo)電,??摻Li的NiO薄 膜電導(dǎo)率可降低到~1。4 Ω- 1 cm- 1[39]?。??近年來,??多家研究 單位基于p-NiO/n-Ga2O3異質(zhì)結(jié),??制備出低漏電、高耐?壓的pn異質(zhì)結(jié)二極管(heterojunction ?diode,? HJD)整流?器件,??其擊穿電壓遠(yuǎn)超過未使用終端和場板結(jié)構(gòu)保護(hù)?的SBDs[40~42]?。

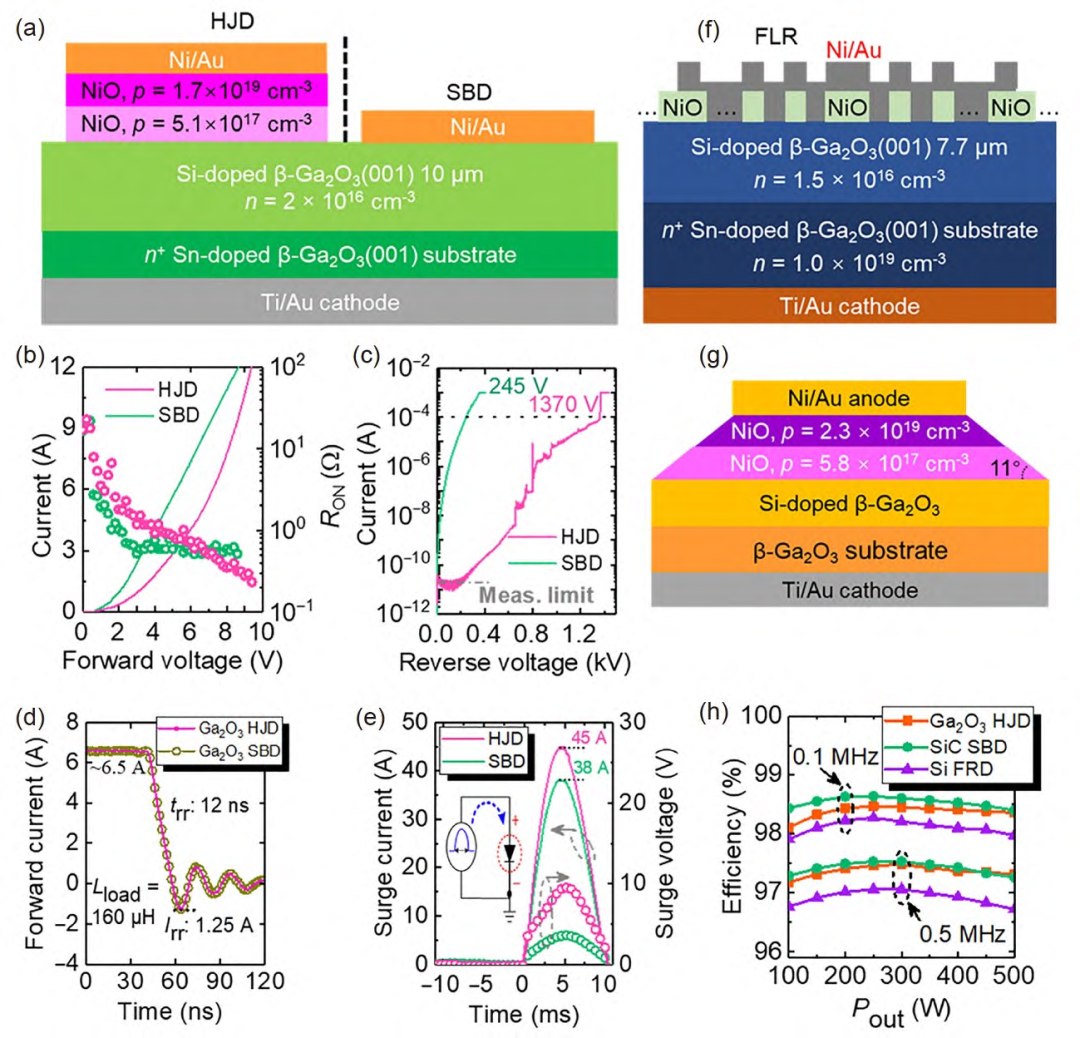

2020年,?南京大學(xué)團(tuán)隊[41]采用雙層NiO結(jié)構(gòu)與Ga2O3 異質(zhì)集成,??實現(xiàn)了器件極低的泄漏電流,??器件在400 K 工作溫度下仍具有高于1010?的開關(guān)比,??同時其擊穿電壓?達(dá)到了1。86 kV。? 2021年,??南京大學(xué)團(tuán)隊[42]進(jìn)一步改善 NiO濺射工藝,?實現(xiàn)了具有1。37 kV/12 A開關(guān)能力的大?面積HJD,?首次在實驗中發(fā)現(xiàn)HJD具有一定的電導(dǎo)調(diào)制?能力,?其導(dǎo)通電阻隨著正向偏壓的增加逐漸減小,?且具?有明顯降低的反向泄漏電流,?? 1 mm×1 mm器件擊穿電

壓達(dá)到1.37 kV,?遠(yuǎn)超Ga2O3 ?SBD的245 V。?在動態(tài)特性方?面,? HJD具有與SBD幾乎相同的反向恢復(fù)時間,??僅為 12 ns; ?同時, HJD具有更優(yōu)異的浪涌電流能力,?在10 ms 的浪涌應(yīng)力持續(xù)時間下, HJD可以承受的峰值浪涌電流?達(dá)到45 A,?超過SBD的38 A,?如圖5(a)~(e)所示。

為了減少HJD的開啟電壓,??南京大學(xué)團(tuán)隊[44]實現(xiàn)?了場限環(huán)結(jié)構(gòu)的異質(zhì)結(jié)勢壘肖特基二極管(junction barrierSchottky, JBS),?結(jié)構(gòu)如圖5(f)所示,?器件同時具有?低開啟和高阻斷能力。??通過引入斜臺面NiO技術(shù),??南京 大學(xué)團(tuán)隊[45]進(jìn)一步實現(xiàn)了擊穿電壓達(dá)到2 kV的大電流?功率HJD,??器件結(jié)構(gòu)如圖5(g)所示。?

?功率轉(zhuǎn)換能力是評?估功率器件的一種簡單有效的方法,??南京大學(xué)團(tuán)隊[44]?構(gòu)建了一個500 W的功率因數(shù)校正(power factor correc- tion, PFC)電路,?在國際上首次采用NiO/Ga2O3 ?HJD實現(xiàn)?了98.5%的功率轉(zhuǎn)換效率,?如圖5(h)所示。

以上研究結(jié)果表明,? p-NiO/n-Ga2O3異質(zhì)結(jié)的優(yōu)異 性能為Ga2O3功率器件結(jié)構(gòu)設(shè)計和實際應(yīng)用空間提供了更多可能性。

3.2 ???Ga2O3超結(jié)晶體管

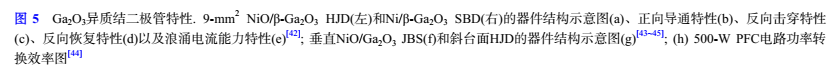

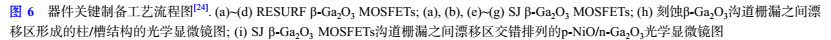

p-NiO/n-Ga2O3異質(zhì)結(jié)展現(xiàn)出良好的電學(xué)特性,??西?安電子科技大學(xué)和南京大學(xué)合作團(tuán)隊基于其設(shè)計?、制?備了表面電場降低和超結(jié)結(jié)構(gòu)β-Ga2O3 ?? MOSFETs,??制 備流程如圖6所示[24]?。

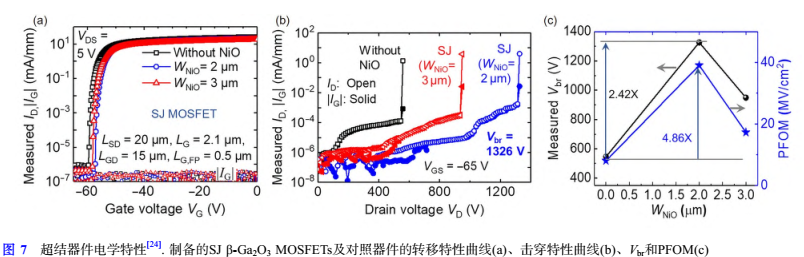

SJ β-Ga2O3 ?MOSFETs展現(xiàn)出與相同結(jié)構(gòu)尺寸常規(guī)?器件相似的轉(zhuǎn)移特性曲線,?如圖7(a)所示。?隨著p-NiO條?寬度增加, SJ β-Ga2O3 MOSFETs相比于對照器件,?開態(tài)?電流略有下降,??導(dǎo)通電阻略有上升[24]?。隨著p-NiO條寬?度的增加,? SJ ?β-Ga2O3 ? MOSFETs的擊穿電壓呈現(xiàn)先增?加后減小的變化趨勢,??在p-NiO條寬度為2 μm時,??實現(xiàn)?了1326 V的高擊穿電壓,而在p-NiO條寬度增加至3 μm 時,?其擊穿電壓發(fā)生退化,?如圖7(b)所示[24]?。?

在p-NiO條?寬度為2 μm時, SJ β-Ga2O3 MOSFET的擊穿電壓相比于?相同結(jié)構(gòu)參數(shù)的常規(guī)器件獲得了2.42倍提升,?對應(yīng)于功率品質(zhì)因子(power figure of merit, PFOM)實現(xiàn)4。86倍的?提升,?如圖7(c)所示[24]?。?隨著尺寸的增加,?由于SJ結(jié)構(gòu)對?器件的抑制影響,??其擊穿電壓和功率品質(zhì)因子均發(fā)生?退化,??表明p-NiO條寬度在0~3 μm之間存在最優(yōu)尺寸,?使得擊穿電壓達(dá)到最大值。??

同時,??隨著擊穿電壓和導(dǎo)通?電阻的權(quán)衡,?存在一個最優(yōu)尺寸使得SJ β-Ga2O3 ?MOS- FETs的綜合性能最優(yōu)。?根據(jù)理論分析,?該值可能更靠近?于0 μm區(qū)域,???即交錯的p-NiO/n-Ga2O3條以納米尺度交?錯排列?、相互實現(xiàn)全耗盡,??可實現(xiàn)更優(yōu)的擊穿電壓和?功率品質(zhì)因子;?而在相互全耗盡尺寸下,?結(jié)合其內(nèi)載流?子濃度值變化實現(xiàn)理想的電荷平衡狀態(tài),??則可以實現(xiàn)?最優(yōu)的擊穿電壓和功率品質(zhì)因子,??但平衡狀態(tài)對器件設(shè)計、制備等均具有一定的挑戰(zhàn)性。

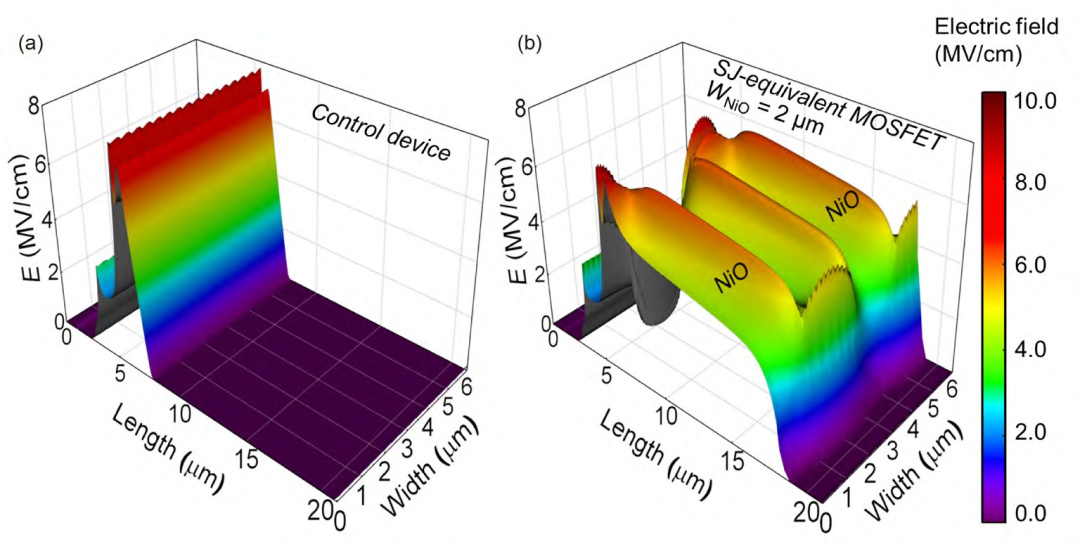

擊穿電壓的顯著提升源于超結(jié)結(jié)構(gòu)對晶體管漂移?區(qū)電場的重構(gòu)作用。SJ結(jié)構(gòu)器件將常規(guī)MOSFET器件?三角形電場分布向漏端平滑,?轉(zhuǎn)變?yōu)榫匦坞妶龇植迹?效抑制了漂移區(qū)邊緣峰值電壓的上升速度,??進(jìn)而增加?了器件的擊穿能力,?對應(yīng)器件電場仿真結(jié)果如圖8所?示[21]?。

綜上所述,??基于p-NiO/n-Ga2O3異質(zhì)結(jié)設(shè)計的雙極?型二極管和超結(jié)結(jié)構(gòu)Ga2O3 ?? MOSFETs均展現(xiàn)了良好?的電學(xué)特性,??其為Ga2O3缺少p型材料的難題提供了一?個有效的解決方案,??進(jìn)一步拓寬了Ga2O3器件的應(yīng)用?廣度。

4 總? 結(jié)?

本文介紹的高導(dǎo)熱襯底異質(zhì)集成晶體管和超結(jié)晶?體管兩類Ga2O3功率晶體管均為我國創(chuàng)新實現(xiàn)。??利用離?子注入-鍵合剝離工藝實現(xiàn)的高導(dǎo)熱襯底Ga2O3異質(zhì)集?成晶圓和器件是解決Ga2O3低導(dǎo)熱瓶頸的有效方法。??實?驗證明, SiC基Ga2O3 晶圓熱導(dǎo)率達(dá)到9。0 W/mK,?界面熱?阻為7。5 m2 ?K/GW,?其熱擴(kuò)散速率接近于SiC晶圓,?遠(yuǎn)優(yōu)?于Ga2 O3 晶圓; ??同時制備的Ga2 O3 異質(zhì)集成晶體管在 250°C仍保持著極佳的熱穩(wěn)定性,??開關(guān)態(tài)特性退化小于?兩個數(shù)量級,??器件綜合性能達(dá)到Ga2O3器件主流水準(zhǔn)。

?超結(jié)晶體管是唯一已被證明可以突破功率半導(dǎo)體擊穿?極限的器件結(jié)構(gòu),???由于p-Ga2O3 的缺少而不易實現(xiàn)。???

相?關(guān)研究創(chuàng)新性地利用p-NiO/n-Ga2O3異質(zhì)結(jié)實現(xiàn)了超結(jié) 結(jié)構(gòu)Ga2O3 ?? MOSFETs,??器件的擊穿電壓相比于同步制?備的相同結(jié)構(gòu)參數(shù)常規(guī)器件獲得了2。42倍提升,??對應(yīng)于功率品質(zhì)因子實現(xiàn)4。86倍的提升。

隨著p-NiO外延技術(shù)的不斷成熟以及p-NiO/n - Ga2O3異質(zhì)結(jié)研究的深入,??在p型Ga2O3摻雜難以實現(xiàn)的?現(xiàn)狀下, p-NiO/n-Ga2O3異質(zhì)結(jié)必將是高性能Ga2O3器件?的有效解決方案。???

目前高導(dǎo)熱襯底Ga2O3異質(zhì)集成晶體?管性能已經(jīng)逐步接近Ga2O3體襯底器件的主流水平,??隨?著對其注入激活工藝?、歐姆接觸工藝?、溝道界面處理 工藝等的開發(fā)以及復(fù)合場板結(jié)構(gòu)?、浮空柵結(jié)構(gòu)等設(shè)計?的深入研究,??將進(jìn)一步提升高導(dǎo)熱襯底Ga2O3異質(zhì)集成?晶體管器件性能,??特別是與p-NiO/n-Ga2O3異質(zhì)結(jié)的結(jié)?合,???開發(fā)實現(xiàn)高導(dǎo)熱襯底Ga2O3異質(zhì)集成超結(jié)晶體管,?將有望實現(xiàn)器件性能突破材料極限且熱導(dǎo)性能極佳的 Ga2O3功率器件。?高導(dǎo)熱襯底Ga2O3異質(zhì)集成和p-NiO/n- Ga2O3異質(zhì)外延技術(shù)將有效推動Ga2O3功率晶體管的發(fā)?展,?助力其在功率、射頻等領(lǐng)域的實用化進(jìn)程。

??

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評論