1.什么是鎖相環(huán)

鎖相環(huán)是一種利用相位同步產(chǎn)生電壓,去調(diào)諧壓控振蕩器以產(chǎn)生目標(biāo)頻率的負(fù)反饋控制系統(tǒng)。

鎖相環(huán)就是通過負(fù)反饋控制系統(tǒng),讓壓控振蕩器的固有振蕩頻率fo 和輸入的參考信號fi 的相位保持在誤差允許范圍內(nèi),從而讓振蕩頻率fo達(dá)到和參考信號fi 同步相位頻率的目的。一般來說,參考信號fi 的信號特性更好,通過鎖相系統(tǒng)提高振蕩頻率fo的信號特性,同時(shí)還可以將參考信號fi 轉(zhuǎn)化為你想要的任意(最好整數(shù)倍)頻率信號。

2.工作原理

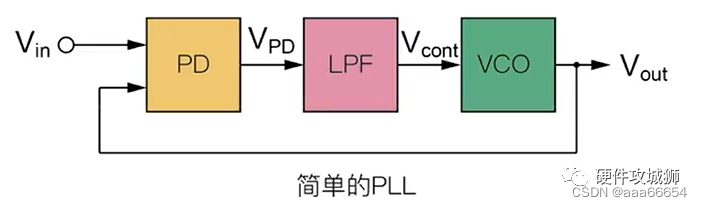

最基礎(chǔ)的鎖相環(huán)系統(tǒng)主要包含三個(gè)基本模塊:鑒相器(Phase Detector:PD)、環(huán)路濾波器(L00P Filter:LF)其實(shí)也就是低通濾波器,和壓控振蕩器(Voltage Controlled Oscillator:VCO)。有了這三個(gè)模塊的話,最基本的鎖相環(huán)就可以運(yùn)行了。但我們實(shí)際使用過程中,鎖相環(huán)系統(tǒng)還會(huì)加一些分頻器、倍頻器、混頻器等模塊。(這一點(diǎn)可以類比STM32的最小系統(tǒng)和我們實(shí)際使用STM32的開發(fā)板)

圖1 鎖相環(huán)基本模塊

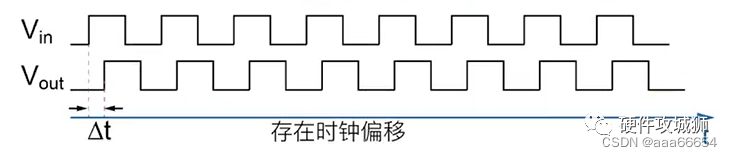

圖2 輸入信號和輸出信號存在相位差

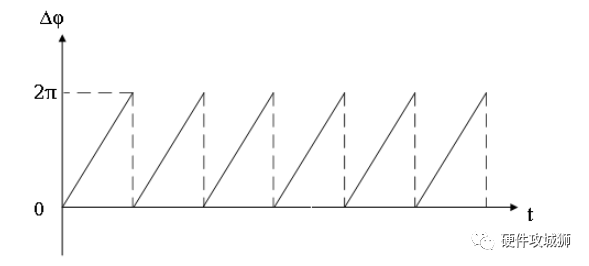

從鎖相系統(tǒng)開始運(yùn)行的那一刻進(jìn)行分析,這個(gè)時(shí)候鑒相器有兩個(gè)輸入信號,一個(gè)是輸入的參考信號Vin,另一個(gè)是壓控振蕩器的固有振蕩信號Vout。這個(gè)時(shí)候由于兩個(gè)信號的頻率不相同,會(huì)因?yàn)轭l差而產(chǎn)生相位差,如果不對壓控振蕩器進(jìn)行任何操作,那么相位差會(huì)不斷累積,從而跨越2Π角度,從零重新開始測相位,如圖3所示。這便是測量死區(qū),明明相位在不斷變大,但鑒相器只能測出0~2Π的范圍,測出的相位差最大便是2Π,這樣就導(dǎo)致了鑒相器的輸出電壓只能在一定的范圍內(nèi)波動(dòng)。理想狀態(tài)是讓這兩個(gè)信號的相位差一直保持在2Π的范圍內(nèi),不進(jìn)入測量死區(qū)。那么在系統(tǒng)剛開始的時(shí)候,鑒相器測出兩個(gè)信號的相位差,將相位差時(shí)間信號轉(zhuǎn)化為誤差電壓信號輸出(具體轉(zhuǎn)化過程見鑒相器講解)。通過環(huán)路濾波器轉(zhuǎn)化為壓控電壓加到壓控振蕩器上,使壓控振蕩器的輸出頻率Vout逐步同步于輸入信號Vin,直到兩個(gè)信號的頻率逐漸同步,相位差也在測量誤差范圍內(nèi),那么整個(gè)系統(tǒng)就穩(wěn)定下來了。兩個(gè)信號的相位差不會(huì)累積變大,而是保持相對固定的相位差。(不是常規(guī)意義上的固定不變,而是在誤差允許范圍內(nèi)的微小波動(dòng))。

圖3 相位規(guī)律變化

3.鑒相器(PD)

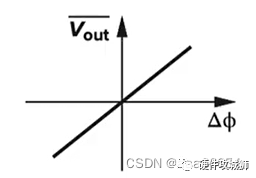

鑒相器的作用就是將相位差信號轉(zhuǎn)化為誤差電壓信號。那么它的傳遞關(guān)系理想上是圖4所示,最好有一定的線性關(guān)系。

圖4 鑒相器傳遞關(guān)系圖

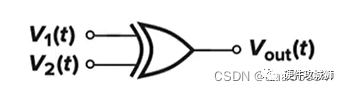

那么鑒相器可以鑒別兩個(gè)信號的相位差,它是如何實(shí)現(xiàn)的?其實(shí)很簡單,異或門就可以實(shí)現(xiàn),如圖5,6所示。鑒相器的輸入端是兩個(gè)信號,只要兩個(gè)信號異或不為零,就說明有相位差,異或出來的信號就是含有它們相位差信息的電壓信號。

圖5 異或門構(gòu)成的鑒相器

圖6 鑒相器鑒相過程

實(shí)際使用的鑒相器不是簡單的異或門,有非時(shí)鐘PD、預(yù)充電PD等多種形式,

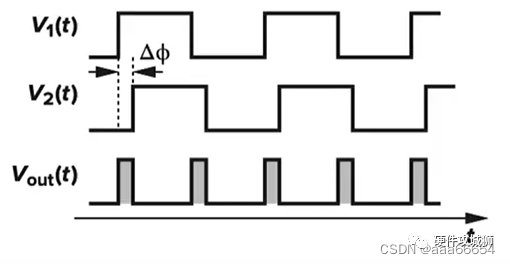

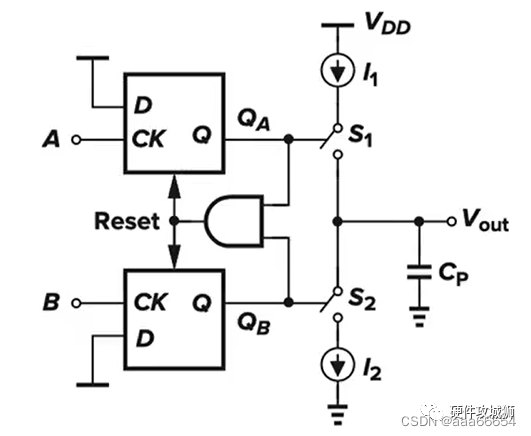

一款鎖相芯片AD9517,這款芯片是帶電荷泵的鑒相鑒頻器,如圖7所示。為什么使用的是鑒相鑒頻器呢?是因?yàn)镻LL剛開始工作的時(shí)候,它的VCO的工作頻率可能和輸入頻率偏差很大,僅僅檢查相位偏差,捕獲范圍較小,PLL需要很長的時(shí)間才能進(jìn)入鎖定狀態(tài)。所以為了提高PLL的響應(yīng)速度,提高捕獲范圍,使用鑒相鑒頻器。

圖7 帶電荷泵的鑒相鑒頻器

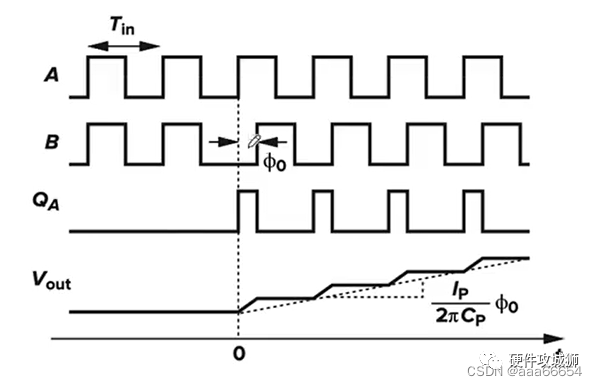

兩個(gè)D觸發(fā)器的D端都是接電源端,當(dāng)A信號相位超前于B信號,那么它的高電平先到來,則A的D觸發(fā)器輸出高電平,S1開關(guān)閉合,上面電荷泵開始灌電流。當(dāng)B信號高電平到來,則B的D觸發(fā)器輸出高電平,而QA和QB一旦同時(shí)為高,則中間的與門就會(huì)輸出高電平,就會(huì)使兩個(gè)D觸發(fā)器復(fù)位,從而都輸出低電平,兩個(gè)門都處于斷開狀態(tài)。同理,當(dāng)B信號相位超前于A信號,那么它的高電平先到來,則B的D觸發(fā)器輸出高電平,S2開關(guān)閉合,下面電荷泵開始拉電流。當(dāng)A的信號高電平到來,則A的D觸發(fā)器輸出高電平,而QA和QB一旦同時(shí)為高,則中間的與門就會(huì)輸出高電平,就會(huì)使兩個(gè)D觸發(fā)器復(fù)位,從而都輸出低電平,兩個(gè)門都處于斷開狀態(tài)。(一般中間的與門和RESET端中間會(huì)加DELAY電路,這樣是為了避免實(shí)際使用中兩個(gè)信號都出現(xiàn)高電平,而由于電路的延時(shí)不確定性,導(dǎo)致到復(fù)位端的電平不確定而形成毛刺干擾的問題)

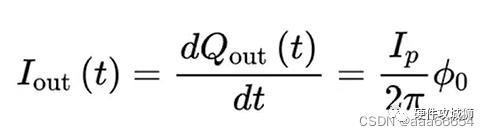

這樣就把相位差信號通過電荷泵充電時(shí)間長短,轉(zhuǎn)化電流的大小,這里簡單的推一下它的線性模型。如圖8所示。由相位差

圖8 線性模型

則相位差對應(yīng)的時(shí)間為

-----相位差除以2π圓,可以知道相位差的占比,然后乘T,可知對應(yīng)的時(shí)間

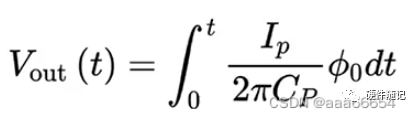

那么在這段時(shí)間內(nèi)輸出電壓增加(恒流充放電的常用公式:⊿Vc=I*⊿t/C,其出自公式:Vc=Q/C=I*t/C)

基于此我們可以計(jì)算出(Vc=Q/C)

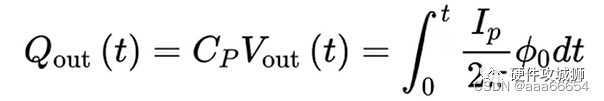

那么輸出的電荷表示為

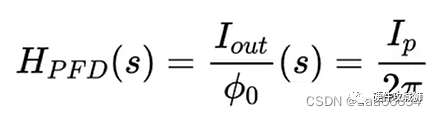

有了電荷,我們就可以計(jì)算輸出電流,我們可以看到這是一個(gè)相位差和輸出電流的關(guān)系式,鑒相鑒頻器就可以看作是一個(gè)相位差為輸入,電荷泵輸出電流為輸出的器件,我們就可以計(jì)算出該傳輸函數(shù)為

這個(gè)值我們也可以看作是鑒相鑒頻器的增益。那么鑒相鑒頻器就介紹到這里了,總的來說,鑒相鑒頻器就是將相位差數(shù)據(jù)轉(zhuǎn)化為了和它有線性關(guān)系的輸出電流。但壓控振蕩器是受電壓變化來改變輸出頻率的,所以還需要在鑒相鑒頻器和壓控振蕩器之間加一個(gè)環(huán)路濾波器,將電流信號轉(zhuǎn)化為電壓信號,同時(shí)還可以濾除鑒相鑒頻器中電荷泵的開關(guān)打開關(guān)閉所帶來的紋波噪聲以及毛刺,讓壓控電壓更加平滑。

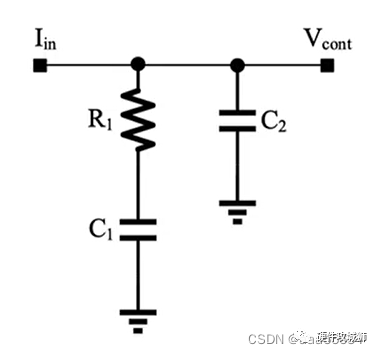

4.環(huán)路濾波器(LF)

為了提升系統(tǒng)穩(wěn)定性和減小輸出控制電壓的紋波,會(huì)在鑒相鑒頻器后加一個(gè)環(huán)路濾波器。一階的環(huán)路濾波器只是一個(gè)電容,見圖7的Cp,一階的易使整個(gè)系統(tǒng)不穩(wěn)定,現(xiàn)在基本看不到了,這里詳細(xì)介紹二階環(huán)路濾波器。

圖9 二階環(huán)路濾波器

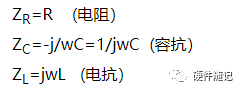

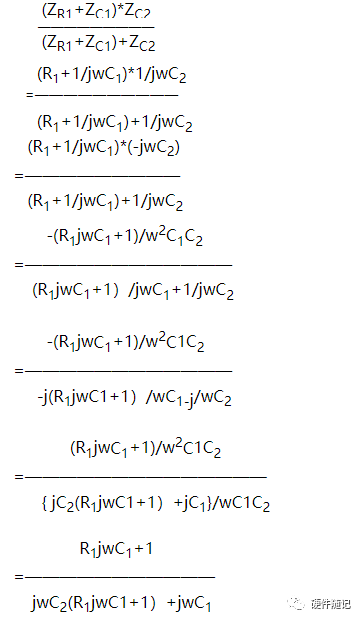

這里詳細(xì)推導(dǎo)一下它的傳遞關(guān)系式,電阻電容電感的阻抗計(jì)算為:

那么根據(jù)這個(gè)我們計(jì)算出它的傳遞函數(shù)

二階環(huán)路濾波器傳遞關(guān)系式推導(dǎo):

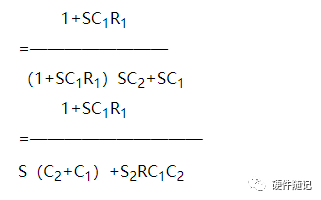

令函數(shù)S=jw,則得到如下傳遞函數(shù):

5.壓控振蕩器(VCO)

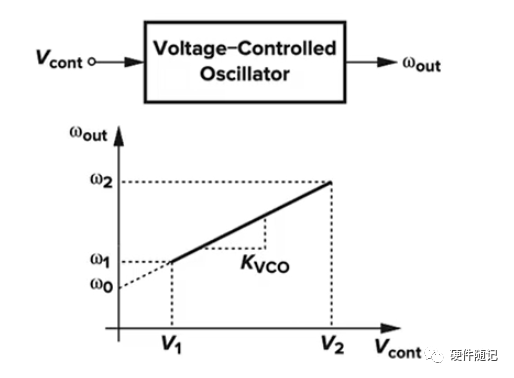

壓控振蕩器是一個(gè)受壓控電壓控制改變輸出頻率的器件,有一個(gè)參數(shù)為壓控靈敏度,就是壓控電壓和輸出頻率的轉(zhuǎn)換系數(shù)。

我們現(xiàn)在使用的都是現(xiàn)成做好的振蕩器,所以不用考慮起振條件這些。但想要自己搭一個(gè)振蕩器,還是要學(xué)好多東西,我只知道起振條件為輸出反饋到輸入的相位差為360°,且增益大于1(必要條件)。這兒就不班門弄斧了。

我詳細(xì)介紹一下VCO的傳遞函數(shù),傳輸模型如圖12所示,輸入為壓控電壓,輸出為頻率,它們之間存在關(guān)系式wout=w0+KvcoVcont,

Kvco為壓控靈敏度,也可以看作是VCO的增益。

圖12 VCO傳輸模型

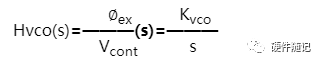

壓控振蕩器輸出的是頻率,鑒頻鑒相器輸入的是相位差,還需要將輸出頻率轉(zhuǎn)化為相位。對于一個(gè)交流信號,其相位變化的速度即為頻率,因此

所以VCO輸出信號的相位為?out=∫woutdt+?0=w0+Kvco∫Vcont+?0???。我們關(guān)注的參數(shù)是盈出相位?ex=Kvco∫Vcontdt這是受壓控 電壓控制的,是我們可以調(diào)整的相位。那這樣的話,VCO就可以看作是一個(gè)輸入為壓控電壓Vcont,輸出為盈出相位的系統(tǒng),是一個(gè)理想的積分器,它的傳輸函數(shù)為

到這兒的話,鎖相環(huán)的三個(gè)基本元件都介紹完了,傳遞函數(shù)也都推導(dǎo)完了。那既然這三個(gè)傳遞函數(shù)都有了,那整個(gè)鎖相環(huán)的傳遞函數(shù)我們也就可以推導(dǎo)出來了。

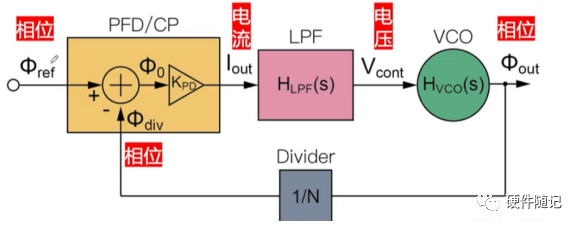

6.鎖相環(huán)線性模型傳輸函數(shù)

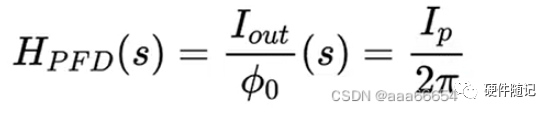

鑒相鑒頻器的傳輸函數(shù)

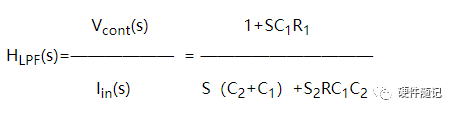

環(huán)路濾波器的傳輸函數(shù)

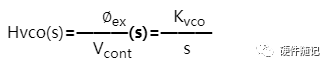

壓控振蕩器的傳輸函數(shù)

AD9517芯片,在基礎(chǔ)的模型上還加入了分頻模塊,這樣的鎖相環(huán)的線性模型為圖13所示。

圖13 鎖相環(huán)模型

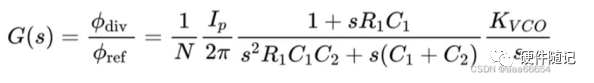

這樣的話,PLL的環(huán)路增益?zhèn)鬏敽瘮?shù)為

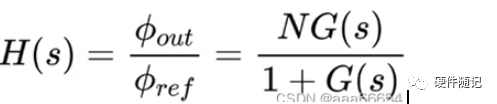

PLL系統(tǒng)的閉環(huán)傳輸函數(shù)為

學(xué)過自動(dòng)控制的同學(xué)是不是看到這里就覺得比較親切了。既然是環(huán)路控制的話,少不了要分析PLL整個(gè)系統(tǒng)是否穩(wěn)定,要計(jì)算伯德圖,要計(jì)算整個(gè)系統(tǒng)的相位裕度,要對系統(tǒng)的零點(diǎn)和極點(diǎn)分析,它直接影響了整個(gè)環(huán)路是否穩(wěn)定。這就是為什么現(xiàn)在環(huán)路濾波器基本不用一階的,最起碼都是二階的,就是因?yàn)榧尤肓艘粋€(gè)極點(diǎn)和一個(gè)零點(diǎn),增加了相位裕度,讓整個(gè)環(huán)路愈加穩(wěn)定了。三階的話比二階再多一個(gè)極點(diǎn)和一個(gè)零點(diǎn),更加有利于系統(tǒng)的穩(wěn)定性,還可以適當(dāng)?shù)奶岣逷LL的響應(yīng)速度。繼續(xù)分析的話會(huì)更加復(fù)雜,篇幅更長,所以這里就不介紹了,總結(jié)介紹一種簡單的辦法,直接計(jì)算出電阻電容的值。

環(huán)路濾波器電阻電容值的計(jì)算,我推薦使用ADI公司的SimPLL、SimCLK這兩個(gè)軟件直接計(jì)算,會(huì)根據(jù)你的設(shè)計(jì)要求,直接計(jì)算出電阻電容的值,好的工具也可以使我們節(jié)省很多時(shí)間。

以上是PLL的簡單理解。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論