近日,美國加州大學(xué)圣塔芭芭,美國IBM研究實(shí)驗(yàn)室,法國格勒諾布爾大學(xué),中國臺(tái)灣臺(tái)機(jī)公司,日本東京大學(xué) ,韓國三星先進(jìn)技術(shù)研究院和美國英特爾公司的研究人員在《Nature》雜志發(fā)表了一篇題為“The future transistors”的論文。 ?

研究內(nèi)容

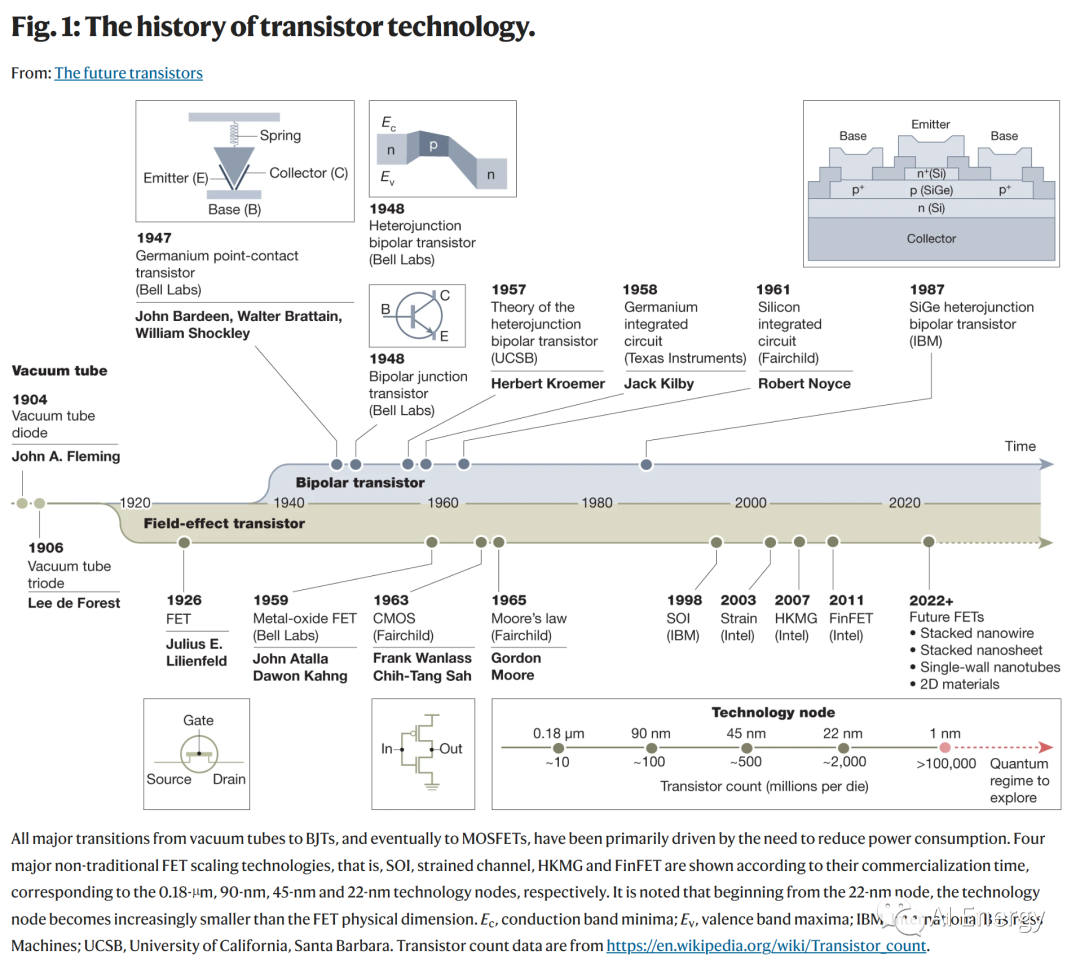

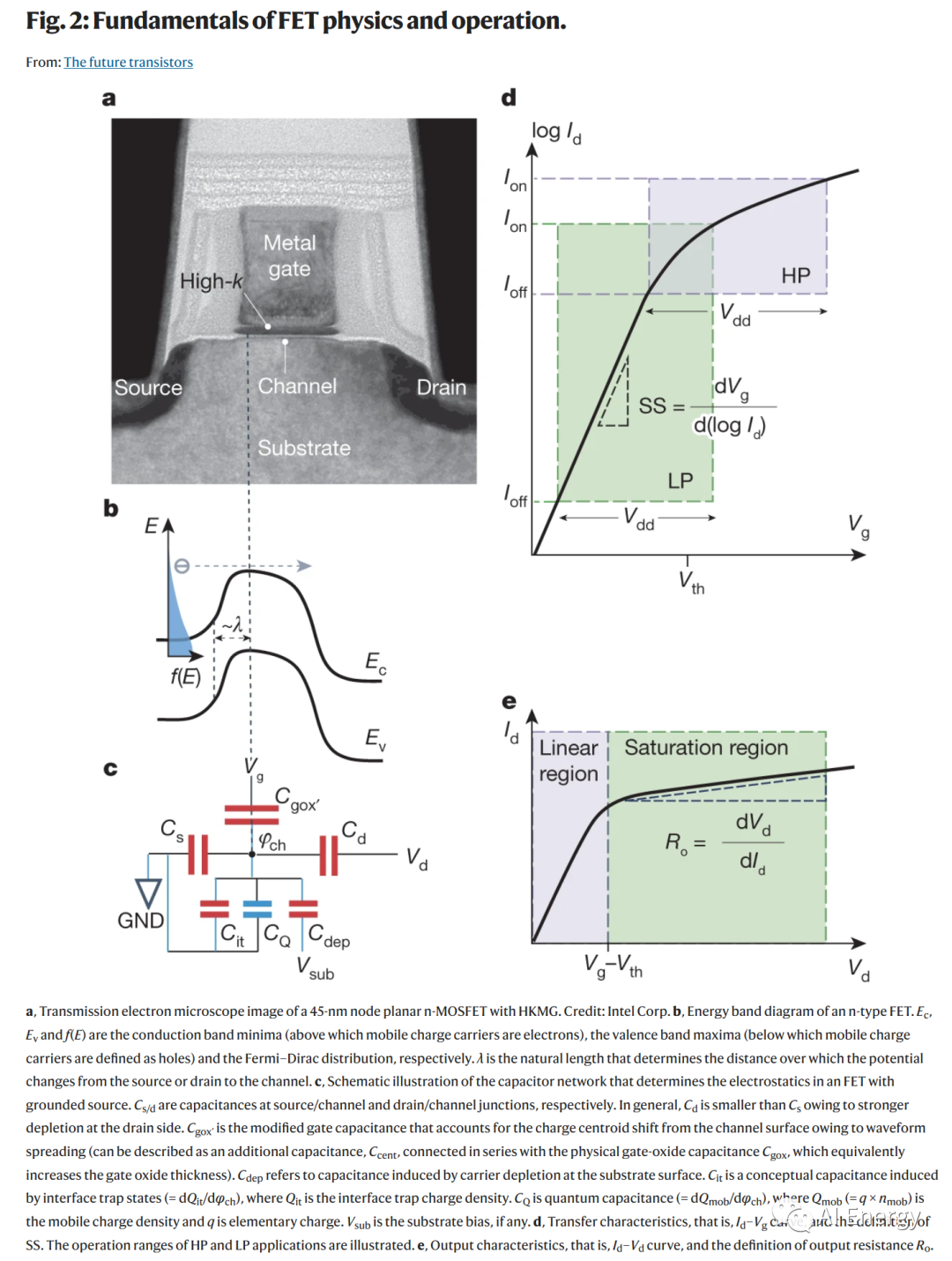

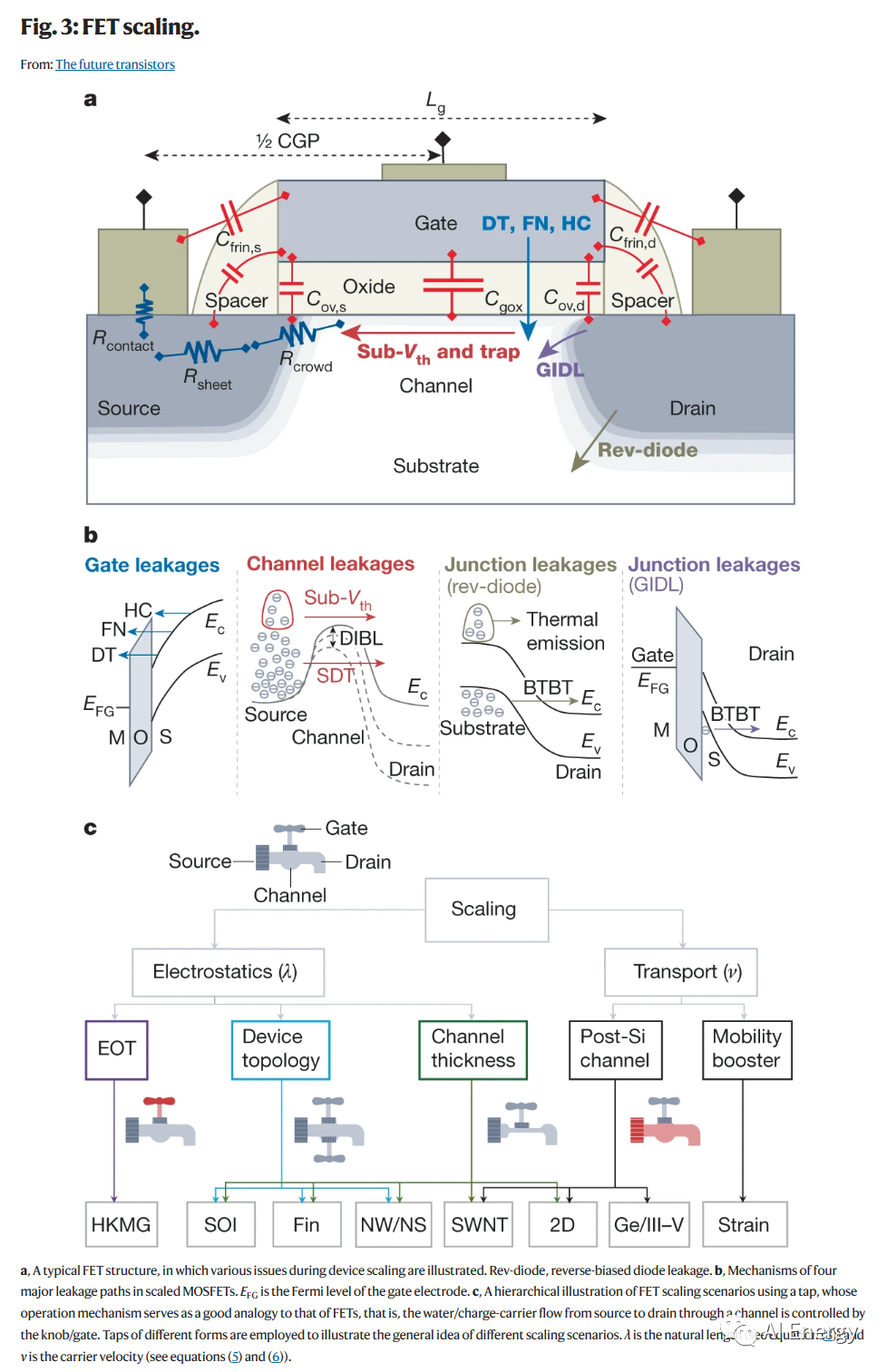

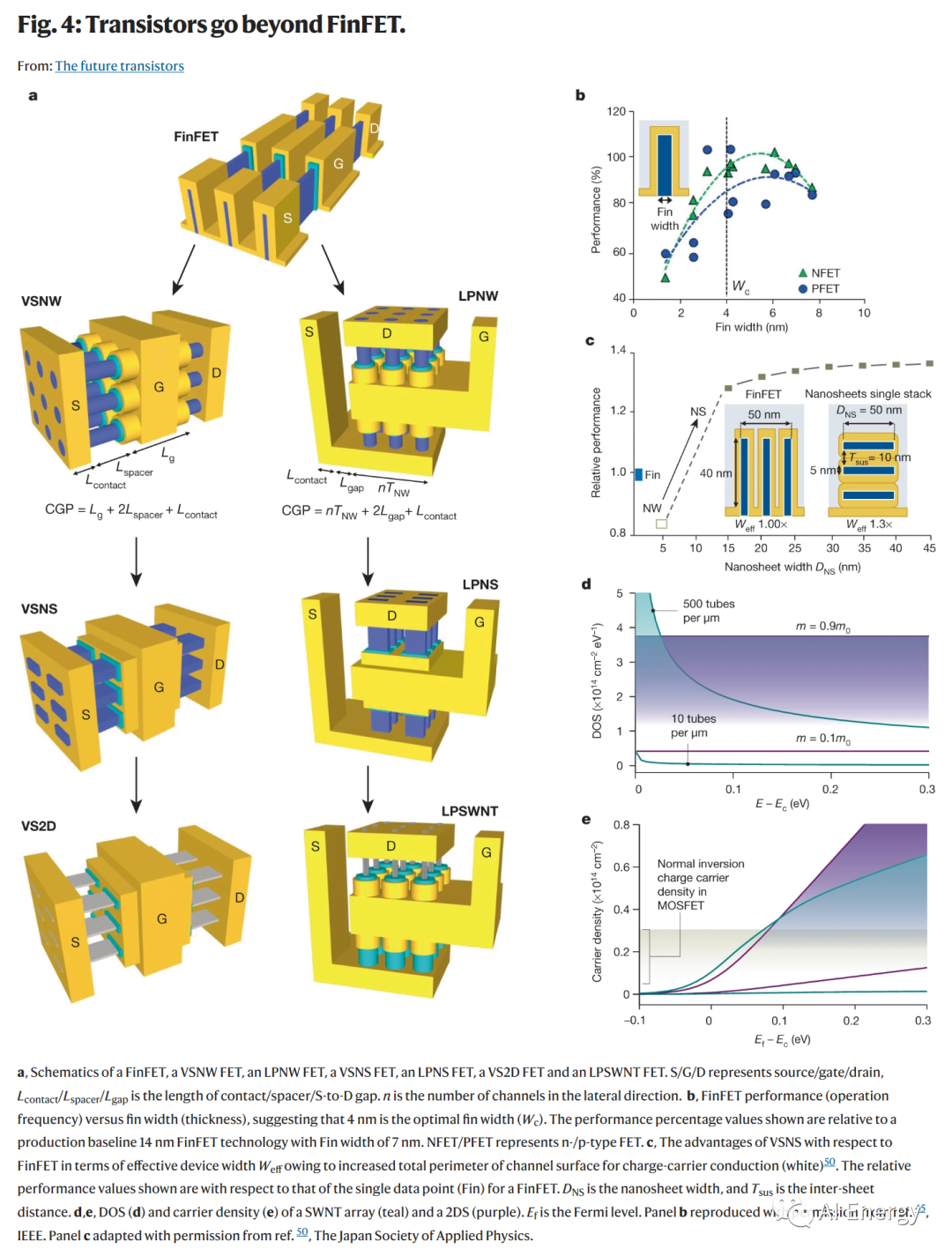

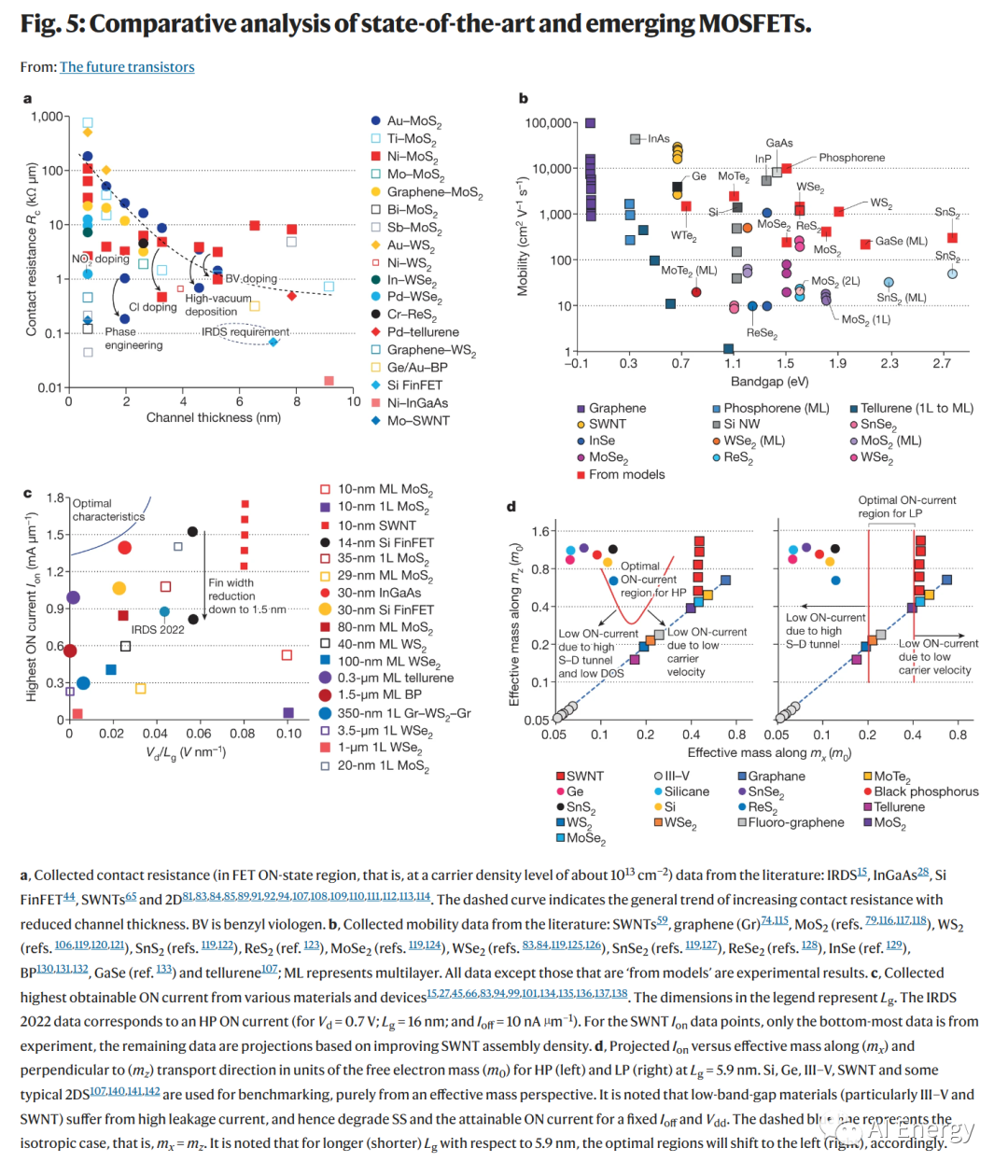

金屬氧化物半導(dǎo)體場效應(yīng)晶體管(Metal–Oxide–Semiconductor Field-Effect Transistor,MOSFET)是互補(bǔ)金屬氧化物半導(dǎo)體(Complementary Metal–Oxide–Semiconductor,CMOS)技術(shù)的核心元件,是工業(yè)革命以來最重要的發(fā)明之一。在集成電路產(chǎn)品對更高的速度、能效和集成密度要求的推動(dòng)下,過去六十年來,MOSFET的物理柵極長度已縮小到20納米以下。然而,即使是最先進(jìn)的鰭式場效應(yīng)晶體管,在保持低功耗的同時(shí)縮小晶體管尺寸也越來越具有挑戰(zhàn)性。本文對現(xiàn)有和未來的CMOS技術(shù)進(jìn)行了全面評估,并根據(jù)為場效應(yīng)晶體管縮放而建立的分層框架,討論了設(shè)計(jì)柵極長度低于10納米的場效應(yīng)晶體管所面臨的挑戰(zhàn)和機(jī)遇。本文的評估重點(diǎn)是根據(jù)以往擴(kuò)展工作中獲得的知識,確定最有前途的10納米以下柵極長度MOSFET,以及使晶體管適用于未來邏輯集成電路產(chǎn)品所需的研究工作。此外還詳細(xì)介紹了對未來超越MOSFET晶體管和潛在創(chuàng)新機(jī)會(huì)的展望。預(yù)計(jì)晶體管技術(shù)的創(chuàng)新將繼續(xù)在推動(dòng)未來材料、器件物理和拓?fù)洹悩?gòu)縱向和橫向集成以及計(jì)算技術(shù)方面發(fā)揮核心作用。

展望

超越MOSFET 的未來 “跨-電阻”

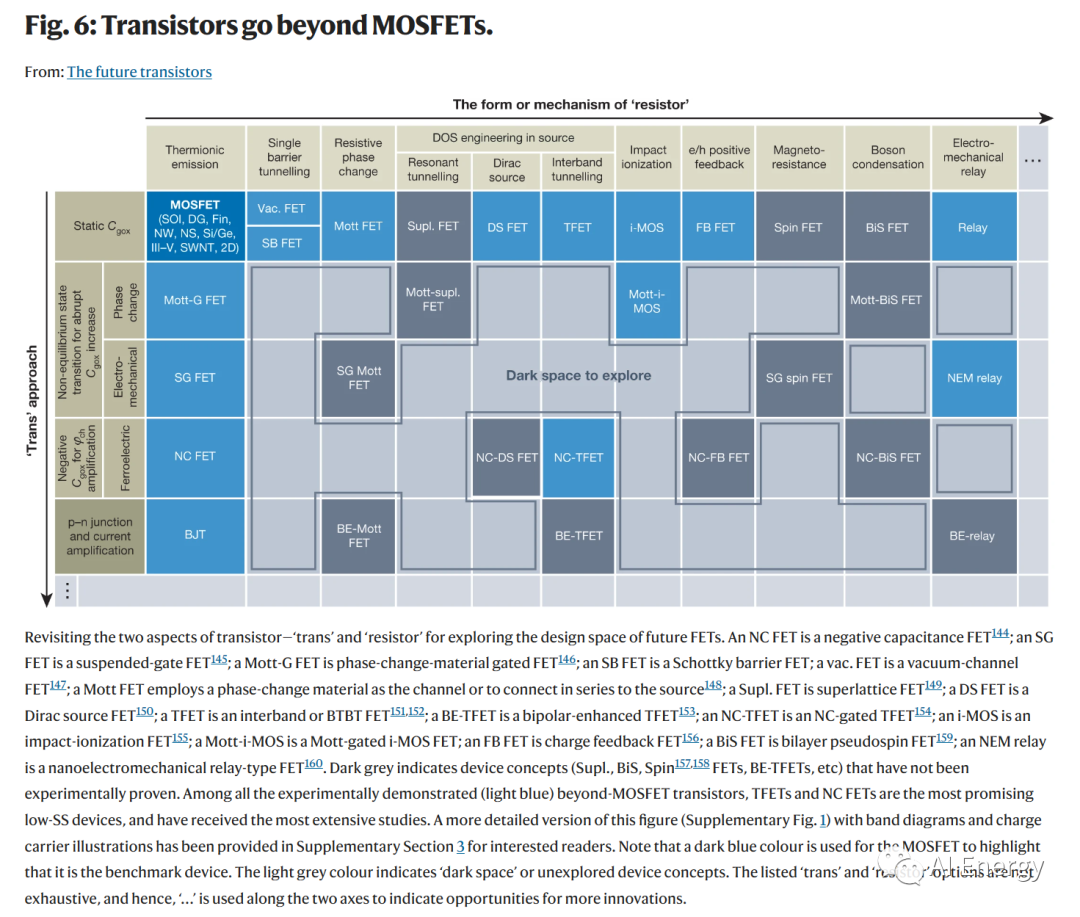

MOSFET受其工作機(jī)制的限制,因此功耗和能效無法與器件尺寸同步增長。CMOS界一直在尋找 "超越 MOSFET "的晶體管,以打破這一能效瓶頸。在這種情況下,回顧一下晶體管的基本方面--"trans"(源于 "傳輸 "或調(diào)制)和 "resistor"(源于溝道電阻)--是很有啟發(fā)性的。因此,"晶體管 "捕捉到的是操縱信息狀態(tài)或載體的方法,也就是 "電阻"。對于商業(yè)化的 MOSFET 和 BJT,"跨 "分別是通過靜態(tài)柵電容和 p-n 結(jié)勢壘調(diào)制的電場效應(yīng)實(shí)現(xiàn)的,而 "阻 "則是通過這兩種器件在勢壘上的熱釋電形式實(shí)現(xiàn)的。為了在這兩個(gè)方面中的一個(gè)(或兩個(gè))方面進(jìn)行創(chuàng)新,人們做出了許多努力。

負(fù)電容 (NC)、懸浮柵 (SG)?和莫特相變材料門控 (Mott-G)場效應(yīng)晶體管(圖 6)等各種 "反式 "方法已被提出并進(jìn)行了實(shí)驗(yàn)探索。NC FETs利用鐵電材料的負(fù)電容狀態(tài)來構(gòu)建負(fù)Cgox,目的是克服柵極效率的統(tǒng)一上限。SG和 Mott-G FETs 在柵極堆棧中分別引入了納米機(jī)電開關(guān)和絕緣體-金屬相變存儲(chǔ)單元,并利用其非平衡態(tài)開關(guān)瞬態(tài)來實(shí)現(xiàn) Cgox的突然增加(相對于柵極電壓),從而轉(zhuǎn)化為電荷密度和漏極電流的突然增加,即超小型 SS。值得一提的是,NEM 開關(guān)和相變存儲(chǔ)單元的存儲(chǔ)特性不可避免地會(huì)在傳輸特性中產(chǎn)生存儲(chǔ)效應(yīng),即滯后,這就限制了 SG 和 Mott-G FETs 在存儲(chǔ)方面的應(yīng)用。 相比之下,"電阻 "已在許多超越熱釋電的形式和機(jī)制中得以實(shí)現(xiàn)。

在肖特基勢壘和真空場效應(yīng)晶體管中,電荷載流子分別通過金屬源和半導(dǎo)體或真空溝道之間的肖特基勢壘隧穿。莫特場效應(yīng)晶體管采用與源極串聯(lián)的相變存儲(chǔ)單元,以實(shí)現(xiàn) "電阻器 "電阻的突變,從而在存儲(chǔ)狀態(tài)切換時(shí)改變漏極電流,這也在I-V曲線中引入了滯后。超晶格場效應(yīng)晶體管在源區(qū)采用多量子阱,形成一個(gè)人造共振隧穿帶,該帶足夠窄,可過濾高能量(相對于費(fèi)米級)載流子的熱離子發(fā)射。狄拉克源 FETs利用向石墨烯源狄拉克點(diǎn)遞減的DOS來減少高能載流子注入。這種器件可實(shí)現(xiàn)的最小SS值仍大于30 mV dec-1,原因很簡單,因?yàn)槭┦菬o間隙的,也就是說,雖然狄拉克點(diǎn)附近的 DOS 值較低,但仍允許高能載流子泄漏。隧穿場效應(yīng)晶體管(TFET)、利用源的帶隙過濾高能載流子的熱離子發(fā)射。

然而,低帶對帶隧穿概率限制了其導(dǎo)通電流。雙極增強(qiáng)型TFET(BE-TFET)已被提出,通過利用BJT的大電流增益放大漏極電流來緩解這一問題。要證明這一器件概念,還需要實(shí)驗(yàn)論證。之前的一項(xiàng)研究在TFET上采用了鐵電柵極(預(yù)計(jì)將起到NC的作用),結(jié)果發(fā)現(xiàn)TFET的性能得到了增強(qiáng)。至于這種增強(qiáng)是由于 NC 效應(yīng)還是僅僅由于鐵電材料的高 k 值,還需要進(jìn)一步研究。從本質(zhì)上講,超晶格場效應(yīng)晶體管、狄拉克源場效應(yīng)晶體管和TFET具有類似的 "電阻 "形式,因?yàn)樗鼈兌际腔谠粗械腄OS工程來實(shí)現(xiàn)費(fèi)米級附近的局部載流子注入。沖擊電離MOSFET(i-MOS)在沖擊電離過程中利用電子-空穴對的超指數(shù)生成(相對于柵極電壓)來實(shí)現(xiàn)漏極電流的超指數(shù)增長。

然而,激活撞擊電離過程需要較大的Vd,因此無助于降低電源電壓。在反饋型場效應(yīng)晶體管中,有意在n型源極和p型漏極附近分別引入電子和空穴電位勢壘,以形成電子-空穴再分布和勢壘調(diào)制之間的正反饋回路,從而動(dòng)態(tài)加快電子-空穴注入速率。該器件還需要較大的Vd值來激活反饋回路。 與上述基于電荷載流子的場效應(yīng)晶體管相比,自旋場效應(yīng)晶體管采用自旋作為信息載流子,并以磁阻的形式實(shí)現(xiàn) "電阻"。值得注意的是,這里的自旋場效應(yīng)晶體管指的是Rashba型,在這種晶體管中,自旋方向在從源極向漏極傳輸?shù)倪^程中由一個(gè)小的柵極電場操縱。遺憾的是,在實(shí)驗(yàn)中很難控制自旋方向,這使得自旋場效應(yīng)晶體管至今未能得到實(shí)驗(yàn)證明。在雙層偽自旋(BiS)場效應(yīng)晶體管中,據(jù)預(yù)測,電子-空穴對(玻色子)在分隔電子-空穴雙層的絕緣體中的凝聚可顯著降低層間電阻,從而實(shí)現(xiàn)電導(dǎo)的突然增加。不過,要驗(yàn)證雙玻色場效應(yīng)晶體管的器件概念,還需要進(jìn)行實(shí)驗(yàn)論證。與SG FET相比,NEM繼電器 在溝道/漏極交界處采用了NEM開關(guān),以實(shí)現(xiàn)溝道和漏極之間的物理接觸和分離。

這種機(jī)械開關(guān)存在嚴(yán)重的滯后可靠性問題,尤其是對超大規(guī)模器件而言。如圖6所示,LP器件設(shè)計(jì)人員仍有很大的黑暗空間需要探索。值得注意的是,要實(shí)現(xiàn)這些未來晶體管,明智地選擇材料平臺(tái)將起到至關(guān)重要的作用。例如,二維材料的原始表面可用于開發(fā)超深斜率TFETs,而傳統(tǒng)的塊狀材料很難實(shí)現(xiàn)這一點(diǎn)。 自2007-2008年提出NC FET的概念以來,由于其便于制造的結(jié)構(gòu)(補(bǔ)圖2a的下半部分),NC FET迅速崛起,成為一個(gè)引人注目的概念,它基本上是一個(gè)MOSFET,在氧化物和柵極之間插入了一個(gè)額外的NC(通常是鐵電材料,F(xiàn)E)層。在FE存儲(chǔ)器應(yīng)用中,F(xiàn)E的雙穩(wěn)態(tài)被用來存儲(chǔ)二進(jìn)制信息,與此相比,NC FET被認(rèn)為是利用FE層的瞬態(tài),即NC,對外部電場提供負(fù)極化響應(yīng),從而更好地(<1)實(shí)現(xiàn)MOSFET的統(tǒng)一柵極效率(等式 (1))。如補(bǔ)充圖2c所示,迄今為止,已有許多聲稱具有低SS的 "NC FET",其直流I-V曲線測量滯后相對較小。

然而,根據(jù)數(shù)控場效應(yīng)晶體管的基本器件物理原理,由于現(xiàn)代場效應(yīng)晶體管的量子電容普遍較大,且靜電性能極佳,因此最近發(fā)現(xiàn)?數(shù)控場效應(yīng)晶體管無滯后、低于60 SS的設(shè)計(jì)空間非常小。換句話說,這些測得的小SS值無法用靜態(tài)NC解釋來解釋。事實(shí)上,越來越多的研究表明,它們可歸因于測量過程中的瞬態(tài)效應(yīng)和/或 FE 極化動(dòng)態(tài)。最近的一項(xiàng)研究?發(fā)現(xiàn),在FE層和柵極氧化層之間存在超高的陷阱密度(1014 cm-2)。因此,捕獲和去捕獲動(dòng)態(tài)(不可控)可能是報(bào)告中 "NC FETs "陡坡的另一種解釋。此外,電子器件中的高陷阱密度通常伴隨著可靠性問題。因此,在CMOS產(chǎn)品中應(yīng)用NC之前,需要開展大量的研究工作來解決這些問題,并深入了解FE與氧化物之間的相互作用。

超越摩爾的集成途徑

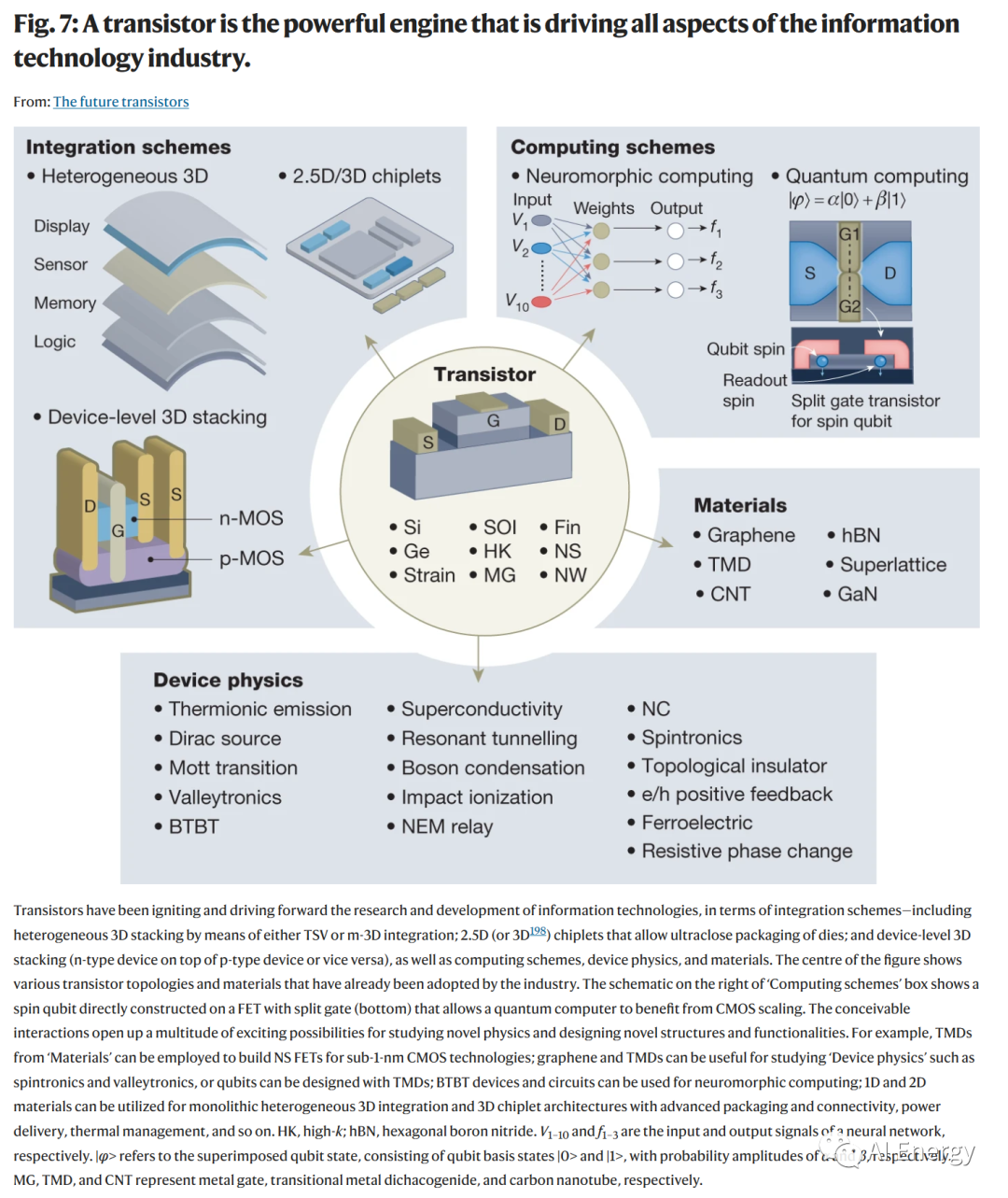

在CMOS技術(shù)發(fā)展史上,大部分努力都是為了縮小MOSFET的特征尺寸,優(yōu)化邏輯芯片的平面面積利用率,包括遵循摩爾定律的 "2.5D "芯片封裝技術(shù)。有一天,我們不難發(fā)現(xiàn),由于制造難度和成本以及功率密度的限制,MOSFET物理尺寸的縮小和器件集成密度的平面內(nèi)增加已經(jīng)停止。在這方面,邏輯芯片的垂直物理空間尚未得到充分利用。雖然FinFET以及NW和 NS FET可被視為這種努力的一種類型,但它們只有利于改善器件電流和靜電,而無助于將器件集成密度提高到一定程度以上。在垂直空間堆疊器件(通常以互補(bǔ)方式)或裸片的三維集成被認(rèn)為是提高器件密度的實(shí)用方法。三維集成電路除了具有密度擴(kuò)展的優(yōu)勢外,還能顯著降低互連延遲和功率耗散。三維集成可通過不同途徑實(shí)現(xiàn),包括基于線鍵合和/或倒裝芯片的三維封裝、基于硅通孔(TSV)的三維裸片/晶圓堆疊以及單片三維集成(m-3D)。

在這三種方法中,m-3D是最理想的方法,因?yàn)樗哂休^大的層密度和較高的局部連接設(shè)計(jì)可能性。雖然m-3D存在熱預(yù)算和散熱問題,但在克服這些挑戰(zhàn)方面已取得了進(jìn)展,例如采用固相外延再生長技術(shù)在600 °C以下激活摻雜劑、利用功率傳輸網(wǎng)絡(luò)冷卻3D集成電路以及采用高熱傳導(dǎo)六方氮化硼層間介質(zhì)。三維集成是一種包容性技術(shù)。最終,它可以發(fā)展為異構(gòu)三維集成的形式,在這種形式中,不同材料(如2DS和硅)、器件和功能的非常不同的系統(tǒng)可以沿垂直和橫向集成在一起,從而構(gòu)建一個(gè)超強(qiáng)、高能效的片上系統(tǒng)和異構(gòu)芯片系統(tǒng)或芯片組(圖 7)。盡管如此,器件和電路架構(gòu),如最近展示的0.5T0.5R混合電阻式隨機(jī)存取存儲(chǔ)器?,不僅可以實(shí)現(xiàn) "內(nèi)存 "計(jì)算等計(jì)算模式,而且專門設(shè)計(jì)用于同時(shí)提供更高的橫向和縱向堆疊密度,仍然是三維集成電路設(shè)計(jì)革命性進(jìn)步的重中之重。

超越馮-諾依曼計(jì)算

信息技術(shù)從未停止過發(fā)展。除了為通用高性能計(jì)算而設(shè)計(jì)的經(jīng)典計(jì)算機(jī)外,神經(jīng)形態(tài)計(jì)算和量子計(jì)算也在積極發(fā)展之中,有望在某些領(lǐng)域(如化學(xué)反應(yīng)模擬、人工智能和機(jī)器學(xué)習(xí))帶來前所未有的優(yōu)勢。如圖 7 所示,所有這些領(lǐng)域的共同要求是晶體管具有超高的緊湊性和超低的漏電率,以及高電流驅(qū)動(dòng)能力、堅(jiān)固性和能效,晶體管可以是核心元件,也可以是輔助元件或接口元件。鑒于這些理想特性,我們有理由認(rèn)為,晶體管的擴(kuò)展和演進(jìn)永遠(yuǎn)不會(huì)停滯,摩爾定律將在可預(yù)見的未來長期存在。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論