根據所使用的硬件,可以使用定點方法或浮點方法來實現校準方程。另一種方法是使用包含集成校準功能的ADC,因為在精密ADC中可能會找到不同類型的校準功能,即:

- 自校準

- 系統校準

- 背景校準

在本文中,我們將探討自校準功能。

ADC 校準選項

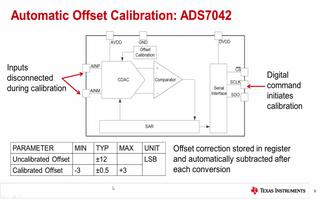

一些ADC支持校準模式,這可以簡化設計,幫助我們從系統處理器中節省一些中央處理單元(CPU)周期。在這種情況下,你只需要調整ADC設置,發送適當的校準命令,并等待ADC確定失調和增益誤差。

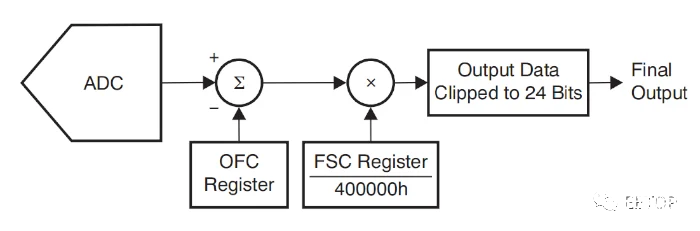

然后,ADC將校準信息存儲在片內寄存器中,并用它來校正后續讀數的失調和增益誤差。圖 1 顯示了德州儀器 (TI)?ADS1246?的示例校準框圖。

圖1. ?ADS1246 框圖顯示校準塊示例。圖片由TI提供

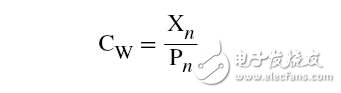

在圖1中,失調寄存器(OFC)和滿量程寄存器(FSC)包含適當的校準值。從A/D(模數轉換)轉換過程產生的數字值中減去OFC的值,結果乘以FSC除以400000h。

例如,當FSC = 800000h時,A/D轉換結果將乘以2,因為FSC值在代碼400000h處歸一化為1.0。ADS1246的校準功能可以用以下公式描述:

啟動校準后,ADC自動設置OFC和FSC寄存器的值。但是,使用ADS1246,用戶可以直接將一些值寫入這些寄存器,從而使用戶能夠更好地控制校準功能。

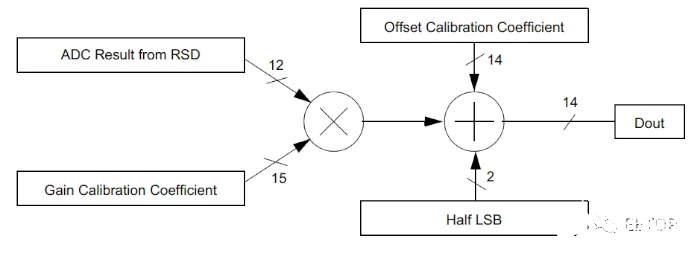

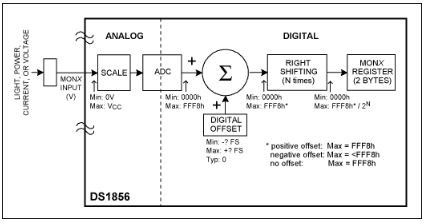

請注意,雖然大多數ADC首先減去失調校準系數,然后將其乘以增益誤差系數,但也有些ADC是首先調整傳遞函數的斜率,然后校正失調誤差。例如,恩智浦MPC5500系列中的ADC使用乘法累加單元來實現校準功能(圖2)。

圖2. MPC5500系列框圖。圖片由恩智浦提供

顯然,對于給定的系統,圖1和圖2中描述的兩種方法將具有不同的增益和失調校準系數。

通常,校準過程實際上包括對已知輸入電壓執行的一個或兩個ADC轉換。ADC使用這些轉換的結果來確定輸入-輸出特性曲線的失調和斜率,并相應地更新其校準寄存器。

模數轉換器自校準或內部校準

自校準(有時稱為內部校準)試圖表征和補償ADC內部模塊的失調和增益誤差。例如,對于集成PGA(可編程增益放大器)的Δσ(ΔΣ)ADC,自校準可消除PGA和ΔΣ調制器的直流誤差。對于AD7124-4等某些ADC,自校準功能可以執行失調(零電平)和增益(滿量程)校準。但是,對于AD7172-2等其他ADC,自校準程序僅執行失調校準。

ADC 內部失調校準

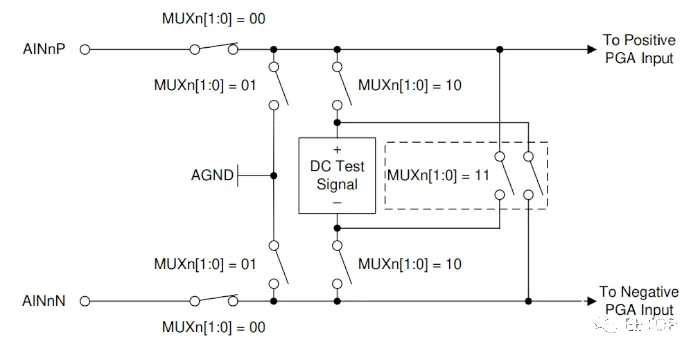

對于內部失調校準,所選ADC通道的輸入在內部短路。此外,將輸出編碼與理想值進行比較,以確定失調誤差。對于大多數ADC,例如ADS1260-Q1,集成了輸入多路復用器,用于斷開輸入與外界的連接,并在內部將其連接到公共電壓以執行失調校準。ADS131M06的輸入多路復用器比ADS1260-Q1的輸入多路復用器相對簡單,如圖3所示。

圖3.顯示 ADS131M06 輸入多路復用器。圖片由TI提供

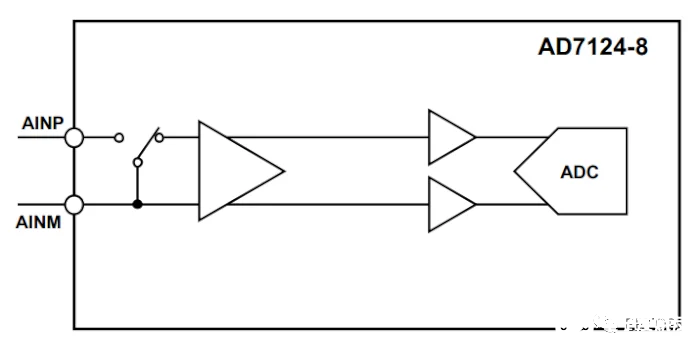

如您所見,其中一個多路復用器配置 MUXn[1:0] = 01 將兩個輸入都短路到地。此多路復用器配置可用于失調校準。另一方面,一些ADC僅斷開其中一個輸入與外部電路的連接。例如,考慮AD7124-4的內部連接,如圖4所示。

在失調校準期間,兩個輸入一起短路。但是,負輸入仍連接到外部電路。因此,器件數據手冊建議設計人員確保在失調校準期間負輸入端不存在任何多余的噪聲和干擾。此外,在執行校準時,該輸入的電壓不允許超過額定限值。

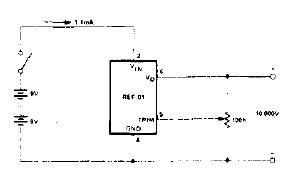

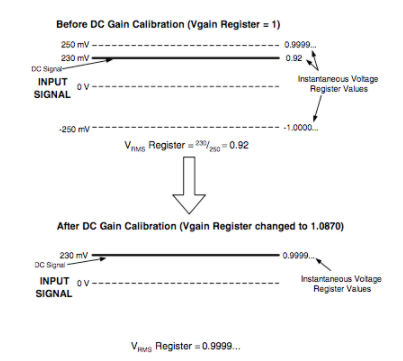

ADC 內部滿量程校準

滿量程校準通常通過向ADC輸入施加內部生成的滿量程電壓來執行。如果ADC的輸入范圍為±V裁判,輸入在內部連接到 +V裁判和 -V裁判線。知道輸入處于滿量程電平后,ADC可以確定所需的增益校準系數。如果ADC具有集成PGA,則內部產生的電壓通常是ADC的基準電壓除以PGA的選定增益,以避免ADC過量程。這允許器件在每個增益設置下支持內部滿量程校準。

具有校準功能的ADC通常重復一定次數(例如16次)的零電平和滿量程測量,并平均轉換結果以計算校準值。對數據求平均值可降低轉換噪聲并提高校準精度。

ADC自校準的有效性

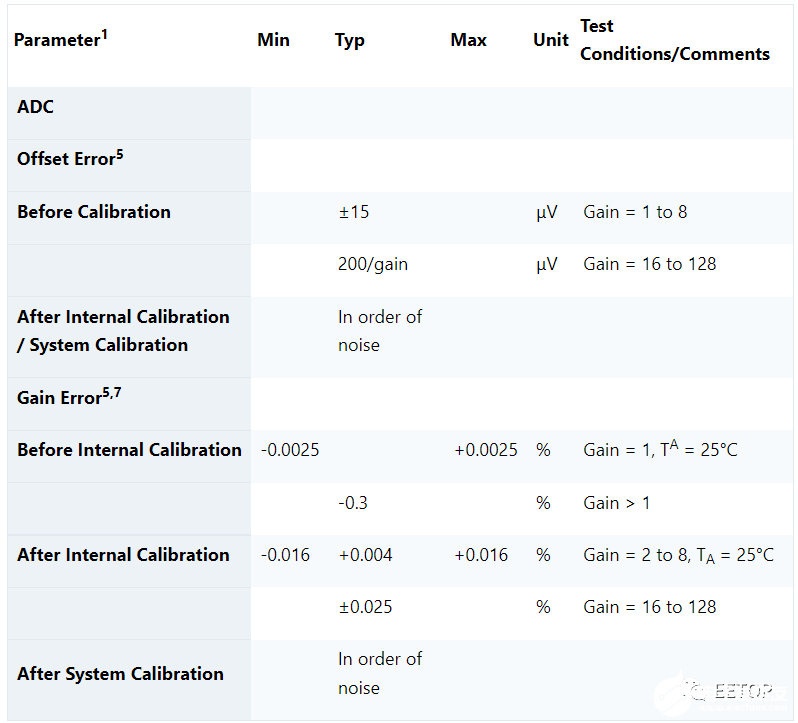

下表1摘自AD7124-4數據手冊。

表 1.使用的數據由ADI公司提供

在應用失調校準之前,ADC失調為±15 μV。但是,失調校準后,失調誤差按噪聲順序排列,根據器件數據手冊,噪聲小于400 nV RMS。同樣,增益校準可顯著降低ADC的增益誤差。

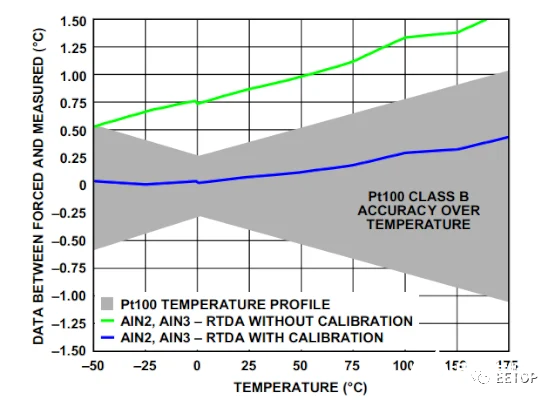

圖5比較了采用和不采用ADC校準的RTD測量系統的誤差。本例中使用的ADC為AD7124-8。

圖5. 使用AD7124-8的RTD測量系統示例。圖片由ADI公司提供

如果不進行校準,測量誤差超出 Pt100 RTD 的預期曲線。但是,在25°C時一次性校準ADC失調和增益誤差會導致誤差在預期范圍內。請注意,在本例中,未消除外部電路元件產生的失調和增益誤差。如需全面了解校準對常見RTD配置的影響,請參考ADI公司的參考設計。

如圖5和上述ADI參考設計的結果所示,許多應用只需消除ADC失調和增益誤差即可滿足設計目標。然而,對于要求更高的應用,我們可能需要系統校準來消除ADC和外部電路的失調和增益誤差。

讓我們快速瀏覽一下RTD應用示例,以了解外部電路的誤差有多大。

計算ADC誤差--系統校準如何有效?

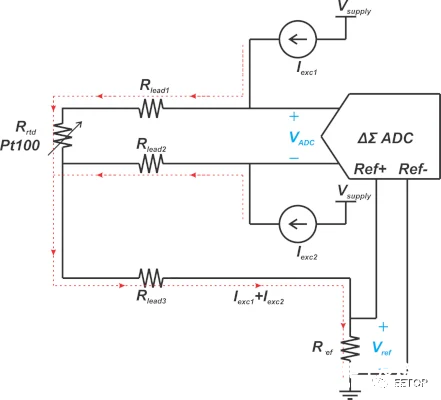

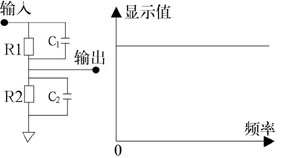

考慮圖6中的3線、比率式RTD測量系統。

圖6.示例 3 線比率式 RTD 測量系統。

假設激勵電流(?Iexc1和?Iexc2) 為 0.5 mA,基準電阻為 R裁判= 1.6 kΩ,產生1.6 V基準電壓。本電路的主要誤差源包括:

DC失調和增益誤差

ADC 積分非線性 (INL)

基準電阻的容差

匹配?Iexc1和?Iexc2

假設激勵電流完全匹配或使用電流交換技術;因此,當前的失配誤差可以忽略不計。這給我們留下了一個主要的外部誤差源:R裁判寬容。

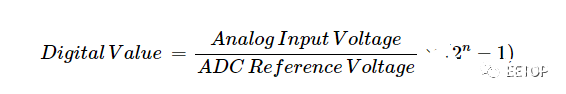

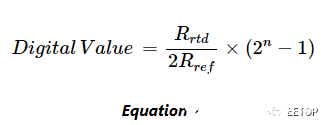

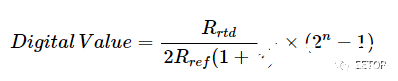

讓我們看看這個誤差有多嚴重。使用上述比率電路,n位ADC產生的數字輸出通常可以用以下公式描述:

假設?Iexc1=?Iexc2,上述等式簡化為等式 1:

假設Rref的實際值與理想值略有不同,由:

Rref,m=Rref(1+α)

其中α是一個很小的值。將Rref,m代入方程1,得到:

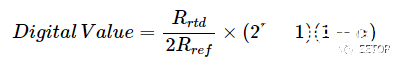

使用泰勒級數分析,我們可以將/(1+α) 近似為1- α。因此,我們獲得:

將其與公式1中的理想關系進行比較,我們觀察到R中的小誤差裁判導致傳遞函數斜率出現相同的誤差。如果我們使用0.1%的基準電阻(α = 0.001),系統的實際增益將與其理想值相差0.1%,這意味著由于R,我們的增益誤差為0.1%。裁判寬容。該增益誤差可與ADC增益誤差相當,具體取決于您選擇的ADC。

例如,如果不進行校準,ADS1260-Q1的最大增益誤差為0.6%。因此,在要求苛刻的應用中,系統校準可以顯著提高精度。要了解有關 RTD 應用中誤差源的更多信息,請參閱 TI 的此參考設計。在下一篇文章中,我們將繼續討論,并探討精密ADC中的系統校準和背景校準模式。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論