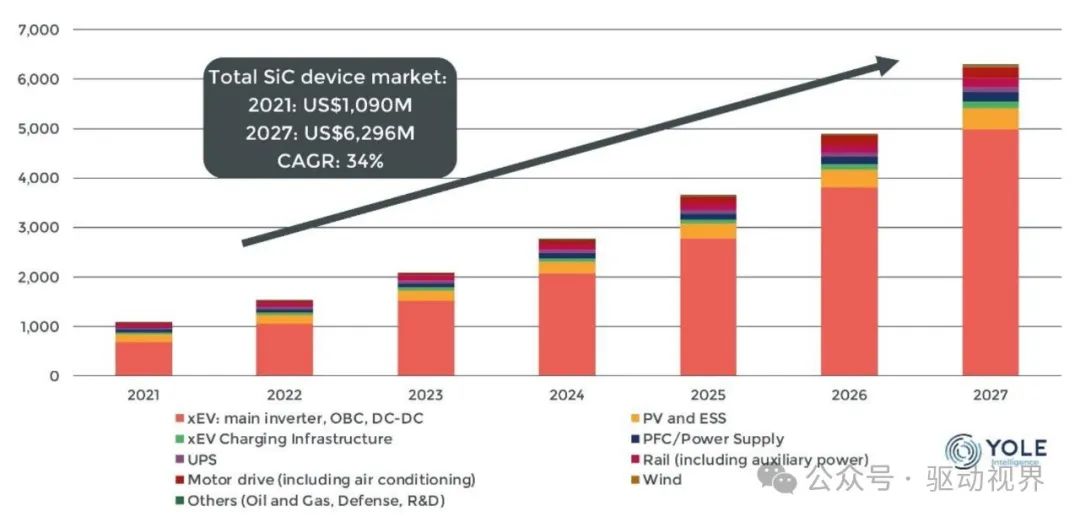

1、市場

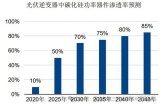

隨著新能源汽車、光伏、充電樁等應(yīng)用對系統(tǒng)效率的不斷追求,功率半導(dǎo)體市場將迎來前所未有的增速。

SiC功率器件市場規(guī)模:

▲Source:Power SiC report,Yole intelligence,2022

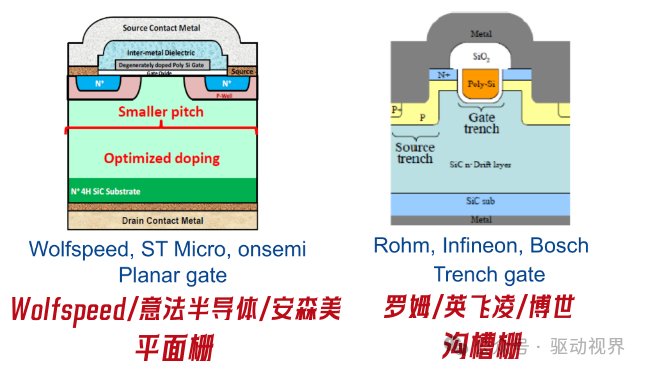

SiC市場格局仍由海外巨頭主導(dǎo),市占率排名依次是:意法半導(dǎo)體、英飛凌、wolfspeed、羅姆、安森美、三菱電機等。

特斯拉是業(yè)界首個在電動汽車逆變器中采用SiC的車企,2018年,特斯拉在model 3中首次將IGBT換成SiC。

2、分類和應(yīng)用

導(dǎo)電型SiC目前主要應(yīng)用于逆變器中,用于制造功率器件。逆變器將電池的直流電轉(zhuǎn)化為電機所用的交流電,在傳統(tǒng)Si基IGBT逆變器中,利用方波電源控制IGBT的開關(guān),使得原來的直流電輸出方波高壓電,經(jīng)過整形后形成正弦電壓,即交流電。

由于輸出電壓和輸出頻率可以任意控制,所以逆變器廣泛用于控制交流電機和無刷電機。

半絕緣型襯底主要用于制造氮化鎵射頻器件等,通過在半絕緣型SiC襯底上生長氮化鎵外延層,制得碳化硅基氮化鎵外延片。

3、原理和優(yōu)勢

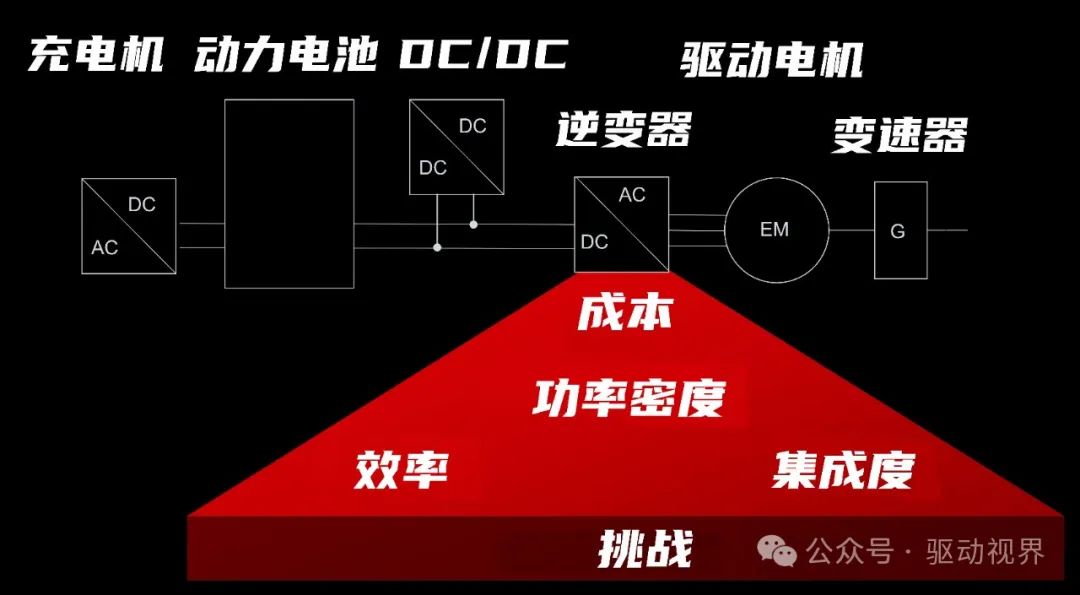

▲電驅(qū)動主要部件和挑戰(zhàn) 電動汽車驅(qū)動用模塊(Power Module for EV)的特點:

(1)布置空間受限(Limited);

(2)溫度變化大(-40℃~105℃);

(3)振動劇烈(Tough);

(4)可靠性要求高(Higher);

(5)通常為水冷(體積小)(Water);

(6)需要精確的力矩控制,要求動態(tài)性能較好(High requirement);

(7)要求性價比高(High requirement)。

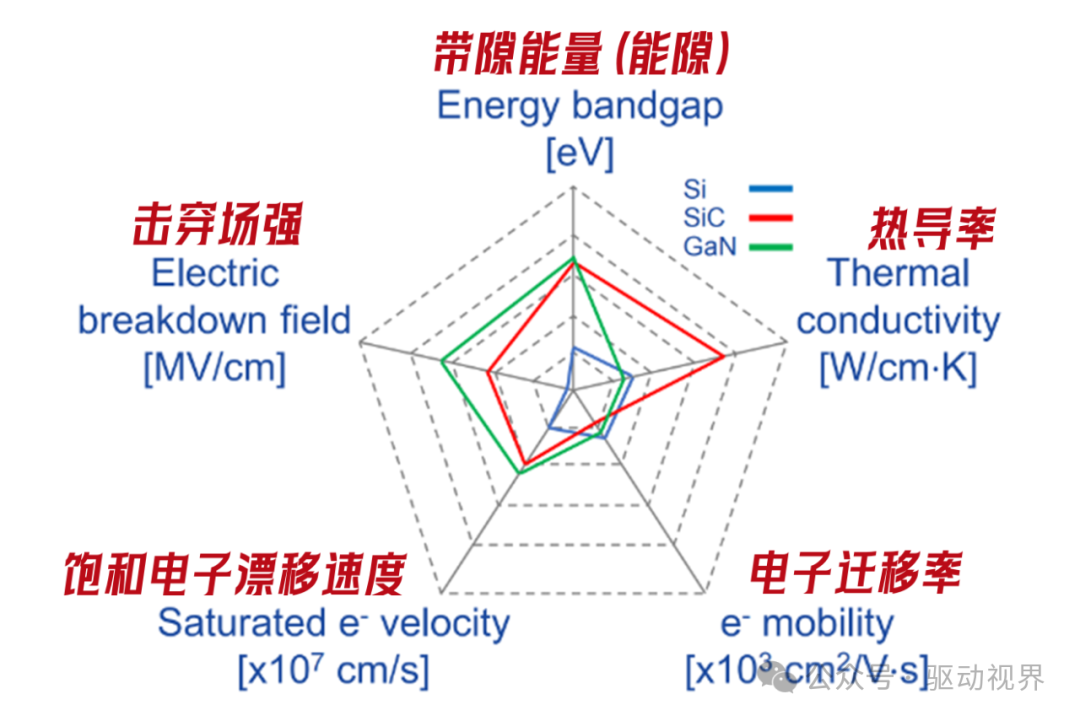

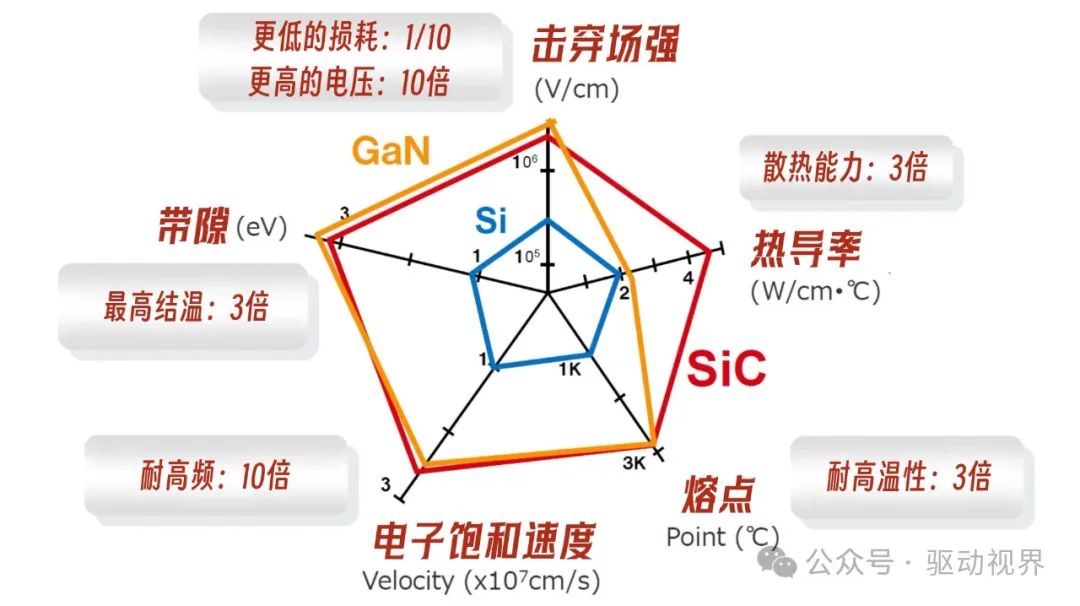

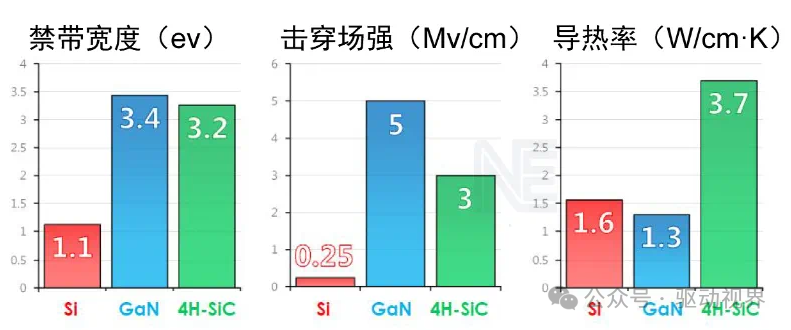

SiC碳化硅是由碳元素和硅元素組成的一種化合物半導(dǎo)體材料,是制作高溫、高頻、大功率、高壓器件的理想材料之一。

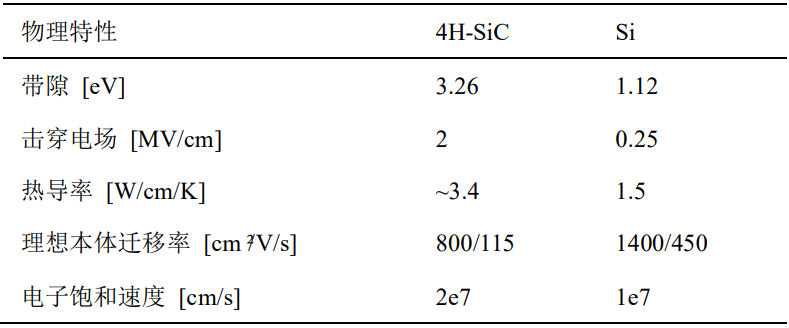

相比傳統(tǒng)的硅材料,碳化硅的禁帶寬度是硅的3倍,導(dǎo)熱率是硅的4-5倍,擊穿電壓是硅的8-10倍,飽和電子漂移速率是硅的2-3倍。

碳化硅器件的核心優(yōu)勢在于:

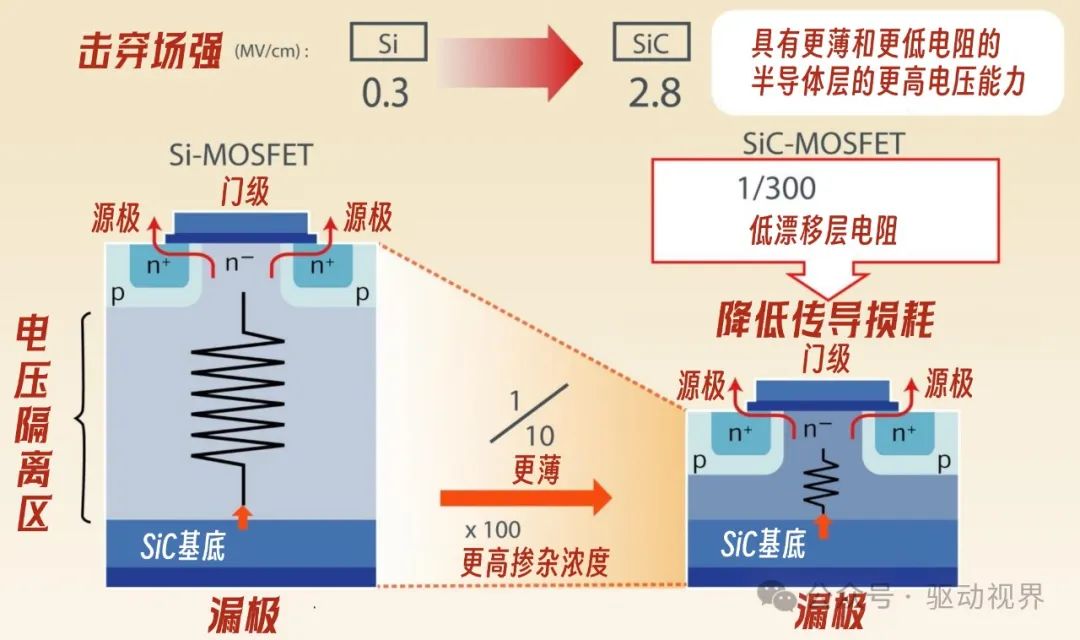

1)耐高壓:阻抗更低、禁帶寬度更寬,能承受更大的電流和電壓,帶來更小尺寸的產(chǎn)品設(shè)計和更高的效率;

2)耐高頻特性:SiC器件在關(guān)斷過程中不存在電流拖尾現(xiàn)象,能有效提高開關(guān)速度(大約是SiC的3-10倍),能達(dá)到更高頻率和更高開關(guān)速度;

3)耐高溫特性:SiC相對Si擁有更高的熱導(dǎo)率,能在更高溫度下工作。

碳化硅與硅基半導(dǎo)體相比(SiC VS. Si):

(1)擊穿場強×10

(2)禁帶寬度×3,極低的本征載流子濃度,耐高壓、高溫能力

(3)熱導(dǎo)率×3,散熱能力提升,有助于提升功率密度

以SiC和GaN為代表的寬禁帶半導(dǎo)體是實現(xiàn)高效率能量轉(zhuǎn)換、小型化、低系統(tǒng)成本的更佳選擇。

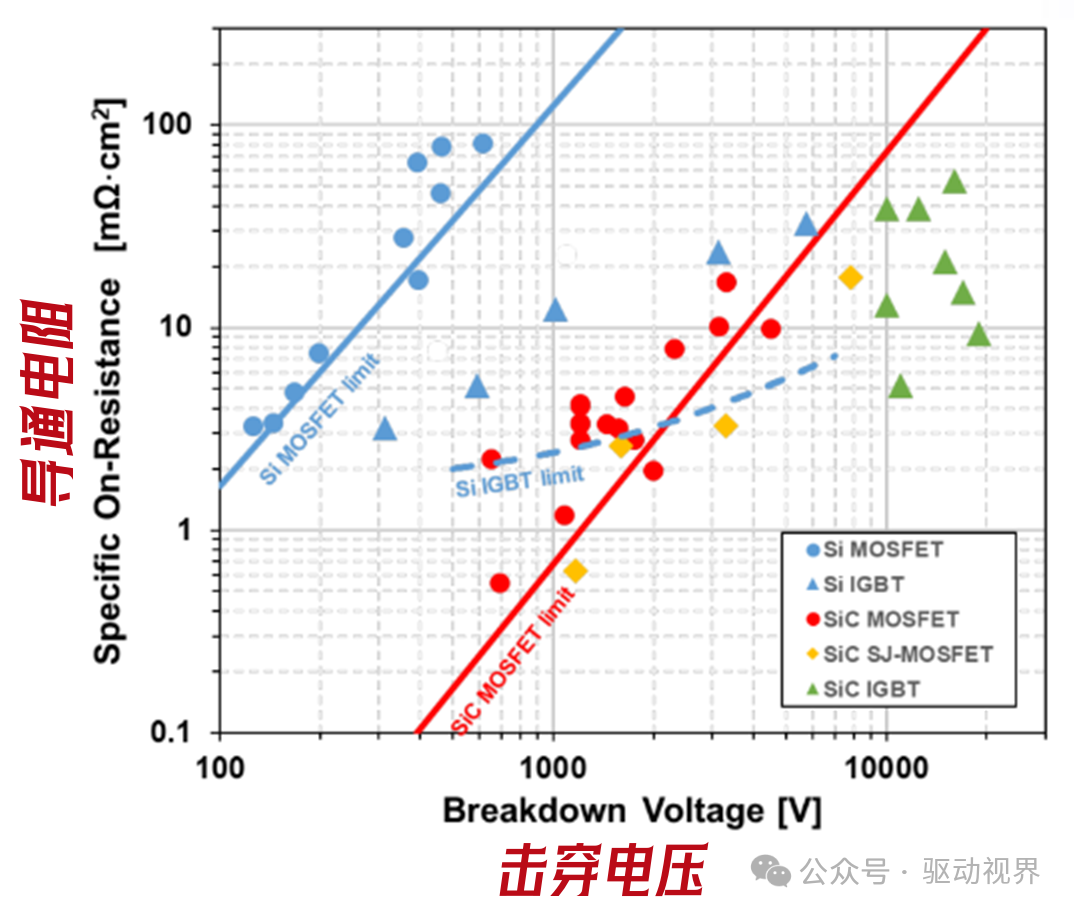

SiC MOSFET在多方面均表現(xiàn)出遠(yuǎn)超傳統(tǒng)Si基器件的性能,有望在多個領(lǐng)域逐漸實現(xiàn)替代,可靠性與成本是商業(yè)化的核心

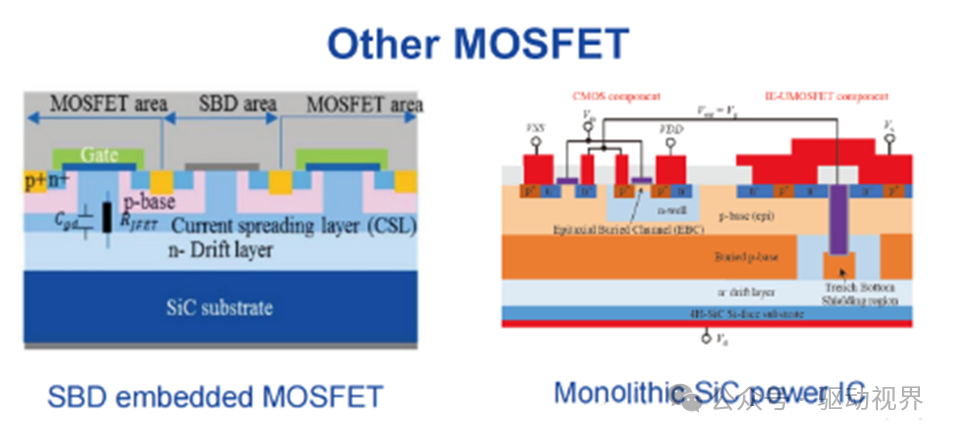

新型器件結(jié)構(gòu)、高溝道遷移率、超級結(jié)、SiC-IGBT、SiC-IC是未來努力的方向

SiC卓越的材料性能:具有Si和C共價鍵的化合物半導(dǎo)體

極硬材料,新莫氏硬度:13(鉆石15)

Si-MOSFET 和SiC-MOSFET結(jié)構(gòu)單元比較:

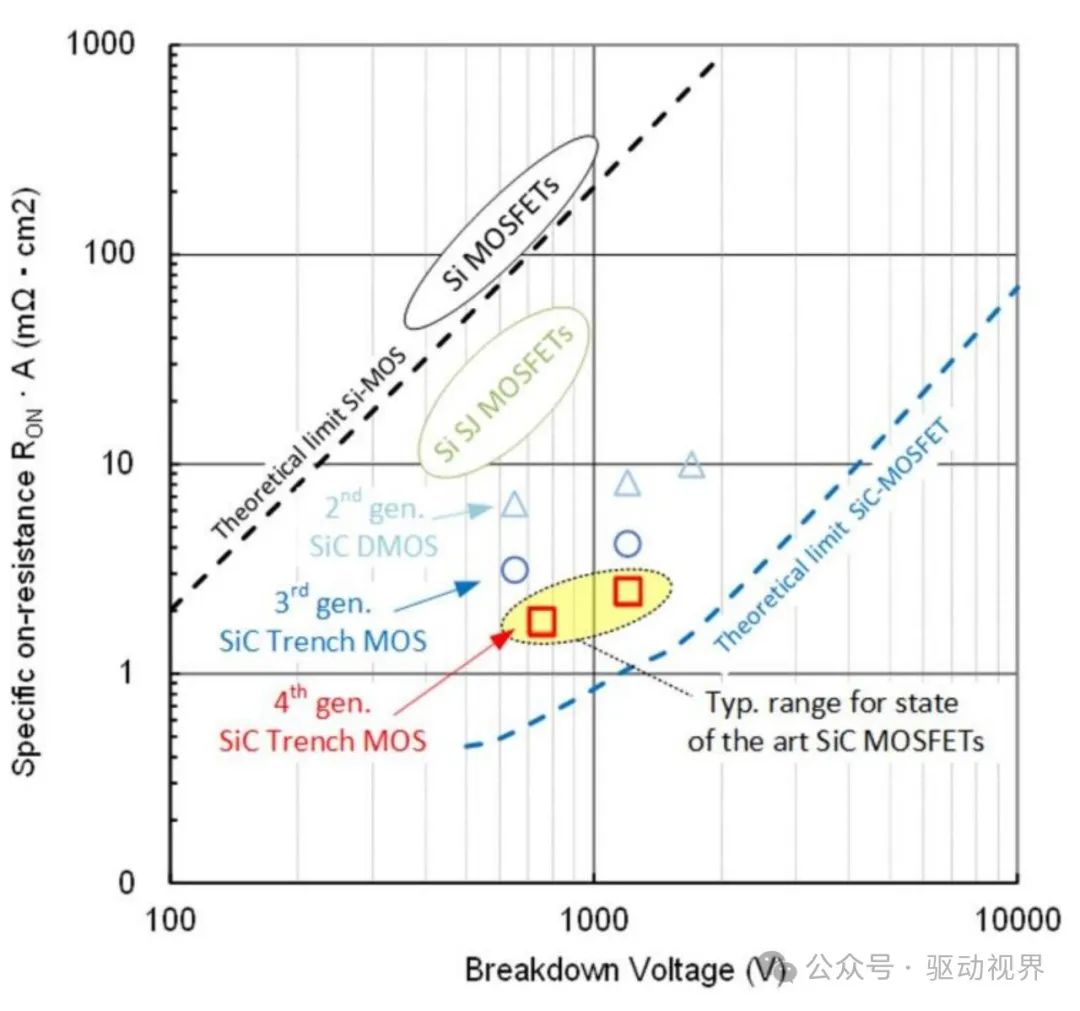

▲Si和SiC材料性能比較 SiC-mos 與Si-IGBT和Si-SJMOS的比較:

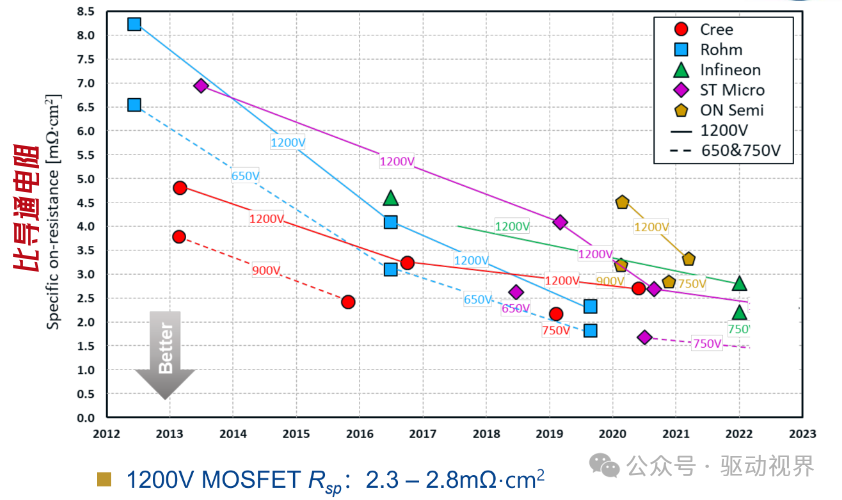

(1)與Si器件相比,SiC器件大大提高了工作性能

(2)每一代SiC器件都接近理論極限

(3)來自不同供應(yīng)商的最先進的SiC MOSFET達(dá)到了同類產(chǎn)品的性能

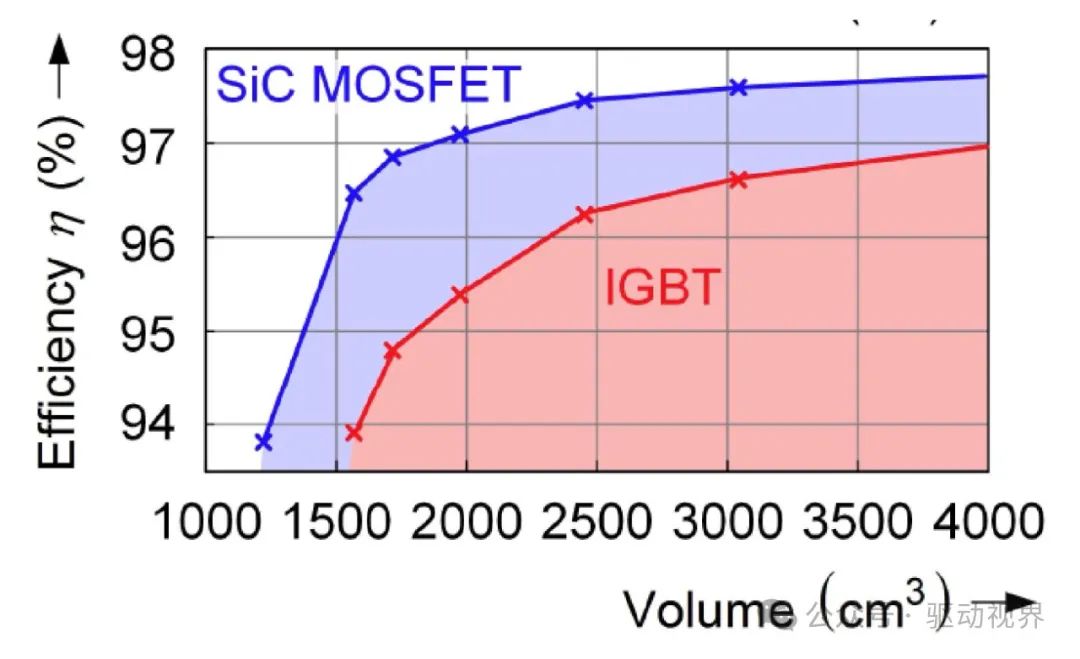

在電動汽車逆變器中采用SiC MOSFET的系統(tǒng)級效益:

SiC MOSFET技術(shù)的器件級優(yōu)勢:

(1)低導(dǎo)通損耗

(2)低開關(guān)損耗

SiC逆變器的系統(tǒng)級效益:

(1)高效率:在不犧牲車輛續(xù)航里程的情況下降低電池容量

(2)簡化且更緊湊的冷卻系統(tǒng)

▲基于SiC MOSFET的逆變器實現(xiàn)更高的效率

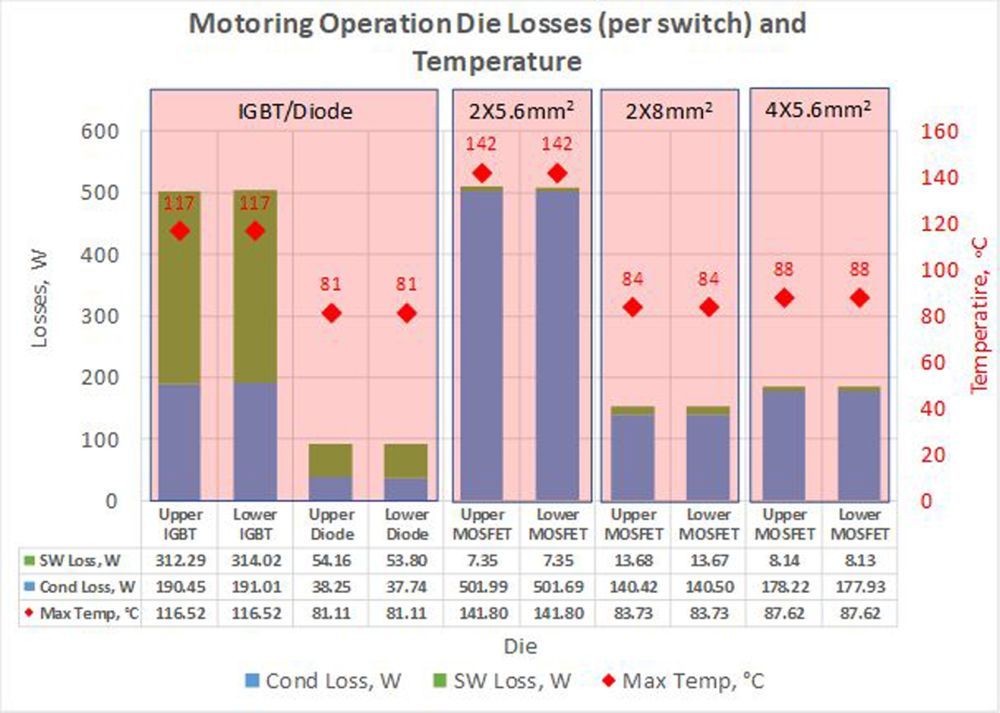

▲Nitzsche et al.,“Comprehensive Comparison of a SiC MOSFET and Si IGBT Based Inverter”,PCIM2019

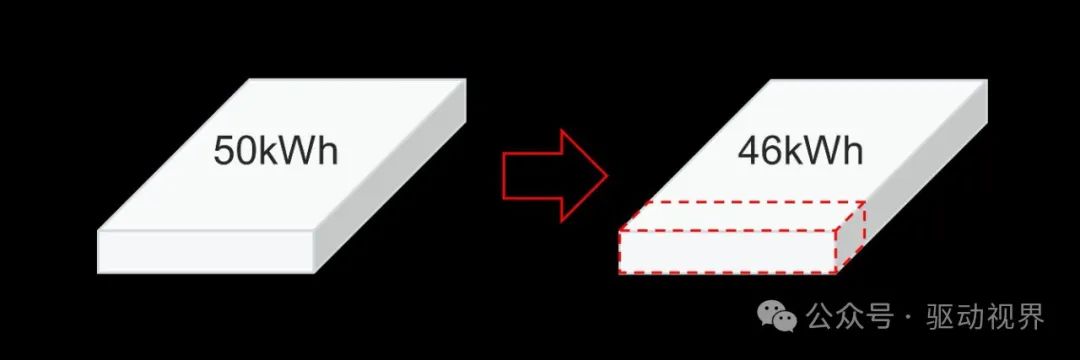

鋰離子電池尺寸和容量減少+保持續(xù)航里程不變

半導(dǎo)體成本的增加被電池費用的節(jié)省所彌補

相比傳統(tǒng)硅基材料,SiC各項性能指標(biāo)優(yōu)勢明顯:

SiC MOSFET在電動汽車主驅(qū)逆變器中相比Si-IGBT優(yōu)勢明顯,雖然當(dāng)前SiC器件單車價格高于Si-IGBT,但SiC器件的優(yōu)勢可降低整車系統(tǒng)成本:

(1)由于SiC MOSFET相比Si-IGBT功率轉(zhuǎn)換效率更高,根據(jù)Wolfspeed數(shù)據(jù),采用SiC MOSFET的電動汽車?yán)m(xù)航距離相比Si-IGBT可延長5%~10%,即在同樣續(xù)航里程的情況下可削減電池容量,降低電池成本;

(2)SiC MOSFET的高頻特性可使得逆變器線圈、電容小型化,電驅(qū)尺寸得以大幅減小;

(3)SiC MOSFET可承受更高電壓,在電機功率相同的情況下可以通過提升電壓來降低電流強度,從而降低線束成本。

SiC器件相比Si基器件的優(yōu)勢:

(1)導(dǎo)通電阻小(Low resistance):是Si基器件的1/3~1/5;

(2)可高溫工作(High temp.):是Si基器件的1.5~2倍;

(3)可高速開關(guān)(High frequency):是Si基器件的3~5倍

4、產(chǎn)品和技術(shù)

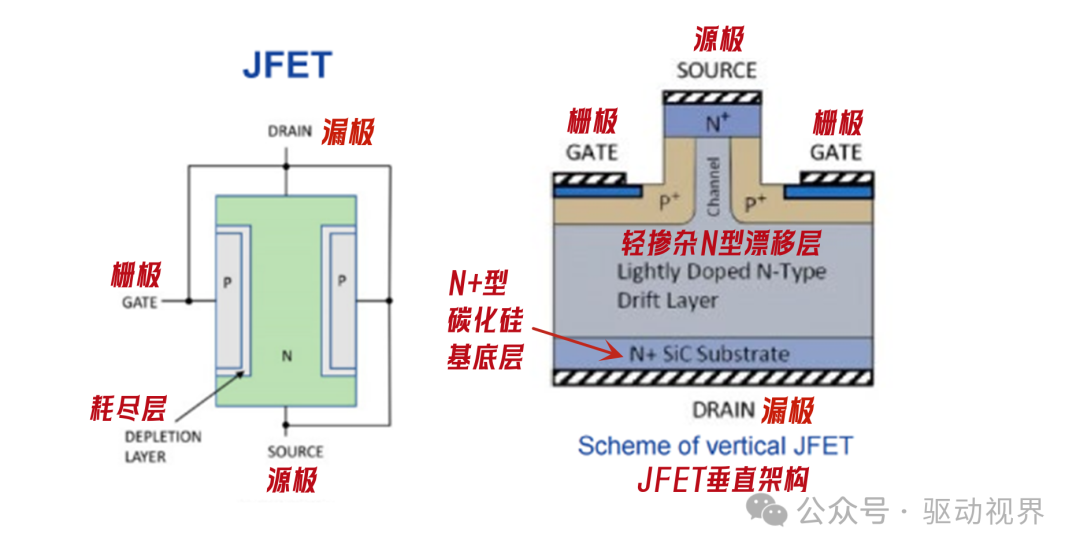

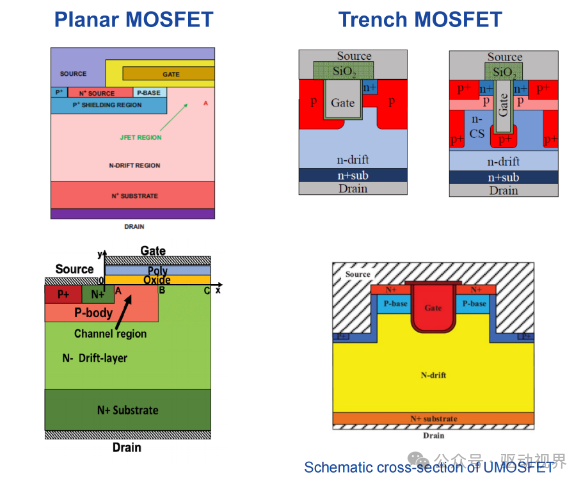

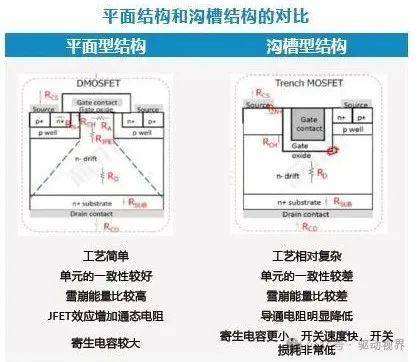

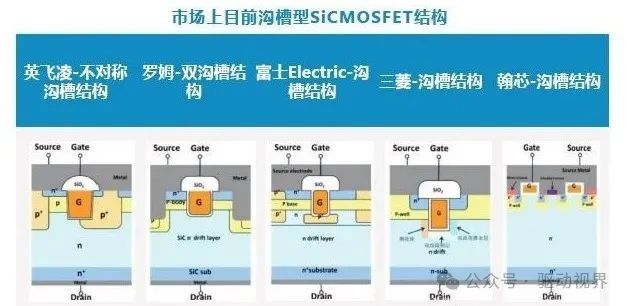

主流SiC功率器件結(jié)構(gòu):

主流SiC MOSFET比導(dǎo)通電阻發(fā)展趨勢

受工藝成熟度與穩(wěn)定性影響,溝槽柵器件暫時并沒有實現(xiàn)對平面柵結(jié)構(gòu)的全面超越。

目前平面型結(jié)構(gòu)式主流,未來溝槽型在高壓領(lǐng)域會廣泛應(yīng)用。平面結(jié)構(gòu)相比溝槽,不容易產(chǎn)生局部擊穿問題,不影響工作穩(wěn)定性,在1200V以下市場應(yīng)用廣泛。并且平面結(jié)構(gòu)制造相對簡單,成本可控。

溝槽型器件寄生電感極低,開關(guān)速度快,損耗低,器件性能相對高效。

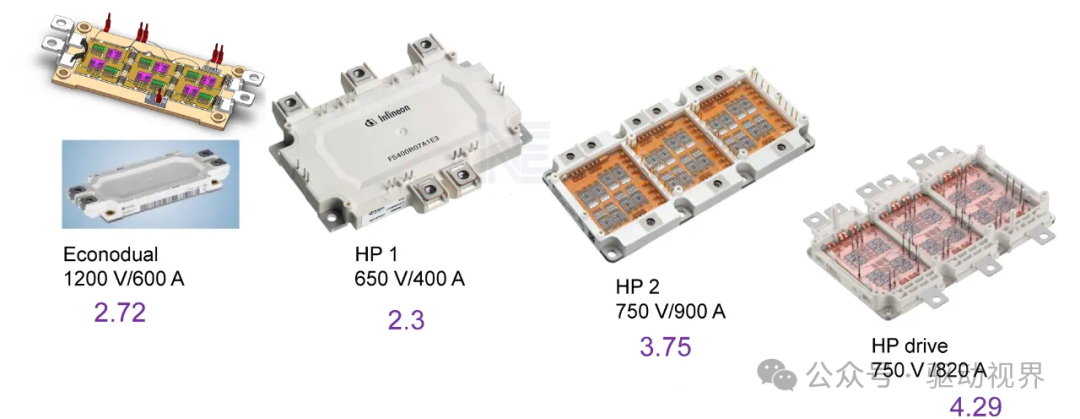

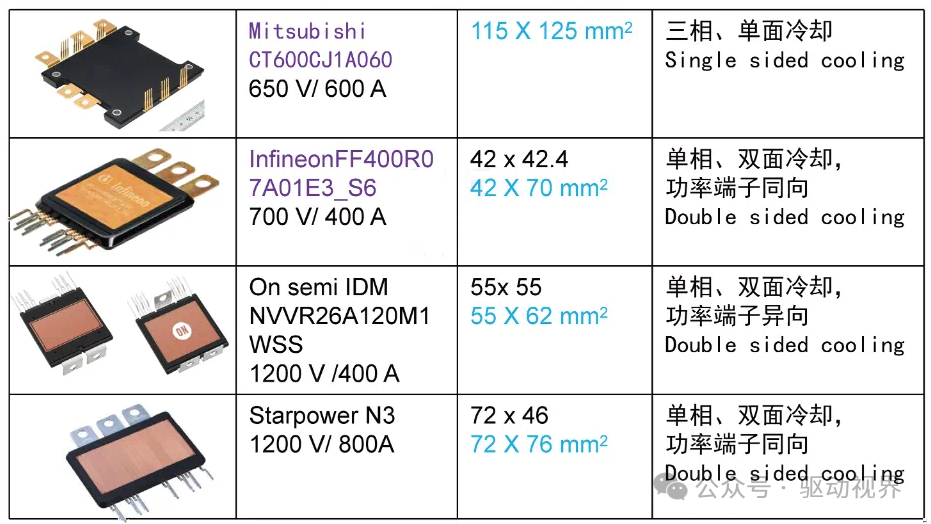

▲車用功率模塊功率密度演化

等效單相功率密度=電壓×電流÷體積×相數(shù)

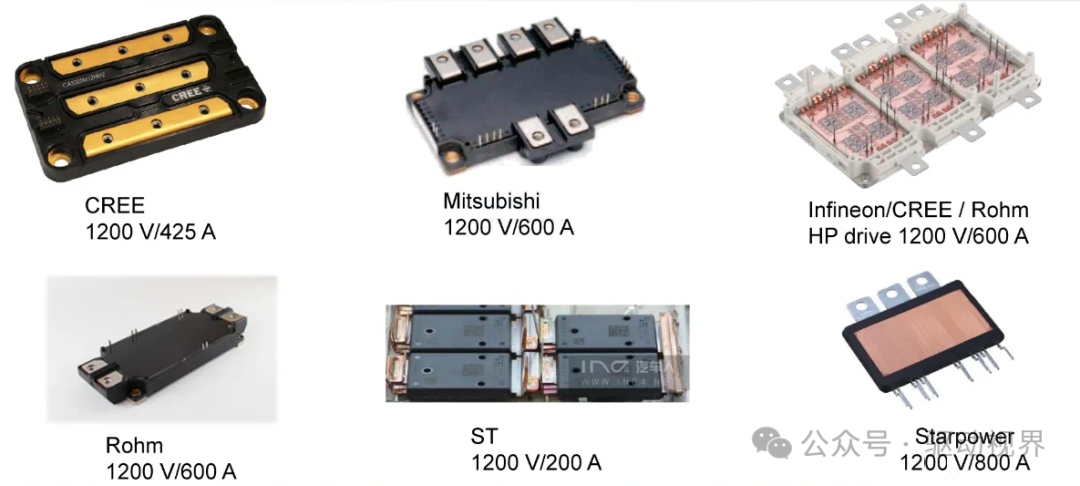

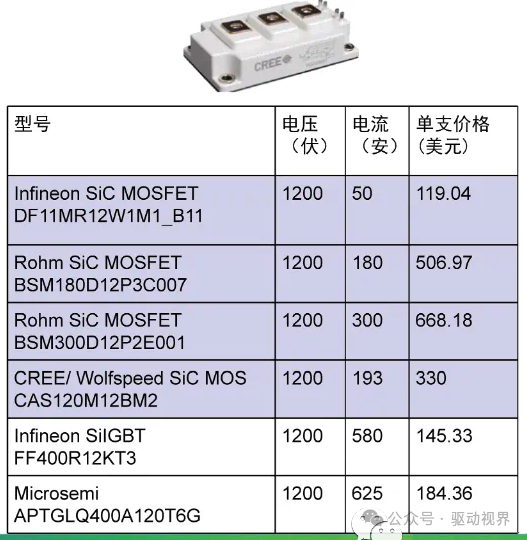

▲大功率SiC車用模塊

▲器件價格對比

SiC行業(yè)存在的問題:

(1)SiC襯底制備成本高

(2)高端技術(shù)和人才缺乏

(3)國外技術(shù)封鎖

(4)外延設(shè)備國產(chǎn)化率低

(5)產(chǎn)品良率低

SiC技術(shù)降本路徑:

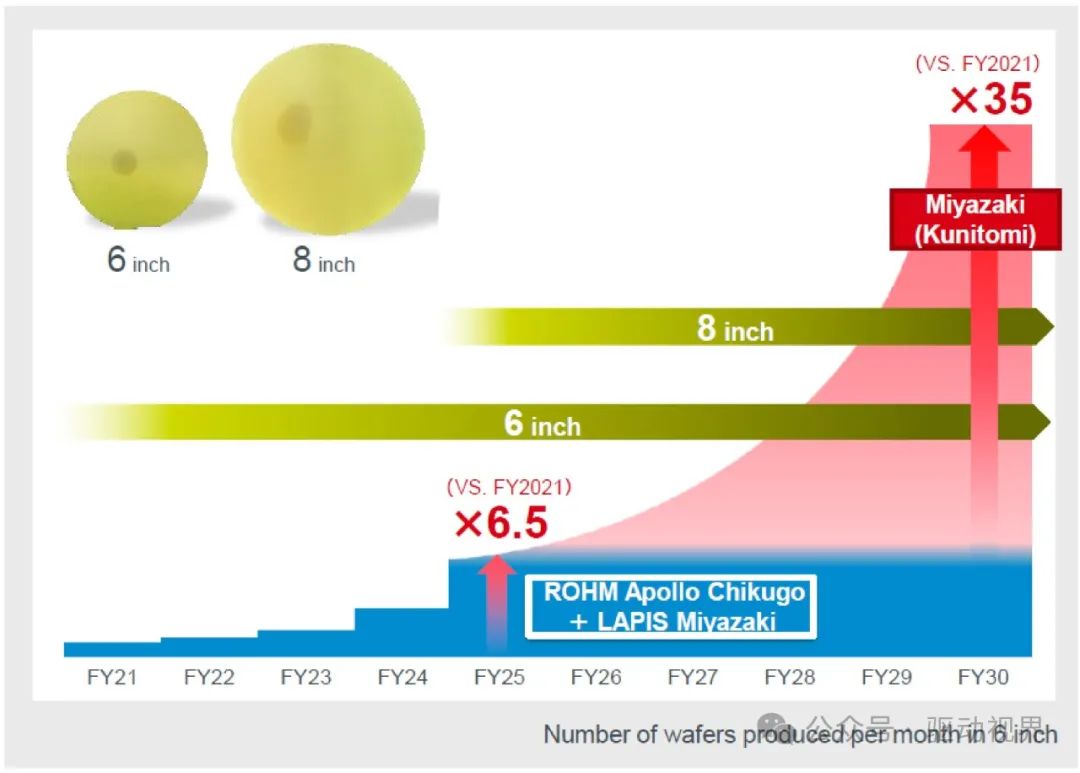

(1)擴大晶圓尺寸。從6寸晶圓轉(zhuǎn)向8寸晶圓,SiC芯片(32mm2)數(shù)量有望從448顆增加到845顆;能夠使整體碳化硅器件成本降低20%~35%。

(2)改進SiC長晶技術(shù),提升長晶速度。

(3)應(yīng)用ColdSplit技術(shù)分割碳化硅晶圓,從而使單個晶圓芯片數(shù)量翻倍。

5、設(shè)計和開發(fā)

SiC器件應(yīng)用需要突破的限制:

(1)突破現(xiàn)有模塊150℃限制(Package limit for high temp.),實現(xiàn)功率模塊200℃穩(wěn)定運行;

(2)解決高速開關(guān)易受干擾問題(Gate drive limit for high freq.),實現(xiàn)高速門級驅(qū)動;

(3)解決散熱過于集中問題(Thermal limit for high density),采用高效散熱方法

碳化硅功率模塊相關(guān)設(shè)計要點(SiC High Density Converter Design):

(1)模塊布局(Module layout)

(2)高溫封裝(High temp. packaging)

(3)驅(qū)動設(shè)計(Gate drive design)

(4)保護設(shè)計(Sensor & protection)

(5)高溫主回路(Busbar design)

?

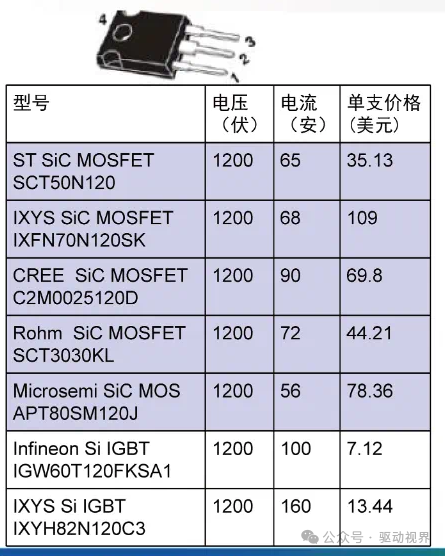

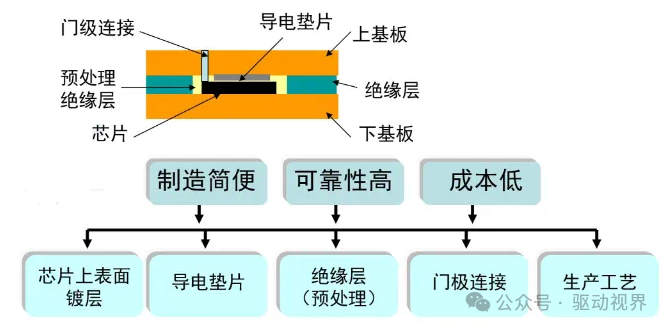

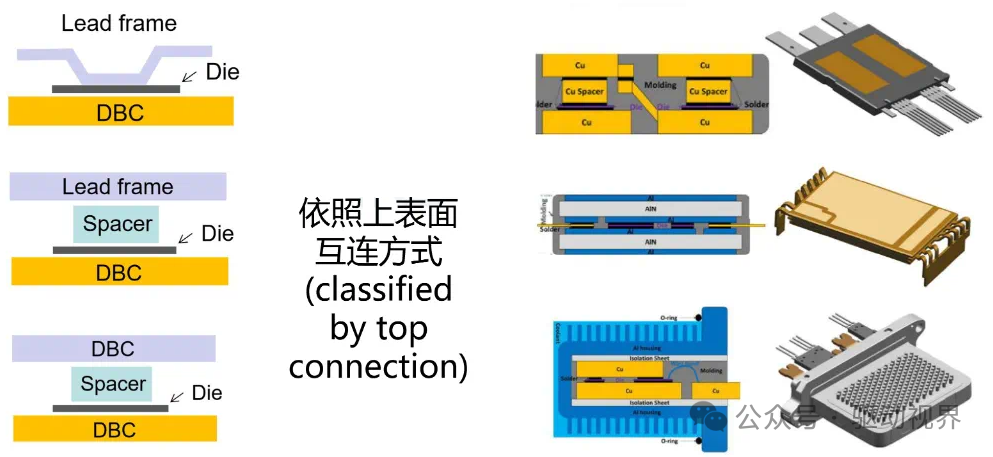

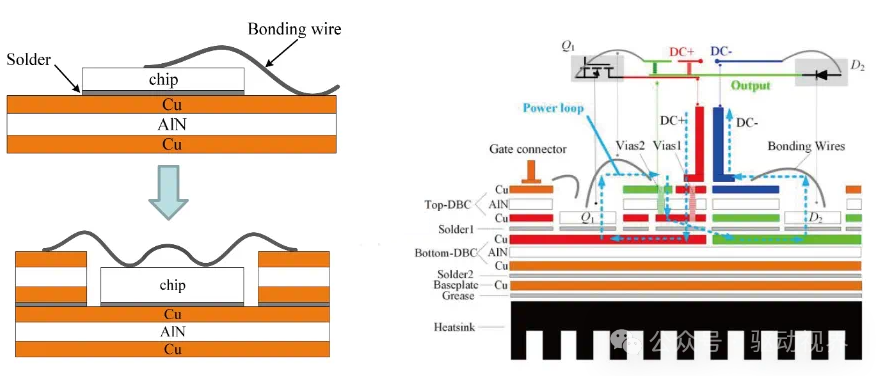

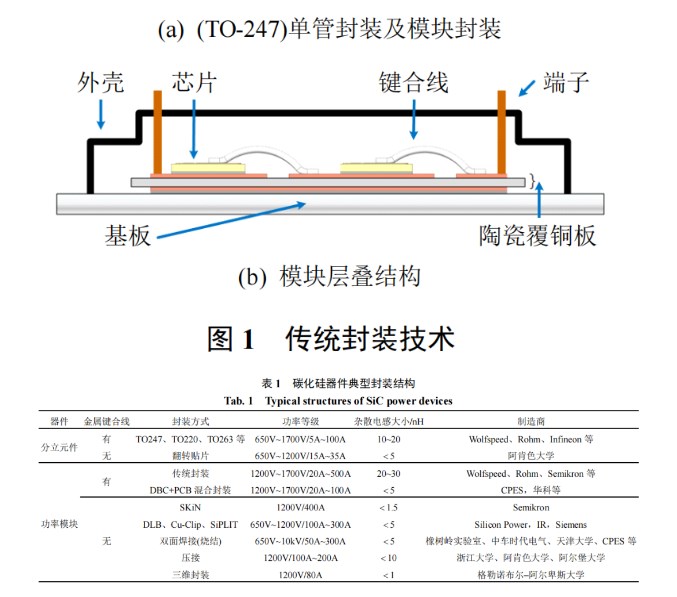

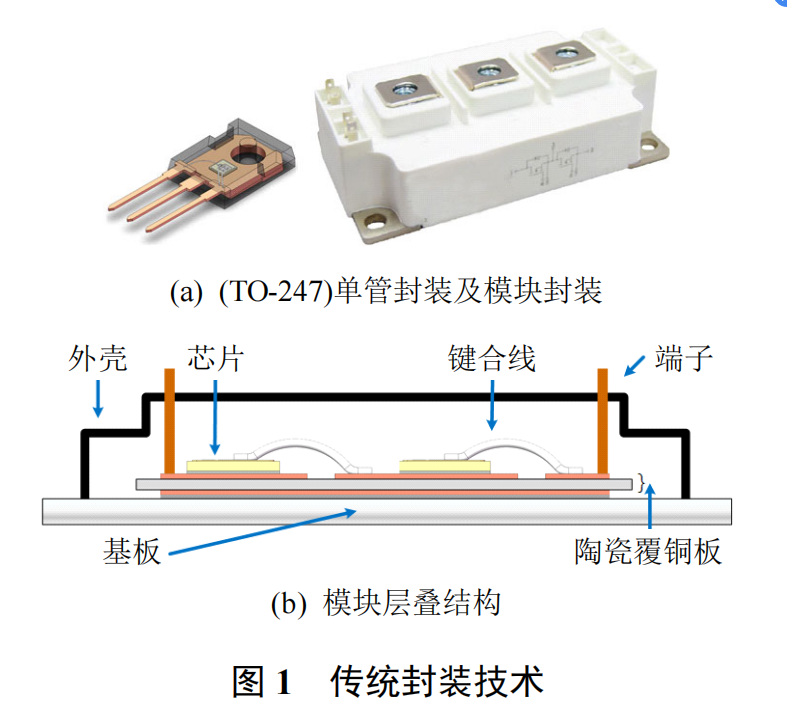

平面封裝和雙面冷卻技術(shù)(Double)

(1)低寄生電感:電壓過沖減小

(2)高散熱能力:降低局部熱點溫度

(3)柔性互聯(lián)/緩沖層:抗熱應(yīng)力能力提高

(4)無鍵合線:功率循環(huán)可靠性提高

▲平面型封裝硅模塊

▲平面型封裝硅模塊典型產(chǎn)品(Plannar Packaged Products)

▲平面型模塊分類(Planar Package Classification) ?

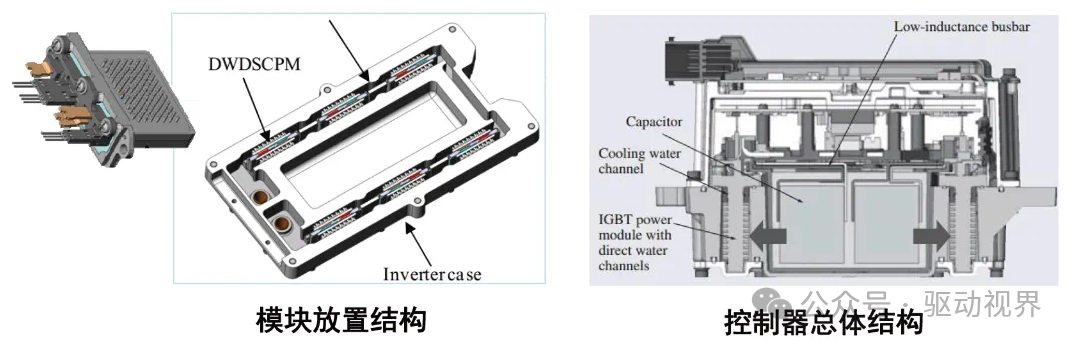

▲雙面散熱

雙面散熱(Double-sided Cooling)技術(shù)要點:

(1)互連與散熱約束

(2)高性能母排

(3)散熱平衡設(shè)計

(4)驅(qū)動板排布位置

▲無源器件水冷散熱

2014年日本Hitachi硅基變頻器,應(yīng)用Pinfin雙面冷卻模塊,電容水冷,峰值功率122.5kW,體積3.5L,功率密度35kW/L。

6、工藝、制造和產(chǎn)業(yè)鏈

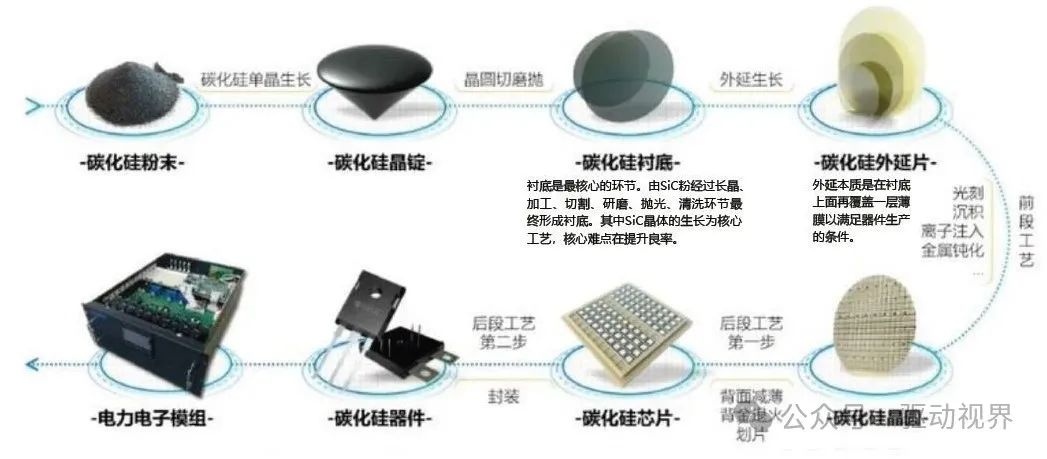

產(chǎn)業(yè)鏈上游是襯底和外延,中游是器件和模塊制造,下游是終端應(yīng)用。

產(chǎn)業(yè)鏈價值量倒掛,其中襯底制造技術(shù)壁壘最高、價值量最大,是SiC大規(guī)模產(chǎn)業(yè)化推進的核心。

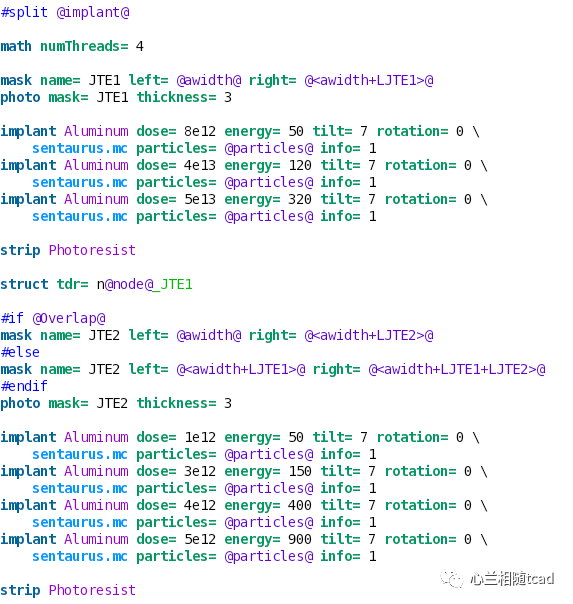

從工藝流程上看,碳化硅一般是先被制作成晶錠,然后經(jīng)過切片、打磨、拋光得到碳化硅襯底;襯底經(jīng)過外延生長得到外延片;外延片經(jīng)過光刻、刻蝕、離子注入、沉積等步驟制造成器件。將晶圓切割成die,經(jīng)過封裝得到器件,器件組合在一起放入特殊外殼中組裝成模組。

碳化硅單晶生長熱場存在溫度梯度,導(dǎo)致晶體生長過程中存在原生內(nèi)應(yīng)力及由此誘生的位錯、層錯等缺陷,降低可靠性。

SiC粉經(jīng)過長晶、加工、切割、研磨、拋光、清洗環(huán)節(jié),最終形成襯底。

▲SiC晶圓生產(chǎn)很復(fù)雜

與傳統(tǒng)硅功率器件制作工藝不同,碳化硅器件不能直接制作在碳化硅襯底上,需在導(dǎo)電型襯底上生長碳化硅外延層得到碳化硅外延片,并在外延層上制造肖特二極管、MOSFET、IGBT等功率器件。

碳化硅襯底無法直接加工,需要生長一層薄膜后再進行加工。導(dǎo)電型襯底生長出同質(zhì)外延層,半絕緣型襯底生長出異質(zhì)外延層。

SiC晶體生長過程中會不可避免地產(chǎn)生缺陷、引入雜質(zhì),導(dǎo)致襯底材料的質(zhì)量和性能都不夠好。而外延層的生長可以消除襯底中的某些缺陷,使晶格排列整齊。

現(xiàn)在所有的器件基本上都是在外延上實現(xiàn),所以外延的質(zhì)量對器件的性能影響非常大。

在半絕緣型SiC襯底上生長氮化鎵外延層,成為異質(zhì)外延層;在導(dǎo)電型SiC襯底表面上生長一層碳化硅外延層,稱為同質(zhì)外延。

外延是一種常用的單晶薄膜制備技術(shù),和Si器件工藝不同,幾乎所有的SiC電力電子器件工藝都是在4H-SiC同質(zhì)外延層上實現(xiàn),襯底只是起到支撐和導(dǎo)電的作用。

電壓越高,對外延厚度和摻雜濃度均勻性要求越高,生產(chǎn)難度越大。

外延片市場Wolfspeed一家獨大,占據(jù)50%市場份額。

現(xiàn)在SiC薄膜外延的方法主要有:化學(xué)氣相沉積(CVD)、分子束外延(MBE)、液相外延法(LPE)等,其中化學(xué)氣相沉積(CVD)是最為普遍的4H-SiC外延方法。

SiC單晶方面主要三個難點:

(1)生長溫度在2300℃以上,對溫度和壓力的控制要求高;

(2)長晶速度慢,7天時間大約可生長2cm碳化硅晶棒;

(3)晶型要求高、良率低,只有少數(shù)幾種晶體結(jié)構(gòu)的單晶型碳化硅可作為半導(dǎo)體材料。

7、概念和定義

(1)能隙(Bandgap energy gap)或譯作能帶隙,在固態(tài)物理學(xué)中泛指半導(dǎo)體或是絕緣體的價帶(valence band)頂端至導(dǎo)帶(conduction band)底端的能量差距。

(2)電子遷移率(electron mobility)是固體物理學(xué)中用于描述金屬或半導(dǎo)體內(nèi)部電子在電場作用下移動快慢程度的物理量。

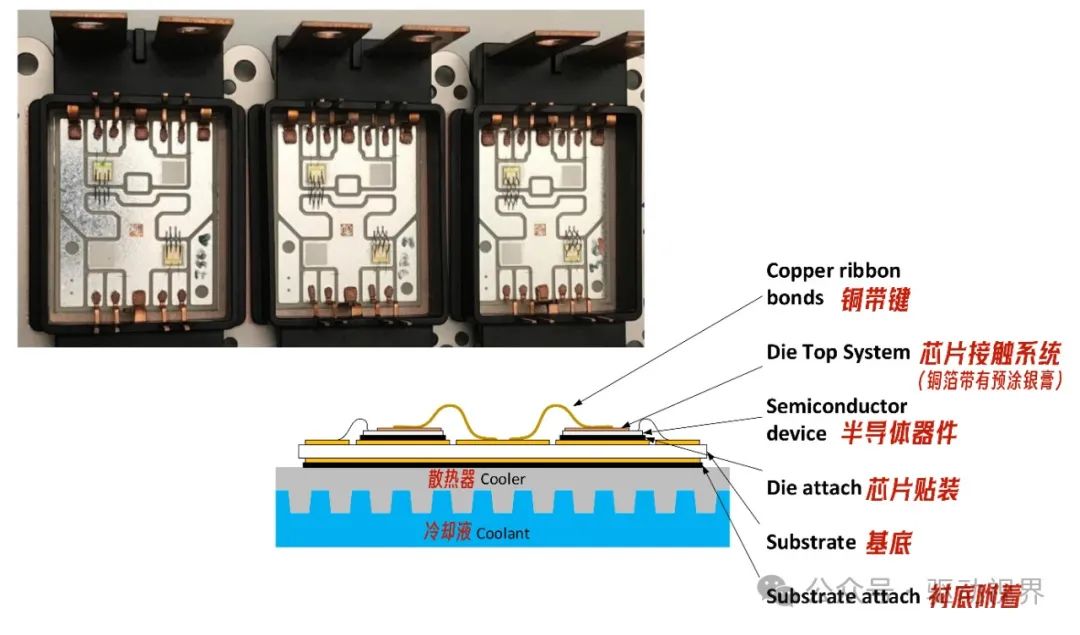

(3)DTS(Die Top System):是一種芯片頂部系統(tǒng)技術(shù)。

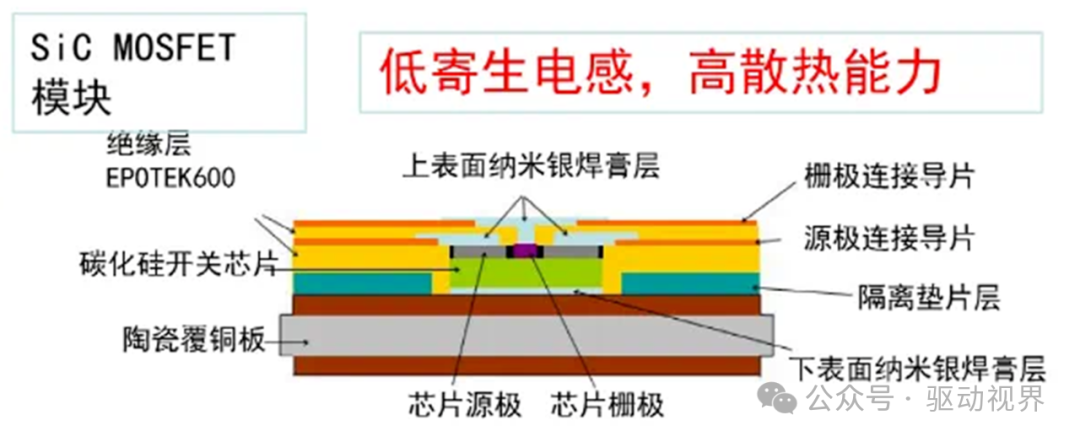

模塊內(nèi)部采用的連接技術(shù)最常見的是焊接和鋁線互連,通常使用的鋁線線徑在100um~500um,在150℃以上時可靠性就有了局限性。

隨著運行溫度和可靠性要求的提升,在車規(guī)模塊中采用銅線代替鋁線是趨勢,但銅線直接鍵合到傳統(tǒng)的芯片金屬化會導(dǎo)致一些損傷和缺陷。

賀利氏推出的DTS技術(shù)有效地解決了硬銅線綁定的一些問題,包含了在銅片上的預(yù)涂銀層來保護芯片免受相對于鋁綁定線而言更高的鍵合力,同時將芯片電流產(chǎn)生的熱量均勻地分布到整個芯片表面,降低芯片局部溫度。

傳統(tǒng)焊料的熔點在220℃~240℃,在較高的運行溫度下會出現(xiàn)過早的失效,特別是碳化硅此類的寬禁帶半導(dǎo)體。而銀的熔點在962℃左右,非常薄的銀層(如20um或30um)作為粘合層,能夠滿足高溫要求。同時銀具有較低的熱阻。

DTS是銅箔帶有預(yù)涂銀膏的組合,主要適用于單面水冷設(shè)計,其中芯片的熱量也可以有效的從芯片頂部耗散。

DTS系統(tǒng)與銀燒結(jié)結(jié)合應(yīng)用對其可靠性有巨大的影響。僅用銀燒結(jié)劑代替焊料,用DTS燒結(jié)和銅線代替頂部鋁線,在極端條件下,結(jié)溫度至少降低了10K,壽命至少增加了10倍。

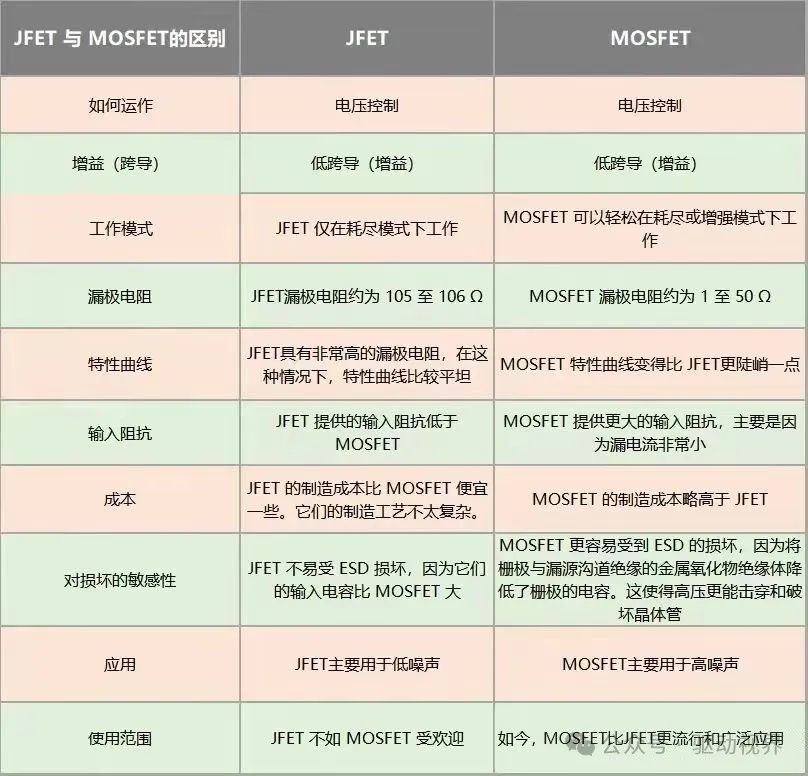

(4)MOSFET和JFET的區(qū)別

JFET是結(jié)型場效應(yīng)晶體管的首字母縮寫,由柵極、源極和漏極 3 個端子組成。在 JFET 中,電場施加在控制電流流動的柵極端子上。從漏極流向源極端子的電流與施加的柵極電壓成正比。JFET基本上有兩種類型,基本上是N溝道和P溝道。

MOSFET是金屬氧化物半導(dǎo)體場效應(yīng)晶體管的首字母縮寫。在這里,器件的電導(dǎo)率也根據(jù)施加的電壓而變化。MOSFET有兩種類型:耗盡型MOSFET和增強型 MOSFET。

(5)襯底和外延

襯底定義:沿特定結(jié)晶方向切割、研磨、拋光,得到具有特定晶面和適當(dāng)電學(xué)、光學(xué)和機械特性,用于生長外延層的潔凈單晶圓薄片。

襯底分類:從電化學(xué)性質(zhì)差異來看,碳化硅襯底材料可以分為導(dǎo)電型襯底和半絕緣型襯底。

外延工藝是指在SiC襯底的表面上生長一層質(zhì)量更高的單晶材料。

8、中科院電工所

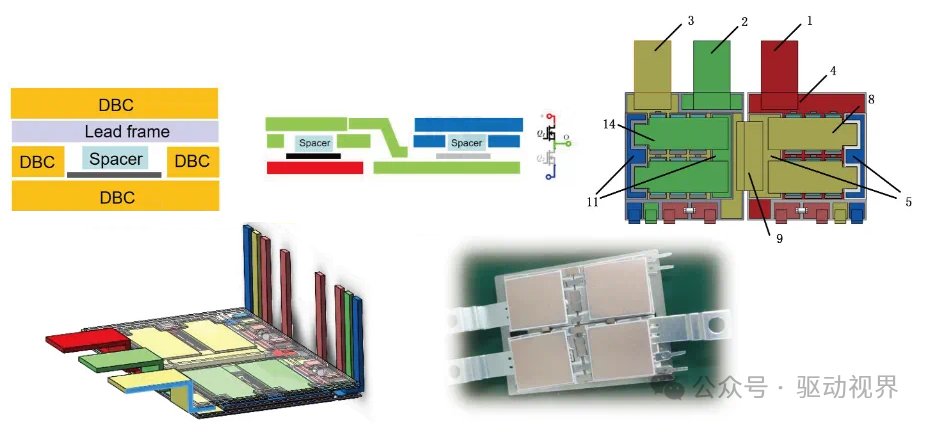

▲疊層DBC方案

中科院電工所疊層DBC方案(Stacked DBC Method):

(1)破除通流瓶頸,芯片并聯(lián)數(shù)量提高80%(Break the limit of current path,parallelling more dies)。

(2)依靠互感降低自感,總體寄生阻抗降低50%(Reduce parastic parameters)。

▲疊層平面模塊設(shè)計

中科院電工所疊層平面模塊設(shè)計(Stacked Planar Module)

(1)導(dǎo)電層從2層增加到4層,芯片并聯(lián)數(shù)量提高50%,寄生阻抗降低15%(Conduction layer increased)

(2)多層DBC直接支撐,可使用雙面pinfin直焊,進一步降低熱阻(DBC support top layer)

中科院電工所18芯片并聯(lián)SiC模塊樣品通過800V/670A雙脈沖測試@150℃(Double pulse test)

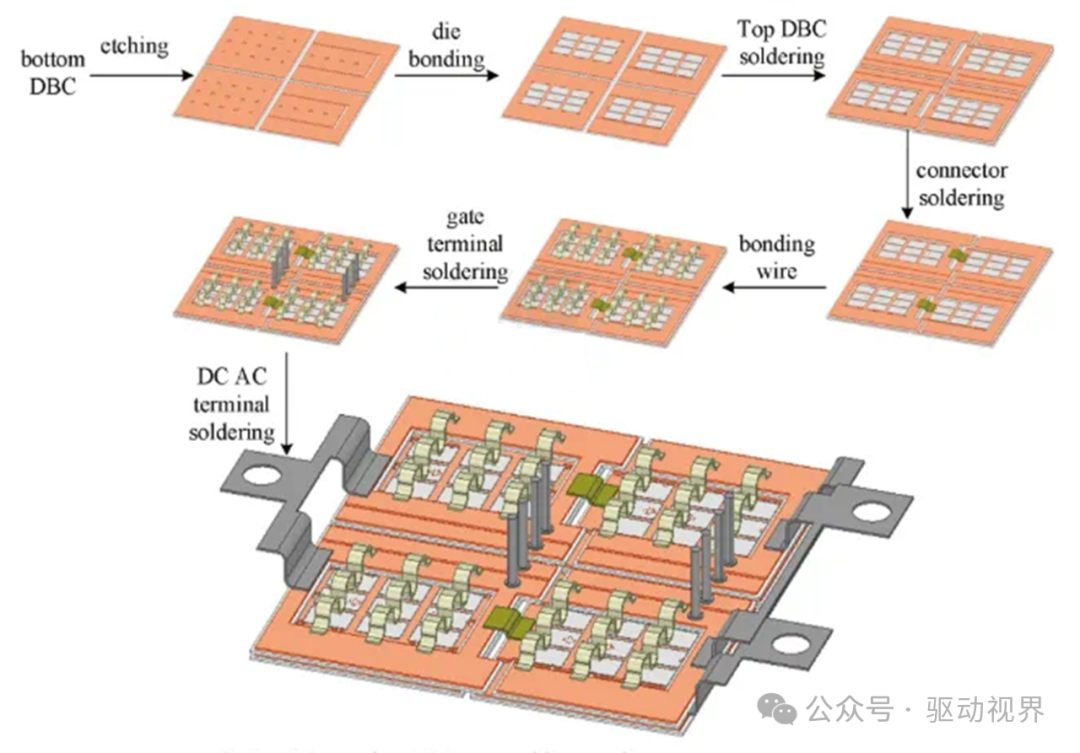

▲疊層模塊制造流程

疊層模塊制造流程(Stacked Module Fabrication):

(1)2~3次焊接,與普通工藝一致(2~3 soldering steps)

(2)功率端子可選擇使用超聲波焊接(Ultra-sonic bonding for terminal)

小結(jié):

(1)平面封裝適用于電動汽車應(yīng)用中的sic器件

(2)堆疊DBC方法可以提高功率模塊的功率密度

(3)格子法有助于熱設(shè)計

9、羅姆(ROHM)

羅姆SiC產(chǎn)能擴展計劃:

審核編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論