富昌電子(Future Electronics)一直致力于以專業的技術服務,為客戶打造個性化的解決方案,進而縮短產品的設計周期、加快行業發展的步伐。在第三代半導體的實際應用領域,富昌電子結合自身的技術、項目經驗積累,著筆SiC相關設計的系列文章,希望能給到大家一定的參考,并期待與您進一步的交流。

作為系列文章的第四篇,本文主要針對SiC MOSFET 短路Desat 保護設計做一些探討。

1.???? 什么是Desat

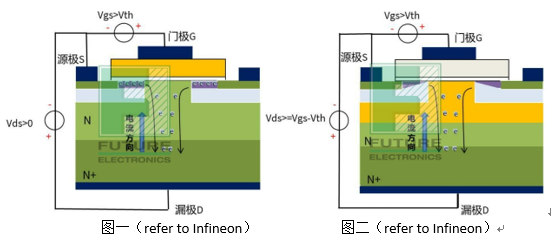

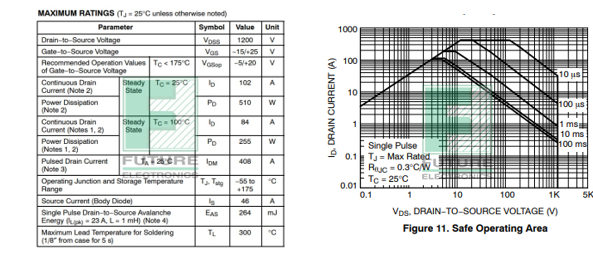

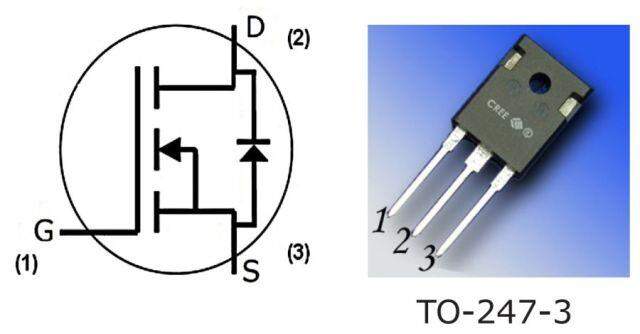

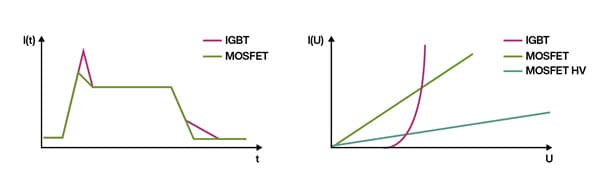

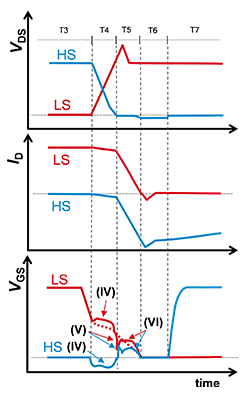

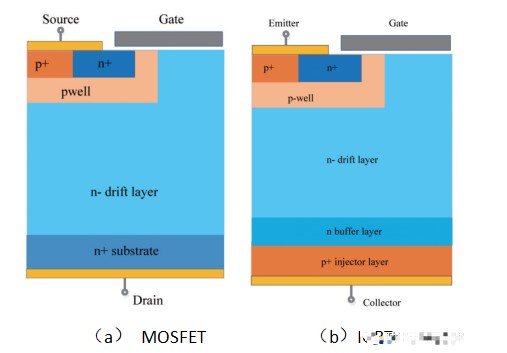

Desat保護是功率MOSFET和IGBT保護中很重要的概念, 下面我們用圖一所示是一個簡化的MOS剖面圖,以此來闡述退飽和發生的原因。柵極施加一個大于閾值的正壓VGS,則柵極氧化層下方會形成導電溝道,這時如果給漏極D施加正壓VDS,則源極中的電子便會在電場的作用下源源不斷地從漏極D流向源極S,這樣電流便形成了,這時電流隨DS電壓的增長而線性增長。隨著DS電壓的增大,使得柵極和硅表面的電壓差很小而不能維持硅表面的強反型,溝道出現夾斷現象,電流不再隨DS電壓的增加而成比例增長,而進入退飽和狀態(如圖二)。

在實際應用 中,退飽和現象一般發生在器件短路時,這時Vds電壓上升到母線電壓,電流一般是額定電流的幾倍。功率異常增大,結溫急劇上升,不及時關斷器件就有可能燒毀器件。多數MOSFET電流短路承受能力差而造成熱損壞,而SiC MOSFET電流的短路能力更差。那么針對SiC MOSFET的Desat保護設計就變得尤為重要了。

?

2.???? 如何進行Desat的設計

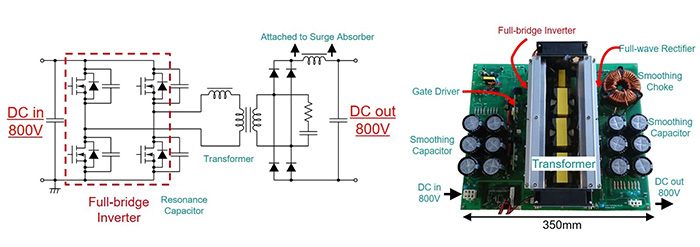

SiC MOSFET電路通常用傳感器進行在線電流檢測,進行精確的過電流保護。而Desat保護被視為第二級保護措施。在有些特殊故障情況,例如橋式直通或逆變器在濾波器前輸出端對地短路等,在線電流傳感器無法檢測到這類故障,Desat保護就成為保護功率器件重要的措施。

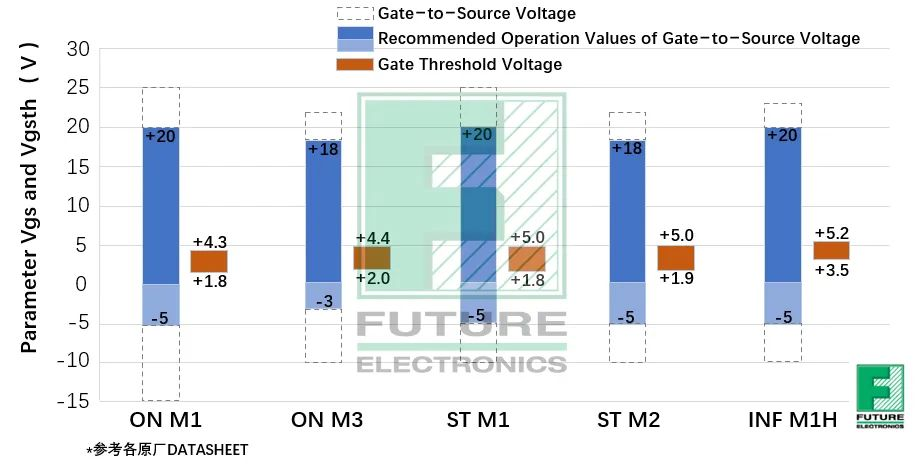

設計中,主要的考慮是Desat保護閾值的設定,一般應設置為保守值,以避免過早觸發。下面就通過onsemi的SiC MOSFET NTH4L020N120SC1為例,來論述下如何設計這個保護閾值。

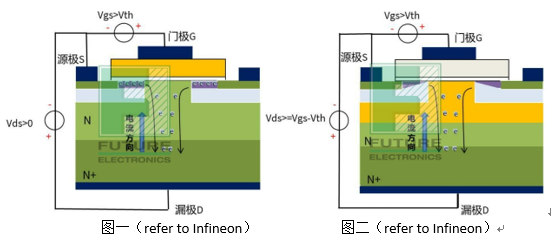

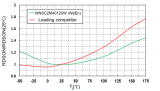

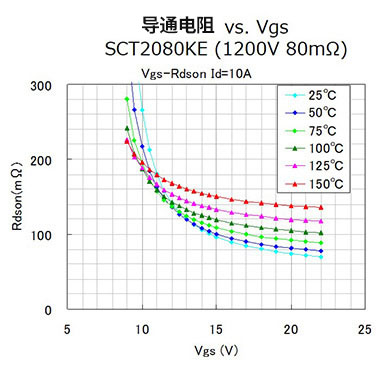

SiC MOSFET datasheet提供“最大漏極脈沖電流”(10us單脈沖)如圖一。該電流約為器件在 125 °C時額定連續電流的 4 倍左右(onsemi NVH4L020N120SC1) 如圖二。在額定連續電流和最大漏極脈沖電流之間選擇過流保護值。過流保護閾值的計算應使用 125 °C 或 150 °C 時的 RDS_ON。傳導電流是 DESAT 引腳提供的電流。二極管壓降具有負溫度系數。保守計算,可以將 25 °C 時二極管 的正向電壓用于過流保護閾值的計算。

?????

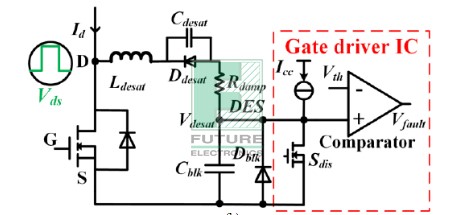

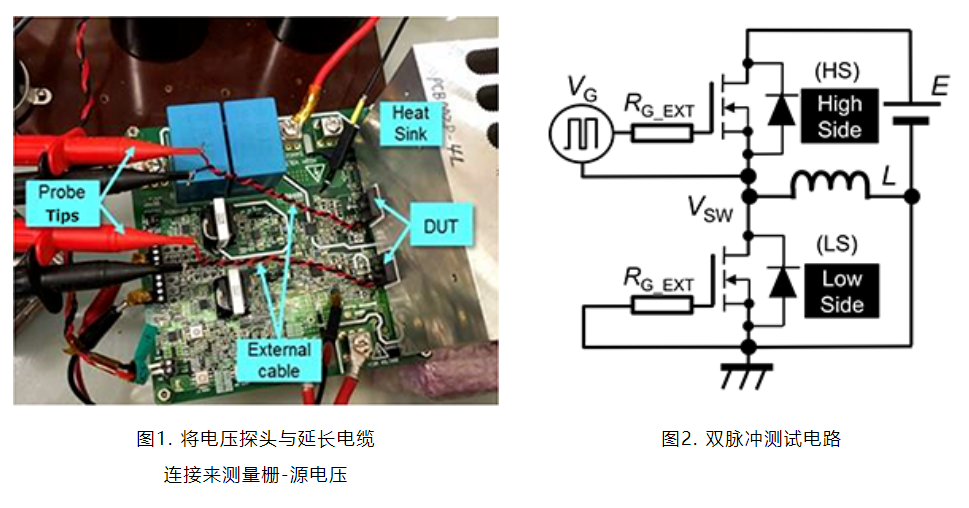

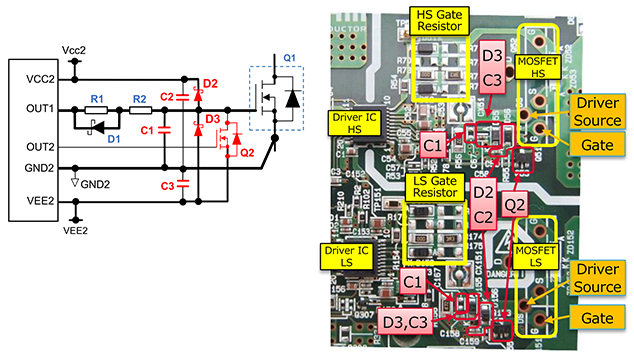

?如圖三所示, 設置限流值的時候,可以用公式 Ilimit = (Vth – Rdamp* IDESAT – VFD)/ Rdson 來計算, 其中 Rdamp 為調壓電阻,VFD為高壓二極管的正向壓降,Rdson為 SiC MOSFET 估算結 溫下的導通電阻。 當發生短路或過流時,SiC MOSFET 漏極電流將會增加 到一個很高的值,并且器件的 Vds 將會升高到很高的值。鉗位DESAT 引腳通過內電流源給消隱電容 Cblk 充電到更高的電壓。當電壓達到過流保護閾值時,OUT 和/FAULT 均被拉低。通過選擇不同的消隱電容,可以設置DESAT 保護電消隱時間。消隱時間可以公式計算: Teblk = Cblk ?Vth / IDESAT。 不同的應用通常需要不同的關斷時間。優化的關斷時間可以最大化地發揮系統的短路 能力,同時限制 Vds 和 bus 電壓上的振蕩。

????????????? 3.???? Desat 保護設計注意事項:

a.???? SiC mosfet 的高dv/dt 是引起噪聲和desat誤觸發主要原因。在高的Vds dv/dt 作用下,高壓阻斷二極管 D寄生電容 Cdesat 引 起的電壓耦合會顯著抬高或降低陽極電壓 。 陽極電壓變化又會將 消隱電容 Cblk充電或放電到一個非預期值,并導致誤觸發或 desat 保護延遲。由于 SiC MOSFET 的高開關速度,這個問題變得更加嚴重。為了鉗制 Vdsat 電壓的上升幅度,使用一個 穩壓二極管。為了最大程度地降低 Cdesat 的影響,使用低結電容的二極管電壓阻斷非常必要。

b.??? 與高壓阻斷二極管串聯的寄生電感Ldesat也是必須考慮的因素,過高的Ldesat 會與二極管寄生電容Cdesat諧振,會影響Vdesat震蕩的最大值的變化。從而影響desat觸發的準確性。降低Ldesat值也是尤為重要。

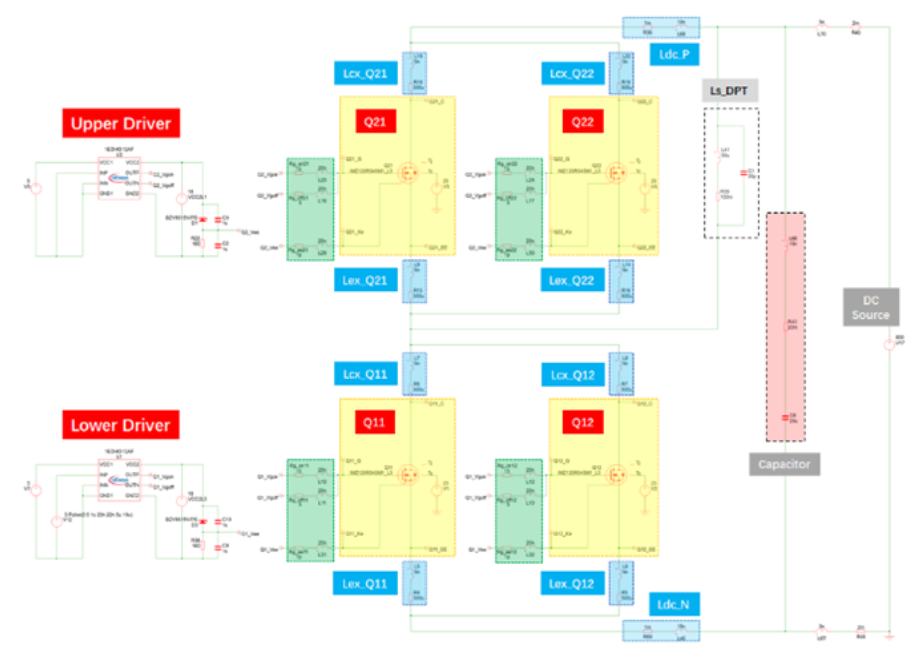

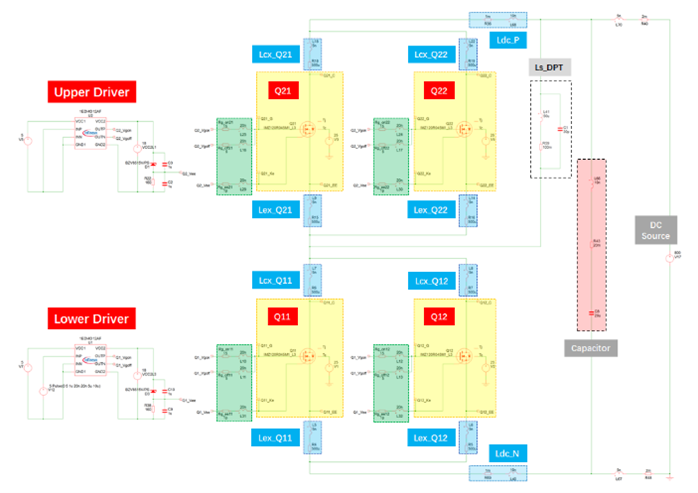

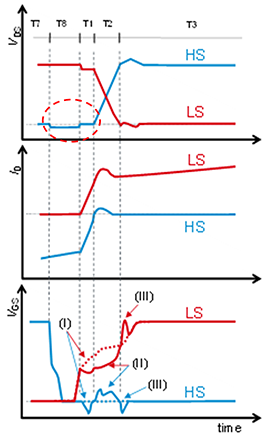

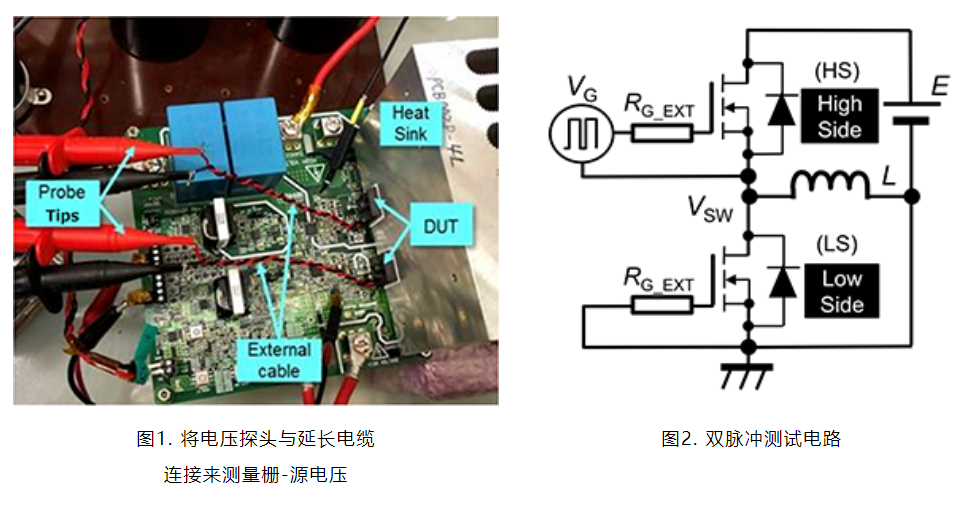

c.???? 要具有穩定和快速的短路保護,上管驅動器和下管驅動器都應該具有desat保護。半橋的短路情況主要有兩種情況。一種情況是一個開關管已經導通情況下,開通另一個開關管;另一種情況是在一個開關管短路的情況下,開通另一個開關管。對于第二種情況,比第一種情況的延遲時間長得多,是工程師必須考慮的極端因素。

?

總結:

SiC mosfet Desat保護得到越來越多工程師的重視,以上是SiC mosfet Desat保護設計基本思路。由于各個原廠的SiC mosfet 驅動的Desat保護參數會有不同,具體產品應用會有調整,如需要進一步交流請聯系富昌電子技術方案中心。

(鏈接: https://biaodan100.com/web/formview/6286e84a75a03c5d1e0da67b)

?

查看該系列其他文章,請掃碼訪問:

關鍵字: 碳化硅,SiC,SiC MOSFET,驅動設計,Desat,新能源汽車,儲能,富昌電子

?

參考文獻:

?

【1】???? AN1306: Driving SiC MOSFET Switches Using the Si828x Isolated Gate Driver

【2】???? Understanding the Short Circuit Protection for Silicon Carbide MOSFETs

【3】???? Comprehensive Analysis and Improvement Methods of Noise Immunity of Desat Protection Circuitry for High Voltage SiC MOSFETs with High dv/dt

【4】???? TND6237/D- SiC MOSFETs: Gate Drive Optimization

?

?

作為系列文章的第四篇,本文主要針對SiC MOSFET 短路Desat 保護設計做一些探討。

1.???? 什么是Desat

Desat保護是功率MOSFET和IGBT保護中很重要的概念, 下面我們用圖一所示是一個簡化的MOS剖面圖,以此來闡述退飽和發生的原因。柵極施加一個大于閾值的正壓VGS,則柵極氧化層下方會形成導電溝道,這時如果給漏極D施加正壓VDS,則源極中的電子便會在電場的作用下源源不斷地從漏極D流向源極S,這樣電流便形成了,這時電流隨DS電壓的增長而線性增長。隨著DS電壓的增大,使得柵極和硅表面的電壓差很小而不能維持硅表面的強反型,溝道出現夾斷現象,電流不再隨DS電壓的增加而成比例增長,而進入退飽和狀態(如圖二)。

在實際應用 中,退飽和現象一般發生在器件短路時,這時Vds電壓上升到母線電壓,電流一般是額定電流的幾倍。功率異常增大,結溫急劇上升,不及時關斷器件就有可能燒毀器件。多數MOSFET電流短路承受能力差而造成熱損壞,而SiC MOSFET電流的短路能力更差。那么針對SiC MOSFET的Desat保護設計就變得尤為重要了。

?

2.???? 如何進行Desat的設計

SiC MOSFET電路通常用傳感器進行在線電流檢測,進行精確的過電流保護。而Desat保護被視為第二級保護措施。在有些特殊故障情況,例如橋式直通或逆變器在濾波器前輸出端對地短路等,在線電流傳感器無法檢測到這類故障,Desat保護就成為保護功率器件重要的措施。

設計中,主要的考慮是Desat保護閾值的設定,一般應設置為保守值,以避免過早觸發。下面就通過onsemi的SiC MOSFET NTH4L020N120SC1為例,來論述下如何設計這個保護閾值。

SiC MOSFET datasheet提供“最大漏極脈沖電流”(10us單脈沖)如圖一。該電流約為器件在 125 °C時額定連續電流的 4 倍左右(onsemi NVH4L020N120SC1) 如圖二。在額定連續電流和最大漏極脈沖電流之間選擇過流保護值。過流保護閾值的計算應使用 125 °C 或 150 °C 時的 RDS_ON。傳導電流是 DESAT 引腳提供的電流。二極管壓降具有負溫度系數。保守計算,可以將 25 °C 時二極管 的正向電壓用于過流保護閾值的計算。

?????

?如圖三所示, 設置限流值的時候,可以用公式 Ilimit = (Vth – Rdamp* IDESAT – VFD)/ Rdson 來計算, 其中 Rdamp 為調壓電阻,VFD為高壓二極管的正向壓降,Rdson為 SiC MOSFET 估算結 溫下的導通電阻。 當發生短路或過流時,SiC MOSFET 漏極電流將會增加 到一個很高的值,并且器件的 Vds 將會升高到很高的值。鉗位DESAT 引腳通過內電流源給消隱電容 Cblk 充電到更高的電壓。當電壓達到過流保護閾值時,OUT 和/FAULT 均被拉低。通過選擇不同的消隱電容,可以設置DESAT 保護電消隱時間。消隱時間可以公式計算: Teblk = Cblk ?Vth / IDESAT。 不同的應用通常需要不同的關斷時間。優化的關斷時間可以最大化地發揮系統的短路 能力,同時限制 Vds 和 bus 電壓上的振蕩。

????????????? 3.???? Desat 保護設計注意事項:

a.???? SiC mosfet 的高dv/dt 是引起噪聲和desat誤觸發主要原因。在高的Vds dv/dt 作用下,高壓阻斷二極管 D寄生電容 Cdesat 引 起的電壓耦合會顯著抬高或降低陽極電壓 。 陽極電壓變化又會將 消隱電容 Cblk充電或放電到一個非預期值,并導致誤觸發或 desat 保護延遲。由于 SiC MOSFET 的高開關速度,這個問題變得更加嚴重。為了鉗制 Vdsat 電壓的上升幅度,使用一個 穩壓二極管。為了最大程度地降低 Cdesat 的影響,使用低結電容的二極管電壓阻斷非常必要。

b.??? 與高壓阻斷二極管串聯的寄生電感Ldesat也是必須考慮的因素,過高的Ldesat 會與二極管寄生電容Cdesat諧振,會影響Vdesat震蕩的最大值的變化。從而影響desat觸發的準確性。降低Ldesat值也是尤為重要。

c.???? 要具有穩定和快速的短路保護,上管驅動器和下管驅動器都應該具有desat保護。半橋的短路情況主要有兩種情況。一種情況是一個開關管已經導通情況下,開通另一個開關管;另一種情況是在一個開關管短路的情況下,開通另一個開關管。對于第二種情況,比第一種情況的延遲時間長得多,是工程師必須考慮的極端因素。

?

總結:

SiC mosfet Desat保護得到越來越多工程師的重視,以上是SiC mosfet Desat保護設計基本思路。由于各個原廠的SiC mosfet 驅動的Desat保護參數會有不同,具體產品應用會有調整,如需要進一步交流請聯系富昌電子技術方案中心。

(鏈接: https://biaodan100.com/web/formview/6286e84a75a03c5d1e0da67b)

?

查看該系列其他文章,請掃碼訪問:

關鍵字: 碳化硅,SiC,SiC MOSFET,驅動設計,Desat,新能源汽車,儲能,富昌電子

?

參考文獻:

?

【1】???? AN1306: Driving SiC MOSFET Switches Using the Si828x Isolated Gate Driver

【2】???? Understanding the Short Circuit Protection for Silicon Carbide MOSFETs

【3】???? Comprehensive Analysis and Improvement Methods of Noise Immunity of Desat Protection Circuitry for High Voltage SiC MOSFETs with High dv/dt

【4】???? TND6237/D- SiC MOSFETs: Gate Drive Optimization

?

?

電子發燒友App

電子發燒友App

評論