關鍵詞: 低功耗 , 電池壽命 , 多核技術 , 異質架構 , 智能手機

智能手機和平板終端配備雙核與四核處理器已成為一種趨勢。新一代應用處理器的CPU內核將會如何發展?在CPU內核領域占有絕對市場份額的英國ARM公司,公開了今后幾年內的多核技術發展藍圖。其戰略是通過組合使用大小各異的內核,同時兼顧高性能和低功耗。而且,異質內核的并用將成為在移動領域引進虛擬化技術的基礎。

2012-2-19 12:19:35 上傳

智能手機及平板終端用CPU內核開發商英國ARM公司2011年秋季發布的內核“Cortex-A7”,配備了很多乍一看有些奇特的功能。

Cortex-A7是一款用于100美元以下低價位智能手機的CPU內核。在設計時最注重降低耗電量和成本,因此其電力效率與美國蘋果公司“iPhone 4”中配備的ARM現有CPU內核“Cortex-A8”相比,提高至約5倍注1)。

注1)ARM公司Cortex系列產品名稱中的數字,代表該CPU內核的相對性能。而不是像蘋果公司的應用處理器“A4”和“A5”那樣,代表發布順序和產品工藝。

Cortex-A7內核徹底實現了“環保運行”,并配備了許多移動領域一般并不需要的先進技術和功能。包括虛擬化技術,用于主存儲器的ECC功能,以及40bit的物理地址擴展(LPAE:Large Physical Address Extensions)等。

即使為了徹底提高電力效率、削減電路面積,也沒有必要在用于低價位智能手機的Cortex-A7中配備虛擬化技術等。為什么ARM公司要在Cortex-A7內核中配備這些功能呢?

兼顧高性能和低功耗

之所以在Cortex-A7中大量配備先進功能,是為了實現一項稱為“big.LITTLE”的技術,該技術可在未來的智能手機中兼顧高性能和低功耗這兩個完全相反的特性。這項技術是ARM公司在發布Cortex-A7的同時推出的,將注重電力效率的內核Cortex-A7與ARM公司性能最高的CPU內核“Cortex-A15”組合使用(見圖1)。正如字面意思一樣,同時采用了性能不同的“大小”兩種內核。

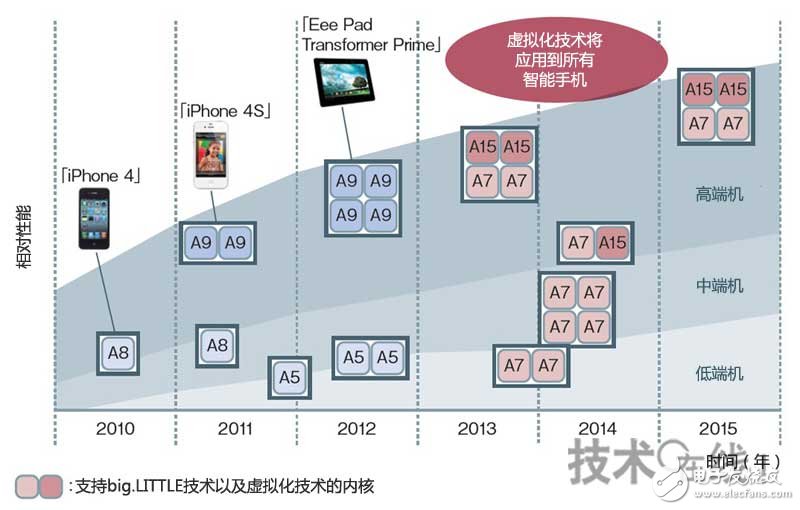

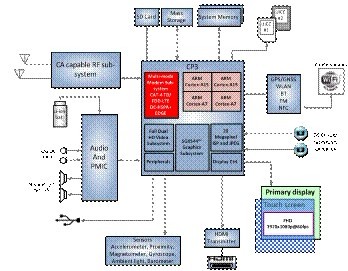

圖1:2013年以后智能手機也將采用虛擬化技術

圖中是ARM公司的CPU內核“Cortex-A”系列,在用于智能手機等便攜終端時的內核數量以及內核種類等。由本雜志根據ARM公司的資料制作而成。

big.LITTLE技術可根據電力和性能等情況,將Cortex-A15和Cortex-A7動態地分開使用。比如,像瀏覽器的屏幕渲染等需要高性能時,就會通過并行性較高、擁有較長管線的CPU內核——Cortex-A15來高速運行相關應用。反之當收發郵件等不需要太高性能時,則會切斷Cortex-A15的電源,將整個系統轉移到管線更短、電力效率較高的CPU內核——Cortex-A7中運行(圖2)注2)。

2012-2-19 12:19:35 上傳

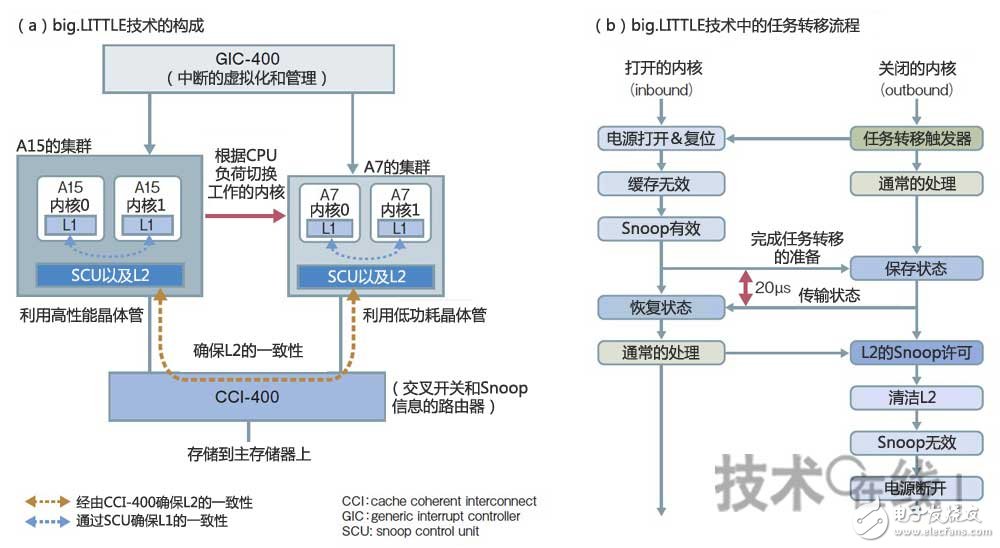

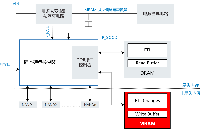

下載附件 (57.07 KB)圖2:通過異構多核實現節能的big.LITTLE技術

ARM公司的big.LITTLE技術將注重性能的“A15”與注重耗電量的“A7”這兩種CPU內核分開使用,由此可降低耗電量。CPU負荷較低時,將OS等整個系統轉移到A7內核,并切斷A15內核的電源(a、b)。由本雜志根據ARM公司的資料制作而成。

注2)在何時將某個應用和OS轉移至其他內核的判斷,與動態控制CPU內核工作頻率與電源電壓的“DVFS(Dynamic Voltage And Frequency Scaling)”以相同的原理進行。如果Cortex-A15F的電源電壓和工作頻率降至下限,就會啟動Cortex-A7并轉移系統。無法從軟件看到內核的切換。另外,big.LITTLE技術可實現同時持續驅動異質內核的SMP利用方式。

在big.LITTLE技術中,兩種內核間采用的SoC上的電源域(區域)和晶體管也不同。Cortex-A7的電路區域采用閾值電壓較高的晶體管,通過降低電源電壓來減少工作電流和漏電流。而Cortex-A15的電路區域則采用閾值電壓較低的晶體管,通過提高電源電壓來追求性能。

架構完全兼容

在big.LITTLE技術中,要想將在一個內核上運行的軟件順利轉移到其他內核上,就需要大小兩種CPU內核的架構和功能完全相同。

因此,ARM公司使Cortex-A7的架構與Cortex-A15完全兼容。除了Cortex-A7的指令集架構(ISA)與Cortex-A15完全相同外,還將Cortex-A15中首次向ARM架構引進的虛擬化技術、ECC功能和LPAE等先進功能,直接移植到了用于低價位智能手機的Cortex-A7中。注重電力效率的Cortex-A7之所以配備許多乍看并不需要的先進功能,是為了實現big.LITTLE技術。

異質架構成主流

big.LITTLE技術被定位為支撐今后智能手機和平板終端應用處理器的核心技術。ARM公司在2011年10月發布的64bit架構“ARMv8”,尚未發布支持的CPU內核,估計要在2014年以后才能配備在設備上。而big.LITTLE技術是已經可以使用的技術,不久的將來就可以實用化。

目前雙核架構的智能手機用SoC,基本上都采用可多個排列相同CPU內核的同質架構。同質架構可采用通過多個內核運行單個OS的SMP(Symmetrical Multi Processing)架構,因此從軟件來看易于使用。但從電力效率來看,即使在不需要高性能的情況下,同質架構也不得不采用配備高速架構(可發揮峰值性能)的內核,這點與異質架構相比處于不利地位。

big.LITTLE技術雖然在物理上采用異質架構,但就軟件而言多個內核看起來就像一個。可以說是融合了異質架構與同質架構兩者優點的技術。

實際上,ARM公司公開的未來應用處理器發展藍圖,從中端到高端的智能手機都并用了Cortex-A15和Cortex-A7,因此估計會采用big.LITTLE技術(見圖1)。由此,智能手機在具備高性能的同時,還可延長電池壽命。作為實現這一點的王牌,big.LITTLE技術可以說是很有用的。

通過虛擬化技術掩蓋微妙的不同

big.LITTLE技術在內部也采用了頗有意思的封裝方法。這就是利用了虛擬化技術。

雖然Cortex-A7與Cortex-A15的ISA是相同的,但是兩者在物理上是不同的內核。如果只統一ISA的話,那么內核間還是會存在無法掩蓋的微妙不同。

例如,ARM架構中有名為“CP15”的寄存區,可存儲CPU內核的ID以及緩存構成的拓撲等信息。ID中包括封裝有相關CPU內核的企業ID,以及與CPU內核產品名稱相對應的型號等。關于這些信息,Cortex-A7與Cortex-A15必然不同。

big.LITTLE技術通過應用虛擬化技術來掩蓋這些不同。如前所述,Cortex-A7與Cortex-A15都采用了虛擬化技術。因此,在這些內核上運行的OS一旦訪問CP15寄存器,根據虛擬化機構的原理,就會發生異常陷阱(Exception Trap)。于是,控制任務便會自動轉移到OS以下模式運行的虛擬化軟件(Hypervisor)上。在Hypervisor上向OS等提示與物理CP15寄存器等不同的信息,由此可以掩蓋Cortex-A7與Cortex-A15之間在硬件上的不同。

利用虛擬化原理在軟件上“欺騙”OS和應用,由此看起來就像在完全相同的內核上運行一樣。ARM公司總裁Tudor Brown表示,“big.LITTLE技術的精髓在于雖然內核的物理性質不同,但從軟件來看卻完全相同”。

在Cortex-A7中封裝虛擬化技術,不僅是為了與前面提到的Cortex-A15確保兼容性,還是為了最終通過Hypervisor消除兩個內核間的微妙差異。

加速虛擬化技術在智能手機上的普及

ARM公司在2010年9月發布了該公司首款采用虛擬化技術的內核Cortex-A15,當時未必明確了在移動領域如何利用虛擬化技術。Cortex-A15不同于此前ARM公司的CPU內核產品,專門面向該公司近年著力發展的服務器領域。因此,估計是為了滿足該領域的需求,才在Cortex-A15中采用了虛擬化技術。

然而,big.LITTLE技術公布后發現,虛擬化技術實際上可以廣泛用于智能手機和平板終端上。ARM公司表示,“最初big.LITTLE項目是與虛擬化技術分別推進的,中途我們認識到可以利用虛擬化技術,于是將兩者融合在了一起”。以big.LITTLE技術以及Cortex-A7的引進為契機,此前一直與移動領域無緣的虛擬化技術,將標配在幾乎所有的智能手機和平板終端上(見圖1)。

在集群間控制一致性

在big.LITTLE技術中,要想使某項任務順利地從一個內核轉移到另一個內核,需要在硬件方面進行改進。具體要求是在不同內核間確保緩存的一致性(Coherency)。

在緩存的一致性控制方面,ARM公司網已經有了“MPCore”多核技術,可以對CPU內核內一次緩存的一致性進行控制。不過,MPCore以最大四核的同質架構多核為前提,不支持big.LITTLE技術這種異質架構多核。

因此,ARM公司針對big.LITTLE技術這種異質架構,在SoC上新設立“集群”(Cluster)這個單位。通過MPCore技術構成的同質架構多核以集群為單位匯總,當在SoC上同時配備不同種類的CPU內核時,需要另外設置新的集群。比如,分別設置一個配備兩個Cortex-A7的集群,以及配備兩個Cortex-A15的集群(圖2)。

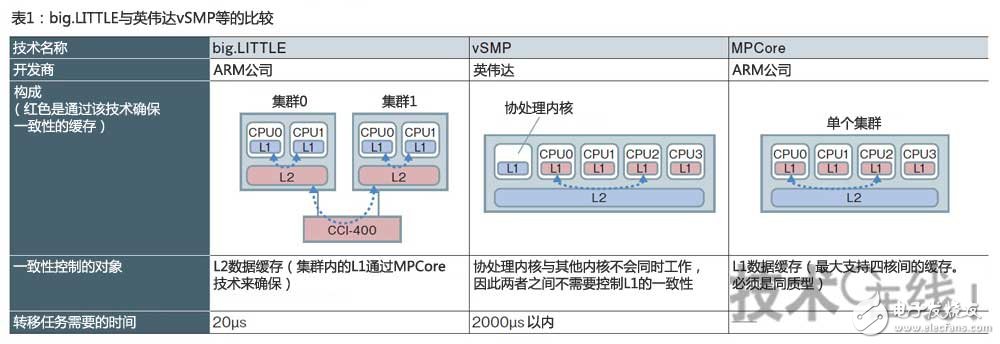

集群間的緩存一致性,采用專用的IP內核“CCI(Cache Coherent Tnterconnect)-400”來確保。CCI-400在內部配備了交叉開關。CPU內核內一次緩存的一致性由MPCore技術控制,集群間二級緩存的一致性由CCI-400控制(表1)。

2012-2-19 12:19:35 上傳

下載附件 (43.36 KB)由于可以在Cortex-A15與Cortex-A7之間維持緩存的一致性,因此big.LITTLE技術可在約20μs內完成兩個內核間的任務轉移。20μs是將CPU內核內部多項寄存器信息轉移到其他內核上所需要的時間(圖2)。利用基于CCI-400的一致性控制,二級緩存數據可與CPU內核處理并行,從而自動轉移到其他內核上。

英偉達也有類似技術

根據負荷情況將閾值電壓更高的節電型CPU內核進行切換使用的方法,其實除了ARM公司的big.LITTLE技術外還有其他技術。比如,美國英偉達(NVIDIA)在2011年9月發布的“vSMP(variable Symmetric Multi Processing)”技術。vSMP技術已經用于該公司2011年11月發布的應用處理器“Tegra 3”上,***華碩電腦(ASUSTeK Computer)的“Eee Pad TransformerPrime”等平板終端產品已經配備了“Tegra 3”。

Tegra 3配備五個“Cortex-A9”,其中一個用作“協處理內核”,采用漏電流較小的低功耗制造技術形成。雖然不能像big.LITTLE技術那樣同時采用微架構不同的內核,但在組合使用電力效率不同的內核這點上,雙方是類似的(表1)。

不過,vSMP沒有big.LITTLE技術中的集群這一概念,協處理內核以及其他內核直接共享二級緩存。內核間切換所需時間在2ms以內,遠遠高于big.LITTLE技術的20μs。估計將來會改換成配備更先進系統的big.LITTLE之類的技術。(記者:進藤 智則,《日經電子》)

來源:日經電子

電子發燒友App

電子發燒友App

評論