頻率合成器是現代無線通信設備中一個重要的組成部分,直接影響著無線通信設備的性能。頻率合成技術歷經了早期的直接合成技術(DS)和鎖相合成技術(PLL),發展到如今的直接數字合成技術(DDS)。直接數字合成技術具有分辨率高,轉換速度快,相位噪聲低等優點,在無線通信中發揮著越來越重要的作用。隨著大規模集成電路的發展,利用鎖相環頻率合成技術研制出了很多頻率合成集成電路。頻率合成器是電子系統的心臟,是決定電子系統性能的關鍵設備,隨著通信 、數字電視、衛星定位、航空航天、雷達和電子對抗等技術的發展,對頻率合成器提出了越來越高的要求。頻率合成技術是將一個或多個高穩定、高精確度的標準頻率經過一定變換,產生同樣高穩定度和精確度的大量離散頻率的技術。頻率合成理論自20世紀30年代提出以來,已取得了迅速的發展,逐漸形成了目前的4種技術:直接頻率合成技術、鎖相頻率合成技術、直接數字式頻率合成技術和混合式頻率合成技術。

本文是以如何設計一個鎖相環頻率合成器為重點,對頻率合成器做了一下概述,主要介紹了鎖相環這一部分,同時也對鎖相環頻率合成器的設計及調試等方面進行了闡述。

1總體方案設計

實現頻率合成的方法有多種,可用直接合成,鎖相環式,而鎖相環式的實現方法又有多種,例如可變晶振,也可變分頻系數M,還可以用單片機來實現等等。下面列出了幾種用鎖相法實現頻率合成的方案。

1.1方案一

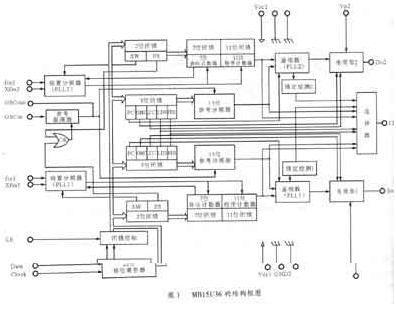

圖1.1 方案一原理框圖

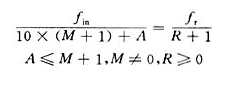

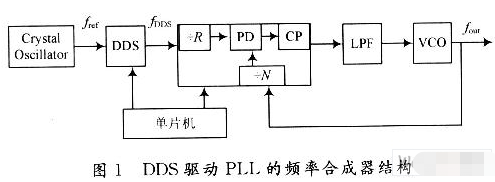

如圖2.1所示,在VCO的輸出端和鑒相器的輸入端之間的反饋回路中加入了一個÷N的可變分頻器。高穩定度的參考振蕩器信號fR經R次分頻后,得到頻率為fr的參考脈沖信號。同時,壓控振蕩器的輸出經N次分頻后,得到頻率為fd的脈沖信號,兩個脈沖信號在鑒頻鑒相器進行頻率或相位比較。當環路處于鎖定狀態時,輸出信號頻率:fo=N*fd。只要改變分頻比N,即可實現輸出不同頻率的fo,從而實現由fr合成fo的目的。其輸出頻率點間隔Δf=fr。

1.2方案二

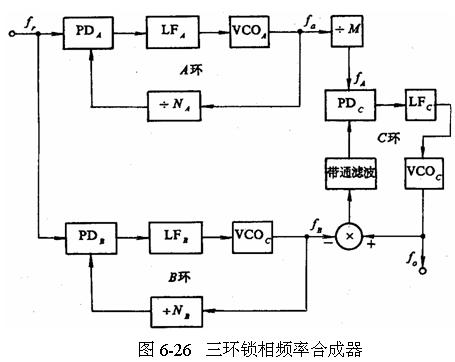

圖1.2 方案二原理框圖

如圖2.2所示,首先由晶體振蕩器產生20KHZ的頻率,即fi為20KHZ。按鍵1按下時,分頻比M為1,N的值通過單片機編程預置,并可通過“N加1鍵”和“N減1鍵”作相應改變。然后經單片機的I/O口輸出作為1~N分頻電路的數據輸入。再經過鎖相環CC4046,因此可實現輸出頻率從20K~200KHZ,頻率間隔為20KHZ。M和N的值確定后,由公式f0=fi*N/M可計算出產生頻率的具體值。經軟件編程計算后由單片機輸出顯示。同理,當按鍵2按下時,由于晶振產生的信號經過了十分頻,M為10。當按鍵3按下時,M為100,其余部分不變。通過改變M的值實現了三個不同的頻段和頻率間隔。

1.3方案三

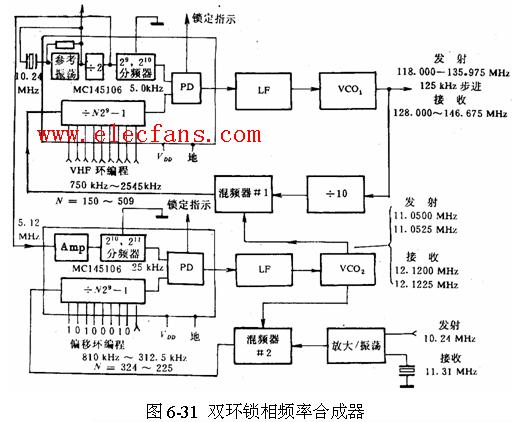

如圖2.3所示,首先由三個晶體振蕩器分別產生20KHZ,2KHZ和200HZ的頻率,然后通過三個按鍵選擇頻率通斷,被選擇的頻率送入鎖相環輸入端作為基準頻率。由此實現頻段的選擇。由1~N分頻電路實現不同的頻率間隔。可用一個十進制可逆計數器實現1~N分頻電路的數據預置。從鎖相環輸出的頻率經數字頻率計測頻后由LED顯示。

圖1.3 方案三原理框圖

1.4方案比較

上面三個方案都是鎖相式頻率合成器,本質上相同。只是實現方法上有差別。方案一采用變模分頻來實現頻率合成。方案二用一個晶振經兩次分頻分別作為鎖相環的輸入信號。方案三用了三個晶振。方案一從整體上看流程簡單明了,思路清晰,實現起來比較簡單。方案二用了單片機完成N分頻電路數據輸入和最后頻率的換算,并送至LED作顯示。方案三沒有使用單片機,采用十進制可逆計數器實現1~N分頻電路的數據預置。最后用了測頻電路將產生的頻率輸出顯示。比較之下,方案一的電路較簡單,容易實現。方案三是直接式頻率合成器。直接模擬頻率合成器容易產生過多的雜散分量以及設備量大因而體積大,價格昂貴不便于集成化是其主要缺點。優點是頻率捷變速度快,相位噪聲低。

1.5方案選擇

經過對三個方案從各方面的比較,我選擇了第一種方案。原因是方案一相對其它兩個方案較簡單,容易實現。方案二加入了單片機模塊,但一旦使用單片機就對整個電路的系統協調能力要求更高,而且對程序部分也要求很高,實現比較困難;方案三采用直接式頻率合成器,而直接模擬頻率合成器存在產生過多的雜散分量以及設備量大因而體積大,價格昂貴等缺點,因此最終我選擇了方案一來作為本次設計的方案。

2 單元模塊設計 2.1頻率源

頻率源電路如圖2.1。

采用74LS04串聯晶體振蕩電路:

圖3.1 頻率源電路圖

反饋電阻Rf主要的作用是讓74LS04芯片的反相器靜態時工作在放大狀態,晶體和電容C構成正反饋網絡。只要NOT1門或者NOT2門的輸入或者輸出電壓有微小的變化都回被晶體和電容構成的正反饋網絡反饋回去,進行放大而引起振蕩。由于NOT1門和NOT2門的振蕩輸出電壓波形不是很好,要經過NOT3門整形輸出形狀標準的方波。根據74LS04芯片的非門電壓傳輸特性,Rf在這里取值100kOhm,C=100pF,晶體的標稱頻率是2.000MHz。

2.2分頻器

1.二分頻

將D觸發器的Q非端和D端連接就可以構成一個最常用的二分頻電路。

如下圖:

圖2.2 二分頻電路

2.變模多頻

將74LS161的進位輸出端C經過反相后接到預置端LD就可以通過進位信號的變化來控制分頻器的模值。預置端直接接上四位撥碼開關。TTL的芯片引腳懸空等價于高電平,所以盡可能地簡便,省去了上拉電阻。

如下圖:

圖2.3 變模多頻電路

2.3環路濾波器

整個4046芯片的外圍元件并不多,關鍵的部分是環路濾波器,他的性能能決定整個鎖相環電路的工作性能。

環路濾波器可以采用:1.RC積分濾波器2.無源比例積分濾波器3.有源濾波器。從本次設計的要求來看,用無源比例積分濾波器比較簡單合適。如下圖:

圖2.5 環路濾波器電路

環路濾波器的截止頻率公式:

Wc=1/[(R3+R4)C2]

環路濾波器的帶寬在1KHz左右,在這里R3=50K可調,R4=1k,C2=1uf。可以通過R3調節來實現最佳鎖相性能。

2.4芯片介紹

1. 集成鎖相環HC4046

HC4046芯片是設計頻率合成器的核心。

單片集成鎖相環HC4046采用CMOS電路工藝,特點是電源電壓范圍寬(3~18 V),輸入阻抗高(約100 MΩ),動態功耗小。在電源電壓VDD=15 V時最高頻率可達1.2 MHz,常用在中、低頻段。HC4046內部集成了相位比較器Ⅰ、相位比較器Ⅱ、壓控振蕩器以及線性放大器、源跟隨器、整形電路等。

相位比較器Ⅰ采用異或門結構,使用時要求輸入信號占空比為50%。當兩路輸入信號的高低電平相異時,輸出信號為高電平,反之,輸出信號為低電平。相位比較器Ⅰ的捕捉能力和濾波器有關,選擇合適的濾波器可以得到較寬的捕捉范圍。

相位比較器Ⅱ由一個信號的上升沿控制,他對輸入信號的占空比要求不高,允許輸入非對稱波形,具有很寬的捕捉范圍。相位比較器Ⅱ的輸出和兩路輸入信號的頻率高低有關,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯“0”,反之則輸出邏輯“1”。如果兩信號的頻率相同而相位不同,當輸人信號的相位滯后于比較信號時,相位比較器Ⅱ輸出的為正脈沖,當相位超前時則輸出為負脈沖。而當兩個輸入脈沖的頻率和相位均相同時,相位比較器Ⅱ的輸出為高阻態。

壓控振蕩器需要外接電阻R1,R2和電容C1。R1,C1是充放電元件,電阻R2起到頻率補償作用。VCO的振蕩頻率不僅和R1,R2以及C1的取值有關,還和電源電壓有關,電源電壓越高振蕩頻率越高。

如圖3.6為HC4046的內部及外圍電路圖和引腳圖。其中,1腳相位輸出端,環路人鎖時為高電平,環路失鎖時為低電平。2腳相位比較器Ⅰ的輸出端。3腳比較信號輸入端。4腳壓控振蕩器輸出端。5腳禁止端,高電平時禁止,低電平時允許壓控振蕩器工作。6、7腳外接振蕩電容。8、16腳電源的負端和正端。9腳壓控振蕩器的控制端。10腳解調輸出端,用于FM解調。11、12腳外接振蕩電阻。13腳相位比較器Ⅱ的輸出端。14腳信號輸入端。15腳內部獨立的齊納穩壓管負極。

圖2.6 HC4046的內部及外圍電路圖和引腳圖

2. 集成反相器74LS04

74LS04芯片是六個獨立的反相器(6個非門)。供電電壓5V,電壓范圍在4.75~5.25V內可以正常工作。門數6,每門輸入輸出均為TTL電平(《0.8V低電平 》2v高電平),低電平輸出電流-0.4mA,高電平輸出電流8mA。每路從輸入倒相到輸出是有一定延時的(9~15ns)。其引腳圖如下:

圖2.7 74LS04引腳圖

3. 集成觸發器74LS74

74LS74芯片是雙D集成觸發器,是上升邊沿觸發的邊沿觸發器。表3.9為其功能表。它采用維持阻塞結構,是上升邊沿觸發的邊沿觸發器,即在CP脈沖上升沿(“0→1”)觸發翻轉。觸發器的次態取決于CP脈沖的上升來到之前D的狀態,即Qn+1 = D。由于電路具有維持阻塞作用,所以在CP=1 期間, D 端的狀態變化不會影響觸發器輸出的狀態。分別是直接置“0”和置“1”端。當不需要直接置“0”和置“1”時,都應置高電平。

其引腳圖如下:

圖2.8 74LS74引腳圖

其功能表如下:

圖2.9 74LS74功能表

4. 同步計數器74LS161

74LS161是四位二進制同步計數器,該計數器能同步并行預置數,異步清零,具有清零、置數、計數和保持四種功能,且具有進位信號輸出端,可串接計數使用。它的引腳圖和邏輯功能表分別見圖3.10和表3.11。

圖2.10 74LS161引腳圖

EPETCP功能

0××××清零

10××↑預置數

1111↑計數

110××保持

11×0×保持QCC=0

表2.11 74LS161功能表

2.5鎖相環的基本組成

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。

鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來。

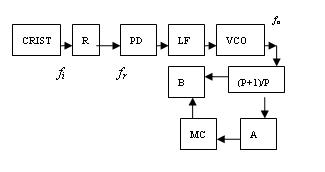

鎖相環通常由鑒相器(PD,Phase Detector)、環路濾波器(LF,Loop Filter)和壓控振蕩器(VCO,Voltage Controlled Oscillator)三部分組成,鎖相環組成的原理框圖如下圖所示。

SHAPE * MERGEFORMAT

圖212 鎖相環組成的原理框圖

鎖相環中的鑒相器又稱為相位比較器,它的作用是檢測輸入信號和輸出信號的相位差,并將檢測出的相位差信號轉換成uD(t)電壓信號輸出,該信號經低通濾波器濾波后形成壓控振蕩器的控制電壓uC(t),對振蕩器輸出信號的頻率實施控制。

1. 鑒相器

鑒相器(PD)是一相位比較裝置,用來檢測輸出信號 與輸入信號 之間的相位差 ,并把 轉化為電壓 輸出, 稱為誤差電壓,通常 為一直流量或一低頻交流量。

鑒相器是鎖相環中很關鍵的一個部件,因此對鑒相器需提出一些技術要求。其主要技術指標有:(1)鑒相特性形狀;(2)鑒相增益Kd;(3)輸入信號的漏泄;(4)工作頻率及輸入、輸出阻抗;(5)對頻率的鑒別能力。

構成鑒相器的電路形式很多,有如下分類:

(1)二極管平衡鑒相器

(2)異或門鑒相器

(3)電壓開關式鑒頻鑒相器

(4)模擬乘法鑒相器

2. 環路濾波器

LF為一低通濾波電路,其作用是濾除因PD的非線性而在 中產生的無用的組合頻率分量及干擾,產生一個只反映 大小的控制信號 。它除了有低通濾波的作用外,還可借助于合理的選擇各元件參數來校正環路的功能。對環路的捕捉、穩定,噪聲的濾除,環路帶寬等等都有關系,是一中很重要惡毒器件。

按照反饋控制原理,如果由于某種原因使VCO的頻率發生變化使得與輸入頻率不相等,這必將使 與 的相位差 ,發生變化,該相位差經過PD轉換成誤差電壓 ,此誤差電壓經LF濾波后得到 ,由 去改變VCO的振蕩頻率使趨近于輸入信號的頻率,最后達到相等。環路達到最后的這種狀態就稱為鎖定狀態,當然由于控制信號正比于相位差,即

因此在鎖定狀態, 不可能為0,換言之在鎖定狀態 與 仍存在相位差。

3. 壓控振蕩器

VCO是本控制系統的控制對象,被控參數通常是其振蕩頻率,控制信號為加在VCO上的電壓,故稱為壓控振蕩器,也就是一個電壓一頻率變換器,實際上還有一種電流一頻率變換器,但習慣上仍稱為壓控振蕩器。任何一種振蕩器,如LC振蕩器,RC振蕩器,多諧振蕩器等,均可構成壓控振蕩器。壓控頻率特性如圖3.13所示。

圖2.13 VCO壓控頻率特性

該曲線斜率稱壓控靈敏度或稱調頻靈敏度記作 ,其單位為rad/s·v。VCO瞬時角頻率 與 的關系式為: = +

VCO瞬時相位為: = t +

式中:VCO固有相位為:

VCO附加相位為: =

上式表明VCO的輸出量 是輸入量 的積分式,或者說VCO是一個積分環節。

4. 鎖相環的工作原理

相環中的鑒相器通常由模擬乘法器組成,利用模擬乘法器組成的鑒相器電路如圖3.14所示。

圖2.14 鑒相器電路

鑒相器的工作原理是:設外界輸入的信號電壓和壓控振蕩器輸出的信號電壓分別為:

式中的ω0為壓控振蕩器在輸入控制電壓為零或為直流電壓時的振蕩角頻率,稱為電路的固有振蕩角頻率。則模擬乘法器的輸出電壓uD為:

用低通濾波器LF將上式中的和頻分量濾掉,剩下的差頻分量作為壓控振蕩器的輸入控制電壓uC(t)。即uC(t)為:

式中的ωi為輸入信號的瞬時振蕩角頻率,θi(t)和θO(t)分別為輸入信號和輸出信號的瞬時位相,根據相量的關系可得瞬時頻率和瞬時位相的關系為:

即

則,瞬時相位差θd為:

對兩邊求微分,可得頻差的導數為:

上式等于零,說明鎖相環進入相位鎖定的狀態,此時輸出和輸入信號的頻率和相位保持恒定不變的狀態,uc(t)為恒定值。當上式不等于零時,說明鎖相環的相位還未鎖定,輸入信號和輸出信號的頻率不等,uc(t)隨時間而變。

因壓控振蕩器的壓控特性,該特性說明壓控振蕩器的振蕩頻率ωu以ω0為中心,隨輸入信號電壓uc(t)的變化而變化。該特性的表達式為:

上式說明當uc(t)隨時間而變時,壓控振蕩器的振蕩頻率ωu也隨時間而變,鎖相環進入“頻率牽引”,自動跟蹤捕捉輸入信號的頻率,使鎖相環進入鎖定的狀態,并保持ω0=ωi的狀態不變。

3 總體電路調試

用仿真軟件按照原理圖接好線路,給電路板接上電源,然后觀察示波器輸出,進行調試。

3.1 VCO及頻率源部分調試

首先檢查電路,未接線之前就調好直流穩壓電源的輸出電壓:5V。

因為VCO由PLL頻率合成器來生成信號輸出,所以PLL的絕大部分性能都是由它決定的。如果VCO未能正確地運作,則許多性能參數都將受到影響。在調試階段的初期應對VCO進行測試,以確保其提供預定的頻率范圍、增益和輸出電平。如果只是想測試VCO,則需對PLL進行修正,以取消閉環控制。“斷開”環路的一種常用方法是使R3開路,并在C4的兩端施加一個實驗室電源,這樣就使得VCO調諧電壓能夠在期望的范圍內改變。當調諧電壓改變時,應在一個頻率計數器(或頻譜分析儀)上監視VCO的工作頻率。記錄若干調諧電壓設定值條件下的VCO工作頻率。

本頻率源是一個石英晶體多諧振蕩器組成的,可通過調節可變電容使74LS04內部的反相器工作在放大區使得電路起振,這時用萬用表來測試晶振兩端電壓使其達到2.5V(因為電源電壓是5V)左右即表明頻率源在正常工作。

3.2 分頻器調試

PLL設計往往會忽視數字分頻器的規格。分頻器的工作狀況一般是良好的,但由于不能始終保持這種良好的工作狀態,因此PLL有時無法獲得預期的工作性能。所有的分頻器都具有針對最大輸入頻率(FMAX)和最小輸入電平的規格。在一個忽視了FMAX規格的設計中,分頻器將“丟失脈沖”。閉環隨后將檢測出VCO的頻率過低并使調諧電壓進一步走高。分頻器將丟失更多的脈沖,而且,環路將試圖把VCO提升至一個更高的頻率上。環路將進入一個“閉鎖”狀態,此時,VCO調諧電壓被保持在正電源電壓上。這里,在工作上容易使人產生誤解的問題是反饋分頻器不僅必須對VCO的預期輸出進行分頻,而且還必須對VCO在鎖定和解鎖條件下有可能產生的最高頻率進行正確的分頻。為了使環路可靠地運行,在啟動或信道變更時所遇到的瞬變條件不得引發反饋極性反轉。

3.3 整體電路板調試

這是基于鎖相環的調試。可變分頻器調試完畢后接入整個電路。此時要使鎖相環上鎖,需要調節變阻器致使環路濾波器帶寬得到調節,解決失鎖現象等。如果電路原理及參數設置沒有錯的話,這時將示波器接到輸出端觀察輸出波形,當輸出的方波在1.000MHz-10.000MHz之間以1.000MHz為頻率間隔可調節地穩定輸出時,頻率合成器才正常工作。

3.4調試結果及原因分析

(1) 經過調試,得出波形是正弦波:

理論上,由晶振產生的是方波,那么最后輸出的也應該是方波,經過再次調試,得出是74LS161芯片的原因,產生頻率太高導致74LS161沒法正常工作,最后把原來的74LS161芯片換成HC74LS161芯片,再進行調試,果然輸出的方波。

(2) 當需要變換頻率時,即從1M到10M的時候,撥碼器雖按照要求撥動了,但輸出波形的頻率并不像理論上那樣穩定,而是會跳動的。原因就是撥碼器沒法正常工作。撥碼器不能正常工作的原因是沒有接上拉電阻。接上上拉電阻后,撥碼器果然好用了好多。當然波形并不是那么完美,畢竟本次頻率合成器的制作都很簡單,沒有做的太復雜,而且元器件的參數也有影響。

4軟件介紹

本次設計中用到的畫圖軟件為Protel 99,Protel 99是一種很適用的畫圖軟件,下面對Protel 99做了一個簡單的介紹。

Protel 99采用全新的管理方式,即數據庫的管理方式。Protel 99 是在桌面環境下第一個以獨特的設計管理和團隊合作技術為核心的全方位的印制板設計系統。所有Protel99設計文件都被存儲在唯一的綜合設計數據庫中,并顯示在唯一的綜合設計編輯窗口。

Protel 99軟件沿襲了Protel以前版本方便易學的特點,內部界面與Protel 98大體相同,新增加了一些功能模塊。Protel公司引進了德國INCASES公司的先進技術,在Protel99中集成了信號完整性工具,精確的模型和板分析,幫助你在設計周期里利用信號完整性分析可獲得一次性成功和消除盲目性。Protel99容易使用的特性就是新的“這是什么” 幫助。按下任何對話框右上角的小問號,然后選擇你所要的信息。現在可以很快地看到特性的功能,然后用到設計中,按下狀態欄末端的按鈕,使用自然語言幫助顧問。

所有Protel99設計文件都被儲存在唯一的綜合設計數據庫中,并顯示在唯一的綜合設計編輯窗口。在Protel99中與設計的接口叫設計管理器。使用設計管理器,可以進行對設計文件的管理編輯、設置設計組的訪問權限和監視對設計文件的訪問。

組織設計文件過去組織和管理40個或更多的原理圖、PCB、Gerber、Drill、BOM和DRC文件,要花費幾天的時間,而Protel99把設計文件全部儲存在唯一的設計數據庫。

在設計數據庫內組織按分層結構文件夾建立的文件顯示在右邊的個人安全系統設計數據庫有一文件夾叫設計文件,這個文件夾中是主設計文件(原理圖和PCB),還有許多的子文件夾,包括了PCB裝配文件、報告和仿真分析。這里對在設計數據庫中創建文件夾的分層深度沒有限制。

設計數據庫對存儲Protel設計文件沒有限制你能輸入任何類型的設計文件進入數據庫,如在MS Word書寫的報告、在MS Excel準備的費用清單和AutoCAD中制的機械圖。簡單雙擊設計數據庫里的文件圖標,在適當的編輯器打開文件,被更新的文件自動地保存到設計數據庫。MS Word和Excel文件可以在設計管理器中直接編輯。

在綜合設計數據庫中用Protel99的設計管理器管理設計文件是非常輕松的。設計管理器的工作就象MS Windows的文件管理器一樣,可用它來導航和組織設計數據庫里文件。使用設計管理器在設計數據庫創建分層結構的文件夾,使用標準文件操作命令來組織這些文件夾內設計文件。

設計管理器的心臟就是左邊的導航面板。面板顯示的樹狀結構是大家熟悉的Protel軟件特性。在Protel99中,這個樹不僅僅顯示的是一個原理圖方案各文件間的邏輯關系,它也顯示了在設計數據庫中文件的物理結構。在導航樹中活躍的文件夾是PCB裝配文件夾。如同Windows文件管理器,設計管理器在右邊顯示這個文件夾的內容。

設計管理器與Windows文件管理器的不同之處是在右邊還顯示已經打開的文件。

打開文件只要在導航樹中單擊所要編輯的文件名,或者雙擊右邊文件夾中的圖標。

在設計數據庫中打開的各個文件用卡片分隔顯示在同一個設計編輯窗口,使得非常容易知道當前工作到哪里,特別在大的設計中。要一起觀察不同的文件可以將設計編輯窗口拆分為多區域。

5總結

本次課程設計所設計的是一款鎖相頻率合成器,其最關鍵的部分應該鎖相環部分,最關鍵的技術當然是鎖相技術,鎖相環里面最關鍵的環路濾波器。通過本次課程設計掌握了鎖相環頻率合成器的基本原理,通過分析了集成鎖相環芯片HC4046的工作特性,并從集成鎖相環芯片HC4046的一個應用實例得到很多知識。實現過程是:晶體振蕩器產生一個固定頻率2M,經2分頻作為鎖相環的一個輸入信號1MHZ,由74LS161實現1到10分頻作為另一個輸入信號。鎖相環在工作時其鎖定時間小于2 ms。輸出150MHz-175MHz,且頻率間隔為5kHz。其中1到10分頻是通過計數器74LS161而獲得,變換的時候可以通過撥動撥碼器來達到自己想要的分頻率。

電子發燒友App

電子發燒友App

評論