LOGIC下,從剛才打開的對(duì)話框里選Design 再選,Send netlist 將網(wǎng)絡(luò)表導(dǎo)到PCB 里面,在PCB 里面按需要放好,元件后,再選Setup---》ECO Prefs 進(jìn)到ECO模式下,這樣

2008-07-21 17:37:54

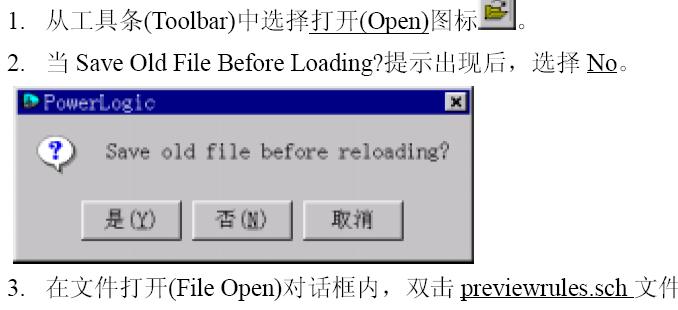

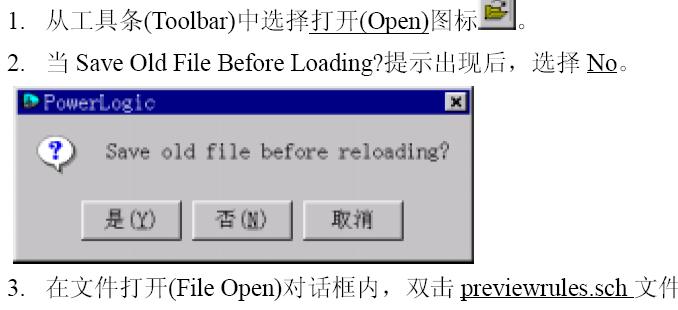

PowerLogic_Tutorial

2012-08-20 14:57:06

PowerLogic_v11教程目錄

2012-08-20 14:58:09

PowerLogic軟件培訓(xùn)

2012-08-20 15:00:31

powerlogic教程

2012-08-20 14:59:12

在生成網(wǎng)表時(shí)報(bào)Error,【ALG0030】Unable to read design "d:\PCB\test\test.dsn"為什么呢,請(qǐng)高手說明,謝謝

2013-03-26 16:04:00

生成網(wǎng)表出問題,,求助!

2017-06-14 13:00:51

您好,我有一個(gè)用于2端口無源組件的SPICE / Spectre子電路。我試圖通過網(wǎng)表導(dǎo)入和Netlist include元素在ADS 2011.10中使用它。我已按照文檔“Netlist

2019-07-04 08:06:30

AD14版的原理圖選項(xiàng)design->netlistfordocumnet中怎么沒有pads選項(xiàng)?怎樣生成.asc網(wǎng)表,導(dǎo)入到pads中?

2015-01-07 16:37:54

AD6中加載網(wǎng)表生成PCB

2015-12-20 13:08:20

AD9在原理圖繪制完之后如何生成網(wǎng)表文件?在PROTEL99SE里面我就可以看到相關(guān)選項(xiàng) 設(shè)計(jì)\GREATE NET,AD9就沒有這個(gè)選項(xiàng),另外AD9里面也沒有電氣規(guī)則檢測選項(xiàng)。

2012-12-25 10:16:31

本帖最后由 菜鳥級(jí)別 于 2015-9-7 22:04 編輯

AD生成OrCad/PCB2網(wǎng)表,第一次導(dǎo)入allgero沒問題,但是更新原理圖(有添加元件)重新生成網(wǎng)表,再導(dǎo)入allegro,沒有報(bào)錯(cuò),allegro中的元件清單還是和之前的一樣,沒有變化,請(qǐng)高手幫忙解釋下。

2015-09-07 21:31:40

在WIN7系統(tǒng)下安裝了allegro,在從原理圖導(dǎo)出網(wǎng)表時(shí),不會(huì)報(bào)錯(cuò),也不會(huì)生成網(wǎng)表文件,我按照附件的安裝方式安裝的,請(qǐng)各位大俠幫忙解答一下!

2013-03-25 19:32:45

您好我有一個(gè)模塊的EDIF網(wǎng)表(由Vivado 2017.4中的第3方生成)。我沒有模塊源verilog。我有加密模塊的行為模型,我有一個(gè)行為模型的測試平臺(tái)。行為模擬在Modelsim中運(yùn)行。行為

2018-11-07 11:34:55

在生成網(wǎng)表文件時(shí)一直提示這兩個(gè)錯(cuò)誤,怎么解決的,求大神指導(dǎo)

2019-02-21 03:23:31

1、 orcad軟件怎么生成allegro網(wǎng)表、ad網(wǎng)表、pads網(wǎng)表?答:首先,通過orcad軟件打開原理圖,選中原理圖的根目錄,點(diǎn)擊Tools-Creat Netlist,或者是點(diǎn)擊菜單欄上N

2019-08-26 17:46:14

PADS-PowerLogic

2012-08-20 14:55:54

PCB設(shè)計(jì)及Powerlogic入門基礎(chǔ)

2012-08-17 14:48:09

8.2.1網(wǎng)表網(wǎng)表也稱網(wǎng)絡(luò)表,顧名思義,就是網(wǎng)絡(luò)連接和聯(lián)系的表示,其內(nèi)容主要是電路圖中各個(gè)元件類型、封裝信息、連接流水序號(hào)等數(shù)據(jù)信息。在使用Altium]

2020-04-24 08:00:00

表格式,再導(dǎo)入到PCB工程中。二、原理圖網(wǎng)表生成方法一(第一方):使用OrCADCapture打開原理圖單擊按鈕或執(zhí)行菜單命令Tools/create Netlist…,彈出對(duì)話框,選擇PCB

2018-07-31 14:15:07

Renumber PowerLogic自動(dòng)編位號(hào)工具

2008-07-21 17:33:51

本帖最后由 糖果. 于 2016-12-19 15:22 編輯

Altium Designer13.3.4導(dǎo)出網(wǎng)表,allegro16.6通過other導(dǎo)入導(dǎo)入后出現(xiàn)error生成了device,setup中路徑已添加,求問如何解決

2016-12-19 14:32:45

第一個(gè)可以生成網(wǎng)表,這是第二個(gè)不能生成網(wǎng)表。查了一下是器件屬性Device 幾個(gè)器件重復(fù),但第一例子器件device重復(fù)就可以導(dǎo)出網(wǎng)表,不知道為什么?使用的均為orcad下PCB Editor 導(dǎo)出

2019-03-04 07:35:18

allegro第三方生成網(wǎng)表如何實(shí)現(xiàn)與allegro pcb交互設(shè)計(jì)

2014-10-28 10:37:14

生成網(wǎng)表文件的時(shí)候 報(bào)“無效指針”錯(cuò)誤,試了網(wǎng)上在cmd里修改注冊表的方法 都沒用,請(qǐng)問是什么問題,應(yīng)該怎么解決

2020-08-13 09:02:42

cadence allegro 16.5軟件生成網(wǎng)表時(shí)出現(xiàn)這些,求大神給予解答

2015-12-16 13:32:22

cadence16.6生成網(wǎng)表后原理圖與PCB不能交互,交互功能勾選了,原理圖改網(wǎng)絡(luò)重新生成網(wǎng)表PCB的網(wǎng)絡(luò)也會(huì)相應(yīng)改過,PCB選擇器件高亮原理圖相應(yīng)的也會(huì)有關(guān)聯(lián),但是在原理圖選擇元器件PCB不會(huì)

2021-09-09 17:10:24

be identicalon all sections of the part.生成網(wǎng)表的時(shí)候,這個(gè)問題如何解決?我的U3是分成三個(gè)部分的(A,B,C),我覺得主要問題估計(jì)是在Conflicting

2012-05-02 14:37:51

剛開始使用allergo,準(zhǔn)備用orcad導(dǎo)出網(wǎng)表,DRC已經(jīng)過了,pcb footprint也都填好了,allergo路徑也設(shè)置了,但是導(dǎo)出的時(shí)候出現(xiàn)了#77 ERROR(SPCODD-77

2017-06-25 21:25:28

求助!orcad生成網(wǎng)表的時(shí)候出現(xiàn)錯(cuò)誤,DRC檢測只有警告,網(wǎng)表文件能生成但導(dǎo)入不了查看錯(cuò)誤信息是{ Using PSTWRITER 16.6.0 d001Aug-21-2018 at 17:28

2018-08-22 15:26:41

1、ORCAD軟件打開原理圖,選中原理圖的根目錄,點(diǎn)擊Tools-Creat Netlist,或者是點(diǎn)擊菜單欄上N的圖標(biāo),如下圖所示,即可產(chǎn)生網(wǎng)標(biāo)。2、Allegro第一方網(wǎng)表如上圖操作以后。彈出

2018-11-05 15:04:04

原理圖和封裝都畫好了,層次原理圖,ERC沒有問題~~生成網(wǎng)表的時(shí)候,子層次圖中,+3.3V節(jié)點(diǎn)沒有了,如果將部分+3.3V節(jié)點(diǎn)換成+3.3V_P,則顯示+3.3V_P節(jié)點(diǎn)(或+3.3V,顯示數(shù)目比較

2011-12-30 15:20:26

Cadence16.6中OrCAD Capture原理圖生成Netlist時(shí)候出現(xiàn)如下圖問題,請(qǐng)大神告知原因以及如何解決。 錯(cuò)誤信息為: #1 ERROR(ORCAP-36020): Unable

2017-12-23 15:54:39

oracd capture cis 生成網(wǎng)表時(shí),我確定所有路徑都是沒問題的,而且也沒有非法字符,但是按了creat netlist的確定時(shí),一直不出現(xiàn)這個(gè)窗口,也沒有生成任何bat文件。后來查看

2016-06-25 13:02:03

生成pads2k網(wǎng)表的時(shí)候顯示這種錯(cuò)誤

2019-06-20 05:35:09

相匹配,應(yīng)在源網(wǎng)表中更改SIM_DEVICE的值。未能正確設(shè)置SIM_DEVICE將阻止此設(shè)計(jì)生成比特流。嚴(yán)重警告[Netlist 29-335]'IDELAYE2'類型的實(shí)例'u_idelaye1'可能

2018-10-29 14:17:21

中,只要你使用邏輯綜合將RTL轉(zhuǎn)換為門級(jí)網(wǎng)表,那么你必然需要使用FEC工具進(jìn)行RTL和門級(jí)網(wǎng)表等價(jià)性比對(duì)。下圖是一個(gè)FEC RTLvs Netlist等價(jià)性比對(duì)的示例。看起來不同,實(shí)際功能是一致

2022-07-22 14:56:37

\Gerbers\ 導(dǎo)入方法和導(dǎo)入NC Drill一樣4、使用Tool/Netlist/Extract 提取導(dǎo)入的Gerber 的網(wǎng)絡(luò)(將相連的Track 視為同一網(wǎng)絡(luò),網(wǎng)絡(luò)名隨機(jī)生成)。如果不導(dǎo)入網(wǎng)表將不

2012-09-10 16:04:56

我只是按照示例制作一個(gè)簡單的GPIO。生成網(wǎng)表時(shí),會(huì)產(chǎn)生如下錯(cuò)誤。錯(cuò)誤:EDK:4074- 實(shí)例:MYaxi_gpio_0,PORT:GPIO_IO,連接器:axi_gpio_0_GPIO_IO-

2019-02-20 10:45:45

PADS9.5 logic-生成網(wǎng)絡(luò)PCB netlist方法

2014-11-05 22:50:51

親愛的先生現(xiàn)在我嘗試使用PADS Maker工具。我是PCB布局的初學(xué)者。那么,是否可以將第三方工具生成的原理圖網(wǎng)表導(dǎo)入PADS Maker?謝謝。以上來自于谷歌翻譯以下為原文Dear sirNow

2018-10-23 11:39:03

在使用candence 編譯生成網(wǎng)表時(shí)出現(xiàn)#1035 error :Cannot find a ppt part that matches the instance properties應(yīng)該怎么解決

2010-01-14 22:35:09

嗨,Vivado的新手問題;是否有可能為后綜合模擬和/或后PAR網(wǎng)表模擬生成VHDL或Verilog網(wǎng)表?謝謝,埃里克

2019-11-11 07:33:05

你好,我現(xiàn)在正在學(xué)習(xí)如何使用Vivado。現(xiàn)在我在Vivado中“實(shí)現(xiàn)”并點(diǎn)擊“Open Implementation Design”后獲得一個(gè)網(wǎng)表。這是我的網(wǎng)表圖片。我可以知道ZYNQ芯片上的確

2018-10-19 14:38:09

你好,我目前正在開發(fā)一些VHDL項(xiàng)目,我們生成可重用的網(wǎng)表似乎很有趣。遺憾的是,我沒有找到從Xilinx ISE 10.1生成這些文件的信息。我需要?jiǎng)?chuàng)建* .ngc和* .xco文件,然后將它們重新

2018-10-08 11:11:22

用OrCAD畫好原理圖后我們需要導(dǎo)出網(wǎng)表便于后續(xù)導(dǎo)入Allego畫PCB(AD這點(diǎn)不同,可直接生成PCB文件)。Tools-Create Netlist,出現(xiàn)以下界面:點(diǎn)擊確定即可生成第一方網(wǎng)表。選擇Other項(xiàng):

2022-02-15 07:33:39

嗨, 我有一個(gè)edif網(wǎng)表,我必須將其轉(zhuǎn)換為ngc網(wǎng)表。我該怎么做謝謝poorna

2019-10-24 08:12:41

我的EDK為9.1i,在為AD添加GPIO之后,嘗試將輸入端口命名為AD_GPIO_in,然后生成網(wǎng)表,但始終存在錯(cuò)誤:錯(cuò)誤:MDT-INST:AD端口:GPIO_in連接器

2018-09-28 16:56:06

一.第三方網(wǎng)表的導(dǎo)出 點(diǎn)擊后(生成的netlist就是第三方網(wǎng)表,第三方網(wǎng)表的格式有.txt .tel等多種格式,但都能用記事本打開) 點(diǎn)擊保存,得到netlist.txt文檔,即第三方網(wǎng)表二

2016-09-14 10:32:32

有沒有人知道在使用Synplify生成edif網(wǎng)表時(shí)如何將LUT用于多路復(fù)用器而不是DSP48模塊?謝謝。以上來自于谷歌翻譯以下為原文Does anybody know how can I use

2018-10-15 11:46:22

各位大俠,我在用orcad生成網(wǎng)表時(shí),軟件無法正常退出,但其實(shí)網(wǎng)表文件已經(jīng)生成了,這個(gè)怎么解決?謝謝本來一直沒有理會(huì)這個(gè)問題,直接那生成的網(wǎng)表去布局布線,但現(xiàn)在需要back annonate,這個(gè)步驟只能在網(wǎng)表正常生成后做,所以需要急需解決這個(gè)問題。

2011-12-18 11:14:55

請(qǐng)問在生成網(wǎng)表文件時(shí)出現(xiàn)錯(cuò)誤 Port has a type which is inconsistent with other ports on the net USART_RX SCHEMATIC1, STM3210E-MCU(2.60, 2.90)是怎么回事啊?我該怎樣修改,謝謝!

2013-01-07 11:02:15

用PADS生成網(wǎng)表時(shí)出現(xiàn)的問題,求高手解答,謝謝。PCB Net List Errors Report - FIRST.sch - Sat Feb 11 19:51:39

2012-02-11 20:08:33

一.第三方網(wǎng)表的導(dǎo)出 點(diǎn)擊后(生成的netlist就是第三方網(wǎng)表,第三方網(wǎng)表的格式有.txt .tel等多種格式,但都能用記事本打開) 點(diǎn)擊保存,得到netlist.txt文檔,即第三方網(wǎng)表二

2016-09-16 16:16:58

pads如何生成IPC網(wǎng)表與gerber比對(duì)?

2019-04-16 07:35:16

用MAXPLUSII或QUARTUS多次編譯同一設(shè)計(jì)生成的帶延時(shí)的網(wǎng)表文件中的延時(shí)是否一樣?

2019-09-03 01:47:27

請(qǐng)問如何在allegro中導(dǎo)入orcad 生成的網(wǎng)表?誰知道詳細(xì)的步驟,如何把DSN導(dǎo)成NETLIST的形式呢?請(qǐng)高手幫幫呀。。

2011-09-29 22:34:58

請(qǐng)問版主:POWERLOGIC如何從原理圖更新PCB?在畫PCB過程中,發(fā)現(xiàn)原理圖有的地方錯(cuò)了,如果重新導(dǎo)入網(wǎng)絡(luò)表,那前期工作就白費(fèi)了,又要重新做,能不能從原理圖更新PCB呢?PROTEL99SE有這個(gè)功能啊,不知POWERPCB有無此功能?怎么做?

2008-11-04 22:19:19

如題 求解想要進(jìn)行后仿真 可是網(wǎng)表和延時(shí)文件無法生成

2015-10-30 15:29:41

orcad &protel 轉(zhuǎn)powerlogic 的工具

2006-05-28 00:58:16 48

48 powerlogic教程下載

2007-11-28 09:29:44 0

0

APD不需重新Import Netlist,要如何直接修改Netname

1. 前言

一般APD設(shè)計(jì)檔的Netlist都是3rd-Party格式,而不是來自于schematic (OrCAD capture, ConceptHDL等)的輸出netlist,因此若

2009-09-06 11:10:29 0

0 歡迎使用 PowerLogic 教程。本教程描述了 PADS-PowerLogic 的各種功能和特點(diǎn)、以及使用方法。這些功能包括:· 如何在 PowerLogic 中使用工作區(qū)(Working Area)。· 如何在 PADS 的元件庫

2010-08-12 17:37:36 0

0 powerlogic快捷鍵

設(shè)置通孔顯示模式:D+O

設(shè)置銅只顯示外框形式:P+O

改變當(dāng)

2007-11-28 09:49:36 1396

1396 如何使用PowerLogic的OLE功能

PowerLogic 現(xiàn)在使用先進(jìn)的目標(biāo)連接與嵌入(OLE) (Object Linking andEmbedding)技術(shù),它可以在Windows 95和Windows NT 之類的

2008-03-12 12:42:44 1944

1944

目錄: 1、一步一步學(xué)用powerlogic/powerpcb(連載,建立元件) 2、SI 高速電路設(shè)計(jì)之第二章(傳輸線理論) 3、PCB 設(shè)計(jì)基礎(chǔ)知識(shí)(trojan 提供) 4、本期特別文章一:PCB 設(shè)計(jì)指引 5、本期特

2011-04-11 10:20:16 0

0 powerlogic2,有需要的朋友下來看看

2016-07-29 18:08:19 0

0 網(wǎng)表輸入有兩種方法,一種是使用PowerLogic的OLE PowerPCB Connection功能,選擇Send Netlist,應(yīng)用OLE功能,可以隨時(shí)保持原理圖和PCB圖的一致,盡量減少出錯(cuò)的可能。

2019-12-13 17:34:22 1323

1323

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論