本文為大家帶來cadence allegro pcb layout詳細教程 。

工程師的巨大福利,首款P_C_B分析軟件,點擊免費領取

一、用Design Entry CIS(Capture)設計原理圖

1、創建工程

file--》new--》project ;輸入工程名稱,指定工程放置路徑;

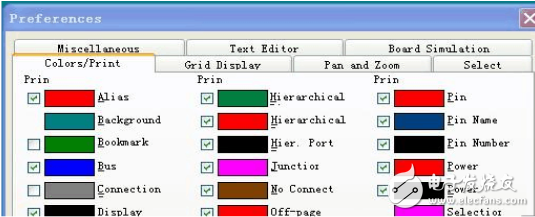

2、設置操作環境Options--》Preferencses:

顏色:colors/Print

格子:Grid Display

雜項:Miscellaneous

常取默認值

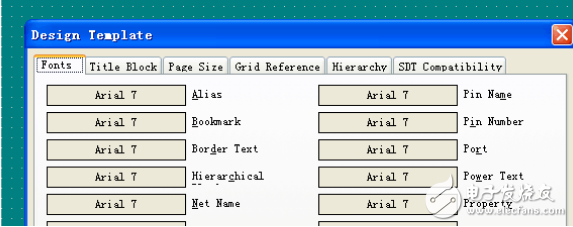

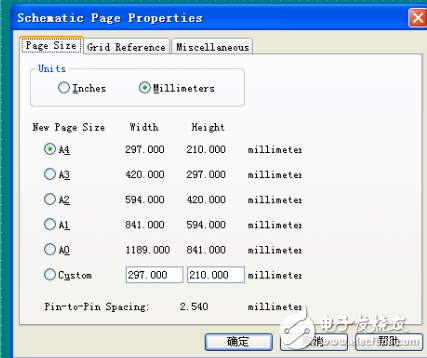

3、配置設計圖紙:

設定模板:Options--》Design Template:(應用于新圖)

設定當前圖紙Options--》Schematic Page Properities

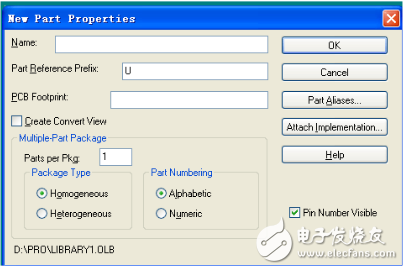

4、創建元件及元件庫

File--》New Library --》選擇要添加到的工程

Design --》New Part.(或者在Library處右擊選擇New Part)

(1)Homogeneous:復合封裝元件中(多個元件圖組成時)每個元件圖都一樣(default適用于標準邏輯)

(2)Heterogeneous:復合封裝元件(多個元件圖組成時)中使用不一樣的元件圖(較適用于大元件)

一個封裝下多個元件圖,以View ext part(previous part)切換視圖 元器件封裝:

(1)place --》line畫線,用來畫封裝外形;

(2)place--》pin放置管腳;放單個或多個;

不同類型的管腳選擇的type不同;

5、繪制原理圖

(1)放置電器

Place--》part ;可以從設計緩存中,活著元件庫,軟件自帶元件庫,中選擇;選擇Add Library增加元件庫;

電源和地(power gnd)從右邊工具欄中選擇;

(2)連接線路 wire

bus:與wire之間必須以支線連接,并以網標(net alias)對應(wire:D0,D1.。。.D7;bus:D[0..7]) 數據總線和數據總線的引出線必須定義net alias

? ? ? (3)Schematic new page (可以多張圖:

單層次電路圖間,以相同名稱的“電路端口連接器”off-page connector連接

多層次式電路圖:以方塊圖(層次塊Hierarchical Block.。。)來代替實際電路的電路圖,以相同名稱Port的配對內層電路,內層電路之間可以多張,同單層連接

(4)PCB層預處理

編輯元件屬性

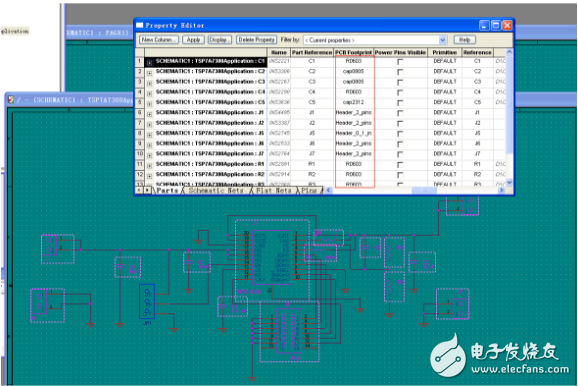

在導入PCB之前,必須正確填寫元件的封裝(PCB Footprint) 參數整體賦值(框住多個元件,然后Edit Properties),出現如圖所示的property editer; 編輯pcb footPrint(與allegro pcb中的元器件的封裝名稱相一致);part Perference是網表導入allegro pcb后的元器件名稱;還能進行其他屬性編輯;還可添加其他需要的屬性;

(6)分類屬性編輯

Edit Properties--》New ColumnClass:IC(IC,IO,Discrete三類,在PCB中分類放置) 放置定義房間(Room) Edit Properties--》New ColumnRoom 添加文本和圖像

添加文本、位圖(Place.。。)

6、 原理圖繪制的后續處理

(切換到項目管理器窗口,選中*.DSN文件,然后進行后處理————DRC檢查、生成網表及元器件清單)

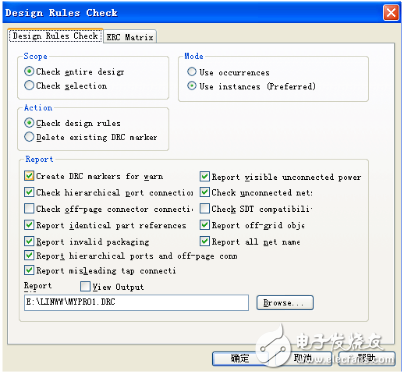

(1)設計規則檢查(Tools--》Design Rules Check.。。)

Design Rules Check

scope(范圍):entire(全部)/selection(所選)

Mode(模式):occurences(事件:在同一繪圖頁內同一實體出現多次的實體電路) instance(實體:繪圖頁內的元件符號) Action(動作):check design rules/delete DRC Report(報告):

Create DRC markers for warn(在錯誤之處放置警告標記) Check hierarchical port connection(層次式端口連接) Check off-page connector connection(平坦式端口連接) Report identical part referenves(檢查重復的元件序號) Report invalid package (檢查無效的封裝)

Report hierarchical ports and off-page connector(列出port和off-page 連接) Check unconnected net Check SDT compatible Report all net names

(2)元件自動編號(Tools --》Annotate)

scope(范圍):Update entire design/selection

Action:Incremental reference update 增長的自動編號

unconfitional reference update

reset part reference to “?” 將編號重置為“?”;

Add/delete Intersheet Reference(在分頁圖紙的端口的序號加上/刪除圖紙的編號) Reset reference numbers to begin at 1 each page原理圖每個頁重置編號從1開始

(3)自動更新器件或網絡的屬性(Tools--》Update Properties.。。)

7、生成網表

在原理圖檢查無誤后

Tools--》Create NetLists生成網表;

電子發燒友App

電子發燒友App

評論