我用OrCAD Capture畫(huà)好了原理圖,也正常的生成了網(wǎng)表,但是今天突然打不開(kāi)原理圖了。現(xiàn)在的現(xiàn)象是打開(kāi)圖后,如下:點(diǎn)擊+號(hào)后,看不到下面的原理圖,+號(hào)也消失了。如下圖:如果在此工程下單擊鼠標(biāo)

2014-08-19 22:32:52

在上一講中我們學(xué)習(xí)了如何使用OrCAD繪制STM32等器件的原理圖Symbol。這一講我們以STM32F411最小系統(tǒng)為例,開(kāi)始講OrCAD原理圖的繪制。基本上每個(gè)芯片,我們都可以在數(shù)據(jù)手冊(cè)中找到

2021-08-03 08:19:08

最近剛學(xué)習(xí)使用Cadence這款軟件進(jìn)行原理圖設(shè)計(jì),但是在設(shè)計(jì)好原理圖之后準(zhǔn)備生成網(wǎng)絡(luò)表時(shí),系統(tǒng)突然出現(xiàn)下圖錯(cuò)誤提醒閃退,在此之前我有生成網(wǎng)絡(luò)表過(guò),都是可以正常生成網(wǎng)絡(luò)表的。請(qǐng)問(wèn)各位大神這種要怎么處理?另軟件重裝過(guò)還是不行。

2019-12-05 10:31:42

的圖標(biāo),如下圖所示,即可產(chǎn)生網(wǎng)標(biāo)。l Allegro第一方網(wǎng)表如上圖操作以后。彈出以下界面,選擇PCB Editor,然后點(diǎn)擊確定,即可生成Allegro第一方網(wǎng)表,網(wǎng)表的形式會(huì)已Allegro文件夾的方式存在于當(dāng)前原理圖的根目錄下。(圖文詳解見(jiàn)附件)

2019-08-26 17:46:14

[size=11.8181819915771px]一、設(shè)計(jì)準(zhǔn)備 原理圖分析,DRC檢查。一、標(biāo)準(zhǔn)元件庫(kù)的建立,特殊元器件的建立,印制板設(shè)計(jì)文件的建立,轉(zhuǎn)網(wǎng)表。二、網(wǎng)表輸入 將生成的網(wǎng)表轉(zhuǎn)換

2015-01-23 10:40:48

規(guī)則了,因?yàn)檩斎刖W(wǎng)表時(shí),設(shè)計(jì)規(guī)則已隨網(wǎng)表輸入進(jìn)PowerPCB了。如果修改了設(shè)計(jì)規(guī)則,必須同步原理圖,保證原理圖和PCB的一致。除了設(shè)計(jì)規(guī)則和層定義外,還有一些規(guī)則需要設(shè)置,比如Pad Stacks

2009-04-27 21:13:30

我工程里面的三張原理圖和一張PCB已經(jīng)布好,現(xiàn)要求微調(diào),比如將3.3V電源再通過(guò)一個(gè)新的電容到地,原理圖改好后,更新到PCB就報(bào)錯(cuò)了,刪除網(wǎng)絡(luò)表和元件類(lèi)后,仍然出現(xiàn)錯(cuò)誤,具體表現(xiàn)是PCB上元器件及布線出現(xiàn)綠色的小叉,求解大神們,謝謝啦

2018-05-17 12:31:48

(1):畫(huà)原理圖的時(shí)候管腳的標(biāo)注一定要用網(wǎng)絡(luò) NET不要用文本TEXT否則導(dǎo)PCB的時(shí)候會(huì)出問(wèn)題 (2):畫(huà)完原理圖的時(shí)候一定要讓所有的元件都有封裝,否則導(dǎo)PCB的時(shí)候會(huì)找不到元件 有的元件

2018-08-30 10:38:05

PCB畫(huà)原理圖的十大注意事項(xiàng)(1)畫(huà)原理圖的時(shí)候管腳的標(biāo)注一定要用網(wǎng)絡(luò) NET不要用文本TEXT,否則導(dǎo)PCB的時(shí)候會(huì)出問(wèn)題 (2)畫(huà)完原理圖的時(shí)候一定要讓所有的元件都有封裝,否則導(dǎo)PCB的時(shí)候會(huì)

2018-08-20 22:16:52

找到。 a. 在裝載網(wǎng)絡(luò)表時(shí),事先沒(méi)有加載對(duì)應(yīng)的PCB封裝庫(kù)。 b. 原理圖中的元件使用了pcb庫(kù)中沒(méi)有的封裝。 c. 原理圖中的元件使用了pcb庫(kù)中名稱(chēng)不一致的封裝。 d. 原理圖中的元件使用了pcb庫(kù)中

2011-10-20 11:07:09

1.原理圖常見(jiàn)錯(cuò)誤:(1)ERC報(bào)告管腳沒(méi)有接入信號(hào):a. 創(chuàng)建封裝時(shí)給管腳定義了I/O屬性;b.創(chuàng)建元件或放置元件時(shí)修改了不一致的grid屬性,管腳與線沒(méi)有連上;c. 創(chuàng)建元件時(shí)pin方向反向

2021-11-11 06:13:36

和非金屬化孔定義準(zhǔn)確7.確認(rèn)PCB模板準(zhǔn)確無(wú)誤后最好鎖定該結(jié)構(gòu)文件,以免誤操作被移動(dòng)位置布局后檢查階段a.器件檢查8, 確認(rèn)所有器件封裝是否與公司統(tǒng)一庫(kù)一致,是否已更新封裝庫(kù)(用viewlog檢查運(yùn)行

2018-12-14 14:18:42

本文總結(jié)了PCB設(shè)計(jì)時(shí)應(yīng)該注意的148個(gè)檢查項(xiàng)目,希望對(duì)您的學(xué)習(xí)有所幫助。一、資料輸入階段1.在流程上接收到的資料是否齊全(包括:原理圖、*.brd文件、料單、PCB設(shè)計(jì)說(shuō)明以及PCB設(shè)計(jì)或更改

2019-05-31 01:09:09

。一、原理圖階段網(wǎng)標(biāo)連接完整性檢查參數(shù)管理器(參數(shù):網(wǎng)絡(luò))檢查內(nèi)容:浮地、網(wǎng)標(biāo)不一致(空格和下劃線)、直接連線沒(méi)有聯(lián)通浮地:編譯原理圖,查看message...

2021-11-11 07:54:14

orcad+ad畫(huà)電路板,由于有種原因,需要返回去修改原理圖,那修改后的orcad原理圖,如何更新到ad pcb里繼續(xù)畫(huà)圖?謝謝!

2019-04-16 22:11:47

請(qǐng)教一下各位orcad高手,從別人那里弄過(guò)來(lái)的orcad原理圖,圖上很多元器件我的庫(kù)里面都沒(méi)有,無(wú)法生成網(wǎng)絡(luò)表,我要怎么才能最快得正常使用這個(gè)原理圖?讓它能夠生成網(wǎng)絡(luò)表供ALLEGRO使用?

2015-10-25 21:34:30

1、ORCAD軟件打開(kāi)原理圖,選中原理圖的根目錄,點(diǎn)擊Tools-Creat Netlist,或者是點(diǎn)擊菜單欄上N的圖標(biāo),如下圖所示,即可產(chǎn)生網(wǎng)標(biāo)。2、Allegro第一方網(wǎng)表如上圖操作以后。彈出

2018-11-05 15:04:04

時(shí),應(yīng)該緊湊一些,不根據(jù)PCB板的大小布板所有器件按原理圖電流走向放置,不隨意擺放有極性的元件盡量保持元器件的方向一致走線回路盡量短,就近打孔過(guò)采樣線的寬度不突變雙面測(cè)試點(diǎn)兩面都要有絲印鋪地時(shí)小塊銅皮

2021-04-28 10:40:06

AD原理圖DRC檢查提示網(wǎng)絡(luò)編號(hào)重復(fù)怎么辦

2015-01-07 20:38:07

在Orcad中生成的網(wǎng)絡(luò)表(格式.ASC),導(dǎo)進(jìn)PADS9.2中(PADS9.2中已有一些元器件),結(jié)果報(bào)Mixing nets,如下圖示。 仔細(xì)檢查原理圖中的這些nets,發(fā)現(xiàn)有的有錯(cuò),有的沒(méi)錯(cuò),如何解決??

2015-01-27 11:06:26

,三引腳器件連接注意引腳排列與功能一致(尤其注意三極管的管腳與原理圖及手冊(cè)要對(duì)應(yīng)) 三、PCB設(shè)計(jì)繪圖規(guī)范 Clearance Constraint:不同兩個(gè)網(wǎng)絡(luò)的間距,設(shè)置>12 mil n

2012-05-23 14:00:38

如題,求教各位大神,畫(huà)完原理圖轉(zhuǎn)PCB后,一塊芯片的對(duì)應(yīng)引腳的網(wǎng)絡(luò)不一樣

2017-10-04 12:16:14

生成PCB后,PCB 中 芯片 第一個(gè)引腳變成了C12的網(wǎng)絡(luò)了,與原理圖不一致,怎么改回來(lái)

2016-03-22 15:54:33

檢查一下你的原理圖,你應(yīng)該會(huì)驚嘆:“我這么仔細(xì)地畫(huà)圖,竟然還會(huì)有這么多錯(cuò)誤啊?”3. 檢測(cè)所有的網(wǎng)絡(luò)節(jié)點(diǎn)net是否都連接正確(重點(diǎn))一般容易出現(xiàn)的錯(cuò)誤有:(1) 本來(lái)兩個(gè)net是應(yīng)該相連接的,卻不小心標(biāo)得不一致

2018-08-10 18:41:18

著錯(cuò)誤文件檢查一下你的原理圖,你應(yīng)該會(huì)驚嘆:“我這么仔細(xì)地畫(huà)圖,竟然還會(huì)有這么多錯(cuò)誤啊?” 3. 檢測(cè)所有的網(wǎng)絡(luò)節(jié)點(diǎn)net是否都連接正確(重點(diǎn)) 一般容易出現(xiàn)的錯(cuò)誤有: (1) 本來(lái)兩個(gè)net是應(yīng)該相連接

2019-04-29 06:09:34

檢查一下你的原理圖,你應(yīng)該會(huì)驚嘆:“我這么仔細(xì)地畫(huà)圖,竟然還會(huì)有這么多錯(cuò)誤啊?”3. 檢測(cè)所有的網(wǎng)絡(luò)節(jié)點(diǎn)net是否都連接正確(重點(diǎn))一般容易出現(xiàn)的錯(cuò)誤有:(1) 本來(lái)兩個(gè)net是應(yīng)該相連接的,卻不小心標(biāo)得不一致

2014-06-05 15:09:01

如題,網(wǎng)絡(luò)表沒(méi)有任何錯(cuò)誤,PCb中導(dǎo)入網(wǎng)絡(luò)表后,所有封裝都在,但是很多元件沒(méi)有連線,檢查了SCH原理圖,連接沒(méi)問(wèn)題啊,交叉點(diǎn)也加了連接點(diǎn),原理圖檢查了若干遍,可就是導(dǎo)入PCB后,很多元件之間沒(méi)有連線,封裝庫(kù)填寫(xiě)也正常啊!請(qǐng)大俠們給說(shuō)說(shuō)!謝謝!

2013-01-17 14:46:57

有誰(shuí)知道,在用AD10設(shè)計(jì)的時(shí)候怎么樣能生成網(wǎng)絡(luò)表?怎么樣把原理圖轉(zhuǎn)化成PCB圖?請(qǐng)各位指導(dǎo),有具體的步驟最好,在此謝過(guò)

2013-04-25 09:16:06

AD8233數(shù)據(jù)手冊(cè)參考案例圖引腳順序與后面給出的引腳信息不一致,請(qǐng)問(wèn)應(yīng)以哪個(gè)為準(zhǔn)?如下圖所示。另外,是否有詳細(xì)的封裝信息或PCB模型。謝謝!

2023-11-15 06:43:29

往我們畫(huà)完電路原理圖后,也知道要檢查檢查,但從哪些地方入手檢查呢?檢查原理圖需要注意哪些地方呢?下面聽(tīng)我根據(jù)我的經(jīng)驗(yàn)一一道來(lái)。1. 檢查所有的芯片封裝圖引腳是否有誤當(dāng)然,我指的是自己畫(huà)的芯片封裝。我

2019-07-04 09:20:58

datasheet上的管腳圖和官網(wǎng)上PCB原理圖,管腳不一致,板都畫(huà)完了,才發(fā)現(xiàn),到底啊哪個(gè)是正確的?

2018-08-16 07:52:57

。目錄(Allegro PCB設(shè)計(jì)最精簡(jiǎn)流程與常見(jiàn)問(wèn)題處理辦法)一、原理圖相關(guān)處理(默認(rèn)原理圖設(shè)計(jì)完畢,進(jìn)入PCB設(shè)計(jì)環(huán)節(jié))1、添加封裝屬性(操作細(xì)節(jié))2、原理圖設(shè)計(jì)規(guī)則檢查3、導(dǎo)出網(wǎng)絡(luò)表二、PCB板邊

2016-09-12 20:14:36

OrCAD Capture作為行業(yè)標(biāo)準(zhǔn)的PCB原理圖輸入方式,是當(dāng)今世界最流行的原理圖輸入工具之一,具有簡(jiǎn)單直觀的用戶設(shè)計(jì)界面。不管是用于設(shè)計(jì)模擬電路、復(fù)雜的PCB、FPGA和CPLD、PCB改版

2020-07-06 16:15:50

Cadance用orcad畫(huà)的原理圖,怎么導(dǎo)入***中畫(huà)PCB布線?

2015-03-31 10:57:47

原理圖

簡(jiǎn)介

在設(shè)計(jì)中添加圖框

原理圖之間導(dǎo)航器

原理圖之間的電氣連接

層次設(shè)計(jì)實(shí)例

檢查原理圖

篩選工具

網(wǎng)絡(luò)高亮顯示

從 PCB 上交叉探測(cè)

電氣規(guī)則檢查

分配封裝

在符號(hào)屬性中分配封裝

2023-05-21 16:06:28

換了,因?yàn)檎{(diào)網(wǎng)表只認(rèn)這個(gè)格式。

第四步:對(duì)比ECO文件

第五步:導(dǎo)入ECO文件,彈出的報(bào)告可以看出是否更新成功

這個(gè)是中途更新原理圖的方法,當(dāng)然如果是新項(xiàng)目就非常簡(jiǎn)單了,在修改好asc那一步后直接導(dǎo)入即可。

原作者:pcb疑難雜癥群友廖工

2023-04-28 17:04:05

PADS可以在沒(méi)有原理圖而僅有PCB圖的情況下,提取網(wǎng)絡(luò)表嗎?如果有該怎么提取,請(qǐng)寫(xiě)出步驟。

2015-12-31 15:48:26

PCBNavigator在OrCAD與PowerPCB間的使用說(shuō)明該軟件是一個(gè)從原理圖到PCB板的雙向綜合環(huán)境系統(tǒng)能完成pin/gate swapreference

2008-11-05 22:55:13

大家好,有空說(shuō)說(shuō)ad9從PCB反抄原理圖步驟,需要把敷銅刪除嗎?還有網(wǎng)絡(luò)標(biāo)號(hào)怎么弄?又不能復(fù)制!而且繪制原理圖如果用導(dǎo)線直接連,繪制出來(lái)的原理圖和原PCB圖網(wǎng)絡(luò)標(biāo)號(hào)肯定會(huì)不一樣。

2012-12-18 14:12:06

cadence Orcad軟件怎么去檢查單端網(wǎng)絡(luò)呢?

2018-11-13 17:22:56

cadence16.6生成網(wǎng)表后原理圖與PCB不能交互,交互功能勾選了,原理圖改網(wǎng)絡(luò)重新生成網(wǎng)表PCB的網(wǎng)絡(luò)也會(huì)相應(yīng)改過(guò),PCB選擇器件高亮原理圖相應(yīng)的也會(huì)有關(guān)聯(lián),但是在原理圖選擇元器件PCB不會(huì)

2021-09-09 17:10:24

power pcb2007 導(dǎo)入orcad網(wǎng)表后元件的值沒(méi)有求指教啊是什么問(wèn)題啊?

2012-04-18 17:15:07

請(qǐng)高手指點(diǎn)原理圖和、pcb已經(jīng)完成,但是后來(lái)有少許的更改,元件有增添和更改,不想重新畫(huà)一遍PCB(原理圖和網(wǎng)絡(luò)表已經(jīng)更改完成),請(qǐng)問(wèn)有什么簡(jiǎn)潔的方法能完成PCB的更改嗎?如果重新加載網(wǎng)絡(luò)表,原來(lái)PCB里的網(wǎng)絡(luò)表是不是已經(jīng)作廢??

2016-09-08 10:07:12

protel修改網(wǎng)絡(luò)表咋更新原理圖

2013-04-01 11:02:03

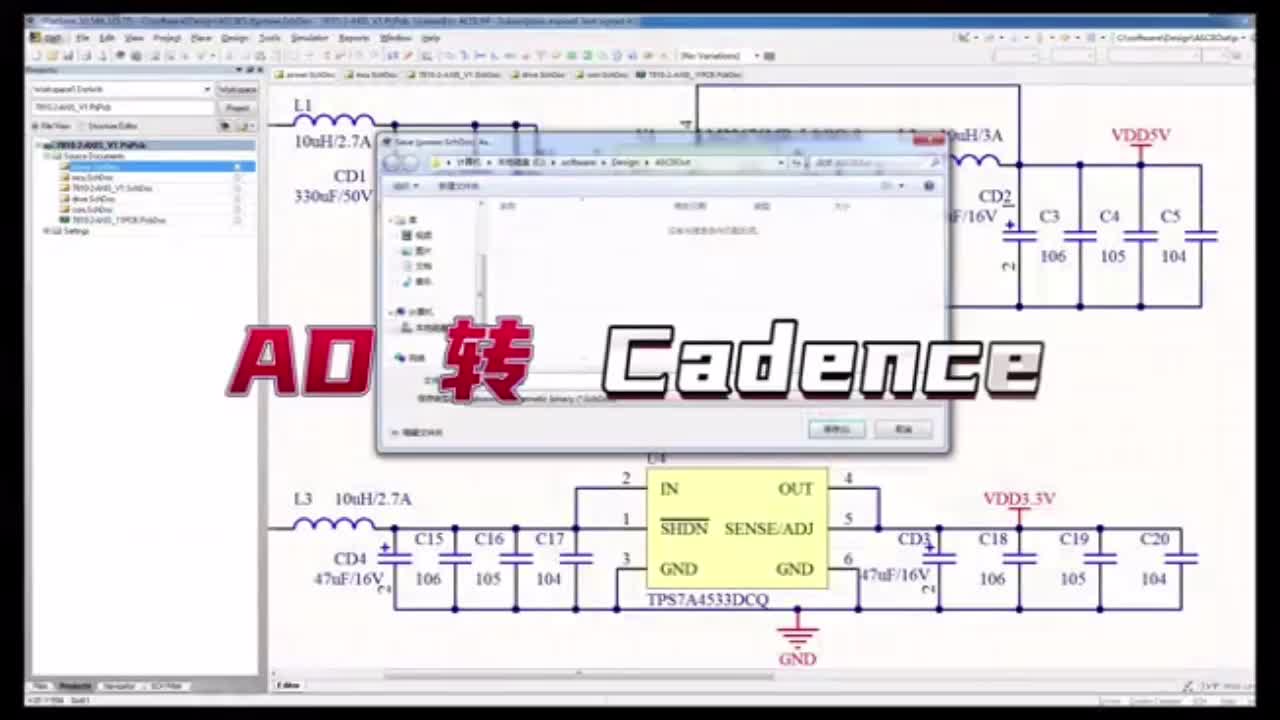

的原理圖僅供參考,如果要使用,則須檢查及確認(rèn)。對(duì)電阻、電容的封裝型號(hào)按照BOM表核對(duì)一遍,有時(shí)候OrCAD中有可選封裝類(lèi)型時(shí),轉(zhuǎn)換過(guò)來(lái)的封裝型號(hào)可能會(huì)變。圖6-202 設(shè)置轉(zhuǎn)換輸出文件路徑及預(yù)覽工程文件 圖6-203轉(zhuǎn)換后的Altium Designer原理圖

2021-08-03 14:35:11

原理圖繪制完成后需要進(jìn)行編譯檢查,檢查原理圖短路可以幫助判斷原理圖是否設(shè)計(jì)有誤,那么AD原理圖中怎么檢查網(wǎng)絡(luò)短路呢?1)執(zhí)行菜單欄命令“工程-工程選項(xiàng)”,在“option for pcb”界面將

2021-08-26 14:10:43

。 [hide]1. 檢查所有的芯片封裝圖引腳是否有誤 當(dāng)然,我指的是自己畫(huà)的芯片封裝。我在項(xiàng)目中曾經(jīng)把一個(gè)芯片的2個(gè)引腳畫(huà)反了,導(dǎo)致最后制版出來(lái)后不得不跳線,這樣就很難看了。 所以,檢查與原理圖

2018-08-15 10:11:55

Orcad 中畫(huà)完原理圖 2.Orcad 與 Pads Layout 建立聯(lián)系 3.導(dǎo)出 .asc 網(wǎng)絡(luò)表 4.導(dǎo)入到 Pads Layout 中Orcad 與 Pads Layout 建立聯(lián)系在

2019-07-25 08:30:00

。 工程檢查:Engineering check,工程檢查是指對(duì)原理圖的相關(guān)特性進(jìn)行必須的檢查,以保證電路所表達(dá)的連接關(guān)系正確、無(wú)誤,這些特性一般包括孤立網(wǎng)絡(luò)、電氣連接的完整、器件管腳的屬性是否匹配等。

2021-09-03 14:47:53

檢查一下你的原理圖,你應(yīng)該會(huì)驚嘆:“我這么仔細(xì)地畫(huà)圖,竟然還會(huì)有這么多錯(cuò)誤啊?”3. 檢測(cè)所有的網(wǎng)絡(luò)節(jié)點(diǎn)net是否都連接正確(重點(diǎn))一般容易出現(xiàn)的錯(cuò)誤有:(1) 本來(lái)兩個(gè)net是應(yīng)該相連接的,卻不小心標(biāo)得不一致

2018-08-10 21:09:05

ad畫(huà)fpga圖pcb管腳交換導(dǎo)致原理圖管腳變化了,我只想交換原理圖里的網(wǎng)絡(luò)表可以嗎?(其實(shí)變引腳也是為了變網(wǎng)絡(luò)表,為什么不直接交換引腳上的網(wǎng)絡(luò)名?)

2019-05-24 00:29:36

有所幫助! 1.打開(kāi)現(xiàn)有PCB Layout 文件,然后選中此設(shè)計(jì)的所有零件封裝,將其保存在庫(kù)中。(這一步是保證封裝的一致性,理由嘛大家試試就知道了)。 2.打開(kāi)原理圖文件,(當(dāng)然是ORCAD中打開(kāi)

2014-11-15 14:55:33

在PCB反向技術(shù)研究中,反推原理圖是指依據(jù)PCB文件圖反推出或者直接根據(jù)產(chǎn)品實(shí)物描繪出PCB電路圖,旨在說(shuō)明線路板原理及工作情況。并且,這個(gè)電路圖也被用來(lái)分析產(chǎn)品本身的功能特征。而在正向設(shè)計(jì)中,一

2015-02-05 17:43:18

同步FIFO代碼已經(jīng)寫(xiě)好了,但是怎么判斷寫(xiě)入的數(shù)據(jù)和讀出的數(shù)據(jù)是否一致呢?求代碼

2016-04-26 15:58:34

如何檢查powerPCB與原理圖的網(wǎng)絡(luò)表是否一致

2011-06-20 11:29:50

請(qǐng)假一下各位大哥如果檢測(cè)或?qū)Ρ犬?dāng)把原理圖導(dǎo)PADS Layout時(shí),兩邊的元件是一致的,所有的封裝形式就顯示出來(lái)了,,,望各位大哥不吝賜教!!小弟這廂有禮了!!!

2023-04-28 16:21:55

如何將orcad的網(wǎng)絡(luò)表導(dǎo)入倒DXP2004的PCB里去啊?PCB打樣找華強(qiáng) http://www.hqpcb.com/3 樣板2天出貨

2012-10-26 10:43:28

在這里給大家分享一個(gè)如何將ad原理圖導(dǎo)入到Orcad中的具體步驟。1.用AD打開(kāi)原理圖(此處用的是AD09講解),執(zhí)行菜單命令:File->New->Project->PCB

2020-07-14 17:36:56

封裝形式?jīng)]有顯示出來(lái)(就是有的元件不見(jiàn)了),很明顯的元件看見(jiàn)了可以修改一下原理圖再導(dǎo)一次就可以解決了,但不明顯的元件有沒(méi)有少就不知道了,,在此想請(qǐng)假一下各位大哥如果檢測(cè)或?qū)Ρ犬?dāng)把原理圖導(dǎo)PADS Layout時(shí),兩邊的元件是一致的,所有的封裝形式就顯示出來(lái)了,,,望各位大哥不吝賜教!!小弟這廂有禮了!

2014-12-31 11:31:32

(1) 認(rèn)證產(chǎn)品的標(biāo)識(shí)(銘牌)與型式試驗(yàn)報(bào)告所標(biāo)明的一致性;(2) 認(rèn)證產(chǎn)品的結(jié)構(gòu)與型式試驗(yàn)樣品的一致性;(3) 認(rèn)證產(chǎn)品重要部件/元器件與型式試驗(yàn)報(bào)告中《重要部件/元器件清單》的一致性;(4) 按《例行檢驗(yàn)項(xiàng)目和確認(rèn)檢驗(yàn)項(xiàng)目表》進(jìn)行現(xiàn)場(chǎng)檢查。

2016-10-19 09:40:11

`請(qǐng)問(wèn)方案商給我的ORCAD原理圖,我都沒(méi)有改動(dòng)過(guò),直接導(dǎo)網(wǎng)絡(luò)表,但是導(dǎo)網(wǎng)表時(shí)報(bào)錯(cuò),導(dǎo)不出來(lái)。

補(bǔ)充內(nèi)容 (2016-3-10 08:54):

`

2016-03-08 11:54:14

他層的比例不一致,無(wú)法對(duì)孔相關(guān)的參數(shù)檢查。一款簡(jiǎn)便實(shí)用的PCB分析軟件,可一鍵導(dǎo)出/導(dǎo)入文件,查看Gerber,分析生產(chǎn)難度。CMA 遇到這樣的問(wèn)題是大伙對(duì)應(yīng)鉆孔格式的不了解。下面就來(lái)帶大伙認(rèn)識(shí)EDA軟件輸出鉆孔文件。(附CAM350 格式錯(cuò)誤圖)

2020-06-12 18:40:12

大家?guī)涂纯磒rotel畫(huà)的原理圖與PCB的網(wǎng)絡(luò)表 不一致不知道是哪里的問(wèn)題剛接觸這個(gè)軟件大神們幫忙看看!謝謝了!求指點(diǎn)一二!急急!

2012-07-18 00:20:21

用multisim畫(huà)好原理圖生成protelPCB網(wǎng)絡(luò)表,由于在multisim中芯片的電源和接地都是默認(rèn)的,在導(dǎo)入網(wǎng)絡(luò)表時(shí)出現(xiàn)錯(cuò)誤,怎么解決這樣的問(wèn)題呢?

2012-06-20 22:47:14

”端與導(dǎo)線相連。6、網(wǎng)絡(luò)載入時(shí)報(bào)告NODE沒(méi)有找到,試分析可能的原因。答:可能的原因有:a、原理圖中的元件使用了pcb庫(kù)中沒(méi)有的封裝;b、原理圖中的元件使用了pcb庫(kù)中名稱(chēng)不一致的封裝;c、原理圖

2016-11-17 15:57:26

”端與導(dǎo)線相連。6、網(wǎng)絡(luò)載入時(shí)報(bào)告NODE沒(méi)有找到,試分析可能的原因。答:可能的原因有:a、原理圖中的元件使用了pcb庫(kù)中沒(méi)有的封裝;b、原理圖中的元件使用了pcb庫(kù)中名稱(chēng)不一致的封裝;c、原理圖

2017-03-10 14:27:49

ORCAD里怎樣畫(huà)PCB板的資料,是不是,這個(gè)軟件不支持畫(huà)PCB板呢, 那Layout又有什么用呢?很是不解,要畫(huà)PCB板一定要把網(wǎng)絡(luò)表倒入別的軟件呢/ 希望行內(nèi)朋友指點(diǎn)指點(diǎn)。。。。。不勝感激。。。

2008-08-07 17:58:03

PCB元件名是不是應(yīng)該與原理圖庫(kù)的元件名一致的?謝謝

2019-03-13 02:33:23

想請(qǐng)教個(gè)問(wèn)題,AD做的原理圖能否像orcad一樣能加下頁(yè)間符數(shù)字符號(hào)

2019-09-16 10:27:28

allegro pcb怎么才能知道和原理圖是一致的

2019-07-24 05:32:12

怎么將ORCAD原理圖輸出網(wǎng)表?PADS-PCB導(dǎo)入網(wǎng)表?然后PCB輸出CAM? 越詳細(xì)越好啊。

2011-09-29 22:38:31

1網(wǎng)表文件是否為硬件工程師發(fā)布和確認(rèn),版本及發(fā)布時(shí)間是否一致 2結(jié)構(gòu)文件(dxf、dwg)是否為結(jié)構(gòu)工程師發(fā)布和確認(rèn),版本及發(fā)布時(shí)間是否一致 3元器件資料是否為現(xiàn)行官方承認(rèn)和發(fā)布版本 4元器件封裝庫(kù)

2015-11-11 16:01:42

orCAD中設(shè)計(jì)檢查:布線初步完成后檢查是否有遺漏未布線的網(wǎng)絡(luò),生成報(bào)告,在其中查看未布線的網(wǎng)絡(luò)并完善布線。查看多余線頭,生成報(bào)告并完善。

2017-12-05 10:19:17 10512

10512

orcad的物理規(guī)則檢查的每一個(gè)的含義是什么? 答:orcad進(jìn)行物理DRC檢測(cè)時(shí),如圖3-65所示,需要對(duì)檢查的每一項(xiàng)參數(shù)進(jìn)行設(shè)置,每個(gè)參數(shù)的含義如下所示: 圖3-65 物理規(guī)則檢查參數(shù)設(shè)置示意圖

2021-11-09 11:25:31 3277

3277

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

10512

10512

3277

3277

評(píng)論