在電路設計中,經常需要使用匹配電阻,如閉路電視同軸電纜、時鐘數據線等,如果阻抗不匹配會有什么不良后果呢?

2020-07-16 11:16:20 2338

2338 總算是存在這樣一個問題,接收端差分線對之間可否加一匹配電阻?

2022-09-15 17:13:48 4618

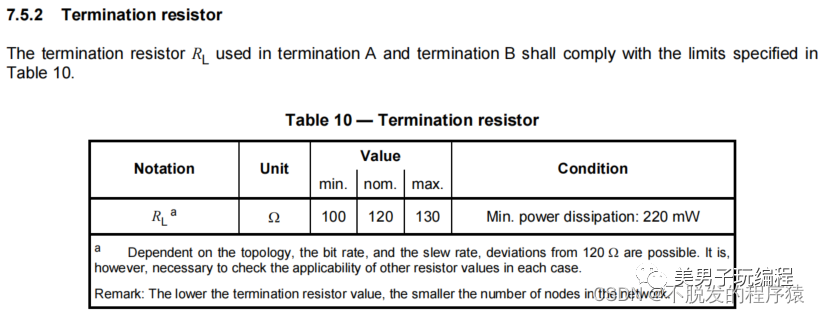

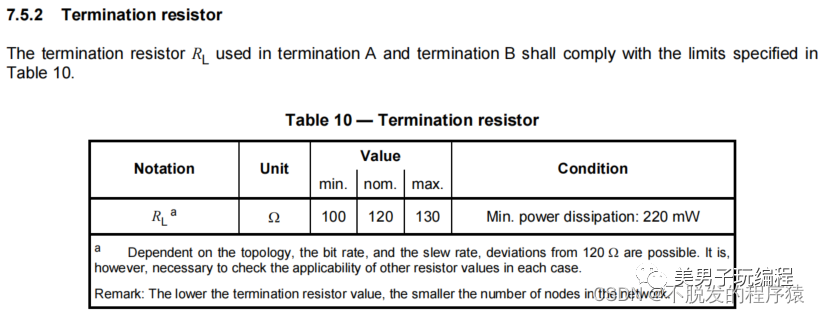

4618 高速CAN網絡需要在CAN_H和CAN_L加終端電阻,電纜上的終端電阻應與電纜的標稱阻抗相匹配,終端匹配電阻一般為120Ω,每個終端電阻應能消耗0.25W的功率(標準來源:ISO 11898-2:2003)。

2023-04-07 14:24:19 741

741 `看485電路有些問題為什么差分電壓增大,驅動電流減小。我理解電壓除電流就是電路中的匹配電阻。匹配電阻小導致電壓小、電流大。希望大家指正錯誤`

2021-01-28 09:31:40

網上查閱資料說芯片A,B之間要加約120歐姆的匹配電阻,但是我看到有的產品上的電阻是12K或者24K,請問這個是怎么選的?

2019-09-27 09:10:10

) 差分信號(Differential Signal)幾個常見設計誤區 PCB Layout and SI 問答專家解答(經典資料) 信號完整性的一些基本概念 什么是差分信號? 高速PCB設計中終端匹配電阻

2008-12-25 09:49:59

mil內。與相匹配的DM和DQS串聯匹配電阻RS值為0~33 Ω,并聯匹配終端電阻RT值為25~68Ω。如果使用電阻排的方式匹配,則數據電阻排內不應有其他DDR信號。地址和命令信號組:保持完整的地和電源

2017-10-16 15:30:56

阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于20M的信號,PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號

2019-02-14 14:50:45

電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于 20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2018-11-15 20:07:35

電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于 20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2019-01-02 10:30:00

電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于 20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2022-05-16 16:15:03

阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度成反比。在嵌入式系統中,一般頻率大于20M的信號且PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2014-07-04 14:00:27

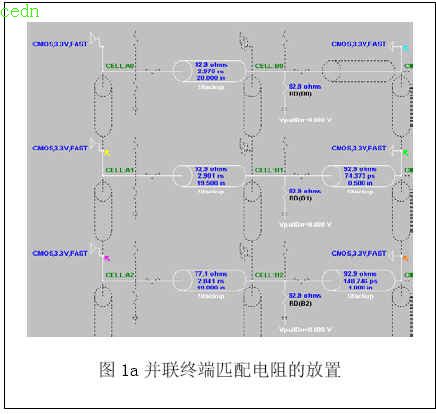

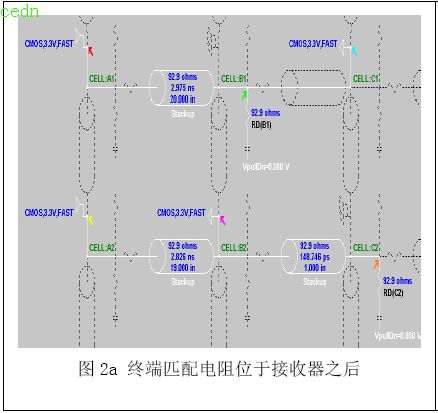

在高速 PCB 中,端接電阻器必須與其余元件一起放置,而不是最終擠壓它們。由于端接電阻器是整個電路的一部分,因此它們的放置對于電路的準確運行至關重要。 以下是放置終端電阻的兩種常用方案: 簡單

2023-04-11 17:22:23

和印刷網板設計 ◎ 高速PCB 設計中終端匹配電阻的放置 ◎ &

2009-04-14 23:48:45

各位大佬這個電路的匹配電路該怎么設計呢

2023-04-02 22:51:19

高頻信號傳輸時,信號波長相對傳輸線較短,信號在傳輸線終端會形成反射波,干擾原信號,所以需要在傳輸線末端加終端電阻,使信號到達傳輸線末端后不反射。對于低頻信號則不用。在長線信號傳輸時,一般為了避免信號的反射和回波,也需要在接收端接入終端匹配電阻。

2019-05-27 09:05:05

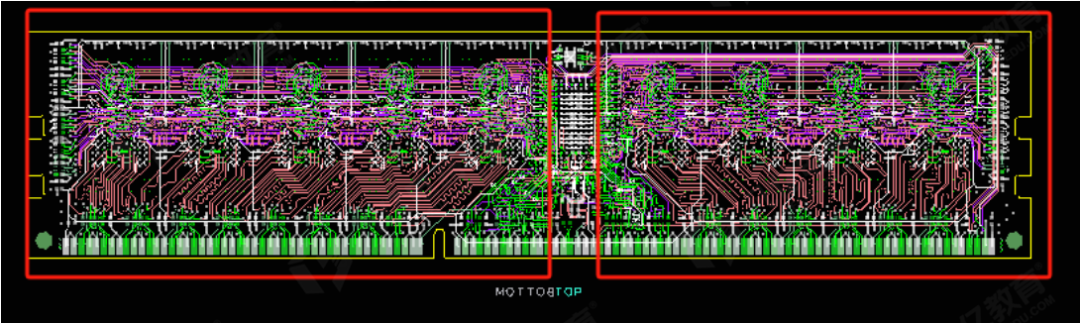

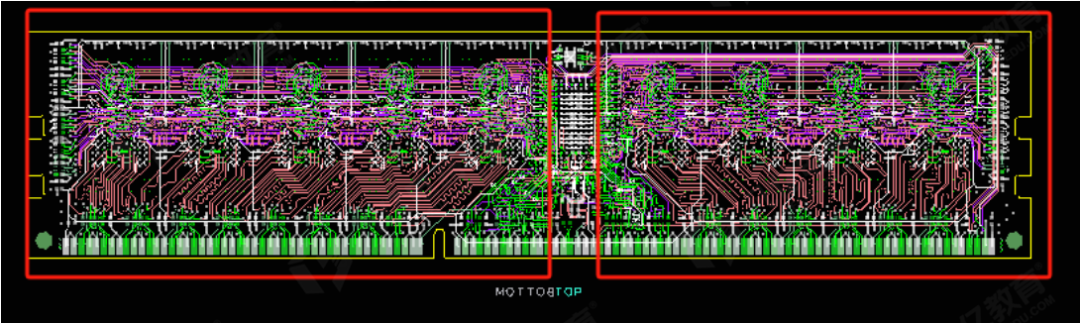

。 有文章提到,一個背板設計采用表面貼裝的電阻來實現終端匹配。電路板上使用了200多個這樣的匹配電阻。試想如果要設計10個原型樣板通過改變這200個電阻確保最佳的終端匹配效果,這將是巨大的工作量。而在

2018-11-27 10:15:02

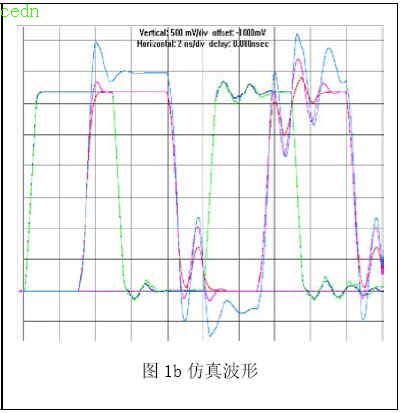

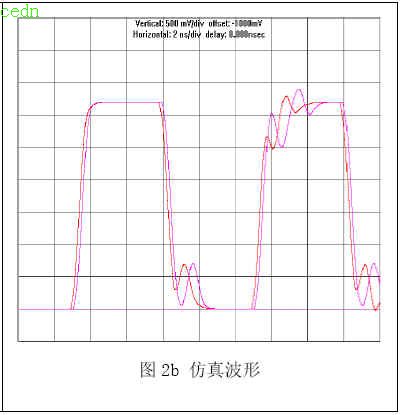

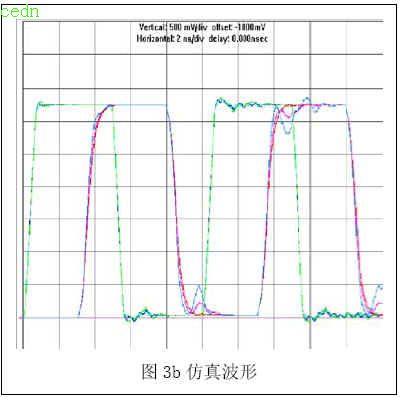

在高速數字電路系統中,傳輸線上阻抗不匹配會造成信號反射,并出現過沖、下沖和振鈴等信號畸變,而當傳輸線的時延TD大于信號上升時間RT的20%時,反射的影響就不能忽視了,不然將帶來信號完整性

2018-11-27 15:22:15

在高速數字電路系統中,傳輸線上阻抗不匹配會造成信號反射,并出現過沖、下沖和振鈴等信號畸變,而當傳輸線的時延TD大于信號上升時間RT的20%時,反射的影響就不能忽視了,不然將帶來信號完整性問題。減小

2019-06-03 07:58:51

阻抗匹配阻抗匹配是指在能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了。反之則在傳輸中有能量損失。在高速PCB設計中,阻抗的匹配與否關系到信號的質量優劣。

2019-05-31 08:12:33

在高速pcb設計中,經常聽到要求阻抗匹配。而設計中導致阻抗不匹配的原因有哪些呢?一般又對應著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

或CMOS電路來說,不可能有十分正確的匹配電阻,只能折中考慮。鏈狀拓撲結構的信號網路不適合使用串聯終端匹配,所有的負載必須接到傳輸線的末端。否則,接到傳輸線中間的負載接受到的波形就會象圖3.2.5中C

2019-05-29 07:03:30

普通光耦的阻抗匹配問題參考我之前的那篇文章《普通光耦 上下拉電阻選擇》。現如今通訊速率越來越快的當下,普通光耦在單純的只接電阻情況下,上升時間Tr有20us左右,這將無法適用于高速通訊。然而高速光耦

2019-05-29 07:47:04

先說說電路為什么需要端接?眾所周知,電路中如果阻抗不連續,就會造成信號的反射,引起上沖下沖、振鈴等信號失真,嚴重影響信號質量。所以在進行電路設計的時候阻抗匹配是很重要的考慮因素。對我們的PCB走線

2020-03-16 11:29:10

作用第一是阻抗匹配。因為信號源的阻抗很低,跟信號線之間阻抗不匹配,串上一個電阻后,可改善匹配情況,以減少反射,避免振蕩等。嚴格來講,當高速電路中,信號在傳輸介質上的傳輸時間大于信號上升沿或者下降沿的1

2018-10-12 09:30:29

關于ADCMP605器件的LVDS輸入、輸出匹配電阻的問題:對于這樣的高速比較器,LVDS布局布線的要求,以及對源端和輸出端電阻匹配的要求如何?可以直接按數據手冊上的方式接么?

2018-08-09 07:21:06

數值),32個節點的并行阻抗為:375歐(ZJJ:12000歐/32=375歐)。2)計算總線負載上述并行阻抗再并入兩端的終端匹配電阻(120歐),兩個120歐并聯為60歐,則總線負載為:52歐

2019-06-24 04:38:01

到底什么時候需要加匹配電阻,什么時候不需要加匹配電阻

2023-10-13 07:01:11

RS485總線按照星形連接,末端是否需要接匹配電阻?怎樣接?

2023-04-27 17:39:33

單片機用RS485與上位機通信,接匹配電阻120Ω。機子中一直流風扇(靠近PCB板)運轉后,用串口調試助手測出機子一直在發送數據給PC機。后經測試:將機子的金屬外殼(地)與PC機殼相接后(機子和PC機都沒有接地),問題解決。或者將機子內的通信匹配電阻120Ω拆掉,問題也解決了。求大神解釋下

2019-09-26 09:12:30

RS485通訊傳輸線上一定要加偏置電阻、匹配電阻嗎? 偏置電阻作用、匹配電阻作用分別是什么?

2023-04-27 17:40:36

從OMAP-L138_C6748 LC Dev Kit Ver A6 .pdf這個原理圖看到TMS320C6748在和DDR2的連接上:數據及地址/時鐘線上串接了10歐電阻,控制信號線串接了22歐電阻,這個匹配電阻是如何確定的,是和DDR2內部終結電阻為75歐還是50歐時相匹配的?

2020-07-27 10:16:46

做過USB的人都或許有一個糾結,那就是D+和D-上到底要串多大的電阻,串在源端還是終端。我想說:網絡上的說法都不完全正確,首先USB有低速、全速和高速之分,在低速和全速模式下是電壓驅動的,驅動電壓為3.3V,但在高速模式下是電流驅動的,驅動電流為17.78mA,host-device模型如下:

2019-05-28 06:09:58

最近需要用到USB的接口保護小板,就是在D+ D-上加了一個匹配電阻22R。但是問題是就是有的產品可以正常使用,有的產品的USB接口在該小板的連接下無法識別u盤。但是把22Ω換掉成0Ω就又可以識別了,請問各位大神這是什么問題?

2018-12-05 10:14:44

第一次發帖啊大家好啊嘿嘿嘿請問一下485差分傳輸匹配電阻都是120R嗎?差分傳輸線的上下拉電阻是怎么計算出來的,有公式嗎,要參考485芯片那些資料參數。要參考負載那些參數?還有485傳輸距離和匹配電阻,上下拉電阻有什么關系?謝謝大家了!!!!!!最好能給出一個參考電路,要實際案例哦!!!

2014-12-31 13:48:43

文章提到,一個背板設計采用表面貼裝的電阻來實現終端匹配。電路板上使用了200多個這樣的匹配電阻。試想如果要設計10個原型樣板通過改變這200個電阻確保最佳的終端匹配效果,這將是巨大的工作量。而在此設計中沒有任何一個電阻值的改變得益于SI軟件的分析結果,這的確令人吃驚。

2016-10-16 12:57:06

20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于 20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據和地址總線信號等

2018-11-19 13:39:51

請教各位大神,在布局布線的過程中上拉電阻和串接的匹配電阻是應給放在靠近輸入引腳還是輸出引腳???

2016-05-05 09:55:01

背景:為統籌電路設計較全面的知識點,本人將在近期推出電路設計中各種常用器件與設計理念,如基本元器件電阻、電容、電感、二極管保護,存儲器件SDRAM、FLASH,PCB設計工藝DCDC電源、PCB板布線設計工藝等,希望能為大家提供些許參考。

2019-05-23 08:16:02

串聯終端匹配后的信號傳輸具有以下特點:A 由于串聯匹配電阻的作用,驅動信號傳播時以其幅度的50%向負載端傳播;B 信號在負載端的反射系數接近+1,因此反射信號的幅度接近原始信號幅度的50%。

2019-05-29 07:10:06

能力問題在一般的TTL、CMOS系統中沒有應用,而雙電阻方式需要兩個元件,這就對PCB的板面積提出了要求,因此不適合用于高密度印刷電路板。當然還有:AC終端匹配; 基于二極管的電壓鉗位等匹配方式。 二、將

2019-05-31 06:45:06

最近公司購入了一匹USB接口保護小板,我看了一下就是在D+ D-上加了一個匹配電阻22R,(另外還有電源的隔離,這個沒影響,我們不談)結果問題來了,有的產品能夠正常使用,有的產品的USB接口在該小板

2018-12-26 09:59:29

千兆電口的PHY輸出到變壓器的4對差分線,有的產品在每對差分線上各用了100歐姆的匹配電阻(兩個50歐姆串聯);有的沒有用100歐姆的匹配電阻。請問,不用匹配電阻它是怎么做到阻抗匹配的呢????還有這4對差分線對,對與對之間需要等長嗎??????

2011-10-21 20:24:04

的精度,使用終端匹配電阻可實現對差分傳輸線的匹配,其阻值一般在90~130?之間。電路也需要用此終端匹配電阻來產生正常工作的差分電壓。對于點對點的拓撲,走線的阻抗通常控制在100?,但匹配電阻可以

2017-07-18 10:57:28

常見的總線通信協議,都需要在信號傳輸線終端設置匹配電阻,比如MODBUS是120歐的電阻,但是在多機通信時,終端電阻應該怎么接?比如說現在總線接成星形,菊花形或者其他什么形狀,終端電阻在這些接法應該是怎樣的?比如說菊花形只在首尾接,星形都要接是這樣嗎?有什么理論依據?

2024-01-16 00:04:27

我參考W5500獨立變壓器原理圖的設計,其中R21/R22/R23/R24使用33歐姆。發現當網線質量較差的情況下,通信容易中斷。我應該如何調節匹配電阻和偏置電阻呢?能否給個思路。

2019-01-03 09:39:49

電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2011-10-18 14:18:47

電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于20M的信號PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據

2019-05-31 08:06:08

本帖最后由 ignosi 于 2017-8-24 18:39 編輯

在學習李明洋老師主講的這門《天線和射頻匹配電路設計》視頻培訓課程之前,我查閱了很多本射頻相關書籍,書上關于匹配電路設計的內容

2017-08-24 18:02:23

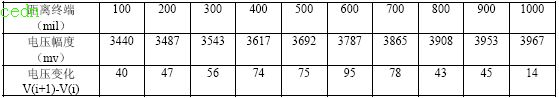

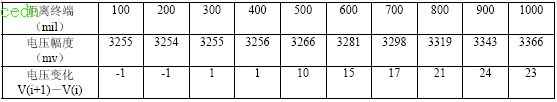

設計比較復雜,是否采用遠端串聯電阻還需要考慮信號的驅動能力和反射情況,根據具體PCB走線拓撲的情況,需要對終端并聯匹配電阻的阻值進行選擇,這通常通過電路信號仿真工具來進行。在仿真工具中,搭建電路拓撲結構,仿真工具支持參數掃描模式,通過多種參數組合仿真、在其中選擇最優的匹配設計方案。

2016-09-29 10:42:43

接收端差分線對之間可否加一匹配電阻?

2009-09-06 08:42:44

需要在傳輸線末端加終端電阻,使信號到達傳輸線末端后不反射。對于低頻信號則不用。在長線信號傳輸時,一般為了避免信號的反射和回波,也需要在接收端接入終端匹配電阻。值得注意的是,終端匹配電阻值取決于電纜的阻抗

2021-12-13 15:07:10

一般的做法是在信號源端串小電阻,在信號終端并一個小電阻。在信號源端串一個小電阻,沒有公式的理論:一般傳輸線的特征阻抗為50歐姆左右,而TTL電路輸出電阻大概為13歐姆左右,在源端串一個33歐姆的電阻

2019-05-30 06:25:34

傳輸線上形成駐波(簡單的理解,就是有些地方信號強,有些地方信號弱),導致傳輸線的有效功率容量降低;功率發射不出去,甚至會損 壞發射設備。關于串聯匹配電阻其作用:1、概述:高速信號線中才考慮使用這樣的電阻

2019-07-22 16:38:58

負載阻抗匹配。5.3.1、終端匹配在終端采用上拉和下拉匹配的方法中,匹配電阻的組織和傳輸線匹配,這樣就會有效的消除終端反射。電阻的選擇根絕反射系數ρ B =(R t -Z 0 )/ (R t +Z

2018-05-02 10:18:05

阻抗匹配阻抗匹配是指在能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了。反之則在傳輸中有能量損失。在高速PCB設計中,阻抗的匹配與否關系到信號

2014-12-01 10:38:55

電阻來解決,也沒辦法在終端加匹配電阻,只能在源端想辦法,各位大神,有好的解決辦法嗎?源端為圖片中的電路`

2013-09-26 19:58:24

請問CH559 USB 是否需要接阻抗匹配電阻,貴司開發板電路圖是沒有該電阻的,是否需要接?目前測試不接沒有任何問題,但是量產是否需要預留電阻位置,否則后面有問題很麻煩,如果要接,推薦值是多少?

2022-05-20 06:26:25

我看了有些人的板在ddr2地址線加匹配電阻,數據線不加。有的人在數據線加匹配電阻地址線不加,到底應該在那里加的,是參考DDR芯片的手冊還是參考TMS320C6748的手冊來做?

2019-01-21 13:50:55

看了資料,不是很明白。請教大家:1,是不是距離很近匹配電阻就不用加?我的兩個通訊距離不超過1米。2,如果需要加120歐匹配電阻,這個電阻的功率該選多少瓦的?謝謝大俠!

2019-10-29 09:10:11

拉終端匹配電阻等。下面,我們開始導入主芯片DSP的數據線D0腳模型。左鍵點芯片管腳處的標志,出現未知管腳,然后再按下圖的紅線所示線路選取芯片IBIS模型中的對應管腳。

2008-07-17 13:47:49

的阻抗比較低,可以串聯一個合適的電阻來跟傳輸線匹配,例如高速信號線,有時會串聯一個幾十歐的電阻。而一些接收器的輸入阻抗則比較高,可以使用并聯電阻的方法,來跟傳輸線匹配,例如,485總線接收器,常在數據線終端并聯120歐的匹配電阻。

2019-06-03 06:04:44

挑戰。

在高速PCB設計中,阻抗匹配顯得尤為重要,為減少在高速信號傳輸過程中的反射現象,必須在信號源、接收端以及傳輸線上保持阻抗的匹配。

一般而言,單端信號線的阻抗取決于它的線寬以及與參考平面之間

2023-05-26 11:30:36

設計了一款高頻天線,匹配電路屬于直接匹配的,不確定匹配電路中是否要加匹配電阻

2021-06-01 11:09:27

本文介紹了常用的幾種終端匹配技術:包括并行連接的終端匹配、串行連接的終端匹配、戴維南終端匹配、AC 終端匹配和基于二極管的終端匹配。

2011-02-21 15:06:50 83

83 電子專業單片機相關知識學習教材資料——電路設計--串聯匹配電阻的應用

2016-10-10 14:17:59 0

0 阻抗匹配是指在能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了。反之則在傳輸中有能量損失。在高速 PCB 設計中,阻抗的匹配與否關系到信號的質量優劣。PCB 走線什么時候需要做阻抗匹配?

2017-08-28 16:33:23 26

26 。串行電阻的阻值為20~75,阻值大小與信號頻率成正比,與PCB走線寬度成反比。在嵌入式系統中,一般頻率大于20M的信號且PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據和地址總線信號等。串行匹配電阻的作用有兩

2017-11-03 10:28:39 19

19 低頻信號則不用。在長線信號傳輸時,一般為了避免信號的反射和回波,也需要在接收端接入終端匹配電阻。 其終端匹配電阻值取決于電纜的阻抗特性,與電纜的長度無關。RS-485/RS-422 一般采用雙絞線(屏蔽或非屏蔽)連接,終端電阻

2017-11-09 17:22:22 6190

6190 高頻信號傳輸時,信號波長相對傳輸線較短,信號在傳輸線終端會形成反射波,干擾原信號,所以需要在傳輸線末端加終端電阻,使信號到達傳輸線末端后不反射。對于低頻信號則不用。在長線信號傳輸時,一般為了避免信號的反射和回波,也需要在接收端接入終端匹配電阻。

2017-12-04 11:00:28 104804

104804 。串行電阻的阻值為20~75,阻值大小與信號頻率成正比,與PCB走線寬度成反比。在嵌入式系統中,一般頻率大于20M的信號且PCB走線長度大于5cm時都要加串行匹配電阻,例如系統中的時鐘信號、數據和地址總線信號等。串行匹配電阻的作用有兩個

2017-12-04 11:12:53 0

0 終端電阻,是一種電子信息在傳輸過程中遇到的阻礙。高頻信號傳輸時,信號波長相對傳輸線較短,信號在傳輸線終端會形成反射波,干擾原信號,所以需要在傳輸線末端加終端電阻,使信號到達傳輸線末端后不反射。對于低頻信號則不用。在長線信號傳輸時,一般為了避免信號的反射和回波,也需要在接收端接入終端匹配電阻。

2017-12-04 11:20:54 130868

130868

精準匹配電阻器被廣泛地使用在眾多的高精度儀表應用中,這包括測量和數據采集、無線 RF、網絡、自動化測試、醫療、工業控制和軍用設備。

LT?5400 是一個四通道、精準匹配電阻器系列,專為

2018-06-05 13:45:00 2950

2950

Greg Zimmer,產品市場工程師,信號調理產品

精準匹配電阻器被廣泛地使用在眾多的高精度儀表應用中,這包括測量和數據采集、無線 RF、網絡、自動化測試、醫療、工業控制和軍用設備。

LT

2018-06-01 14:50:00 5867

5867

精準匹配電阻器被廣泛地使用在眾多的高精度儀表應用中,這包括測量和數據采集、無線 RF、網絡、自動化測試、醫療、工業控制和軍用設備。 LT5400 是一個四通道、精準匹配電阻器系列,專為高性能信號調理應用而設計,例如:差動放大器、精準分壓器、高精度增益級和橋式電路。

2019-07-25 06:13:00 2082

2082 生活中用電是我們不可缺少的,而且幾乎每天都在用電,現在用電的電器設備也多了,比如冰箱,空調等,那么是什么維持這些電路平衡呢?下面就要說到匹配電阻了,一起來了解一下。

2020-06-20 10:08:20 11584

11584 生活中用電是我們不可缺少的,而且幾乎每天都在用電,現在用電的電器設備也多了,比如冰箱,空調等,那么是什么維持這些電路平衡呢?下面就要說到匹配電阻了,一起來了解一下。 什么是匹配電阻 匹配電阻就是電阻

2020-12-31 14:28:06 8141

8141 LT5400:四路匹配電阻器網絡數據表

2021-04-22 09:29:22 4

4 高速CAN網絡需要在CAN_H和CAN_L加終端電阻,電纜上的終端電阻應與電纜的標稱阻抗相匹配,終端匹配電阻一般為120Ω,每個終端電阻應能消耗0.25W的功率(標準來源:ISO 11898-2:2003)。

2023-04-12 08:12:00 958

958 高速CAN網絡需要在CAN_H和CAN_L加終端電阻,電纜上的終端電阻應與電纜的標稱阻抗相匹配,終端匹配電阻一般為120Ω,每個終端電阻應能消耗0.25W的功率

2023-05-11 15:16:48 1864

1864

高頻信號一般使用串行阻抗匹配。串行電阻的阻值為20~75Ω,阻值大小與信號頻率成正比,與PCB走線寬度和長度成反比。在嵌入式系統中,一般頻率大于20M的信號PCB走線長度大于5cm時都要加串行匹配電阻

2023-09-12 17:32:33 854

854

運放電路為什么要匹配電阻?輸入偏置電流IB太大有什么后果? 一、運放電路為什么要匹配電阻? 運放電路中的電阻匹配是指將兩個或多個電阻的阻值相等,以達到一定的電路性能要求。在運放電路中,我們需要匹配電阻

2023-10-30 09:11:57 861

861 什么是阻抗匹配?高速PCB設計為什么要控制阻抗匹配? 阻抗匹配是指在電路傳輸信號時,控制電路中信號源、傳輸線和負載之間的阻抗相等的過程,從而確保信號的完整性和可靠性。在高速PCB設計中,阻抗匹配

2023-10-30 10:03:25 919

919 接收端差分線對之間可否加一匹配電阻? 接收端差分線對之間是由發送端發出差分信號,在接收端進行差分輸入來實現數據傳輸的一種常見的電路連接方式。差分信號的優勢在于抗干擾性能強,能夠有效地減少共模噪聲

2023-11-24 14:32:33 1085

1085 485總線是一種常用的通信總線標準,在工業現場常被使用于對遠程傳感器、控制設備和其他外圍設備進行數據傳輸和通信。為了確保信號質量和抗干擾能力,485總線上通常需要匹配電阻。 匹配電阻是一種電阻,用于

2023-12-20 09:44:12 1567

1567 DDR采用菊花鏈拓撲結構時,由于信號傳輸線較長通常需要在DDR末端加上終端匹配電阻,端接的方式有很多,但是都是為了解決信號的反射問題,通常為了消除信號的反射可以在信號的源端或者終端進行

2023-12-25 07:45:01 211

211

DDR加終端匹配電阻和不加信號質量的區別? DDR(雙倍數據傳輸速率)是一種常用于計算機內存的高速數據傳輸技術。在DDR中,終端匹配電阻和信號質量是對于數據傳輸穩定性至關重要的兩個方面。下面將詳細

2023-12-29 13:54:22 316

316

電子發燒友App

電子發燒友App

評論