問:我已看過你們的“產品說明”(data sheets)和“應用筆記”(appl ication notes),也參加過你們的技術講座,但有關如何處理ADC中模擬地和數字地的引腳 我仍有點兒糊涂。產品說明書中通常要求把模擬地和數字地在器件上連接在一起,但我不 想把ADC接成系統的星形接地點。我應該怎么做?

答:首先,對涉及到模擬地和數字地感到糊涂這件事,你不必感覺那么壞,許 多人都是這樣的!許多迷惑首先來自ADC接地引腳的名稱。模擬地和數字地的引腳名稱表示內 部元件本身的作用,未必意味著外部也應該按照內部作用去做。讓我們來解釋一下。

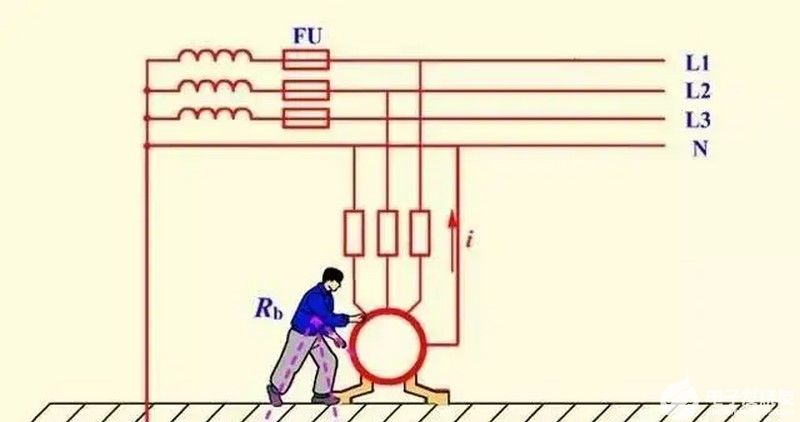

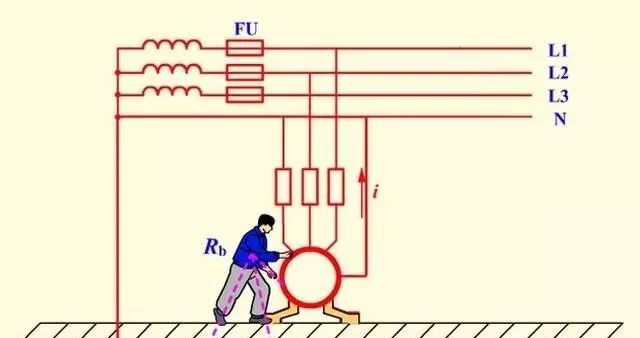

一個集成電路內部有模擬電路和數字電路兩部分,例如ADC,為了避免數字信號耦合到模擬 電路中去,模擬地和數字地通常分開。圖12?1所示是一個ADC的簡單示意圖。從芯片上的焊 點到封裝引腳的連線所產生的引線接合電感和電阻,并不是IC設計者專門加上去的。快速變 化的數字電流在B點產生一個電壓,經過雜散電容(C STRAY )必然耦合到模擬電路的A點 。盡 管這是制造芯片 過程中IC設計者應考慮的問題。可是你能夠看到為了防止進一步耦合,模擬地和數字地的引 腳在外面應該用最短的連線接到同一個低阻抗的接地平面上。任何在數字地引腳附加的外部 阻抗都將在B點上引起較大的數字噪聲。然后將大的數字噪聲通過雜散電容耦合到模擬 電路上。可通過一個極簡單的示意圖(圖12?1)來說明這一點。

圖12?1 模擬地與數字地

問:好,你已告訴我把集成電路的模擬地和數字地引腳接到同一接地平面,但我 仍然要把模擬和數字接地平面在系統中分離開來,我要它們僅僅在一點上連起來,但這 個公共點是電源的返回端,并且連到底座接地線上。那么現在我還要做什么?

答:假如你的系統只有一個數據轉換器,實際上你可以按照產品說明中所說的方 法去做 ,并且把模擬地和數字地線系統一起連在轉換器上。你的系統的星形接地點現在是在數據轉 換器上。但是這也許是極不希望的,除非在開始時你就用這樣的想法來設計你的系統。假如 你有幾個數據轉換器安排在不同的印制線路板上,這個規則不適用應該另想辦法,因為模 擬地 和數字地系統被連接在許多印制線路板的每個轉換器上。對于接地環路這是最好的建議。

問:我已經能想像出來了!假如我必須把模擬地和數字地引腳在器件上連 在一 起,我仍舊需要分開系統的模擬地和數字地,我把模擬地和數字地連起來再接到印制線路板 上的模擬接地平面,或者是數字接地平面上,但不能兩者都連上,對嗎?因為ADC既是模 擬器件又是數字器件,那么連到哪一個接地平面更合適呢?

答:對!假如你把模擬地和數字地引腳都連到數字接地平面上,那么你的模擬輸 入信號將有數字噪聲疊加上去,因為模擬輸入信號是單端的且相對于模擬接地平面而言。

問:所以正確的回答是把模擬地和數字地引腳兩者連起來并接到模擬接地 平面上,對嗎?但這樣會不會把數字噪聲加到本來很好的接地平面上?另外,因為現在輸出信 號是相對于模擬接地平面,而所有其它邏輯是相對于數字接地平面,那么輸出邏輯噪聲容限 是否會下降?我打算把ADC輸出接到印制線路板背面三態數據總線上,在那里噪聲會相當大, 所以我認為首先需要能夠得到的所有噪聲容限。

答:好!沒有什么人會說生活是很容易的!你已經通過困難的道路得到了正確的 結論,但你提出的模擬接地平面上的數字噪聲和在ADC輸出端上減少噪聲容限(noise margin )的問題, 實際上并非像想象的那樣壞,可以把它們克服掉。把幾百毫伏不可靠的信號加到數字接口明 顯地好 于把同樣不可靠信號加到模擬輸入端。對于10 V輸入的16位ADC,其最低位信號僅僅 為150 μV!在數字地引腳上的數字地電流實際上不可能比這更壞,否則它們將使ADC內部 的 模擬部分首先失效!假如你在ADC電源引腳到模擬接地平面之間接一種高質量高頻陶瓷電容器 (0 ?1μF)來旁路高頻噪聲,你將把這些電流隔離到集成電路周圍非常小的范圍,并且將其對 系統其余部分的影響減到最低。

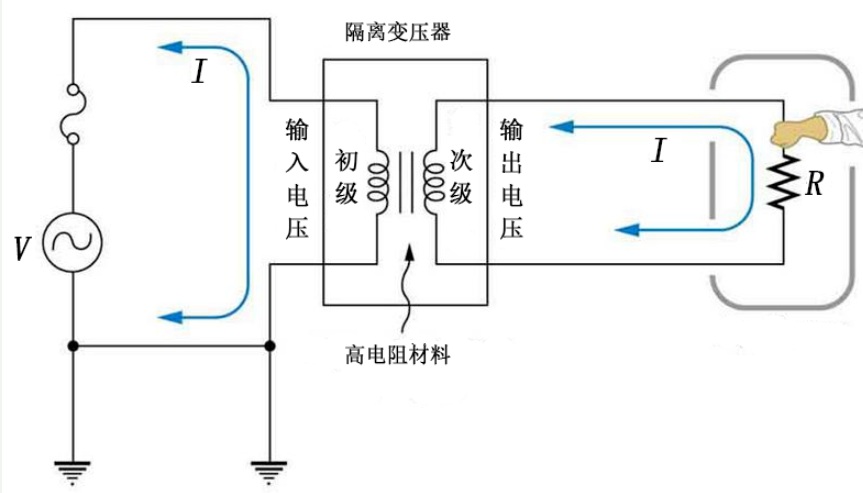

雖然數字噪聲容限會減少,但是如果低于幾百毫伏,對于TTL和CMOS邏輯通常是可以接受 的。假如你的ADC有單端ECL輸出,你就需 要在每一個數字門上加一個推挽門,即起平衡和補償輸出的作用。把這些門電路封裝塊地線 引 到模擬接地平面,并且用差分方式連接邏輯信號接口。在另一端使用一個差分線路接收器, 將 它的接地端接到數字接地平面上。模擬接地平面和數字接地平面之間的噪聲是共模信號,它 們的大 多數將在差分線路接收器的輸出端被衰減抑制掉。你可以把同樣方法用于TTL和CMOS,但它 們通常有足夠的噪聲容限,所以不需要差分傳輸。

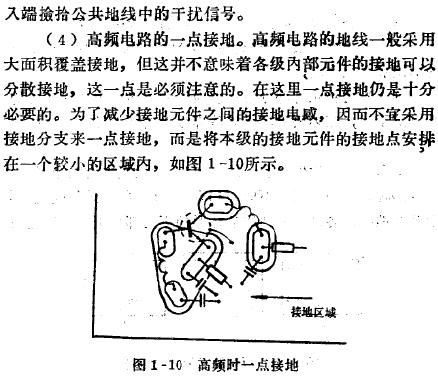

但是你說過的一件事使我大感憂慮。通常把ADC輸出直接連到有噪聲的數據總線上,是很 輕率的作法。總線噪聲經過內部寄生電容耦合可能返回ADC模擬輸入端。寄生電容從0?1到0 ?5 p F。如果把ADC輸出直接連到靠近ADC的中間緩沖鎖存器就要好得多(見圖12?2)。緩沖鎖存器 地線接到數字接地平面上,所以它的輸出邏輯電平和系統其余部分的邏輯電平兼容。

圖12?2 ADC輸出通過緩沖鎖存器接到數據總線

問:我現在明白了。但究竟為什么你不把ADC的所有地線引腳都稱作模擬 地(AGND)?這樣就不會先出現這些問題。

答:假如新來的檢查人員用一只歐姆表,看一看它們在封裝體內部是否連在一起 。這種做法多半會被拒絕,因為集成電路可能會被燒。另外存在一個慣例,我們必須把這些 引腳做標記,以便指示它們的真實功能,而不是像我們想象的那樣。

問:好!我不去做你剛才的試驗了。現在討論一個問題。我有一個同事,他設計了 一個模擬地和數字地獨立的系統,他把模擬地引腳接到模擬接地平面,把數字地引腳 接到 數字接地平面上,他說系統工作得很好,怎么解釋這件事?

答:首先,你按照未被推薦的方法去做,并不一定意味著你能一時僥幸成功,有 時你會陷入虛假的安全感(這就是鮮為人知的Murphy定律),有些ADC對于模擬地與數字 地 引腳 之間的外部噪聲不敏感,你的同事偶然選到的可能就是這一種。如果要求我們對你的同事所 說的 “工作很好”的定義做考察,可能還會有其它的解釋。然而ADC的制造廠家指出,在那種工 作條件下ADC的技術指標得不到保證。像ADC那樣復雜器件要在所有工作條件下進行試驗是不 現實的,特別是在不是首先推薦的那些條件下!你的同事這次是僥幸的。假如這個做法在將 來的系統設計中繼續使用,你還是會相信Murphy定律最終會得到證實的。

問:關于ADC接地的基本原理現在我已經懂了,但對于DAC應該怎樣接地呢 ?

答:應用同樣的原則。DAC的模擬地引腳和數字地引腳連在一起并接到模擬接地平 面 上。如果DAC沒有輸入鎖存器,應該把驅動DAC的寄存器的基準和接地引腳接到模擬地以預 防數字噪聲耦合到模擬輸出端。

問:對于含有ADC,DAC和DSP(例如ADSP?21msp50音頻處理器)的混合處理 芯片應該怎樣接地呢?

答:應用同樣的原則。對于復雜的混合信號芯片,例如ADSP?21msp50,你決不能 把它僅看作是數字芯片!應該應用我們剛剛討論的同樣的原則。即使一個16位的Σ?ΔADC和 DAC的有效采樣速率僅僅為8 ksps,轉換器過采樣工作頻率仍然達到1 MHz。這種轉換器需要 一 個13 MHz的外部時鐘,而52 MHz的內部處理器時鐘是由一個鎖相環來產生的。正如你所看到 的,成功地應用這種器件需要懂得精密電路和高速電路的設計方法。

問:這些器件對模擬電源和數字電源要求怎么樣?我究竟是買獨立的模擬電源和數 字電源,還是買相同的電源?

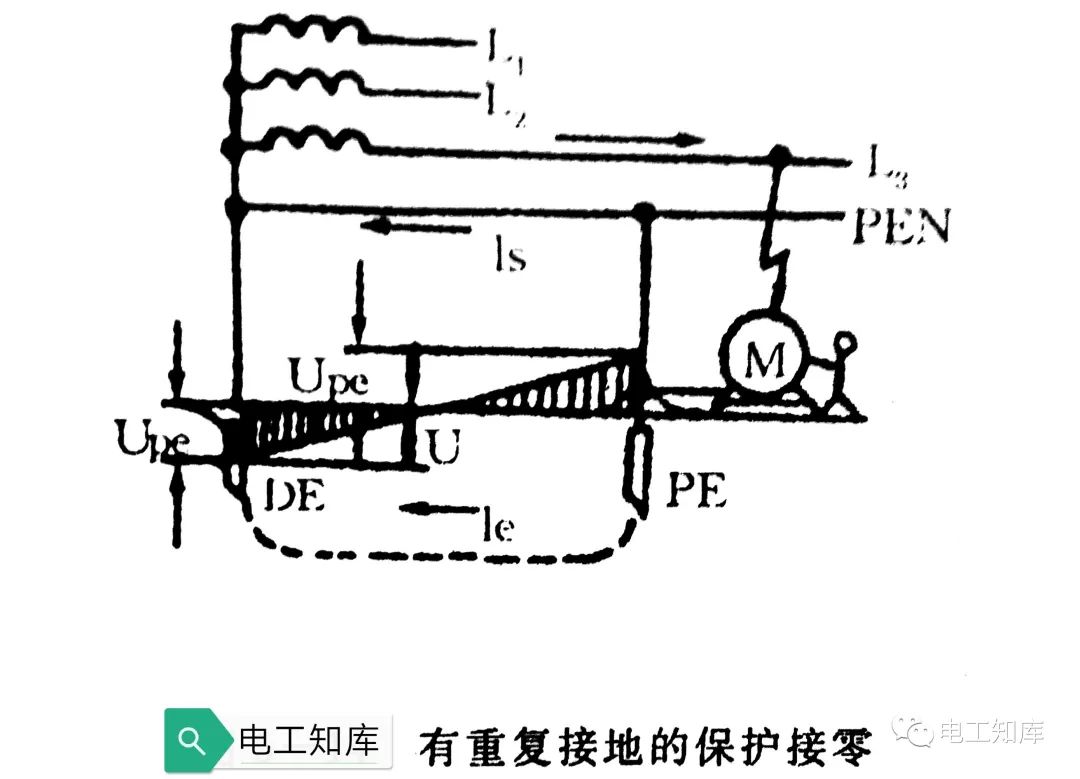

答:這個問題實際上與數字電源的噪聲大小有關。例如ADSP?21msp50有獨立的+5 V 模擬電源引腳和+5 V數字電源引腳。倘若你有一個相當干凈的數字電源,你還把它作為 模擬 電源使用,可能僥幸沒出現問題。一定要在器件每個電源引腳上用0?1μF陶瓷電容適當去 耦 。推薦對模擬接地平面去耦,而不是數字接地平面!你也可以用一個鐵氧體環把模擬電源和 數字電 源進一步隔離。圖12?3示出的是一種正確接法。更為保險的辦法是使用單獨的+5 V電源。 假如你能允許附加的功率損耗,可使用三端穩壓塊從無噪聲+15 V或+12 V電源中產生一個+5 V電 源。

圖12?3 鐵氧體對模擬電源和數字電源的隔離

電子發燒友App

電子發燒友App

評論