本文介紹,許多人把芯片規(guī)模的BGA封裝看作是由便攜式電子產品所需的空間限制的一個可行的解決方案,它同時滿足這些產品更高功能與性能的要求。為便攜式產品的高密度電路設計應該為裝配工藝著想。

當為今天價值推動的市場開發(fā)電子產品時,性能與可靠性是最優(yōu)先考慮的。為了在這個市場上競爭,開發(fā)者還必須注重裝配的效率,因為這樣可以控制制造成本。電子產品的技術進步和不斷增長的復雜性正產生對更高密度電路制造方法的需求。當設計要求表面貼裝、密間距和向量封裝的集成電路?煟桑謾∈保?可能要求具有較細的線寬和較密間隔的更高密度電路板。可是,展望未來,一些已經在供應微型旁路孔、序列組裝電路板的公司正大量投資來擴大能力。這些公司認識到便攜式電子產品對更小封裝的目前趨勢。單是通信與個人計算產品工業(yè)就足以領導全球的市場。

高密度電子產品的開發(fā)者越來越受到幾個因素的挑戰(zhàn):很精密、和環(huán)境,造成裝配處理期間的破裂 。物理因素也包括安裝工藝的復雜性與最終產品的可靠性。進一步的財政決定必須考慮產品將如何制造和裝配設備效率。較脆弱的引腳元件,如0.50與0.40mm,0.20與0.016引腳間距的SQFP quad flatpack ,可能在維護一個持續(xù)的裝配工藝合格率方面向裝配專家提出一個挑戰(zhàn)。最成功的開發(fā)計劃是那些已經實行工藝認證的電路板設計指引和工藝認證的焊盤幾何形狀。

在環(huán)境上,焊盤幾何形狀可能不同,它基于所用的安裝電子零件的焊接類型。可能的時候,焊盤形狀應該以一種對使用的安裝工藝透明的方式來定義。不管零件是安裝在板的一面或兩面、經受波峰、回流或其它焊接,焊盤與零件尺寸應該優(yōu)化,以保證適當?shù)暮附狱c與檢查標準。雖然焊盤圖案是在尺寸上定義的,并且因為它是印制板電路幾何形狀的一部分,它們受到可生產性水平和與電鍍、腐蝕、裝配或其它條件有關的公差的限制。生產性方面也與阻焊層的使用和在阻焊與導體圖案之間的對齊定位有關。

1、焊盤的要求

國際電子技術委員會 International Eletrotechnical Commission 的61188標準認識到對焊接圓角或焊盤凸起條件的不同目標的需要。這個新的國際標準確認兩個為開發(fā)焊盤形狀提供信息的基本方法:

1).基于工業(yè)元件規(guī)格、電路板制造和元件貼裝精度能力的準確資料。這些焊盤形狀局限于一個特定的元件,有一個標識焊盤形狀的編號。

2).一些方程式可用來改變給定的信息,以達到一個更穩(wěn)健的焊接連接,這是用于一些特殊的情況,在這些情況中用于貼裝或安裝設備比在決定焊盤細節(jié)時所假設的精度有或多或少的差別。

該標準為用于貼裝各種引腳或元件端子的焊盤定義了最大、中等和最小材料情況。除非另外標明,這個標準將所有三中“希望目標”標記為一級、二級或三級。

一級:最大 - 用于低密度產品應用,“最大”焊盤條件用于波峰或流動焊接無引腳的片狀元件和有引腳的翅形元件。為這些元件以及向內的″J″型引腳元件配置的幾何形狀可以為手工焊接和回流焊接提供一個較寬的工藝窗口。

二級:中等 -具有中等水平元件密度的產品可以考慮采用這個“中等”的焊盤幾何形狀。與IPC-SM-782標準焊盤幾何形狀非常相似,為所有元件類型配置的中等焊盤將為回流焊接工藝提供一個穩(wěn)健的焊接條件,并且應該為無引腳元件和翅形引腳類元件的波峰或流動焊接提供適當?shù)臈l件。

三級:最小 - 具有高元件密度的產品 式產品應用 可以考慮“最小”焊盤幾何形狀。最小焊盤幾何形狀的選擇可能不適合于所有的產品。在采用最小的焊盤形狀之前,使用這應該考慮產品的限制條件,基于表格中所示的條件進行試驗。

在IPC-SM-782中所提供的以及在IEC61188中所配置的焊盤幾何形狀應該接納元件公差和工藝變量。雖然在IPC標準中的焊盤已經為使用者的多數(shù)裝配應用提供一個穩(wěn)健的界面,但是一些公司已經表示了對采用最小焊盤幾何形狀的需要,以用于便攜式電子產品和其它獨特的高密度應用。

國際焊盤標準(IEC61188)了解到更高零件密度應用的要求,并提供用于特殊產品類型的焊盤幾何形狀的信息。這些信息的目的是要提供適當?shù)谋砻尜N裝焊盤的尺寸、形狀和公差,以保證適當焊接圓角的足夠區(qū)域,也允許對這些焊接點的檢查、測試和返工。

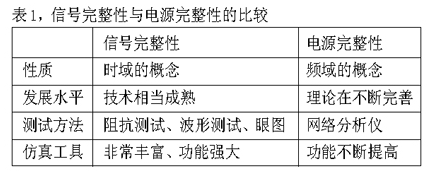

圖一和表一所描述的典型的三類焊盤幾何形狀是為每一類元件所提供的:最大焊盤(一級)、中等焊盤(二級)和最小焊盤(三級)。

圖一、兩個端子的、矩形電容與電阻元件的IEC標準可以不同以滿足特殊產品應用

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 0.6 0.4 0.2

腳跟-焊盤突出 0.0 0.0 0.0

側面-焊盤突出 0.1 0.0 0.0

開井余量 0.5 0.25 0.05

圓整因素 最近0.5 最近0.05 最近0.05

表一、矩形與方形端的元件

(陶瓷電容與電阻) (單位:mm)

焊接點的腳趾、腳跟和側面圓角必須針對元件、電路板和貼裝精度偏差的公差?熎椒膠汀 H繽級?所示,最小的焊接點或焊盤突出是隨著公差變量而增加的(表二)。

圖二、帶狀翅形引腳元件的IEC標準定義了三種可能的變量以滿足用戶的應用

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 0.8 0.5 0.2

腳跟-焊盤突出 0.5 0.35 0.2

側面-焊盤突出 0.05 0.05 0.03

開井余量 0.5 0.25 0.05

圓整因素 最近0.5 最近0.05 最近0.05

表二、平帶L形與翅形引腳

(大于0.625mm的間距) (單位:mm)

如果這些焊盤的用戶希望對貼裝和焊接設備有一個更穩(wěn)健的工藝條件,那么分析中的個別元素可以改變到新的所希望的尺寸條件。這包括元件、板或貼裝精度的擴散,以及最小的焊接點或焊盤突出的期望(表3,4,5和6)。

用于焊盤的輪廓公差方法的方式與元件的類似。所有焊盤公差都是要對每一個焊盤以最大尺寸提供一個預計的焊盤圖形。單向公差是要減小焊盤尺寸,因此得當焊接點形成的較小區(qū)域。為了使開孔的尺寸標注系統(tǒng)容易,焊盤是跨過內外極限標注尺寸的。

在這個標準中,尺寸標注概念使用極限尺寸和幾何公差來描述焊盤允許的最大與最小尺寸。當焊盤在其最大尺寸時,結果可能是最小可接受的焊盤之間的間隔;相反,當焊盤在其最小尺寸時,結果可能是最小的可接受焊盤,需要達到可靠的焊接點。這些極限允許判斷焊盤通過/不通過的條件。

假設焊盤幾何形狀是正確的,并且電路結構的最終都滿足所有規(guī)定標準,焊接缺陷應該可以減少;盡管如此,焊接缺陷還可能由于材料與工藝變量而發(fā)生。為密間距發(fā)焊盤的設計者必須建立一個可靠的焊接連接所要求的最小腳尖與腳跟,以及在元件封裝特征上允許最大與最小?

表三、J形引腳 (單位:mm)

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 0.2 0.2 0.2

腳跟-焊盤突出 0.8 0.6 0.4

側面-焊盤突出 0.1 0.05 0.0

開井余量 1.5 0.8 0.2

圓整因素 最近0.5 最近0.05 最近0.05

表四、圓柱形端子(MELF) (單位:mm)

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 1.0 0.4 0.2

腳跟-焊盤突出 0.2 0.1 0.0

側面-焊盤突出 0.2 0.1 0.0

開井余量 0.2 0.25 0.25

圓整因素 最近0.5 最近0.05 最近0.05

表五、只有底面的端子 (單位:mm)

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 0.2 0.1 0

腳跟-焊盤突出 0.2 0.1 0

側面-焊盤突出 0.2 0.1 0

開井余量 0.25 0.1 0.05

圓整因素 最近0.5 最近0.05 最近0.05

表六、內向L形帶狀引腳 (單位:mm)

焊盤特性 最大一級 中等二級 最小三級

腳趾-焊盤突出 0.1 0.1 0.0

腳跟-焊盤突出 1.0 0.5 0.2

側面-焊盤突出 0.1 0.1 0.1

開井余量 0.5 0.25 0.05

圓整因素 最近0.5 最近0.05 最近0.05

2、BGA與CAP

BGA封裝已經發(fā)展到滿足現(xiàn)在的焊接安裝技術。塑料與陶瓷BGA元件具有相對廣泛的接觸間距(1.50,1.27和1.00mm),而相對而言,芯片規(guī)模的BGA柵格間距為0.50,0.60和0.80mm。BGA與密間距BGA元件兩者相對于密間距引腳框架封裝的IC都不容易損壞,并且BGA標準允許選擇性地減少接觸點,以滿足特殊的輸入/輸出(I/O)要求。當為BGA元件建立接觸點布局和引線排列時,封裝開發(fā)者必須考慮芯片設計以及芯片塊的尺寸和形狀。在技術引線排列時的另一個要面對的問題是芯片的方向?熜酒?模塊的焊盤向上或向下 。芯片模塊“面朝上”的結構通常是當供應商正在使用COB(chip-on-board)(內插器)技術時才采用的。

元件構造,以及在其制造中使用的材料結合,不在這個工業(yè)標準與指引中定義。每一個制造商都將企圖將其特殊的結構勝任用戶所定義的應用。例如?熛?費產品可能有一個相對良好的工作環(huán)境,而工業(yè)或汽車應用的產品經常必須運行在更大的壓力條件下。取決于制造BGA所選擇材料的物理特性,可能要使用到倒裝芯片或引線接合技術。因為芯片安裝結構是剛性材料,芯片模塊安裝座一般以導體定中心,信號從芯片模塊焊盤走入接觸球的排列矩陣。

在該文件中詳細敘述的柵格陣列封裝外形在JEDEC的95出版物中提供。方形BGA,JEDECMS-028定義一種較小的矩形塑料BGA元件類別,接觸點間隔為1.27mm。該矩陣元件的總的外形規(guī)格允許很大的靈活性,如引腳間隔、接觸點矩陣布局與構造。JEDEC MO-151定義各種塑料封裝的BGA。方形輪廓覆蓋的尺寸從7.0-50.0,三種接觸點間隔 -1.50,1.27和1.00mm。

球接觸點可以單一的形式分布,行與列排列有雙數(shù)或單數(shù)。雖然排列必須保持對整個封裝外形的對稱,但是各元件制造商允許在某區(qū)域內減少接觸點的位置。

3、芯片規(guī)模的BGA變量

針對“密間距”和“真正芯片大小”的IC封裝,最近開發(fā)的JEDECBGA指引提出許多物理屬性,并為封裝供應商提供“變量”形式的靈活性。JEDECJC-11批準的第一份對密間距元件類別的文件是注冊外形MO-195,具有基本0.50mm間距接觸點排列的統(tǒng)一方形封裝系列。

封裝尺寸范圍從4.0-21.0mm,總的高度(定義為“薄的輪廓”)限制到從貼裝表面最大為1.20mm。下面的例子代表為將來的標準考慮的一些其它變量。

球間距與球尺寸將也會影響電路布線效率。許多公司已經選擇對較低I/O數(shù)的CSP不采用0.50mm間距。較大的球間距可能減輕最終用戶對更復雜的印刷電路板(PCB)技術的需求。

0.50mm的接觸點排列間隔是JEDEC推薦最小的。接觸點直徑規(guī)定為0.30mm,公差范圍為最小0.25、最大0.35mm。可是大多數(shù)采用0.50mm間距的BGA應用將依靠電路的次表面布線。直徑上小至0.25mm的焊盤之間的間隔寬度只夠連接一根0.08mm(0.003″)寬度的電路。將許多多余的電源和接地觸點分布到矩陣的周圍,這樣將提供對排列矩陣的有限滲透。這些較高I/O數(shù)的應用更可能決定于多層、盲孔或封閉的焊盤上的電鍍旁路孔 (via-on-pad)技術。

4、考慮封裝技術

元件的環(huán)境與電氣性能可能是與封裝尺寸一樣重要的問題。用于高密度、高I/O應用的封裝技術首先必須滿足環(huán)境標準。例如,那些使用剛性內插器(interposer)結構的、由陶瓷或有機基板制造的不能緊密地配合硅芯片的外形。元件四周的引線接合座之間的互連必須流向內面。μBGA* 封裝結構的一個實際優(yōu)勢是它在硅芯片模塊外形內提供所有電氣界面的能力。

μBGA使用一種高級的聚酰胺薄膜作為其基體結構,并且使用半加成銅電鍍工藝來完成芯片上鋁接合座與聚酰胺內插器上球接觸座之間的互連。依順材料的獨特結合使元件能夠忍受極端惡劣的環(huán)境。這種封裝已經由一些主要的IC制造商用來滿足具有廣泛運作環(huán)境的應用。

超過20家主要的IC制造商和封裝服務提供商已經采用了μBGA封裝。定義為“面朝下”的封裝,元件外形密切配合芯片模塊的外形,芯片上的鋁接合焊盤放于朝向球接觸點和PCB表面的位置。這種結構在工業(yè)中有最廣泛的認同,因為其建立的基礎結構和無比的可靠性。μBGA封裝的材料與引腳設計的獨特系統(tǒng)是在物理上順應的,補償了硅芯片與PCB結構的溫度膨脹系統(tǒng)的較大差別。

5、安裝座計劃

推薦給BGA元件的安裝座或焊盤的幾何形狀通常是圓形的,可以調節(jié)直徑來滿足接觸點間隔和尺寸的變化。焊盤直徑應該不大于封裝上接觸點或球的直徑,經常比球接觸點規(guī)定的正常直徑小10%。在最后確定焊盤排列與幾何形狀之前,參考IPC-SM-782第14.0節(jié)或制造商的規(guī)格。

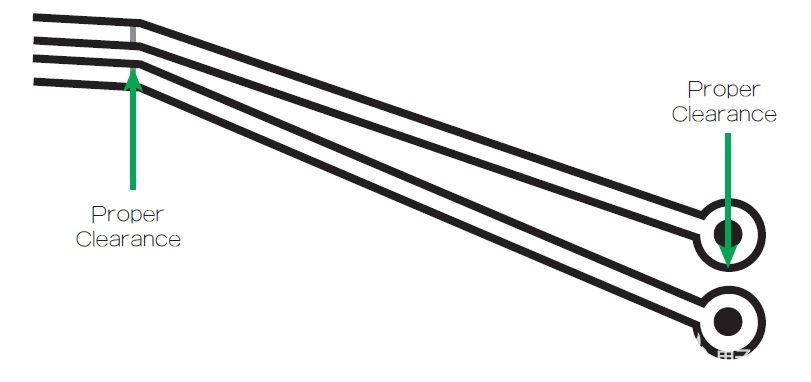

有兩種方法用來定義安裝座:定義焊盤或銅,定義阻焊,如圖三所示。

圖三、BGA的焊盤可以通過化學腐蝕的圖案來界定,

無阻焊層或有阻焊層疊加在焊盤圓周上(阻焊層界定)

銅定義焊盤圖形 - 通過腐蝕的銅界定焊盤圖形。阻焊間隔應該最小離腐蝕的銅焊盤0.075mm。對要求間隔小于所推薦值的應用,咨詢印制板供應商。

阻焊定義焊盤圖形 - 如果使用阻焊界定的圖形,相應地調整焊盤直徑,以保證阻焊的覆蓋。

BGA元件上的焊盤間隔活間距是“基本的”,因此是不累積的;可是,貼裝精度和PCB制造公差必須考慮。如前面所說的,BGA的焊盤一般是圓形的、阻焊界定或腐蝕?熥韜竿牙牒概獺〗綞ǖ摹K淙喚洗蠹渚嗟模攏牽兩?接納電路走線的焊盤之間的間隔,較高I/O的元件將依靠電鍍旁路孔來將電路走到次表面層。表七所示的焊盤幾何形狀推薦一個與名義標準接觸點或球的直徑相等或稍小的直徑。

表七、 BGA元件安裝的焊盤圖形

接觸點間距

(基本的) 標準球直徑 焊盤直徑 (mm)

最小 名義 最大 最小 - 最大

0.05 0.25 0.30 0.35 0.25-0.30

0.65 0.25 0.30 0.35 0.25-0.30

0.65 0.35 0.40 0.45 0.35-0.40

0.80 0.25 0.30 0.35 0.25-0.30

0.80 0.35 0.40 0.45 0.35-0.40

0.80 0.45 0.50 0.55 0.40-0.50

1.00 0.55 0.60 0.65 0.50-0.60

1.27 0.70 0.75 0.80 0.60-0.70

1.50 0.70 0.75 0.80 0.60-0.70

有些公司企圖為所有密間距的BGA應用維持一個不變的接觸點直徑。可是,因為一些0.65與0.80mm接觸點間距的元件制造商允許隨意的球與接觸點直徑的變化,設計者應該在制定焊盤直徑之前參考專門的供應商規(guī)格。較大的球與焊盤的直徑可能限制較高I/O元件的電路布線。一些BGA元件類型的焊盤幾何形狀可能不允許寬度足夠容納不止一條或兩條電路的間隔。例如,0.50mm間距的BGA將不允許甚至一條大于0.002″或0.003″的電路。那些采用密間距BGA封裝變量的可能發(fā)現(xiàn)焊盤中的旁路孔(微型旁路孔)更加實際,特別如果元件密度高,必須減少電路布線。

6、裝配工藝效率所要求的特征

為了采納對密間距表面貼裝元件(SMD)的模板的精確定位,要求一些視覺或攝像機幫助的對中方法。全局定位基準點是用于準確的錫膏印刷的模板定位和在精確的SMD貼裝中作為參考點。模板印刷機的攝相機系統(tǒng)自動將板對準模板,達到準確的錫膏轉移。

對于那些使用模板到電路板的自動視覺對中的系統(tǒng),電路板的設計者必須在焊盤層的設計文件中提供至少兩個全局基準點(圖四)。在組合板的每一個裝配單元內也必須提供局部基準點目標,以幫助自動元件貼裝。另外,對于每一個密間距QFP、TSOP和高I/O密間距BGA元件,通常提供一或兩個目標。

在所有位置推薦使用一個基準點的尺寸。雖然形狀和尺寸可以對不同的應用分別對待,但是大多數(shù)設備制造商都認同1.0mm(0.040″)直徑的實心點。該點必須沒有阻焊層,以保證攝相機可以快速識別。除了基準點目標外,電路板必須包含一些定位孔,用于二次裝配有關的操作。組合板應該提供兩或三個定位孔,每個電路板報單元提供至少兩個定位孔。通常,裝配專家規(guī)定尺寸(0.65mm是常見的),應該指定無電鍍孔。

至于在錫膏印刷模板夾具上提供的基準點,一些系統(tǒng)檢測模板的定面,而另一些則檢測底面。模板上的全局基準點只是半腐蝕在模板的表面,用黑樹脂顏料填充。

7、指定表面最終涂層

為元件的安裝選擇專門類型的表面最終涂鍍方法可以提高裝配工藝的效率,但是也可能影響PCB的制造成本。在銅箔上電鍍錫或錫/鉛合金作為抗腐蝕層是非常常見的制造方法。選擇性地去掉銅箔的減去法?熁?學腐蝕 繼續(xù)在PCB工業(yè)廣泛使用。因為錫/鉛導線當暴露在195°C溫度以上時變成液體,所以大多數(shù)使用回流焊接技術的表面貼裝板都指定裸銅上的阻焊層(SMOBC,soldermask over barecopper)來保持阻焊材料下一個平坦均勻的表面。當處理SMOBC板時,錫或錫/鉛是化學剝離的,只留下銅導體和沒有電鍍的元件安裝座。銅導體用環(huán)氧樹脂或聚合物阻焊層涂蓋,以防止對焊接有關工藝的暴露。雖然電路導線有阻焊層覆蓋,設計者還必須為那些不被阻焊層覆蓋的部分?熢?件安裝座 指定表面涂層。下面的例子是廣泛使用在制造工業(yè)的合金電鍍典型方法。

通常要求預處理安裝座的應用是超密間距QFP元件。例如,TAB(tableautomatedbond)元件可能具有小于0.25mm的引腳間距。通過在這些座上提供700-800μ″的錫/鉛合金,裝配專家可以上少量的助焊劑、貼裝零件和使用加熱棒、熱風、激光或軟束線光源來回流焊接該元件。在特殊的安裝座上選擇性地電鍍或保留錫/鉛合金將適用于超密間距TAB封裝的回流焊接。

使用熱風均勻法,錫/鉛在上阻焊層之后涂鍍在電路板上。該工藝是,電鍍的板經過清洗、上助焊劑和浸入熔化的焊錫中,當合金還是液體狀態(tài)的時候,多余的材料被吹離表面,留下合金覆蓋的表面。熱風焊錫均勻?煟齲粒櫻?(hot air solderleveling)電鍍工藝廣泛使用,一般適合于回流焊接裝配工藝;可是,焊錫量與平整度的不一致可能不適合于使用密間距元件的電路板。

密間距的SQFP、TSOP和BGA元件要求非常均勻和平整的表面涂層。作為控制在密間距元件的安裝座上均勻錫膏量的方法,表面必須盡可能地平整。為了保證平整度,許多公司在銅箔上使用鎳合金,接著一層很薄的金合金涂層,來去掉氧化物。

在阻焊涂層工藝之后,在暴露的裸銅上使用無電鍍鎳/金。用這個工藝,制造商通常將使用錫/鉛電鍍圖案作為抗腐蝕層,在腐蝕之后剝離錫/鉛合金,但是不是對暴露的安裝座和孔施用焊錫合金,而是電路板浸鍍鎳/金合金。

按照IPC-2221標準《印制板設計的通用標準》,推薦的無電鍍鎳厚度是2.5-5.0μm(至少1.3μm),而推薦的浸金厚度為0.08-0.23μm。

有關金的合金與焊接工藝的一句話忠告:如果金涂層厚度超過0.8μm(3μ″),那么金對錫/鉛比率可能引起最終焊接點的脆弱。脆弱將造成溫度循環(huán)中的過分開裂或裝配后的板可能暴露到的其它物理應力。

8、合金電鍍替代方案

在上阻焊層之后給板增加焊錫合金是有成本代價的,并且給基板遭受極大的應力條件。例如用錫/鉛涂層,板插入熔化的焊錫中,然后抽出和用強風將多余的錫/鉛材料去掉。溫度沖擊可能導致基板結構的脫層、損壞電鍍孔和可能影響長期可靠性的缺陷。Ni/Au涂鍍,雖然應力較小,但不是所有電路板制造商都有的一種技術。作為對電鍍的另一種選擇,許多公司已經找到成功的、有經濟優(yōu)勢的和平整的安裝表面的方法,這就是有機保護層或在裸銅上與上助焊劑涂層。

作為阻止裸銅安裝座和旁通孔/測試焊盤上氧化增長的一個方法,將一種特殊的保護劑或阻化劑涂層應用到板上。諸如苯并三唑(Benzotriazole)和咪唑(Imidazole)這些有機/氮涂層材料被用來取代上面所描述的合金表面涂層,可從幾個渠道購買到,不同的商標名稱。在北美洲,廣泛使用的一種產品是ENTEK PLUSCU-106A。這種涂層適合于大多數(shù)有機助焊焊接材料,在對裝配工藝中經常遇到的三、四次高溫暴露之后仍有保護特征。多次暴露的能力是重要的。當SMD要焊接到裝配的主面和第二面的時候,會發(fā)生兩次對回流焊接溫度的暴露。混合技術典型的多次裝配步驟也可能包括對波峰焊接或其它焊接工藝的暴露。

9、一般成本考慮

與PCB電鍍或涂鍍有關的成本不總是詳細界定的。一些供應商感覺方法之間的成本差別占總的單位成本中的很小部分,所以界不界定是不重要的。其他的可能對不是其能力之內的成本有一個額外的費用,因為板必須送出去最后加工。例如,在加州的一家公司將板發(fā)送給在德州的一家公司進行Ni/Au電鍍。這個額外處理的費用可能沒有清晰地界定為對客戶的一個額外開支;可是,總的板成本受到影響。

每一個電鍍和涂鍍工藝都有其優(yōu)點與缺點。設計者與制造工程師必須通過試驗或工藝效率評估仔細地權衡每一個因素。在指定PCB制造是必須考慮的問題都有經濟以及工藝上的平衡。對于細導線、高元件密度或密間距技術與 μBGA,平整的外形是必須的。焊盤表面涂層可以是電鍍的或涂敷的,但必須考慮裝配工藝與經濟性。

在所有涂敷和電鍍的選擇中,Ni/Au是最萬能的(只要金的厚度低于5μ″)。電鍍工藝比保護性涂層好的優(yōu)勢是貨架壽命、永久性地覆蓋在那些不暴露到焊接工藝的旁路孔或其它電路特征的銅上面、和抗污染。雖然表面涂層特性之間的平衡將影響最終選擇,但是可行性與總的PCB成本最可能決定最后的選擇。在北美,HASL工藝傳統(tǒng)上主宰PCB工業(yè),但是表面的均勻性難于控制。對于密間距元件的焊接,一個受控的裝配工藝取決于一個平整均勻的安裝座。密間距元件包括TSOP、SQFP和μBGA元件族。如果密間距元件在裝配中不使用,使用HASL工藝是可行的選擇。

10、阻焊層(sldermask)要求

阻焊層在控制回流焊接工藝期間的焊接缺陷中的角色是重要的,PCB設計者應該盡量減小焊盤特征周圍的間隔或空氣間隙。雖然許多工藝工程師寧可阻焊層分開板上所有焊盤特征,但是密間距元件的引腳間隔與焊盤尺寸將要求特殊的考慮。雖然在四邊的QFP上不分區(qū)的阻焊層開口或窗口可能是可接受的,但是控制元件引腳之間的錫橋可能更加困難。對于BGA的阻焊層,許多公司提供一種阻焊層,它不接觸焊盤,但是覆蓋焊盤之間的任何特征,以防止錫橋。多數(shù)表面貼裝的PCB以阻焊層覆蓋,但是阻焊層的涂敷,如果厚度大于0.04mm(0.0015″),可能影響錫膏的應用。表面貼裝PCB,特別是那些使用密間距元件的,都要求一種低輪廓感光阻焊層。阻焊材料必須通過液體?熓? 工藝或者干薄膜疊層來使用。干薄膜阻焊材料是以0.07-0.10mm(0.003-0.004″)厚度供應的,可適合于一些表面貼裝產品,但是這種材料不推薦用于密間距應用。很少公司提供薄到可以滿足密間距標準的干薄膜,但是有幾家公司可以提供液體感光阻焊材料。通常,阻焊的開口應該比焊盤大0.15mm(0.006″)。這允許在焊盤所有邊上0.07mm(0.003″)的間隙。低輪廓的液體感光阻焊材料是經濟的,通常指定用于表面貼裝應用,提供精確的特征尺寸和間隙。

結論

密間距 (fine-pitch)、BGA和CSP的裝配工藝可以調整到滿足可接受的效率水平,但是彎曲的引腳和錫膏印刷的不持續(xù)性經常給裝配工藝合格率帶來麻煩。雖然使用小型的密間距元件提供布局的靈活性,但是將很復雜的多層基板報上的元件推得更近,可能犧牲可測試性和修理。BGA元件的使用已經提供較高的裝配工藝合格率和更多的布局靈活性,提供較緊密的元件間隔與較短的元件之間的電路。一些公司正企圖將幾個電路功能集成到一兩個多芯片的BGA元件中來釋放面積的限制。用戶化的或專用的IC可以緩解PCB的柵格限制,但是較高的I/O數(shù)與較密的引腳間距一般都會迫使設計者使用更多的電路層,因此增加PCB制造的復雜性與成本。

芯片規(guī)模的BGA封裝被許多人看作是新一代手持與便攜式電子產品空間限制的可行答案。許多公司也正在期待改進的功能以及更高的性能。當為這些元件選擇最有效的接觸點間距時,必須考慮硅芯片模塊的尺寸、信號的數(shù)量、所要求的電源與接地點和在印制板上采用這些元件時的實際限制。雖然密間距的芯片規(guī)模(chipscale)與芯片大小的元件被看作是新出現(xiàn)的技術,但是主要的元件供應商和幾家主要的電子產品制造商已經采用了一兩種CSP的變化類型。在較小封裝概念中的這種迅速增長是必須的,它滿足產品開發(fā)商對減小產品尺寸、增加功能并且提高性能的需求。

第二篇? 抗干擾3(部分)

提高敏感器件的抗干擾性能

提高敏感器件的抗干擾性能是指從敏感器件這邊考慮盡量減少對干擾噪聲

的拾取,以及從不正常狀態(tài)盡快恢復的方法。

提高敏感器件抗干擾性能的常用措施如下:

(1)布線時盡量減少回路環(huán)的面積,以降低感應噪聲。

(2)布線時,電源線和地線要盡量粗。除減小壓降外,更重要的是降低耦

合噪聲。

(3)對于單片機閑置的I/O口,不要懸空,要接地或接電源。其它IC的閑置

端在不改變系統(tǒng)邏輯的情況下接地或接電源。

(4)對單片機使用電源監(jiān)控及看門狗電路,如:IMP809,IMP706,IMP813,

X25043,X25045等,可大幅度提高整個電路的抗干擾性能。

(5)在速度能滿足要求的前提下,盡量降低單片機的晶振和選用低速數(shù)字

電路。

(6)IC器件盡量直接焊在電路板上,少用IC座。

第三篇? 印制電路板的可靠性設計-去耦電容配置

在直流電源回路中,負載的變化會引起電源噪聲。例如在數(shù)字電路中,當電路從一個狀態(tài)轉換為另一種狀態(tài)時,就會在電源線上產生一個很大的尖峰電流,形成瞬變的噪聲電壓。配置去耦電容可以抑制因負載變化而產生的噪聲,是印制電路板的可靠性設計的一種常規(guī)做法,配置原則如下:

●電源輸入端跨接一個10~100uF的電解電容器,如果印制電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會更好。

●為每個集成電路芯片配置一個0.01uF的陶瓷電容器。如遇到印制電路板空間小而裝不下時,可每4~10個芯片配置一個1~10uF鉭電解電容器,這種器件的高頻阻抗特別小,在500kHz~20MHz范圍內阻抗小于1Ω,而且漏電流很小(0.5uA以下)。

●對于噪聲能力弱、關斷時電流變化大的器件和ROM、RAM等存儲型器件,應在芯片的電源線(Vcc)和地線(GND)間直接接入去耦電容。

●去耦電容的引線不能過長,特別是高頻旁路電容不能帶引線。?

第四篇? 電磁兼容性和PCB設計約束(缺具體數(shù)據(jù))

?? PCB布線對PCB的電磁兼容性影響很大,為了使PCB上的電路正常工作,應根據(jù)本文所述的約束條件來優(yōu)化布線以及元器件/接頭和某些IC所用去耦電路的布局

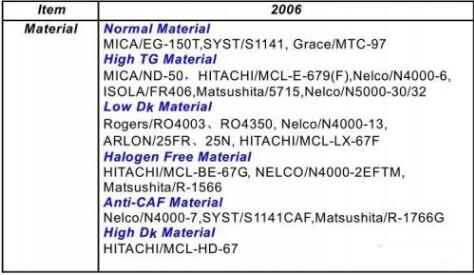

(一)、PCB材料的選擇

?? 通過合理選擇PCB的材料和印刷線路的布線路徑,可以做出對其它線路耦合低的傳輸線。當傳輸線導體間的距離d小于同其它相鄰導體間的距離時,就能做到更低的耦合,或者更小的串擾(見《電子工程專輯》2000年第1期"應用指南")。

?? 設計之前,可根據(jù)下列條件選擇最經濟的PCB形式:

對EMC的要求

·印制板的密集程度

·組裝與生產的能力

·CAD系統(tǒng)能力

·設計成本

·PCB的數(shù)量

·電磁屏蔽的成本

?? 當采用非屏蔽外殼產品結構時,尤其要注意產品的整體成本/元器件封裝/管腳樣式、PCB形式、電磁場屏蔽、構造和組裝),在許多情況下,選好合適的PCB形式可以不必在塑膠外殼里加入金屬屏蔽盒。

?? 為了提高高速模擬電路和所有數(shù)字應用的抗擾性同時減少有害輻射,需要用到傳輸線技術。根據(jù)輸出信號的轉換情況,S-VCC、S-VEE及VEE-VCC之間的傳輸線需要表示出來,如圖1所示。

?? 信號電流由電路輸出級的對稱性決定。對MOS而言IOL=IOH,而對TTL而言IOL>IOH.

功能/邏輯類型??? ZO(Ω)

電源(典型值) <<10

ECL邏輯???????? 50

TTL邏輯???????? 100

HC(T)邏輯??????? 200

表1:幾種信號路徑的傳輸線阻抗ZO。

?? 邏輯器件類型和功能上的原因決定了傳輸線典型特征阻抗ZO,如表1所示。

圖1:顯示三種特定傳輸線的(數(shù)字)IC之間典型互聯(lián)圖

圖2:IC去耦電路。

圖3:正確的去耦電路塊

表2:去耦電容Cdec..的推薦值。

邏輯電路噪聲容限

(二)、信號線路及其信號回路

?? 傳送信號的線路要與其信號回路盡可能靠近,以防止這些線路包圍的環(huán)路區(qū)域產生輻射,并降低環(huán)路感應電壓的磁化系數(shù)。

?? 一般情況下,當兩條線路間的距離等于線寬時,耦合系數(shù)大約為0.5到0.6,線路的有效自感應從1μH/m降到0.4-0.5μ H/m.

?? 這就意味著信號回路電流的40%到50%自由地就流向了PCB上其它線路。

?? 對兩個(子)電路塊間的每一塊信號路徑,無論是模擬的還是數(shù)字的,都可以用三種傳輸線來表示,如圖1所示,其中阻抗可從表1得到。

?? TTL邏輯電路由高電平向低電平轉換時,吸收電流會大于電源電流以,在這種情況下,通常將傳輸線定義在Vcc和S之間,而不是VEE和S之間。通過采用鐵氧體磁環(huán)可完全控制信號線和信號回路線上的電流。

?? 在平行導體情況下,傳輸線的特征阻抗會因為鐵氧體而受到影響,而在同軸電纜的情況下,鐵氧體只會對電纜的外部參數(shù)有影響。

?? 因此,相鄰線路應盡可能細,而上下排列的則相反(通常距離小于1.5mm/雙層板中環(huán)氧樹脂的厚度)。布線應使每條信號線和它的信號回路盡可能靠近(信號和電源布線均適用)。如果傳輸線導體間耦合不夠,可采用鐵氧體磁環(huán)。

(三)、IC的去耦

?? 通常IC僅通過電容來達到去耦的目的,因為電容并不理想,所以會產生諧振。在大于諧振頻率時,電容表現(xiàn)得象個電感,這就意味著di/dt受到了限制。電容的值由IC管腳間允許的電源電壓波動來決定,根據(jù)資深設計人員的實踐經驗,電壓波動應小于信號線最壞狀況下的噪聲容限的25%,下面公式可計算出每種邏輯系列輸出門電路的最佳去耦電容值:

? I=c·dV/dt

?? 表2給出了幾種邏輯系列門電路在最壞情況下信號線噪聲的容限,同時還給出每個輸出級應加的去耦電容Cdec.的推薦值。

圖4:PCB上環(huán)路的輻射

?? 對快速邏輯電路來說,如果去耦電容含有很大串聯(lián)電感(這種電感也許是由電容的結構、長的連接線或PCB的印制線路造成的),電容的值可能不再有用。這時則需要在盡可能靠近IC管腳的地方加入另外一個小陶瓷電容(100- 100Pf),與"LF-"去耦電容并聯(lián)。陶瓷電容的諧振頻率(包括到IC電源管腳的線路長度)應高于邏輯電路的帶寬[1/(π.τr)],其中,τr是邏輯電路中電壓的上升時間。

?? 如果每個IC都有去耦電容,信號回路電流可選擇最方便的路徑,VEE或者VCC,這可以由傳送信號的線路和電源線路間的互耦來決定。

?? 在兩個去耦電容(每個IC一個)和電源線路形成的電感Ltrace之間,會形成串聯(lián)諧振電路,這種諧振只可以發(fā)生在低頻(<1MHz=或諧振電路的Q值較低(<2=的情況下。

?? 通過將高射頻損耗扼流線圈串聯(lián)在Vcc網絡和要去耦的IC中,可使諧振頻率保持在1MHz以下,如果射頻損耗太低可通過并聯(lián)或串聯(lián)電阻來補償(圖2)。

?? 扼流線圈應該總是采用封閉的內芯,否則它會成為一個射頻發(fā)射器或磁場鐵感應器。

例如:1MHz*1μHz??? Z1=6.28Ω? Rs=3.14Ω???? Q<2 Rp=12.56Ω

?? 大于諧振頻率時,"傳輸線"的特征阻抗Z0(此時將IC的阻抗看作電源負載)等于:Z0 =(Ltrace/Cdecoupling)的平方根

??? 去耦電容的串聯(lián)電感和連接線路的電感對射頻電源電流分配沒有多大影響,比如采用了一個1μH扼流線圈的情況。但它仍然會決定IC電源管腳間的電壓波動,表 3給出了電源信噪容限為25%時,推薦的最大電感值Ltrace.根據(jù)圖2所建議的去耦方法,兩個IC間的傳輸線數(shù)量從3條減少到了1條(見圖3)。

?? 因此,對每個IC采用適當?shù)娜ヱ罘椒ǎ篖choke+Cdec.電路塊間就只需定義一條傳輸線。

?? 對于τr<3ns的高速邏輯電路,與去耦電容串聯(lián)的全部電感必須要很低(見表3)。與電源管腳串聯(lián)的50mm印制線路相當于一個50hH電感,與輸出端的負載(典型值為50pF)一起決定了最小上升時間為3.2ns。如要求更快的上升時間,就必須縮短去耦電容的引腳。長度(最好無引腳)并縮短IC封裝的引腳,例如可以用IC去耦電容,或最好采用將(電源)管腳在中間的IC與很小的3E間距(DIL)無引腳陶瓷電容相結合等方法來達到這一目的,也可以用帶電源層和接地層的多層電路板。另外采用電源管腳在中間的SO封裝還可得到進一步的改善。但是,使用快速邏輯電路時,應采用多層電路板。

(四)、根據(jù)輻射決定環(huán)路面積

?? 無終點傳輸線的反射情況決定了線路的最大長度。由于對產品的EM輻射有強制性要求,因此環(huán)路區(qū)域的面積和線路長度都受到限制,如果采用非屏蔽外殼,這種限制將直接由PCB來實現(xiàn)。

?? 注意:如果在異步邏輯電路設計中采用串聯(lián)端接負載,必須要注意會出現(xiàn)準穩(wěn)性,特別是對稱邏輯輸入電路無法確定輸入信號是高還是低,而且可能會導致非定義輸出情況。

圖3:正確的去耦電路塊。

??? 對于頻域中的邏輯信號,頻譜的電流幅度在超出邏輯信號帶寬(=1/π.τr)的頻率上與頻率的平方成反比。用角頻率表示,環(huán)路的輻射阻抗仍隨頻率平方成正比。因而可計算出最大的環(huán)路面積,它由時鐘速率或重復速率、邏輯信號的上升時間或帶寬以及時域的電流幅度決定。電流波形由電壓波形決定,電流半寬時間約等于電壓的上升時間。

? 電流幅度可用角頻率(=1/π.τr)表示為:? I(f)=2.I. τr/T

其中: I=為時域電流幅度;T=為時鐘速率的倒數(shù),即周期;

???? τr為電壓的上升時間,約等于電流半寬時間τH。

? 從這一等式可計算出某種邏輯系列電路在某一時鐘速率下最大環(huán)路面積,表5給出了相應的環(huán)路面積。最大環(huán)路面積由時鐘速率、邏輯電路類型(=輸出電流)和PCB上同時存在的開關環(huán)路數(shù)量n決定。

?? 如果所用的時鐘速率超過30MHz,就必須要采用多層電路板,在這種情況下,環(huán)氧樹脂的厚度與層數(shù)有關,在60至300μm之間。只有當PCB上的高速時鐘信號的數(shù)量有限時,通過采用層到層的線路進行仔細布線,也可在雙層板上得到可以接受的結果。

?? 注意:在這種情況下,如采用普通DIL封裝,則會超過環(huán)路面積的限制,一定要有另外的屏蔽措施和適當?shù)臑V波。

?? 所有連接到其它面板及部件的連接頭必須盡可能相互靠近放置,這樣在電纜中傳導的共模電流就不會流入PCB電路中的線路,另外,PCB上參考點間的電壓降也無法激勵(天線)電纜。

?? 為避免這種共模影響,必須使靠近接頭的參考地和PCB上電路的接地層、接地網格或電路參考地隔開,如果可能,這些接地片應接到產品的金屬外殼上。從這個接地片上,只有高阻器件如電感、電阻、簧片繼電器和光耦合器可接在兩個地之間。所有的接頭要盡可能靠近放置,以防止外部電流流過PCB上的線路或參考地。

(五)、電纜及接頭的正確選擇

?? 電纜的選擇由流過電纜的信號幅度和頻率成分決定。對于位于產品外部的電纜來說,如果傳送10kHz以上時鐘速率的數(shù)據(jù)信號,則一定要用到屏蔽(產品要求),屏蔽部分應在電纜的兩端連接到地(金屬外殼產品),這樣能確保對電場和磁場都進行屏蔽。

?? 如果用的是分開接地,則應連到"接頭地"而不是"電路地"。

?? 如果時鐘速率在10kHz到1MHz之間,并且邏輯電路的上升時間盡可能保持低,將可以得到80%以上的光覆蓋或小于10Nh/m的轉移阻抗。如果時鐘速率超過1MHz時,就需要更好的屏蔽電纜。

?? 通常,除同軸電纜外,電纜的屏蔽不應用作為信號回路。

?? 通過在信號輸入/輸出和地/參考點之間串入無源濾波器以減少射頻成分,可以不必采用高質量屏蔽和相應接頭。好的屏蔽電纜應配備合適的連接頭。

電子發(fā)燒友App

電子發(fā)燒友App

評論